**Olivier Duarte**

february 11th 2011

### **Tests Front-end card Status**

#### • Firmware A3PE

- Architecture status

- Clock divider and Trigger generator

- Acquisition sequence

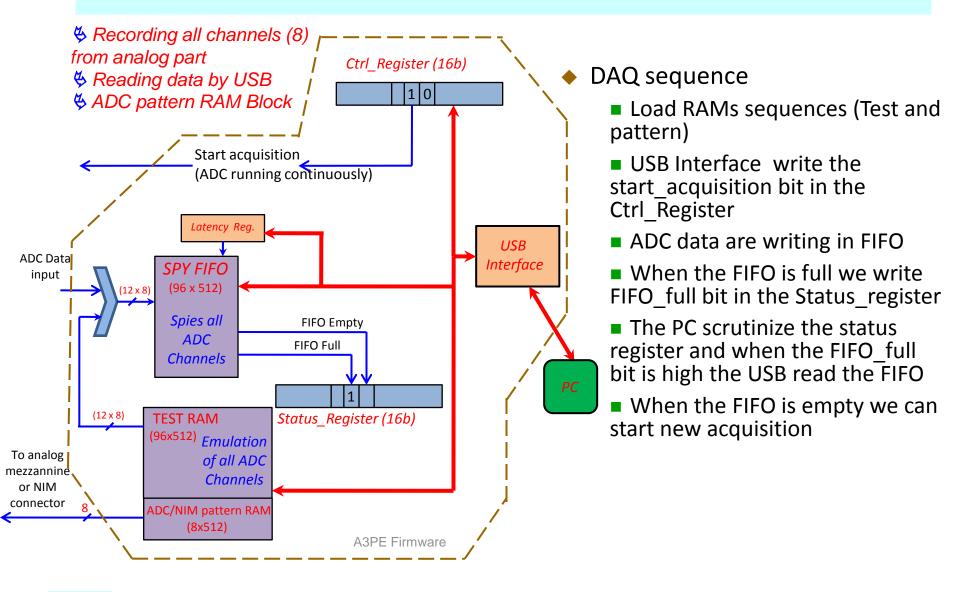

- Basic DAQ

- Test status

- Next step

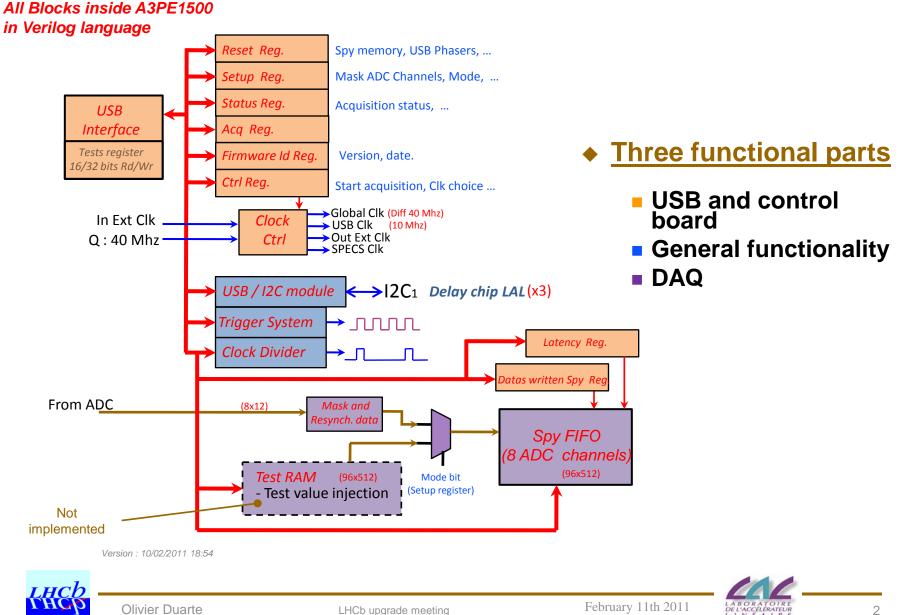

### Firmware architecture status

## <u>A3PE firmware blocks : Clock divider</u> <u>and trigger generator</u>

#### Clock divider

50 ns to 0.4s (24 bits counter)

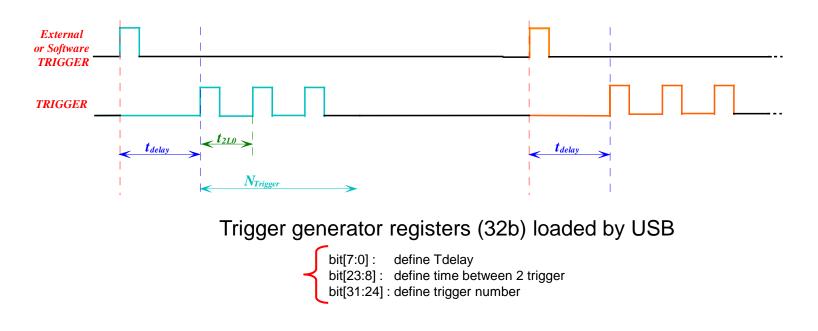

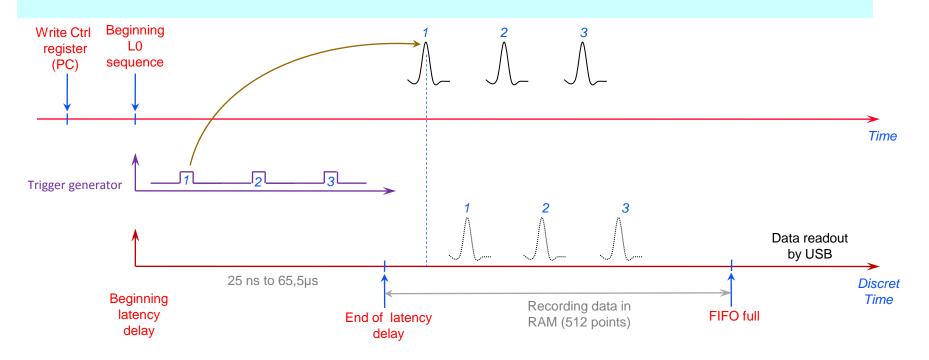

#### Trigger generator (L0)

With this module we can produce trigger (external trigger or software command)

- PC write start sequence bit of Ctrl register.

- Beginning of L0 sequence.

- Each trigger pulse involve pulse shape.

- At the end of the latency delay recording 512 points of data.

LHCb upgrade meeting

- At the end of the record the system write one "end of acquisition" bit in the Status register.

- The PC scrutinize the Ctrl register, when the "end of acquisition" is high the PC download data with the USB interface.

Olivier Duarte

LHCb upgrade meeting

February 11th 2011

#### Intensive tests with Frédéric's code

- Rd / Wr register

- Rd / Wr Spy FIFO

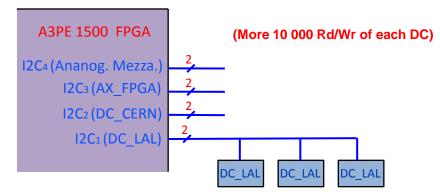

- I2C module (Delay Chip)

(first I2C module to drive DC\_LAL)

#### Tests with "test\_245" by Chafik.

Latency delay

February 11th 2011

- Reset tree

- • •

### Next steps

- AX500 Basic test, before cabling 2 new board.

- RAM test. (Thierry's code)

- Tests trigger generator module for Lemo outputs.

- Intensive test of basic DAQ.

Recording all channels (8) from analog part and read data by USB

**Processing ADC data (dynamic pedestal subtraction)**

- Digital board for Barcelona team.

- Analog board for LAL team ?

Spring / summer

End of

February

- Adaptation Christophe's code or PC computing

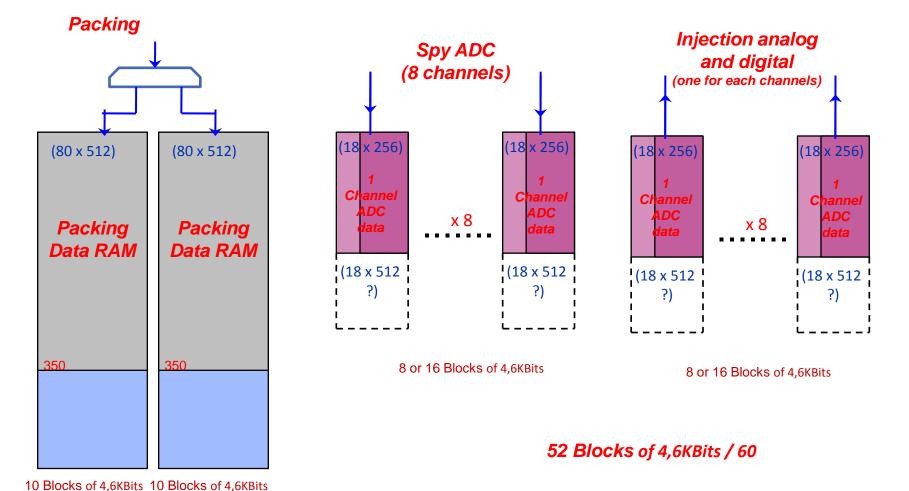

Packing

- A3PE FPGA tests (SS0, SSI, ...)

- Depending accelerator availability !

- Radiation tests

Olivier Duarte

February 11th 2011

Olivier Duarte

December 10th 2010

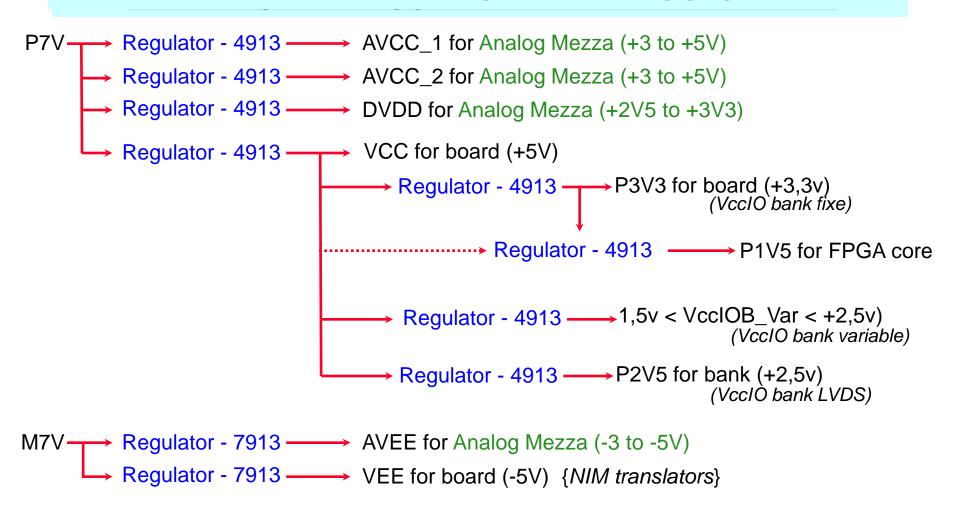

# Tests board power supply

# Lab. Power Supply input (+/- 7V) 10 Radiation tolerance regulators ! !

Olivier Duarte

LHCb upgrade meeting

*Lнсb* гнср

Olivier Duarte

LHCb upgrade meeting