### Tests tools for Analog and Digital parts

- Typical acquisition sequence

- Basic DAQ tests and results

- Tools to test Analog part

- First tests with AX FPGA

- Tools to test A3PE FPGA (SSO & SSI)

- Conclusion : next steps

Caceres Thierry Duarte Olivier

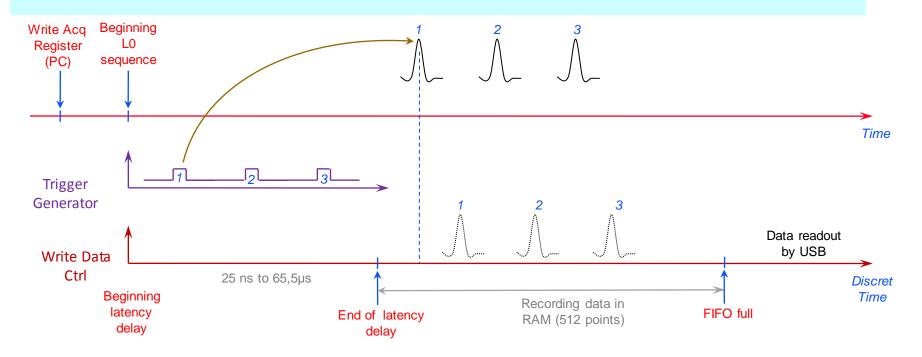

# <u>**Reminder : Typical acquisition sequence</u>**</u>

- PC write start sequence bit of Acquisition (Acq) Register.

- Beginning of L0 sequence.

- Each trigger pulse involve pulse shape.

- At the end of the latency delay recording 512 points of data (Max).

- At the end of the record the system write one "end of acquisition" bit in the Acq\_Register.

- The PC scrutinize the Acq\_Register, when the "end of acquisition" is high the PC download data with the USB interface.

Olivier Duarte / Thierry Caceres

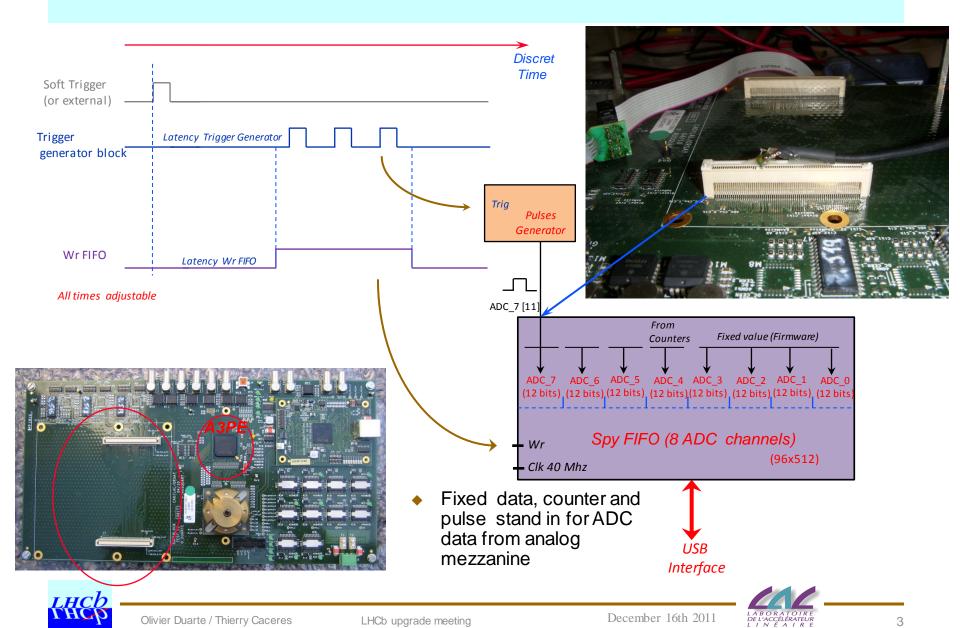

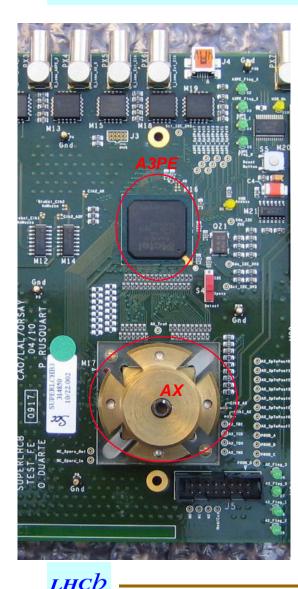

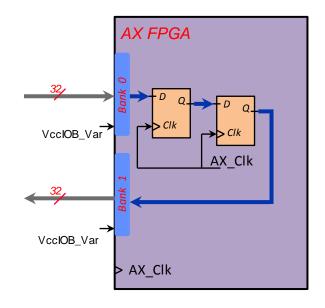

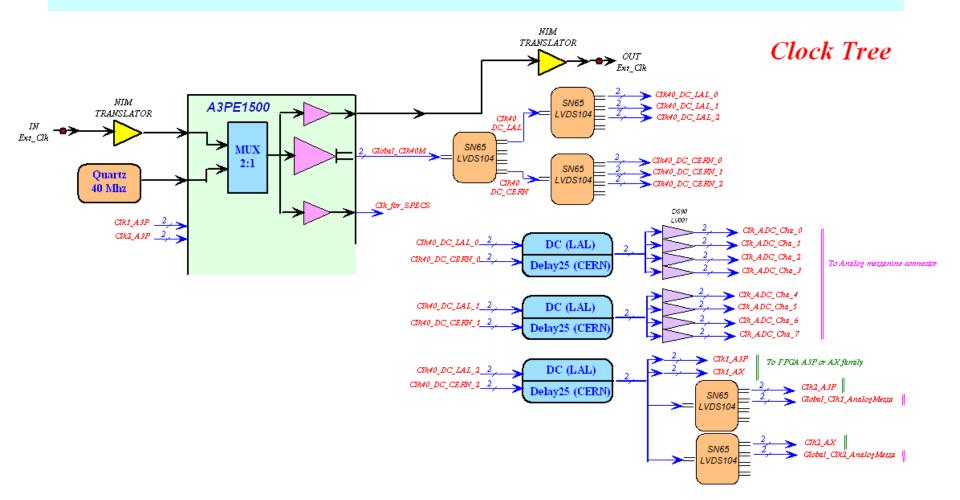

## First tests with AX FPGA

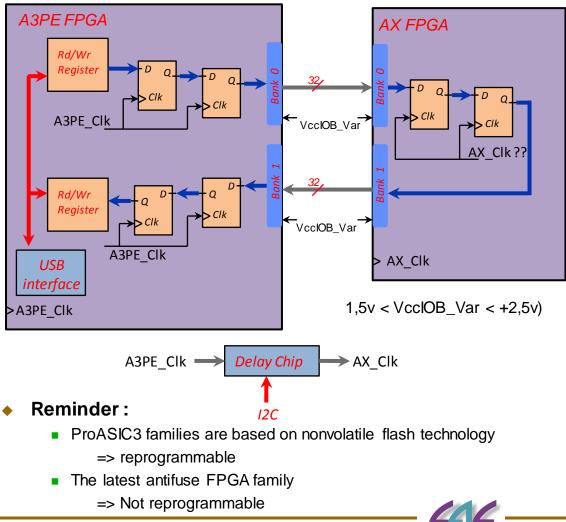

Idea : RAM pattern to test the A3PE IOs functioning by exchanging data between the 2 FPGA (SSO and SSI)

LHCb upgrade meeting

December 16th 2011

Olivier Duarte / Thierry Caceres

LHCb upgrade meeting

December 16th 2011

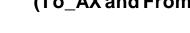

- Sequence: To AX FIFO Rd/Wr by USB

- Start commande

- Loop on to AX\_FIFO until stop command

- **Programmable latency to** <u>capture data</u> from To AX FIFO to FROM AX FIFO

# USB Rd / Wr the FIFO (To\_AX and From\_AX).

Idea: RAM pattern to test the A3PE IOs functioning by exchanging data between the 2 FPGA (SSO and SSI)

- Digital electronic is ok, several adjustment have been done (Tests with Carlos at LAL in November).

- Do you have other needs of firmware to test the analog mezzanine??

- Started Production of third mother digital board (ready in Jannuary)

- Should we considered a 8 channel prototype FEB for the end of 2012 with GBT ?

- Packing is in stand by. Waiting for decision on GBT bandwith.

Olivier Duarte / Thierry Caceres

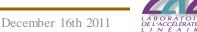

## <u> Reminder : Basic DAQ tests results</u>

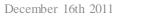

Dump of the Prototype Spy Fifo

## First tests with AX FPGA

$1,5v < VcclOB_Var < +2,5v$ )

#### **Reminder :**

ProASIC3 families are based on not volatile flash technology

=> reprogrammable

AX is the latest antifuse FPGA family

=> Not reprogrammable

• AX programmation with Silicon Scultor

27th November, 2009

Olivier Duarte / Thierry Caceres