# Space engineering, product assurance

**Techniques for Radiation Effects Mitigation in ASICs and FPGAs**

## **Foreword**

This Handbook is one document of the series of ECSS Documents intended to be used as supporting material for ECSS Standards in space projects and applications. ECSS is a cooperative effort of the European Space Agency, national space agencies and European industry associations for the purpose of developing and maintaining common standards.

The material in this Handbook is defined in terms of description and recommendation how to organize and perform the work of **XXXX**....

This handbook has been prepared by the name of group Working Group, reviewed by the ECSS Executive Secretariat and approved by the ECSS Technical Authority.

#### Disclaimer

ECSS does not provide any warranty whatsoever, whether expressed, implied, or statutory, including, but not limited to, any warranty of merchantability or fitness for a particular purpose or any warranty that the contents of the item are error-free. In no respect shall ECSS incur any liability for any damages, including, but not limited to, direct, indirect, special, or consequential damages arising out of, resulting from, or in any way connected to the use of this document, whether or not based upon warranty, business agreement, tort, or otherwise; whether or not injury was sustained by persons or property or otherwise; and whether or not loss was sustained from, or arose out of, the results of, the item, or any services that may be provided by ECSS.

Published by: ESA Requirements and Standards Division

ESTEC, P.O. Box 299, 2200 AG Noordwijk The Netherlands

Copyright: 2009 © by the European Space Agency for the members of ECSS

# **Table of contents**

| 1 Sco   | oe       |                                          | 10 |

|---------|----------|------------------------------------------|----|

| 2 Norr  | native ı | references                               | 11 |

| 3 Defii | nitions  | and acronyms                             | 12 |

| 3.1     | Specif   | ic terms to the present document         | 12 |

| 3.2     | Abbrev   | viated terms                             | 15 |

| 4 Orga  | anisatio | on and purpose                           | 19 |

| 5 Radi  | iation e | environment and integrated circuits      | 20 |

| 5.1     | Radiat   | tion sources                             | 20 |

|         | 5.1.1    | Solar flares                             | 20 |

|         | 5.1.2    | Coronal mass ejections                   | 21 |

|         | 5.1.3    | Solar wind                               | 21 |

|         | 5.1.4    | Galactic cosmic rays                     | 21 |

| 5.2     | Radiat   | tion environment                         | 21 |

|         | 5.2.1    | Van Allen belts                          | 21 |

|         | 5.2.2    | Atmospheric neutrons                     | 23 |

|         | 5.2.3    | Terrestrial radiation sources            | 24 |

| 5.3     | The di   | fferent types of interactions            | 26 |

|         | 5.3.1    | Interaction with photons                 | 26 |

|         | 5.3.2    | Interaction with neutrons                | 26 |

|         | 5.3.3    | Interaction with charged particles       | 27 |

| 5.4     | Radiat   | tion effects                             | 27 |

|         | 5.4.1    | Definitions                              | 27 |

|         | 5.4.2    | Cumulative effects                       | 30 |

|         | 5.4.3    | Single Event Effects (SEEs)              | 30 |

| 6 Cho   | osing a  | design hardening strategy                | 34 |

| 7 Tech  | nnology  | y selection and process level mitigation | 35 |

| 7.1     | Scope    |                                          | 35 |

| 7.2     | Table    | of effects vs mitigation techniques      | 36 |

| 7.3    | Mitigati | on techniques                                                              | 36 |

|--------|----------|----------------------------------------------------------------------------|----|

|        | 7.3.1    | Epitaxial layers                                                           | 36 |

|        | 7.3.2    | Silicon On Insulator                                                       | 37 |

|        | 7.3.3    | Triple wells                                                               | 41 |

|        | 7.3.4    | Buried layers                                                              | 43 |

|        | 7.3.5    | Dry thermal oxidation                                                      | 44 |

|        | 7.3.6    | Implantation into oxides                                                   | 46 |

| 7.4    | Techno   | ology scaling and radiation effects                                        | 47 |

|        | 7.4.1    | Effects of technology scaling on TID sensitivity                           | 48 |

|        | 7.4.2    | Effects of technology scaling on SEE sensitivity                           | 48 |

| 8 Lavo | out      |                                                                            | 50 |

| 8.1    |          |                                                                            |    |

| 8.2    | •        | of effects vs mitigation techniques                                        |    |

| 8.3    |          | on techniques                                                              |    |

|        | 8.3.1    | Enclosed Layout Transistor                                                 |    |

|        | 8.3.2    | Contacts and guard rings                                                   | 53 |

| 8.4    | Radiati  | on-hardened libraries                                                      | 56 |

|        | 8.4.1    | ESA Design Against Radiation Effects library                               | 57 |

|        | 8.4.2    | CERN 0.24 µm radiation hardened library                                    | 58 |

|        | 8.4.3    | BAE 0.15 µm radiation hardened library                                     | 58 |

|        | 8.4.4    | Ramon Chips 0.18 µm and 0.13 µm radiation hardened libraries               | 58 |

|        | 8.4.5    | Aeroflex 600, 250, 130 and 90 nm radiation hardened libraries              | 59 |

|        | 8.4.6    | Atmel MH1RT 0.35 µm and ATC18RHA 0.18 µm CMOS radiation hardened libraries | 59 |

|        | 8.4.7    | ATK 0.35 μm radiation hardened cell library                                | 60 |

|        | 8.4.8    | ST Microelectronics radiation hardened library                             | 60 |

| 9 Anal | loque ci | rcuits                                                                     | 61 |

| 9.1    | •        |                                                                            |    |

| 9.2    | -        | of effects vs mitigation techniques                                        |    |

| 9.3    |          | on techniques                                                              |    |

|        | 9.3.1    | Node Separation and Interdigitation                                        | 62 |

|        | 9.3.2    | Analog Redundancy (Averaging)                                              | 66 |

|        | 9.3.3    | Resistive Decoupling                                                       | 68 |

|        | 9.3.4    | Filtering                                                                  | 71 |

|        | 9.3.5    | Modifications in Bandwidth, Gain, Operating Speed, and Current Drive       |    |

|        | 9.3.6    | Reduction of Window of Vulnerability                                       | 75 |

|         | 9.3.7      | Reduction of High Impedance Nodes              | 79  |

|---------|------------|------------------------------------------------|-----|

|         | 9.3.8      | Differential Design                            | 81  |

|         | 9.3.9      | Dual Path Hardening                            | 84  |

| 10 Digi | ital circ  | uits                                           | 89  |

| 10.1    | Scope.     |                                                | 89  |

| 10.2    | Table o    | of effects vs mitigation techniques            | 90  |

| 10.3    | Mitigation | on techniques                                  | 90  |

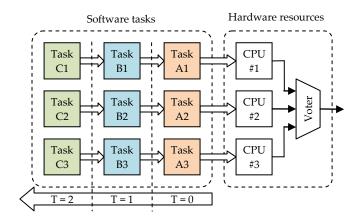

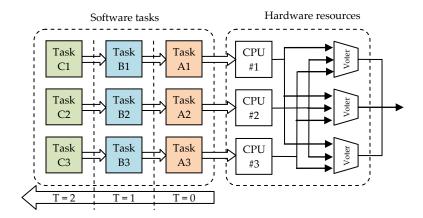

|         | 10.3.1     | Spatial redundancy                             | 90  |

|         | 10.3.2     | Temporal redundancy                            | 94  |

|         | 10.3.3     | Fail-Safe Finite State Machines                | 97  |

| 10.4    | Vendor     | solutions                                      | 98  |

|         | 10.4.1     | Radhard circuit manufacturers                  | 98  |

|         | 10.4.2     | Radhard processors                             | 98  |

|         | 10.4.3     | Radhard computers                              | 99  |

| 11 Mix  | ed-sign    | al circuits                                    | 101 |

|         | _          |                                                |     |

| 11.2    | Table o    | of effects vs mitigation techniques            | 101 |

|         |            | on techniques                                  |     |

|         | 11.3.1     | Triple Modular Redundancy                      | 101 |

| 12 Fiel | d Progr    | rammable Gate Arrays                           | 104 |

| 12.1    | Scope.     |                                                | 104 |

| 12.2    | Table o    | of effects vs mitigation techniques            | 106 |

| 12.3    | Mitigation | on techniques                                  | 106 |

|         | 12.3.1     | Local Triple Modular Redundancy                | 106 |

|         | 12.3.2     | Global Triple Modular Redundancy               | 108 |

|         | 12.3.3     | Large grain Triple Modular Redundancy          | 111 |

|         | 12.3.4     | Embedded user memory TMR                       | 113 |

|         | 12.3.5     | Voter insertion                                | 114 |

|         | 12.3.6     | Reliability-Oriented place and Route Algorithm | 117 |

|         | 12.3.7     | Temporal redundancy                            | 119 |

|         | 12.3.8     | Embedded processor redundancy                  | 121 |

|         | 12.3.9     | Scrubbing                                      | 122 |

| 12.4    | Vendor     | solutions                                      | 126 |

|         | 12.4.1     | Microsemi's RTAX-S/SL antifuse-based FPGA      | 126 |

|         | 12.4.2     | Aeroflex's UT6325 antifuse-based FPGA          | 126 |

|         | 12.4.3     | Microsemi's ProASIC3/E flash-based FPGA        | 127 |

|        | 12.4.4     | Atmel AT40KEL SRAM-based FPGA                           | 128 |

|--------|------------|---------------------------------------------------------|-----|

|        | 12.4.5     | Atmel ATF280F SRAM-based FPGA                           | 129 |

|        | 12.4.6     | Xilinx Virtex family SRAM-based FPGA (commercial grade) | 129 |

|        | 12.4.7     | Xilinx Virtex-5Q SRAM-based FPGA (defense grade)        | 130 |

|        | 12.4.8     | Xilinx Virtex-5QV SRAM-based FPGA (space grade)         | 131 |

| 12.5   | Device     | comparison for space applications                       | 132 |

| 13 Em  | bedded     | memories                                                | 134 |

| 13.1   | Scope.     |                                                         | 134 |

| 13.2   | Table o    | f effects vs mitigation techniques                      | 135 |

| 13.3   | Mitigation | on techniques                                           | 135 |

|        | 13.3.1     | Resistive hardening                                     | 135 |

|        | 13.3.2     | Capacitive hardening                                    | 137 |

|        | 13.3.3     | IBM hardened memory cell                                | 139 |

|        | 13.3.4     | HIT hardened memory cell                                | 141 |

|        | 13.3.5     | DICE hardened memory cell                               | 142 |

|        | 13.3.6     | NASA-Whitaker hardened memory cell                      | 144 |

|        | 13.3.7     | NASA-Liu hardened memory cell                           | 146 |

|        | 13.3.8     | Scrambling                                              | 147 |

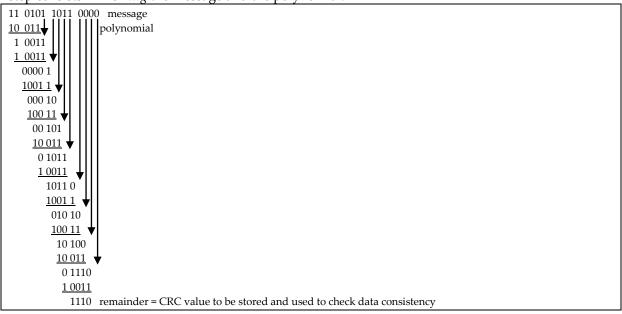

|        | 13.3.9     | Error Correcting Codes                                  | 149 |

| 13.4   | Compa      | rison between hardened memory cells                     | 151 |

| 14 Em  | bedded     | software                                                | 152 |

| 14.1   | Scope.     |                                                         | 152 |

| 14.2   | Table o    | f effects vs mitigation techniques                      | 153 |

| 14.3   | Mitigation | on techniques                                           | 153 |

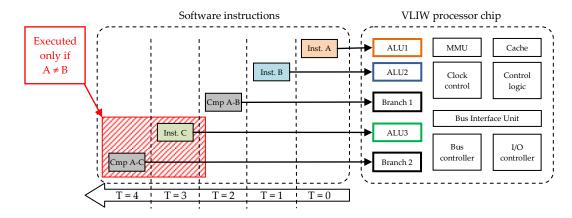

|        | 14.3.1     | Redundancy at instruction level                         | 153 |

|        | 14.3.2     | Redundancy at task level                                | 159 |

|        | 14.3.3     | Redundancy at application level                         | 163 |

| 15 Sys | tem arc    | hitecture                                               | 166 |

| 15.1   | Scope.     |                                                         | 166 |

| 15.2   | Table o    | f effects vs mitigation techniques                      | 167 |

| 15.3   | Mitigation | on techniques                                           | 167 |

|        | 15.3.1     | Shielding                                               | 167 |

|        | 15.3.2     | Watchdog timers                                         | 169 |

|        | 15.3.3     | Latching current limiters                               | 171 |

|        | 15.3.4     | Duplex architectures                                    | 173 |

|        | 15.3.5     | Triple Modular Redundancy                               | 177 |

|        |            |                                                         |     |

|         | 15.3.6    | Error Correcting Codes                         | 180 |

|---------|-----------|------------------------------------------------|-----|

| 15.4    | Comme     | rcial solutions                                | 187 |

|         | 15.4.1    | Space Micro Proton platform                    | 187 |

|         | 15.4.2    | Maxwell SCS750                                 | 188 |

| 15.5    | Example   | es of adopted architectures onboard satellites | 189 |

|         | 15.5.1    | Architecture for the MYRIADE satellite         | 189 |

|         | 15.5.2    | Architecture for the REIMEI (INDEX) satellite  | 190 |

|         | 15.5.3    | Architecture for the CALIPSO satellite         | 190 |

| 16 Vali | dation r  | nethods                                        | 191 |

| 16.1    | Introduc  | etion                                          | 191 |

| 16.2    | Real-life | e tests                                        | 191 |

| 16.3    | Ground    | accelerated tests                              | 192 |

|         | 16.3.1    | Standards and specifications                   | 192 |

|         | 16.3.2    | Test methodologies                             | 193 |

|         | 16.3.3    | Test facilities                                | 194 |

|         | 16.3.4    | Practical constraints                          | 199 |

|         | 16.3.5    | DUT preparation                                | 200 |

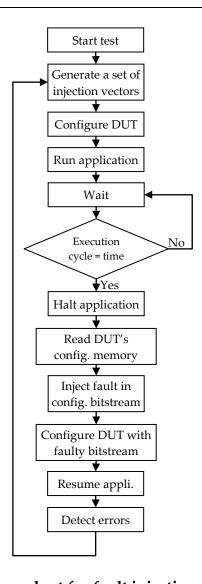

| 16.4    | Fault inj | ection                                         | 200 |

|         | 16.4.1    | Fault injection at transistor level            | 201 |

|         | 16.4.2    | Fault injection at gate level                  | 201 |

|         | 16.4.3    | Fault injection at device level                | 202 |

|         | 16.4.4    | Fault injection at system level                | 206 |

| 16.5    | Analytic  | al methods                                     | 206 |

| Annov   | A Dofor   | rangas                                         | 200 |

# Acknowledgements

This Handbook has been authored and agreed upon by the following persons:

- M. Alles, University of Vanderbilt (process and layout level)

- D. Loveless, University of Vanderbilt (analogue & mixed-signal circuits)

- M. Nicolaidis, TIMA laboratory (digital circuits)

- F. L. Kastensmidt, Universidade Federal do Rio Grande do Sul (digital circuits & FPGAs)

- M. Violante, Politecnico di Torino (embedded software)

- M. Pignol, CNES (system architecture)

The ESA-HB-XX-XX-rev.6 has been prepared based on volunteer contributions of the authors.

# Introduction

Integrated circuits devoted to space applications require special care during their design, manufacturing and qualification processes as they will be operating in a harsh radiative environment composed of various energetic particles. The diversity in nature and energy of particles present in this environment is a threat for electronic equipment as they can provoke different type of undesired effects. The consequences can either be long term effects due to the accumulation of charges, deposited in the integrated circuits by impinging particles, and leading to a partial or full lose of functionality or they can be the consequence of a unique particle. In this last case the consequences can be different depending on several parameters such as the particle's energy and nature, the circuit's technology and type. They can provoke erroneous results, functionality interruption and even device destruction.

Drastic device shrinking, very low operating voltages, increasing complexities and high clock frequencies make circuits increasingly sensitive to various kinds of failures. Due to these evolutions, radiation sensitivity, considered in the past as a concern only for space applications, became a major source of system failures of electronic products even for those operating at ground level. Consequently, mitigation of radiation effects is becoming mandatory for an increasing number of application domains, including networking, servers, avionics, medical, and automotive electronics. To tackle this problem, integrated circuits and system designers may benefit from several decades of knowledge related R&D from the military and space domains. However, as ground level and aeronautic applications concern high-volume production they are not subject to the same constraints as space applications.

Significant efforts have been made during the past years to cope with the undesired effects induced by radiation. A wide scope of methodologies and tools adapted to address these effects for the different phases of the microelectronic development flow: manufacturing process, design, hardware, software.

The goal of this handbook is to present the techniques and methods devoted to mitigate radiation induced effects on analogue, mixed-signal and digital ASICs and FPGAs.

# 1 Scope

This handbook describes the up-to-date known validation methods for the mitigation of radiation effects which are applicable to microelectronic components and systems. The presentation of available mitigation methods is organized according to development flow in a bottom-up approach: manufacturing process, layout, schematic, digital design, architecture, embedded software and system architecture.

# Normative references

The following normative documents contain provisions which, through references in this text, constitute provisions of this ECSS Standard. For dated references, subsequent amendments to, or revision of any of these publications do not apply. However, parties to agreements based on this ECSS Standard are encouraged to investigate the possibility of applying the more recent editions of the normative documents indicated below. For undated references, the latest edition of the publication referred to applies.

AO/1-3240/97/NL/TM Circumventing radiation effects by logic design: Cookbook, July 1999. FPGA-003-01 Functional Triple Modular Redundancy (FTMR), Gaisler Research, December 2002 NASA ASIC NASA ASIC Guide – Radiation Hardening SPRINGER 2007 Radiation Effects on Embbeded Systems, Raoul Velazco, Pascal Fouillat, Ricardo Reis, 2007, Springer, ISBN: 978-1-4020-5645-1 ECSS-E-HB-10-12A Calculation of radiation and its Effects and Margin Policy Handbook. ECSS-Q-ST-60-02C Space Product Assurance: ASIC and FPGA Development. Electrical, Electronic and Electromechanical ECSS-Q-ST-60C

(EEE) Components.

# Definitions and acronyms

# 3.1 Specific terms to the present document

#### Levels of abstraction

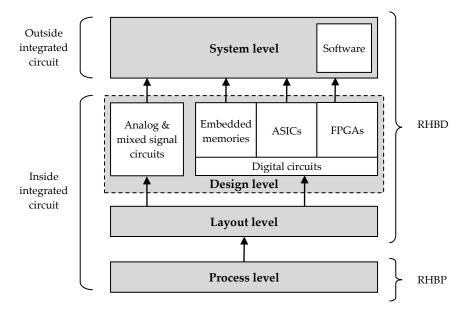

Building robust systems for space applications requires a lot of stages and techniques aiming at mitigating radiation effects which exist at all levels of the hierarchy from the fabrication process, the circuit design (layout) to the system architecture and the software levels.

Mitigation techniques presented in this handbook are organized according to the following identified levels of abstraction:

- <u>System level</u>: these techniques apply at component level (e.g. microprocessor redundancy), unit level or embedded software level (e.g. computer redundancy).

- <u>Architecture</u>: techniques devoted to this level are most often specific to the circuit's nature (digital, analogue or mixed signal) and/or to the circuit's family (ASICs, FPGAs or embedded memory). Moreover, a majority of them belong to main approaches such as redundancy (hardware or temporal) or Error Detection And Correction (EDAC).

- <u>Layout</u>: techniques aiming at optimizing transistor's layout and placement in order to reduce sensitivity to radiation of the final circuit.

- <u>Process</u>: techniques concerning the manufacturing processes, also known as Radiation Hardening By Process. These approaches generally concern modifications of doping profiles in devices and substrates, optimization of deposition processes for insulators and use of specific materials.

Figure 3-1: Levels of abstraction

#### Radiation Hardening By Process / Design

Radiation-Hardening-By-Process (RHBP) concerns modifications at fabrication processes in order to reduce the impact of radiation on integrated circuits. This goal can be achieved by several means such as modifications of doping profiles in devices and substrates, optimization of deposition processes for insulators and use of specific materials. RHBP will mainly address two main effects: Total Ionizing Dose (TID) and Single Event Effect (SEE). Details about the considered effects can be found in chapter 5.4.2 and 5.4.3.

In contrast, Radiation Hardening By Design (RHBD) refers to special circuits design techniques that can be applied at layout level, at architectural level or at system level. RHBD approaches exist both for TID and SEE mitigation. The use of such techniques usually induces a penalty including area, power consumption, frequency, costs or procurement delays.

#### Critical charge

The critical charge, noted Q<sub>crit</sub>, is the minimum charge a particle must deposit in an integrated circuit's node to invert its state.

#### Fault masking

As described in chapter 5.4.3, Single Event Effects are the consequence of the current pulse resulting by the charge deposited by a single particule inpinging a sensitive area of the circuit. The occurrence of an Single Event Transient (SET) in a circuit does not necessarily end up with an error. Indeed, there are three factors that determine whether an SET will propagate and result in an error:

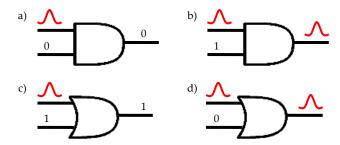

• Logical masking occurs, for example, when an SET provoked by a particle is not propagated to an output due the value of the inputs. Figure 1-2 illustrates the logical masking phenomenon for an AND and an OR gate. Whenever an input of the AND gate is "0" it will naturally reject the transient (Figure 1-2 (a)) and when one input is set to "1" the SET will be able to propagate

(Figure 1-2 (b)). For the OR gate, the SET will propagate with an input set to "1" (Figure 1-2 (c)) but will be masked when the input is "0" (Figure 1-2 (d)).

Figure 3-2: Logical masking of a transient in two logical gates

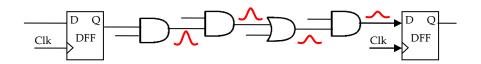

• Electrical masking occurs, for example, if the SET is attenuated as it propagates along a path until it does not affect anymore the result of the circuit. Such a phenomenon is illustrated in Figure 1-3 where an SET is attenuated by each gate. When it reaches the flip-flop, the pulse's amplitude is not sufficient to create an error.

Figure 3-3: Electrical masking along a path in combinational logic

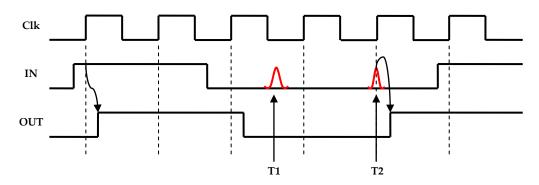

• Temporal masking occurs, for example, if an SET reaches a memory element at an instant other than the clocking window. Figure 1-4 depicts an example of temporal masking in a flip-flop at instant T1 because the SET on its input is not concurrent with a clock rise edge. At instant T2 the SET occurs as the same time than the clock pulse and will thus modify the content of the memory cell. The resulting error may propagate to the circuit output. In this case the SET transforms itself into an Single Event Upset (SEU) also called bit-flip or soft error.

Figure 3-4: Temporal masking

Consequently, these three factors present a natural barrier to soft errors in integrated circuits.

# 3.2 Abbreviated terms

For the purpose of this document, the abbreviated terms from ECSS-S-ST-00-01 and the following apply:

| Abbreviation  | Meaning                                                |

|---------------|--------------------------------------------------------|

| μP            | Microprocessor                                         |

| ADC           | Analogue-to-Digital Converter                          |

| ASET          | Analogue Single-Event Transient                        |

| ASIC          | Application Specific Integrated Circuit                |

| BICS          | Built-In Current Sensors                               |

| Bi-MR         | Bi-Modular Redundancy                                  |

| BJT           | Bipolar Junction Transistor                            |

| BOX           | Buried OXide                                           |

| CED           | Concurrent Error Detection                             |

| CEU           | Code Emulated Upset                                    |

| CFCSS         | Control Flow Checking by Software Signatures           |

| CLB           | Configuration Logic Block                              |

| CME           | Coronal Mass Ejection                                  |

| CMOS          | Complementary Metal Oxide Semiconductor                |

| COTS          | Commercial Off The Shelf                               |

| CRC           | Cyclic Redundancy Check                                |

| CWSP          | Code Word State Preserving                             |

| DAC           | Digital-to-Analogue Converter                          |

| DARE          | Design Against Radiation Effects                       |

| DCM           | Digital Clock Manager                                  |

| DFF           | D-Flip-Flop                                            |

| DMS           | Defense Meteorological Satellite                       |

| DMT           | "Duplex Multiplexé dans le Temps", i.e. duplex in time |

| DROM          | Demultiplexer-ROuter-Multiplexer                       |

| DSP           | Digital Signal Processor                               |

| DUT           | Device Under Test                                      |

| DWC           | Duplication With Comparison                            |

| ECC           | Error-Correcting Codes                                 |

| EDAC          | Error Detection And Correction                         |

| EDDI          | Error Detection by Duplicated Instructions             |

| ESA           | European Space Agency                                  |

| <b>ESCIES</b> | European Space Components Information Exchange         |

System

**ESD** ElectroStatic Discharge

eV Electron-Volt

**FEC** Forward Error Correction

**FF** Flip-flop

FIR Finite Impulse Response

**FIT** Failure In Time

**FPGA** Field Programmable Gate Array

GCC GNU Compiler Collection

GCR Galactic Cosmic Rays

GEO GEOstationary

GNU GNU's Not Unix

**GPS** Global Positioning Satellite

**HBFT** Hypervisor-Based Fault Tolerance

**HBT** Heterojunction Bipolar Transistor

HDL Hardware Description language

**HWICAP** HardWare Internal Configuration Access Port

HW HardwareI/O Input/Output

IC Integrated Circuit

ILO Injection-Locked Oscillator

IOB Input/Output Block

ISS International Space Station

LCL Latching Current Limiter

**LEO** Low Earth Orbit

**LET** Linear Energy Transfer

LET<sub>th</sub> Linear Energy Transfer threshold

LHC Large Hadron Collider

LNA Low-Noise Amplifier

LOCOS LOCal Oxidation of Silicon

LPF Low Pass Filter

LUT Look-Up Table

LVDS Low-Voltage Differential Signaling

**LWS-SET** Living With a Star – Space Environment Testbed

MAJ MAJority voter

MBU Multiple Bit Upset

MCU Multiple Cell Upset

MEO Medium Earth Orbit

MMU Memory Management UnitMOS Metal Oxyde Semiconductor

MOSFET Metal-Oxide Semiconductor Field-Effect Transistor

MPTB Microelectronics and Photonics TestBed

MTBF Mean Time Between Failures

MUX Multiplexer

NMOS N-channel Metal-Oxide Semiconductor

NPOESS National Polar-orbiting Operational Environmental

Satellite System

OA Operational Amplifier

PCI Peripheral Component Interconnect

PLL Phase-Locked Loop

PMCD Phase-Matched Clock Divider

**PMOS** P-channel Metal-Oxide Semiconductor

POA Post Oxidation Anneal

**POR** Power-On Reset

**PUC** Processing Unit Core

RAID Redundant Array of Independent Disks

**RAM** Random Access Memory

RHBD Radiation Hardening By Design

RHBP Radiation Hardening By Process

**RoRa** Reliability Oriented Place and Route

**RS** Reed-Salomon

RTL Register Transfer Level

SAA South Atlantic Anomaly

SBIRS Space Based InfraRed System

SCSI Small Computer System Interface

SE Soft Error

**SEB** Single Event Burnout

**SEC-DED** Single Error Correction-Double Error Detection

**SEE** Single Event Effect

**SEFI** Single Event Functional Interrupt

**SEGR** Single Event Gate Rupture

**SEL** Single Event Latchup

**SER** Soft Error Rate

SerDes Serializer/Deserializer

**SET** Single Event Transient

SEU Single Event Upset

SiGe Silicon Germanium

SNR Signal-to-Noise Ratio

**SoC** System on Chip

SOI Silicon On InsulatorSOS Silicon On SapphireSPF Single Point Failure

**SPICE** Simulation Program with Integrated Circuit Emphasis

United Microelectronics Corporation

STI Shallow Trench Isolation

**STRV** Space Technology Research Vehicle

SW Software

**UMC**

TID Total Ionizing Dose

TMR Triple Modular Redundancy

TNID Total Non Ionizing Dose

TPA Two-Photon Absorption

**USAF** United States Air Force

VCDL Voltage-Controller Delay Line

VCO Voltage Controlled Oscillator

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuits

WL Write Line

# Organisation and purpose

This document aims at describing state-of-the-art techniques used to mitigate radiation effects in ASICs and FPGAs. Depending on the type of circuit and the nature of the radiation effect, the mitigation technique can be applied at different abstraction levels, such as manufacturing process, layout, design, software and architecture levels. This handbook is organized so that the reader can easily access mitigation techniques suitable to both his profile and the chosen level of abstraction. The reader can refers to Chapter 6 to get guidelines about the choice of the mitigation techniques suitable for a considered project.

This handbook shall serve as a comprehensive reference which will enable microelectronics engineers to choose and check the adequacy of methodologies for radiation hardening, and to improve design techniques where necessary. It describes the available technology choices and mitigation techniques for digital and analogue integrated circuits including but not limited to ASICs and FPGAs.

Everyone who is concerned with reliability of applications devoted to operate in radiation environment, i.e. project managers, semi-conductor manufacturing engineers, hardware and software engineers, quality assurance personnel, should read this handbook.

# Radiation environment and integrated circuits

Failures induced by radiation, which appeared first in satellite equipments, have become one of the most challenging issues for modern electronic systems, even for ground-level applications. Many efforts have been spent in the last decades to measure, model, and mitigate radiation effects, applying numerous different techniques approaching the problem at various abstraction levels.

This chapter is intended to give the reader a general overview of radiation and its potential effects on integrated circuits. Firstly, existing radiation sources are exposed. The Earth radiation environment (and its neighborhood) is then described followed by an explanation concerning the different types of interaction between particles and matter. Finally, radiation effects on integrated devices are discussed.

#### 5.1 Radiation sources

Radiation sources are multiple: some take their origin in the Sun (e.g. solar flares, coronal mass ejection and solar wind) and others come from outside the solar system [1].

#### 5.1.1 Solar flares

A solar flare is a sudden and rapid release of magnetic energy that has built up in the solar atmosphere (Figure 5-1). It can last from a few seconds up to one hour. The first solar flare was reported in astronomical literature by Richard C. Carrington and Richard Hodgson on September 1, 1859. During this phenomena radiation is emitted through the entire electromagnetic spectrum, from radio waves to X-rays and gamma rays. However, protons and heavy ions should be considered first when analyzing solar flare impacts on integrated circuit reliability.

Figure 5-1 : A solar flare

#### 5.1.2 Coronal mass ejections

A Coronal Mass Ejection (CME) is a huge plasma bubble ejected by the Sun (Figure 5-2) over the course of several hours [2]. Coronal events where observed for the first time in 1971 with the use of a coronagraph which produces an artificial eclipse of the Sun by placing an "occulting disk" over the Sun. In this case considered particles are high-energy protons.

Figure 5-2: Coronal mass ejections

#### 5.1.3 Solar wind

Coronal mass ejections cause shock waves in the thin plasma of the heliosphere, launching electromagnetic waves and accelerating particles (mostly protons and electrons) to form showers of ionizing radiation that precede the CME. The solar wind streams off of the Sun in all directions at an average speed of approximately 400 km/s. The source of the solar wind is the Sun's corona where the temperature is so high that electrons have sufficient energy to escape the Sun's gravity. As a reaction, protons and heavy ions are ejected in order to maintain the zero electrical charge of the star. The solar wind is not uniform in terms of speed and charge intensity.

## 5.1.4 Galactic cosmic rays

Galactic cosmic rays (GCRs) are high-energy charged particles coming from outside the solar system and generally from within the Milky Way galaxy [3]. The highest cosmic ray energy measured is over 1020 eV. They are composed of about 89% of hydrogen nuclei (protons), 10% of Helium nuclei, the remaining 1% being fully ionized nuclei of heavier elements and electrons.

#### 5.2 Radiation environment

#### 5.2.1 Van Allen belts

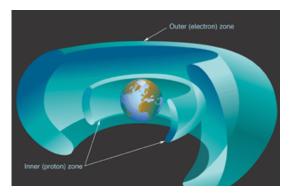

Van Allen Belts are two regions of the magnetosphere, shown in Figure 5-3, where high-energy particles, mainly protons and electrons, are trapped by the Earth's magnetic field. James Van Allen named them after their discovery in 1958.

The inner belt extends from 100 km and 10,000 km above the Earth's surface and is mainly composed of high-energy protons (up to several 100 MeV) and electrons issued from solar wind protons or generated by galactic cosmic ion collisions with atmosphere. Electrons in the range of hundreds of keV are also present in the inner belts.

The outer belt spreads from 13,000 km to 65,000 km of the Earth's surface. Trapped particles are mainly high-energy electrons (0.1 to 10 MeV).

The South Atlantic Anomaly (SAA) is a particularity to be noted as it is a region of very high-energy particle flux about 250 km and higher above the Atlantic Ocean and the coast of Brazil. It comes from several reasons:

- The symmetry of the Van Allen belts with the Earth's magnetic axis.

- The 11° tilt between the Earth's magnetic axis and the Earth's rotation axis.

- The 500 km offset of the Earth's magnetic axis toward Pacific Ocean geographic N-S.

The particle flux is so high in the region that detectors on satellites are often shut off or placed in "safe" mode while passing through.

Figure 5-3: Van Allen radiation belts

#### 5.2.2 Atmospheric neutrons

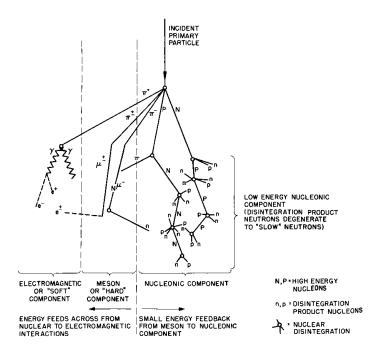

Figure 5-4: Schematic Diagram of Cosmic Ray Shower

High-energetic cosmic ray particles (mostly protons) can create neutrons, secondary protons, muons and neutrinos by spallation<sup>1</sup> reaction on atmospheric nuclei (Figure 5-4). As most particles are easily stopped, most of the error contribution is arising from the neutron "shower".

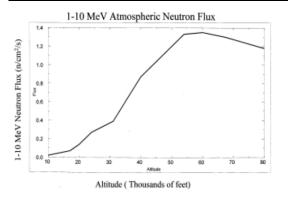

The neutron peak flux, 3,600 to 10,000 particles/cm².hour (E > 10 MeV), can be found at an altitude of 18 km (60,000 feet). At 9km (30,000 feet) the neutron flux is equal to about 1/3 of the peak flux. At ground level the observed flux is about 1/400 the peak flux. Note that these figures may change depending on the Sun activity. Indeed, when this activity is high the solar wind increases, which results in strengthening the Earth's magnetic field and, thus repelling further away cosmic rays.

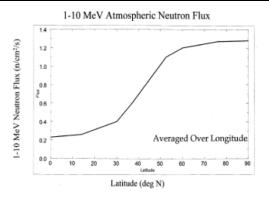

The neutron population in the atmosphere varies with both altitude and latitude as shown in Figure 5-5 and Figure 5-6. The latitude variation of the 1-10 MeV atmospheric neutrons is based on measurements made aboard aircrafts at an altitude of 35,000 feet.

23

<sup>&</sup>lt;sup>1</sup> In nuclear physics, spallation is the process in which a heavy nucleus emits nucleons as a result of being hit by a high-energy particle, thus reducing its atomic weight.

Figure 5-5: Neutron flux vs. altitude

Figure 5-6: Neutron flux vs. latitude

Neutrons cannot cause errors in integrated circuits through direct ionization, as it is the case with protons and heavy ions, but they can generate errors through nuclear reactions with silicon resulting in recoils which may deposit enough charge in a small volume to trigger an event.

#### 5.2.3 Terrestrial radiation sources

Radioactive materials are found throughout nature: in the soil, water, and vegetation. Low levels of uranium, thorium and their decay products can be found everywhere. These materials are either ingested with food and water, or inhaled like the radon. Natural deposited dose is linked to several parameters such as geographic location, presence of uranium mine, etc.

The major isotopes of concern for terrestrial radiations are uranium and the decay products of uranium, such as thorium, radium, and radon.

Different sources of alpha impurities are present in micro-electronic devices. These sources are mainly wafer process, packaging impurities, chip materials and solder. These alpha emitters are in the low energy spectra (< 5 MeV) and are locally highly ionizing and they may disrupt the functional behavior of the component.

Table 5-1 provides the relevant primary and secondary radiation as a function of radiation effects and mission types.

Table 5-1: Relevant primary and secondary radiations as a function of radiation effects and mission types

| as a function of radiation effects and mission types |                      |                                                                     |                                                     |  |  |  |  |  |

|------------------------------------------------------|----------------------|---------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|

| Radiation effects                                    | Mission type         | Important primary radiations                                        | Important secondary radiation                       |  |  |  |  |  |

|                                                      | LEO                  | Trapped protons and electrons Solar protons                         | X-rays from electrons                               |  |  |  |  |  |

|                                                      | High MEO             | Trapped electrons Solar protons                                     | X-rays from electrons                               |  |  |  |  |  |

|                                                      | Low MEO              | Trapped protons and electrons Solar protons                         | X-rays from electrons                               |  |  |  |  |  |

| Total ionizing dose                                  | GEO                  | Low energy trapped protons Trapped electrons Solar protons          | X-rays from electrons                               |  |  |  |  |  |

|                                                      | Interplanetary space | Cosmic rays Solar energetic particles Other planetary trapped-belts | X-rays from electrons                               |  |  |  |  |  |

|                                                      | Planetary<br>lander  | Solar energetic particles                                           | Secondary protons & neutrons                        |  |  |  |  |  |

|                                                      | LEO                  | Trapped protons Trapped electrons Solar protons                     | Secondary neutrons                                  |  |  |  |  |  |

|                                                      | MEO                  | Trapped protons (low MEO) Trapped electrons Solar protons           | Secondary neutrons                                  |  |  |  |  |  |

| Displacement damage                                  | GEO                  | Trapped protons (low energy) Trapped electrons Solar protons        | Secondary neutrons                                  |  |  |  |  |  |

|                                                      | Interplanetary space | Cosmic rays Solar energetic particles Other planetary trapped-belts | Secondary neutrons                                  |  |  |  |  |  |

|                                                      | Planetary<br>lander  | Cosmic rays<br>Solar energetic particles                            | Secondary protons & neutrons                        |  |  |  |  |  |

|                                                      | LEO                  | Trapped protons Solar energetic particles Cosmic rays               | Secondary neutrons                                  |  |  |  |  |  |

|                                                      | MEO                  | Trapped protons Solar energetic particles Cosmic rays               | Secondary neutrons                                  |  |  |  |  |  |

| Single Event Effects                                 | GEO                  | Solar energetic particles<br>Cosmic rays                            | Secondary neutrons                                  |  |  |  |  |  |

|                                                      | Interplanetary space | Cosmic rays Solar energetic particles Other planetary trapped-belts | Secondary neutrons                                  |  |  |  |  |  |

|                                                      | Planetary<br>lander  | Cosmic rays<br>Solar energetic particles                            | Secondary protons & heavier ions Secondary neutrons |  |  |  |  |  |

## 5.3 The different types of interactions

Natural environment interacts in many different ways with electronic devices depending on the radiation type, the particle type and its energy. In the following section, are described the different interactions with material. A more detailed description can be found in [4].

### 5.3.1 Interaction with photons

Photons are electromagnetic radiation with zero mass, zero charge, and a velocity that is always c, the speed of light. Because they are electrically neutral, they do not steadily loose energy via *Coulombic interactions*, also called ionization, with atomic electrons as do charged particles. Instead, they travel a considerable distance before undergoing a more "catastrophic" interaction. Among all the photon interactions, only those leading to partial or total transfer of the photon energy to electron energy are detailed in this document. Thus, three interactions of interest are presented:

- <u>Photoelectric Effect</u>: In the *photoelectric absorption* process, a photon undergoes an interaction with an absorber atom in which the photon completely disappears. In its place, an energetic *photoelectron* is ejected from one of the bound shells of the atom. The interaction leaves an ionized absorber atom with a vacancy in one of its bound shells. This vacancy is quickly filled through the capture of a free electron from the medium and/or rearrangement of electrons from other shells of the atom. The photoelectric process is the predominant mode of interaction for photons of relatively low energy (below a few tens of keV).

- <u>Compton Scattering</u>: The *Compton scattering* interaction takes place between the incident photon and an electron in the absorbing material. It is most often the predominant interaction mechanism for photons having an energy between tens keV and several MeV. The photon transfers a portion of its energy to the electron, which is then known as a recoil electron, or a *Compton electron*.

- <u>Pair Production</u>: If an energetic photon enters matter and has an energy in excess of 1.022 MeV, it may interact by a process called *pair production*. In this mechanism of energy transfer, the photon when passing near the nucleus of an atom, is subjected to strong field effects from the nucleus and may disappear as a photon and reappear as a positive and negative electron pair. Pair production becomes more likely with increasing photon energy.

#### 5.3.2 Interaction with neutrons

As a neutron has no charge, it mainly interacts with the nucleus of the atoms forming the matter it passes through. However, the probability it passes close enough to a silicon nucleus or a dopant nucleus is low. When this happens it can cause two types of interactions: scattering or absorption [5][6]. When a neutron is scattered by a nucleus, its speed and direction change but the nucleus is left with the same number of protons and neutrons it had before the interaction. The nucleus will have some recoil velocity and it may be left in an excited state that will lead to the eventual release of radiation. When a neutron is absorbed by a nucleus, either a wide range of radiation can be emitted or fission can be induced. Three effects are considered as they can affect integrated circuits.

- <u>Elastic Scattering</u>: In elastic scattering a fraction of the neutron's kinetic energy is transferred to the nucleus. This nucleus can then leave the crystalline silicon network if it has gained enough energy from the neutron.

- <u>Inelastic Scattering</u>: Inelastic scattering is similar to elastic scattering except that the nucleus undergoes an internal rearrangement into an excited state from which it eventually releases

radiation. This secondary particle creates a trail of electron-hole pairs able to modify the state of a transistor.

• <u>Absorption</u>: One type of neutron absorption by a nucleus can lead to the mutation of the atom into a heavier element. In case a neutron is absorbed by a boron-10 atom (used as a dopant in CMOS technology), the reaction will produce a gamma photon, an alpha particle and a lithium-7 nuclei. The alpha and the lithium recoil are both capable to interfere with the integrated circuit by ionization process [7].

#### 5.3.3 Interaction with charged particles

When a charged particle enters a matter it will interact with the electrons and nuclei in the medium and begins to lose energy as it travels through. The interaction can be generally thought of as collisions between the charged particle and either the atomic electron or the nucleus. The energy given off will result in ionization, production of ion-electron pairs, in the medium. It can also appear in the form of electromagnetic radiation.

Considered charged particles are protons, alpha-particles and ions. And given their energy, their interaction with matter is ionization. It is important to note that direct ionization from protons is only possible for 90 nm technologies and below. Older technologies will interact through indirect ionization where the effect in the circuit is provoked by the secondary particles. Alpha-particles and ions may generate single events (see following section) from electron-hole pairs issued from direct ionization of the material.

#### 5.4 Radiation effects

This section defines some useful notions related to radiation effects and then describes the different effects radiation can provoke in integrated circuits.

#### 5.4.1 Definitions

#### **Linear Energy Transfer (LET)**

When a particle interacts with the matter it passes through, it transfers its energy to the medium. The charge deposition capacity, through ionization, is described in terms of Linear Energy Transfer (LET) which corresponds to the energy deposition by length unit and depends on the material density,  $\varrho$ :

$$LET = \frac{1}{\rho} \cdot \frac{\Delta E}{\Delta x}$$

(In MeV.cm<sup>2</sup>/mg or MeV/mg/cm<sup>2</sup>)

A detailed explanation of the LET is available in [8].

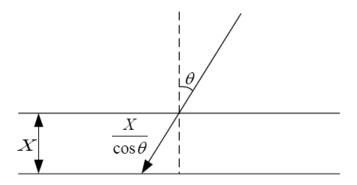

The deposited energy is given by the following equation where  $\theta$  is the ion incident angle:

$$\Delta E = \frac{dE}{dx} \cdot \frac{X}{\cos \theta}$$

Figure 5-7: Deposited energy for a heavy ion with a  $\theta$  incident angle

When  $\Delta E > Ec$  (critical energy), a single event phenomenon may occur. The LET threshold (LETth) is thus defined by this characteristic LET as the minimum LET required for a particle to create a single event. Consequently, components having a high LETth have a good immunity to single events.

#### **Cross section**

The cross section,  $\sigma$ , is a measure of the sensitivity of a device for a given particle LET or energy respectively for heavy-ions and protons. It is defined by the ratio of the number of single events observed on the device by the particle fluence (particles per cm<sup>2</sup>) received by the component under test. Thus, the cross section can be interpreted as the probability that an impinging particle provokes a single event and is given by the following equation:

$$\sigma_{sat} = \frac{\# of \ observed \ events}{fluency}$$

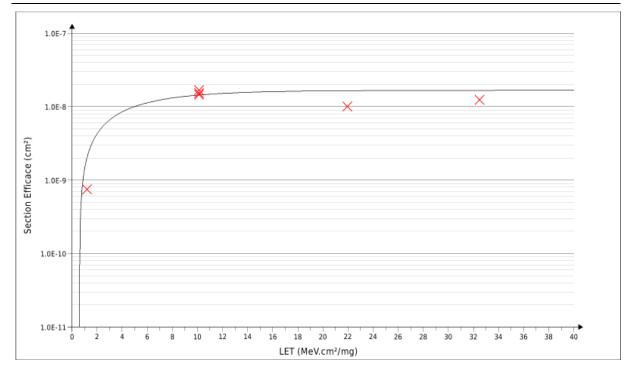

#### **Cross-section curve**

The cross-section curve describes the sensitivity of a device for a given effect. It is obtained by plotting the obtained cross-section measures versus incident particle LET, for heavy ions, or energy for protons.

The LET or energy is represented in the x-axis and the cross section in the y-axis. The cross-section curve has two specific values. The first is the *LET threshold*, which is the lowest LET required to trigger an event in the studied circuit. The second is the *saturation cross-section*, which indicates the maximal sensitivity of the device and thus is an image of the total sensitive area of the device.

An example of typical cross-section curve is given in Figure 5-8. The heavy ion cross section can be fit using a Weibull distribution with width (W) and shape (S) parameters. The curve shape equation is the following:

$$\sigma = \sigma_{sat} \left[ 1 - exp \left( \left( -\frac{LET - LET_{th}}{W} \right)^{S} \right) \right]$$

In the case of proton testing the Bendel model is used either with 1 parameter (threshold energy is the only parameter usable for old devices and low data points number) or with 2 parameters (threshold E and asymptotic cross section):

$$\sigma = \sigma_{sat} \left[ 1 - exp \left( -0.18 \left( \sqrt{18/E_{th}} \left( E - E_{th} \right) \right)^{1/2} \right) \right]^4$$

Figure 5-8: Example of heavy ions typical cross-section curve measure

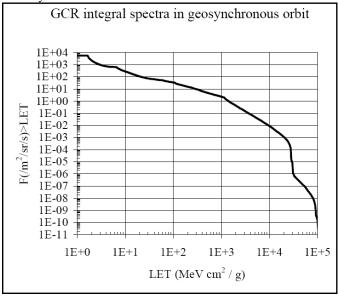

#### **Integral LET spectrum**

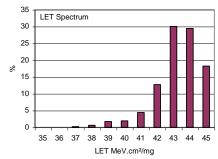

The integral LET spectrum is a graph representing for a given environment (orbit, solar activity and shielding) the particle distribution depending on their LET. As shown in Figure 5-9 the particle flux is plotted in the y-axis while the particle LET is plotted in the x-axis. Thus, for a given environment, one can obtain the particle density for a selected LET.

Figure 5-9: Example of integral LET spectrum

As a conclusion, when an energetic particle passes through an integrated circuit it interacts with its atomic structure. Events issued from this interaction may be classified into two groups: cumulative

effects and effects due to a single particle, also called Single Event Effects (SEEs). The two following sections briefly describe these phenomena.

#### 5.4.2 Cumulative effects

Exposure to radiation produces relatively stable, long-term changes in devices and circuit's characteristics that may result in parametric degradation and functional failures. Ionizing particles will cause Total Ionizing Dose (TID) effects whereas non-ionizing ones will cause displacement damage effects, also called Total Non-Ionizing Dose (TNID).

#### 5.4.2.1 Total Ionizing Dose

The total ionizing dose effect provokes cumulative long term ionizing damages due to protons and electrons. It primarily impacts insulating layers, which may trap charge or produce interface changes. In MOS devices, trapped charges can lead to a shift in the gate threshold voltages. More generally, in semiconductors, interface states can significantly increase device leakage currents. Ultimately, TID provokes permanent functional failures of the device [9].

Table 5-1 provides the estimated TID per year for four different orbits: Geosynchronous orbit (GEO), Global Positioning Satellite (GPS), Low Earth Orbit (LEO) and Defense Meteorological Satellite (DMS) [10].

Table 5-2: Estimated TID per year from electrons and protons (100 mm Al satellite skin)

| Orbit name            | GEO    | GPS    | LEO    | DMS   |

|-----------------------|--------|--------|--------|-------|

| Apogee<br>(km)        | 35,796 | 20,189 | 1,600  | 946   |

| Perigee<br>(km)       | 35,795 | 20,172 | 1,600  | 824   |

| Inclination (degrees) | 0      | 55     | 60     | 99    |

| Dose<br>rad(Si)/yr    | 6,600  | 59,000 | 17,300 | 1,260 |

#### 5.4.2.2 Displacement damage

Non-ionizing energy loss results in displacement damage and defects in both insulator and semiconductor regions. This energy deposited by impinging particles displaces atoms and creates electrically active defects. The overall effect of displacement damage is a change in the minority carrier lifetimes of semiconductors, and increased light absorption and coloration in crystalline optical materials. This effect concerns particularly bipolar devices and opto-electronics.

# 5.4.3 Single Event Effects (SEEs)

The charge deposited by a single ionizing particle can produce a wide range of effects. Some of them, such as Single-Event Transient (SET), Single-Event Upset (SEU) and Single-Event Functional Interrupt (SEFI) are temporary and can be recovered. Others can lead to permanent damage such as Single-

Event Latchup (SEL) or Single-Event Gate Rupture (SEGR). These effects can be produced either by direct ionization or by secondary particles issued from nuclear reactions or elastic collisions.

#### 5.4.3.1 Single-Event Transient

A single-event transient is an energy pulse issued from the ionization of sensitive volumes in electronic devices. SETs are a major concern for analog and mixed-signal CMOS circuits, analog and digital bipolar circuits and opto-electronics.

Transients can also propagate in combinational logic found in digital CMOS integrated circuits and may be captured by a memory element if they occur during a clock edge. In this case an SET may result in a single-event upset (see below).

#### 5.4.3.2 Single-Event Upset

Single-event upsets may occur when deposited charges, by ions and protons, are collected at sensitive nodes of storage elements such as flip-flops, latches, SRAM cells, etc. SEU may also be the result of an SET being latched on a clock edge after propagating in combinational logic.

The consequence of SEU phenomenon, also called bit-flip may depend on both the instant of occurrence and the purpose of the perturbed cell in the studied circuit of system. Indeed, the SEU can either be silent (unused or yet used perturbed data) or resulting a wide scope of errors including critical errors, such as SEFIs (see section 1.4.3.4).

The sensitivity to SEU of electronic devices greatly varies according to the technologies and several parameters. In particular, reduction of transistor size or supply voltage tends to decrease the critical charge and thus increase the sensitivity to SEEs.

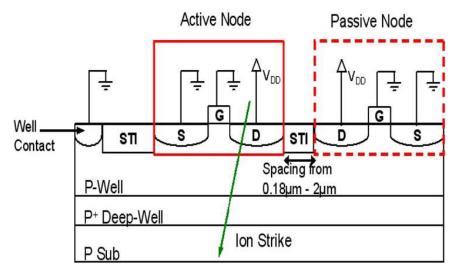

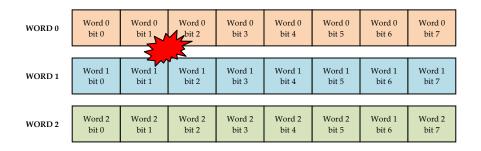

#### 5.4.3.3 Multiple-Bit Upset (MBU) and Multiple-Cell Upset (MCU)

Multiple upsets occur when several bit-flips are triggered by a single particle. Several upsets in a memory word are called MBUs, whereas several upsets in different memory words are referenced as MCUs.

Integrated circuits tend to be increasingly sensitive to multiple upset events as gaps between transistors are becoming smaller. This allows charges deposited by ions and protons to be collected by several sensitive nodes of the circuit and thus results in SEUs in different memory cells.

Error-Correcting Codes (ECCs), such as Hamming codes, are well adapted to mitigate SEUs as they can detect and correct errors in a word. However, MBUs are a real challenge for advanced technologies as they require elaborated and complex ECCs.

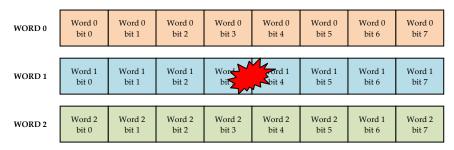

Figure 5-10: Two upsets in the same word provoked by a single particle (MBU)

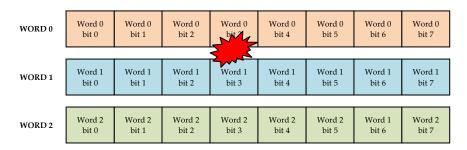

Figure 5-11: Two upsets in different words provoked by a single particle (MCU)

#### 5.4.3.4 Single-Event Functional Interrupt (SEFI)

In complex circuits such as processors, FPGAs, etc, SEUs may have severe consequences, called single-event functional interrupt (SEFIs). Indeed, an SEU in the device's control circuitry may place the device into a test mode, halt, or undefined state. Another example of SEUs provoking SEFIs in processors is the so-called sequence loss resulting, for instance, of an SEU in the program counter leading to an infinite loop. In such cases, a reset of the application or a power off/on cycle is required to recover the full functionality of the system.

SEFIs were observed and defined for the first time in 1997, see [11], from observations in SDRAM, EEPROMS and Microprocessors. SEFIs were also reported in flash-based memories, SRAM-based FPGAs and microcontrollers.

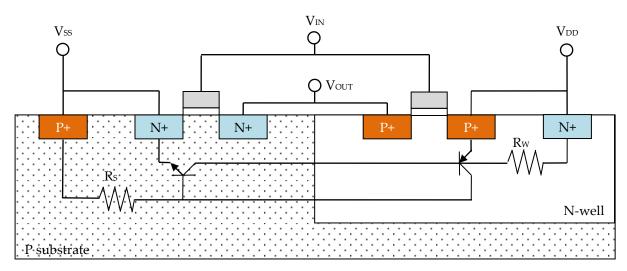

#### 5.4.3.5 Single-Event Latchup (SEL)

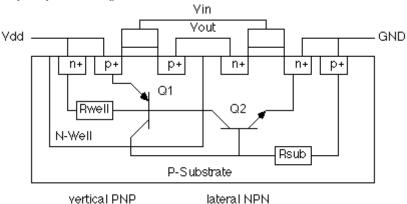

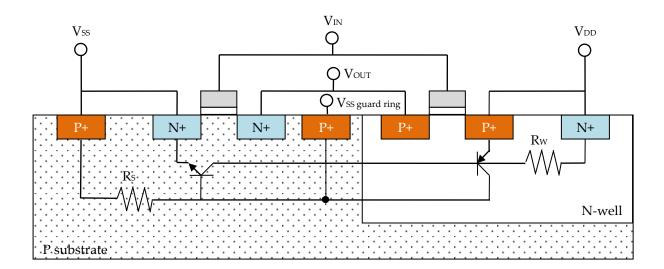

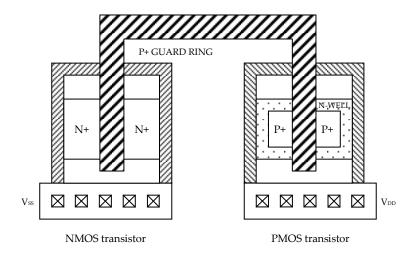

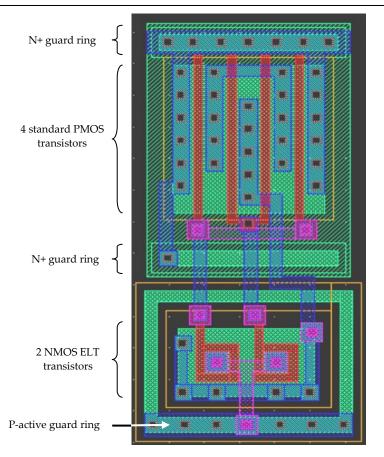

A Single-Event Latchup is the result of the triggering of a parasitic thyristor (PNPN structure) mainly existing in CMOS circuits (Figure 5-12) and potentially in bipolar devices. When it occurs, an important current flows and increases the local temperature of the die, until destruction of the structure. This effect can be stopped by powering-off the circuit.

A specific case of latchup, called micro-latchup, can be encountered when the current is limited by the internal device circuitry. Since the current is limited, the micro-latchup is not destructive but the effect on the functionality may still be significant.

Figure 5-12 : Cross section of the PNPN parasitic structure in standard CMOS technology

#### 5.4.3.6 Single-Event Burnout (SEB)

Another type of destructive effect, called Single-Event Burnout, occurs mainly in power MOSFETs when the source gets forward-biased and the drain-source current is higher than the breakdown voltage of the parasitic structures. The resulting high-current may provoke a local overheating able to destroy the device.

#### 5.4.3.7 Single-Event Gate Rupture (SEGR)

Single event gate rupture occurs when a particle damages (increased leakage current) or ruptures the gate oxide insulation (device destruction) of a power MOSFET.

#### 5.4.3.8 **Summary**

Table 5-3 provides a list of integrated circuits technologies and families with their respective sensitivity to SEEs.

Table 5-3: Relevant single event effects as a function of component technology and family

| Technology        | Family  | Function            | SEL | SEGR | SEB | SEU | MCU/MBU | SEFI | SET |

|-------------------|---------|---------------------|-----|------|-----|-----|---------|------|-----|

| Power MOS         |         |                     |     | Χ    | Χ   |     |         |      |     |

|                   |         | SRAM                | Χ*  |      |     | Χ   | X       |      |     |

|                   |         | DRAM                | Χ*  |      |     | X   | X       | X    |     |

|                   | OS and  | FPGA                | Χ*  |      |     | Χ   | X       | Χ    | Χ   |

| CMOS,             |         | Flash<br>EEPROM     | Χ*  |      |     | X   |         | X    |     |

| BiCMOS and<br>SOI |         | μP /<br>μcontroller | Χ*  |      |     | X   | X       | X    | Х   |

|                   |         | ADC                 | Χ*  |      |     | Χ   |         | Χ    | Χ   |

|                   |         | DAC                 | Χ*  |      |     | Χ   |         | Χ    | Χ   |

|                   | Linear  |                     | Χ*  |      |     |     |         |      | Χ   |

| Discolor.         | Digital |                     |     |      |     | X   |         |      | Χ   |

| Bipolar           | Linear  |                     |     |      |     | Χ   |         |      | Χ   |

<sup>\*</sup>except SOI

# Choosing a design hardening strategy

This section will be added soon.

# Technology selection and process level mitigation

# 7.1 Scope

Radiation-Hardening-By-Process (RHBP) concerns modifications in manufacturing processes in order to reduce the consequences of radiation on integrated circuits. This goal can be achieved by several means such as modifications of doping profiles in devices and substrates, optimization of deposition processes for insulators and use of specific materials. These techniques deal with two main effects: TID and SEEs.

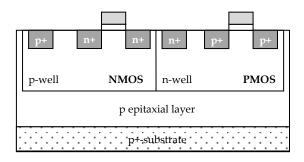

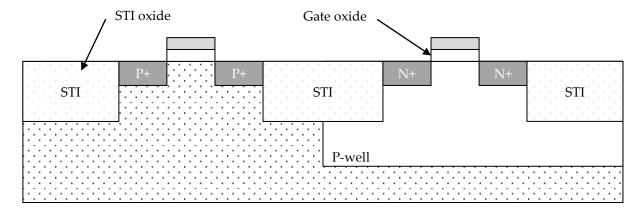

- TID is associated to charge deposition in insulators (e.g. grid oxide and field oxide), thus degrading their properties. This is due to a difference in the mobility and trapping of electrons and holes, resulting in a net positive trapped charge. The result is a current leakage increase either intra-device (within a transistor) or inter-device (between two adjacent transistors). Solutions devoted to reduce the impact of TID focus on modifying insulator's properties and doping levels in active regions nearby interfaces. Currently, Shallow Trench Isolation<sup>2</sup> (STI) is one of the main concerns for TID effects in CMOS technology, particularly the parasitic sidewall and top corner regions. Therefore, most of the presented techniques devoted to mitigate TID concern STI oxide.

- SEEs are associated to instantaneous failures in active regions and thus can be mitigated by modifications of used materials and/or structures or by using alternative substrates such as Epitaxial layers, Silicon On Insulator (SOI) or Silicon On Sapphire (SOS).

The designer must keep in mind that the sensitivity to radiation effects of integrated circuits may also be very dependent on the technology scaling. As an example, in reference [12] is shown that the Soft Error Rate<sup>3</sup> (SER) for DRAMs remains relatively constant with scaling while for SRAMs it significantly increases for each new technology generation.

<sup>&</sup>lt;sup>2</sup> Shallow Trench Isolation (STI), also known as "box isolation technique", is a feature which prevents electrical current leakage between adjacent transistors. STI is generally used in sub-0.5µm CMOS technology.

<sup>&</sup>lt;sup>3</sup> A soft error is an error in a memory, for example caused by an upset, which can be recovered by rewriting the correct value or reinitializing the system.

# 7.2 Table of effects vs mitigation techniques

| Marie de la la companya de la compan |                          | R | <b>.</b> |     |     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---|----------|-----|-----|------|

| M1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mitigation techniques    |   | SET      | SEU | SEL | Page |

| 7.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Epitaxial layers         |   |          |     | X   | 36   |

| 7.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Silicon On Insulator     |   | Х        | Х   | X   | 37   |

| 7.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Triple wells             |   | X        | Х   | X   | 41   |

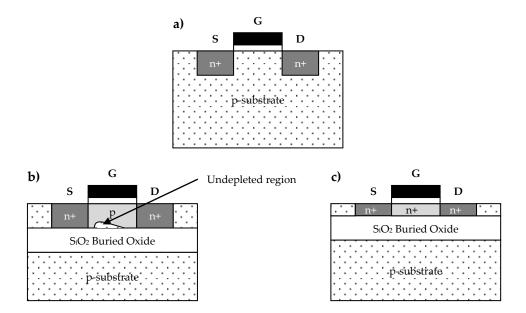

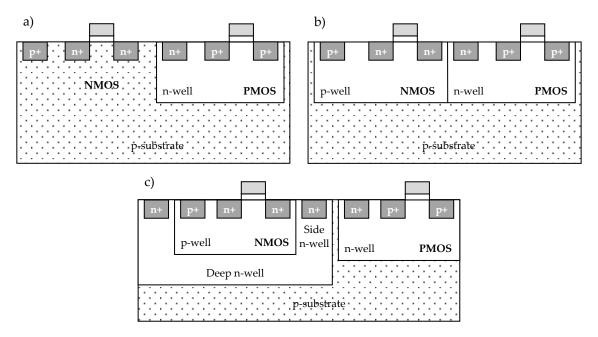

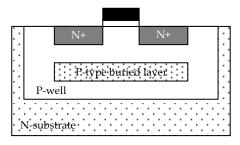

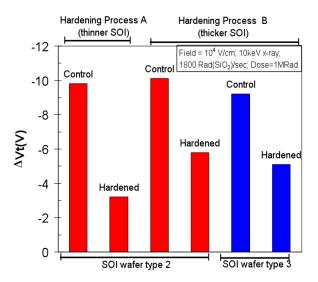

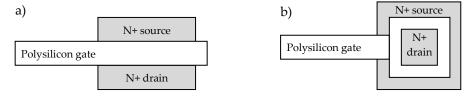

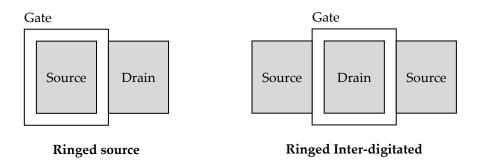

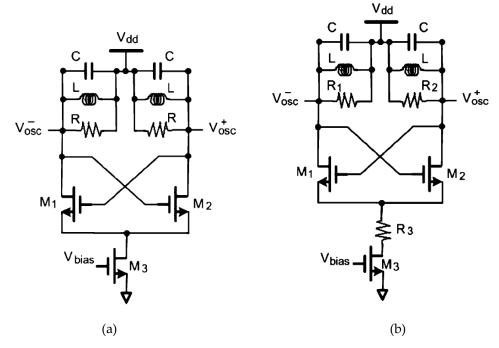

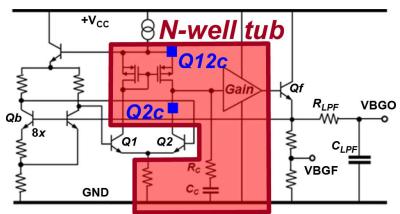

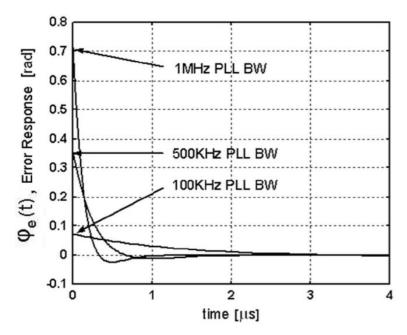

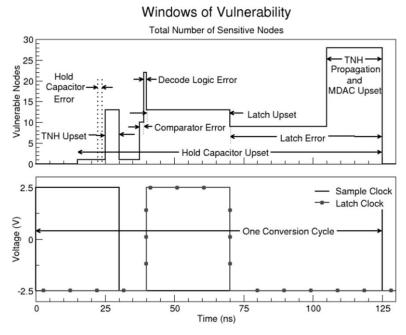

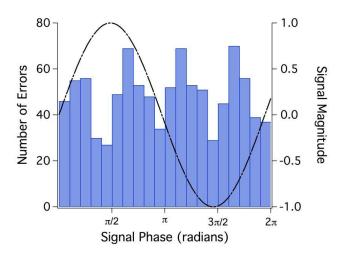

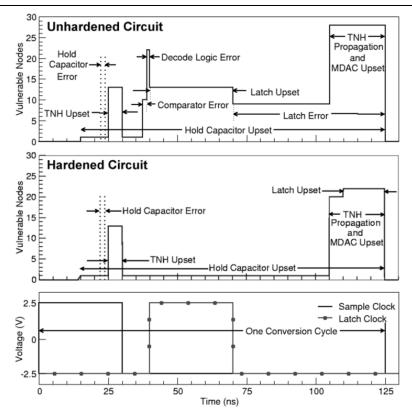

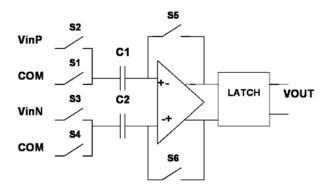

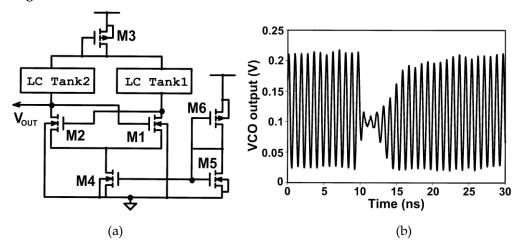

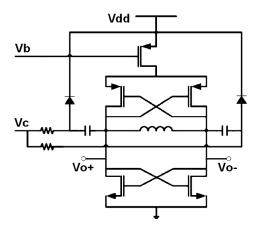

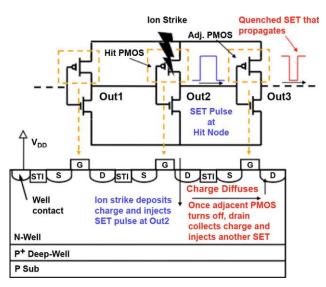

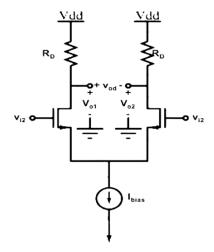

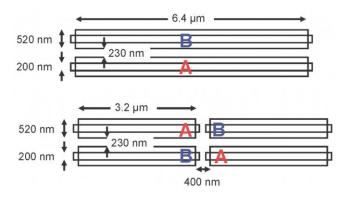

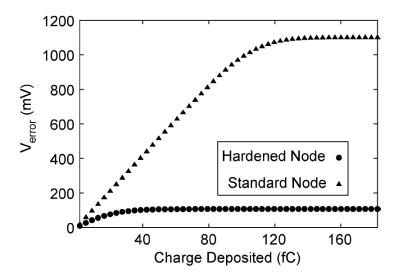

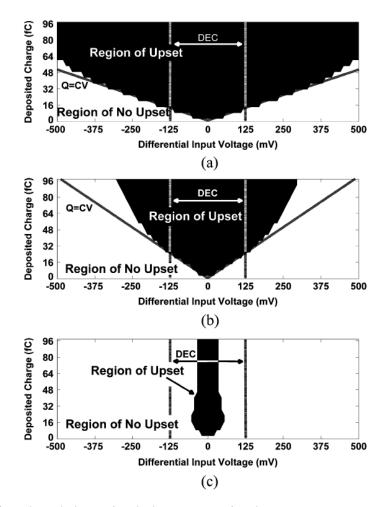

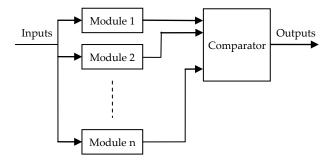

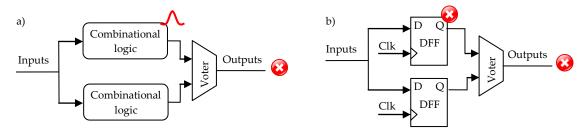

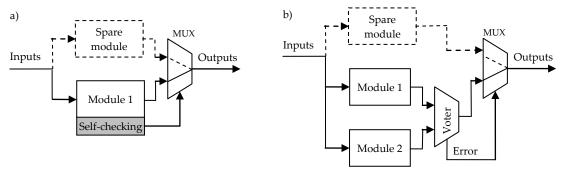

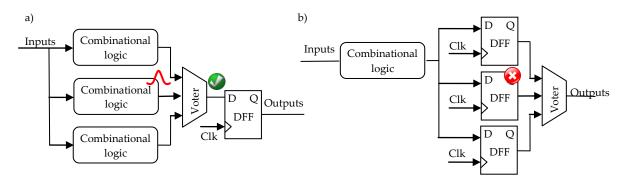

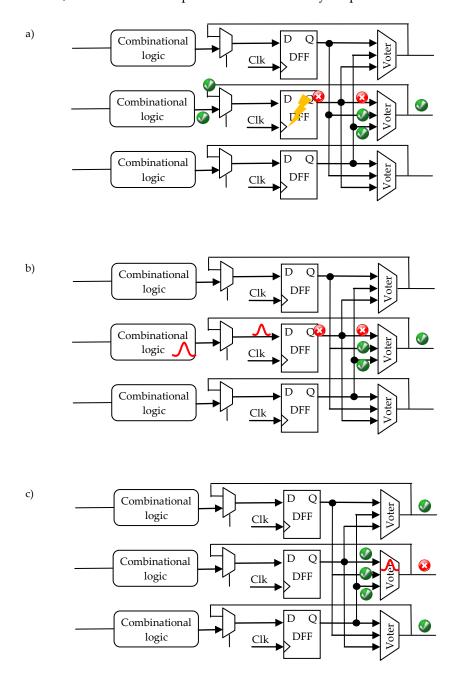

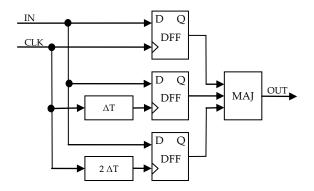

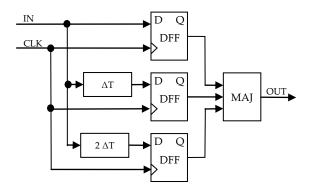

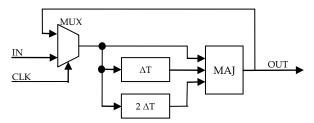

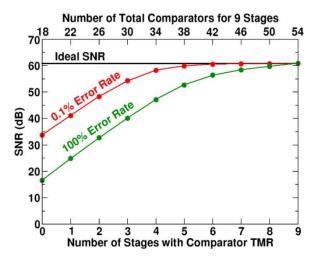

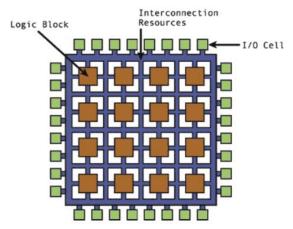

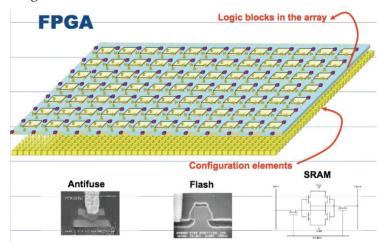

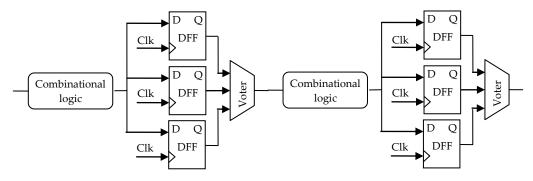

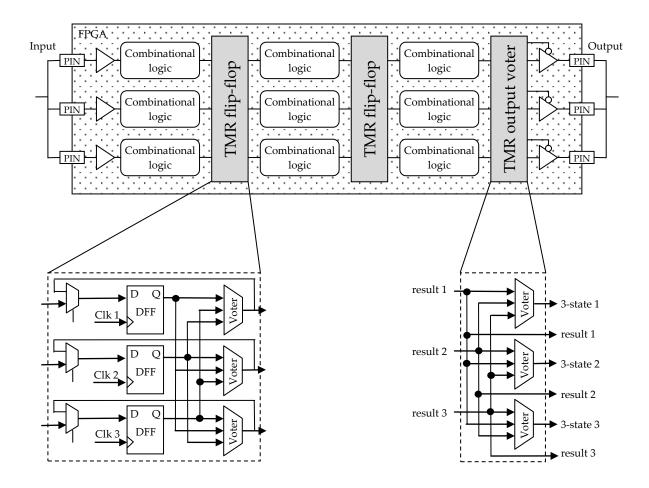

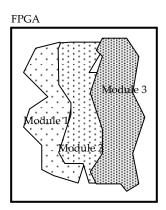

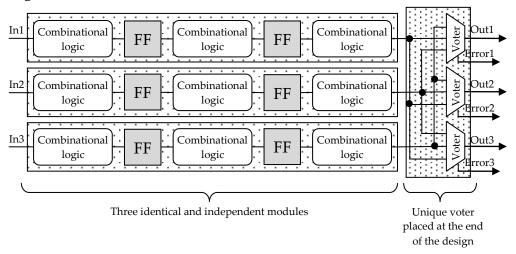

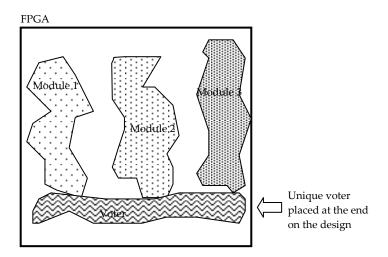

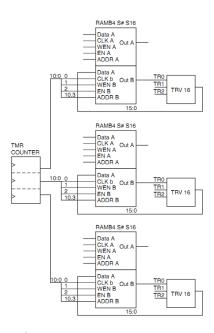

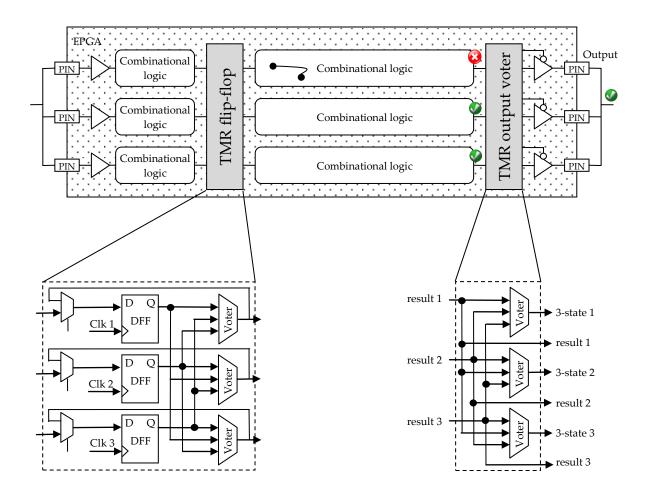

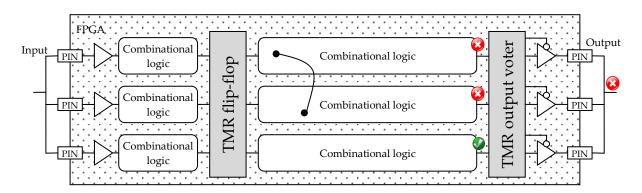

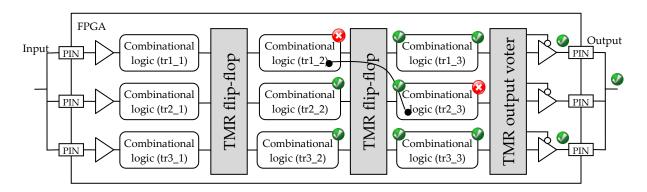

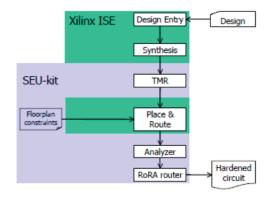

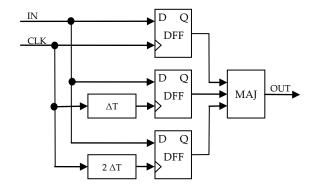

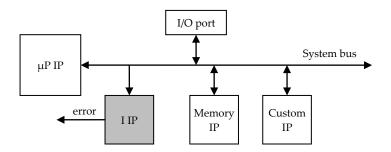

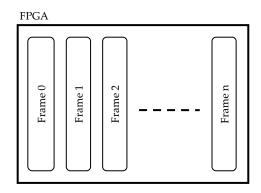

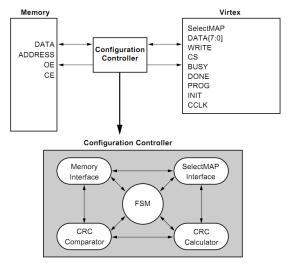

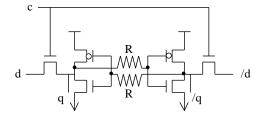

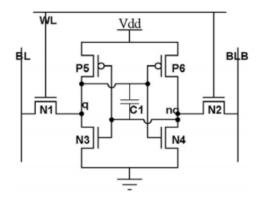

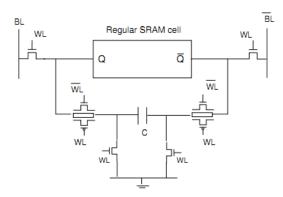

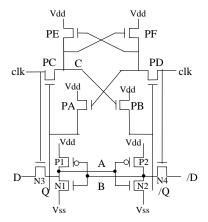

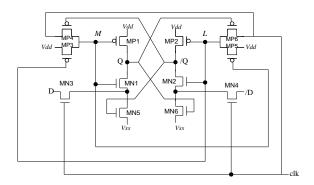

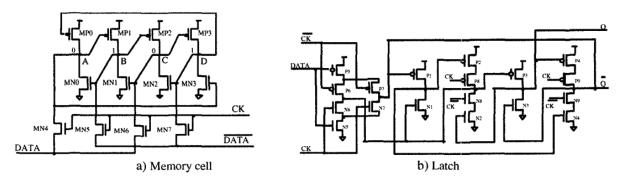

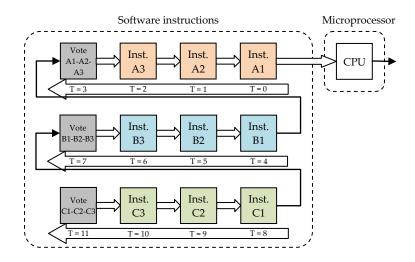

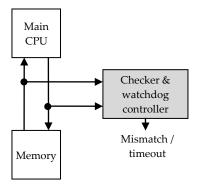

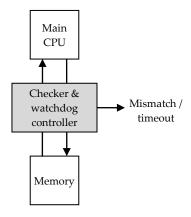

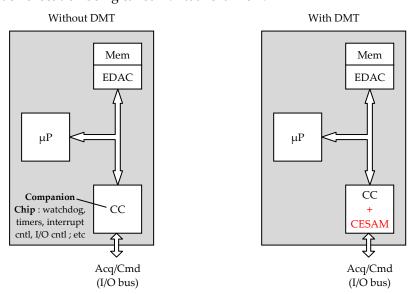

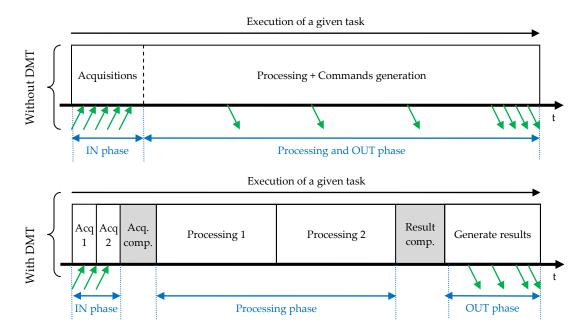

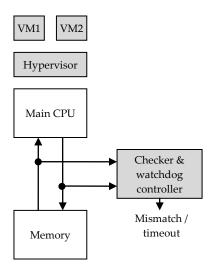

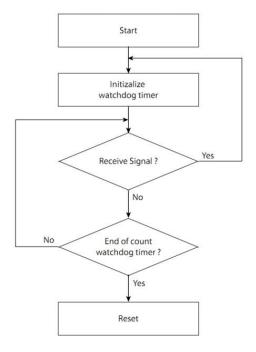

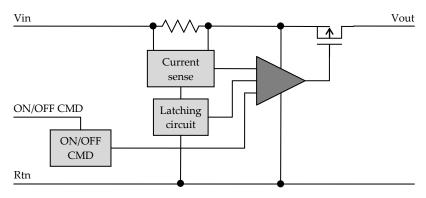

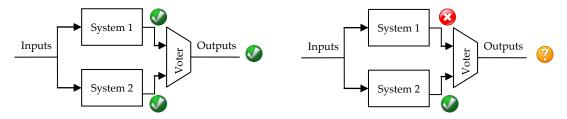

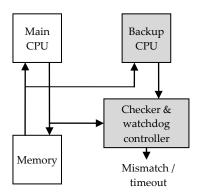

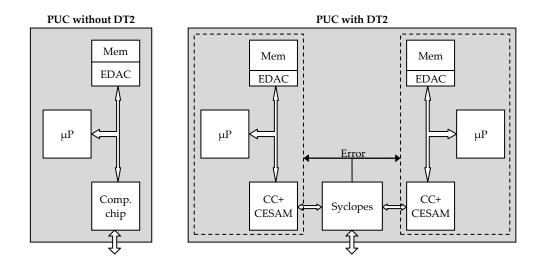

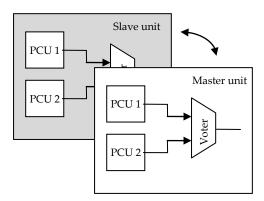

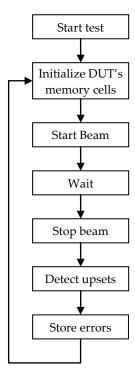

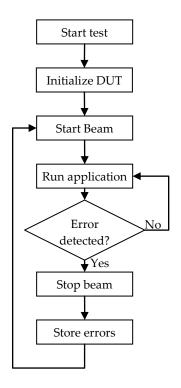

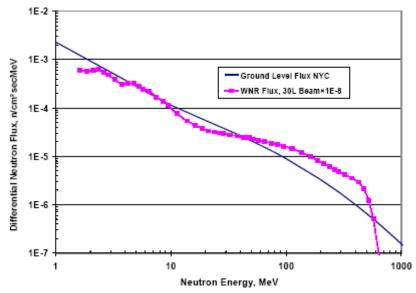

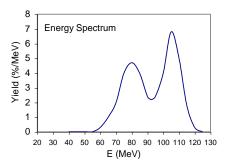

| 7.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Buried layers            |   | X        | Х   | X   | 43   |