# **3D activities @ CEA-LETI**

**D. Henry** / CEA-Leti-Minatec

Contibuting authors : A. Berthelot / R. Cuchet / G. Simon / Y. Lamy / P. Leduc / J. Charbonnier

January 24th 2013

#### Outline

- Introduction

- Medipix 3 project status

- 3D Technological toolbox @ LETI

- Available technologies / short term projects

- Technological modules developments / Mid & long term projects

- Products examples

- Conclusions / prospects

#### **CEA - Leti at a Glance**

Commissariat à l'Énergie Atomique et aux Énergies Alternatives

rtomique + energies alternative

is one of the largest research organizations in Europe, focused on energy, health, information technologies, and national defense

16,037 **People** (10% PhD and Post Doc)

#### **Research centers** 10

Founded in 1967 as part of CEA

#### 1,700 researchers

190 PhD students + 34 post PhD with 70 foreign students (30%)

#### **Over 1,700 patents**

265 generated in 2010 40% under license

210 M€ budget ~ 40M€ CapEx

### 40 start-ups & 265 industrial partners

3D activities @ CEA-LETI / CERN Workshop / 24-01-2013- D.Henry 3 © CEA. All rights reserved

#### **CEO Dr. Laurent Malier**

leti

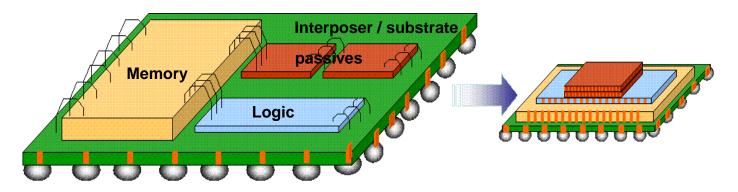

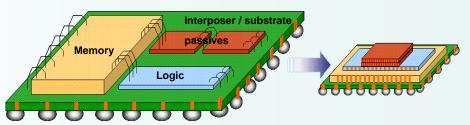

### **Introduction : What is 3D Integration ?**

- In electronics, a 3D integrated circuit is a chip in which two or more layers of active electronic components are integrated vertically into a single circuit, component or system.

- 3D Integration key drivers :

- Form factor decrease

- Performances improvement

- Heterogeneous integration

- Cost decrease

### **Introduction : Why do we need 3D Integration ?**

### • To solve the following issues :

- Form factor decrease :

- X & Y axis

- Z axis

- Performances improvement

- Decrease R, C, signal delay

- Increase device bandwidth

- Decrease power consumption

- Heterogeneous integration

- Integration of heterogeneous components in the same system

- Cost decrese

- Si surface decrease

- Reuse of existing Packaging, BEOL & FEOL lines

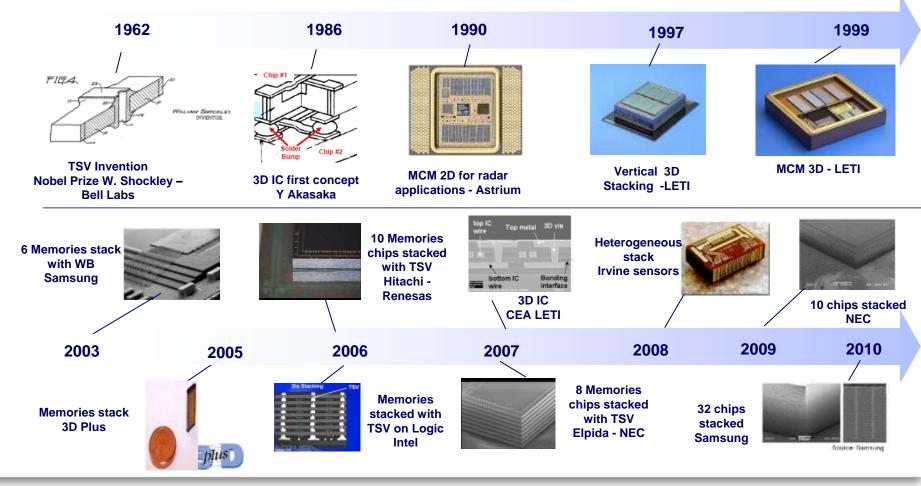

### **3D Integration electronic components (brief) history**

3D activities @ CEA-LETI / CERN Workshop / 24-01-2013– D.Henry 6 © CEA. All rights reserved

#### Outline

### Introduction

### Medipix 3 project status

- 3D Technological toolbox @ LETI

- Available technologies / short term projects

- Technological modules developments / Mid & long term projects

- Products examples

- Conclusions / prospects

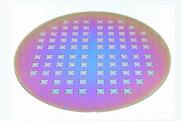

### Medipix 3 project status (summary)

- **Customer: CERN**

- **Project start up:**

- June 2011

- **Objectives**:

- Fabrication of a read-out chip with TSV

- Assembly of a particle detector on top of it

- Proof of concept

- **Project status**

- 1<sup>st</sup> lot: µS6688P (2 wafers)

- 2<sup>nd</sup> lot: µS6924P (3 wafers)

- 3rd lot: µS7394P (3 wafers)

- First lot delivered on January 2012

→ not in specification

- Third lot delivered on June 2012  $\rightarrow$  OK

- Dicing & pick out issues @ LETI & VTT

- Dicing solution in october 2012

- **CERN** electrical tests :

leti

- Preliminary (14 chips)  $\rightarrow$  OK

- Complete tests + detectors assy on going

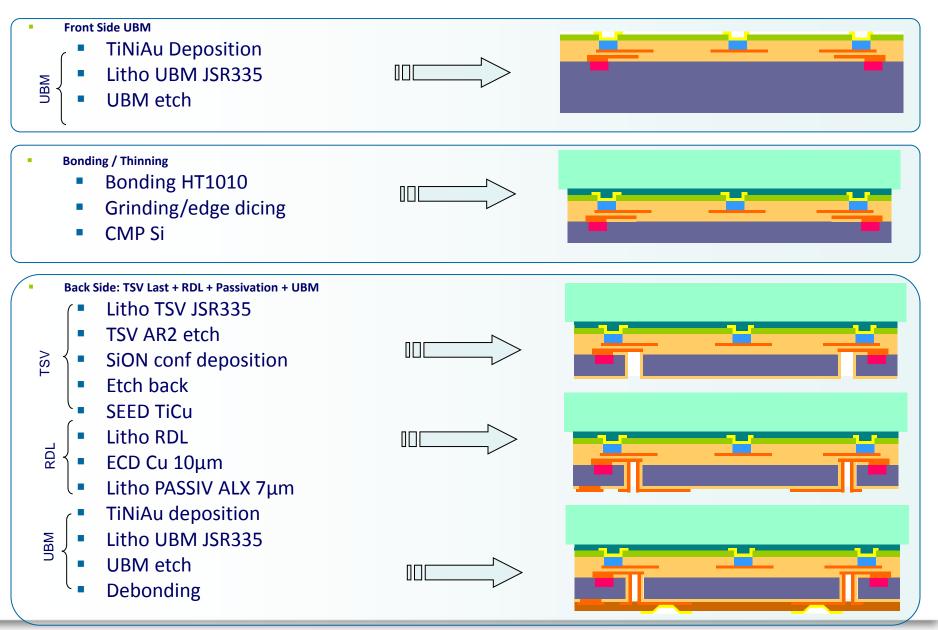

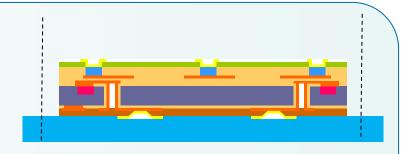

### **Medipix 3 process flow**

leti

3D activities @ CEA-LETI / CERN Workshop / 24-01-2013– D.Henry 9 © CEA. All rights reserved

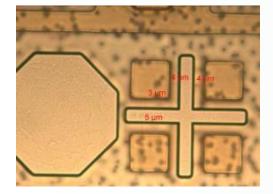

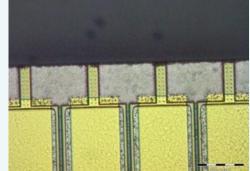

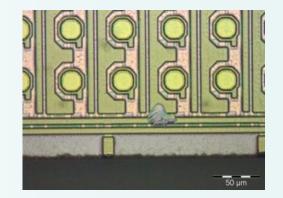

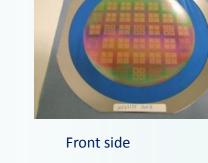

#### Front Side

- Front Side topology = 4µm

- Alu/UBM contact resistance: Preclean + Ti / Ni / Au deposition

- UBM litho: positive photo resist

- Alignment on Top metal (Specs +/-1µm):

Alignment marks UBM/Final metal

Pixels after litho

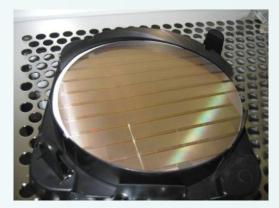

#### Bonding on a temporary glass carrier

- HT1010 (BSI product)

- Bonding on EVG520

- Accoustic microscope inspection

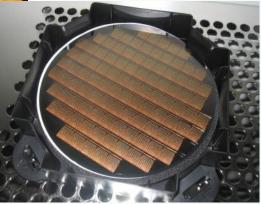

#### Silicon thinning to 120μm

- Coarse grinding until 200μm

- Edge timming until 1.5mm

- Coarse + Fine grinding until 125μm

- Silicon CMP (2μm) until 120μm + scrubber

P01-SONOSCAN inspection

leti

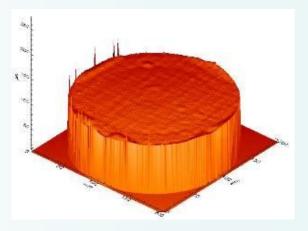

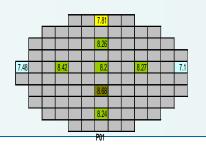

P01-3D mapping-Si thickness post grinding

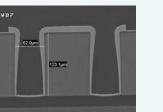

#### TSV patterning

- Hard mask deposition:

- TSV :

- Photo resist

- Alignment BS (TSV) / FS (UBM)

- CD=60µm (AR 2:1)

- TSV etch process → Multi step

- HM etch

- Si etch : Bosch process

- TSV insulation :

- LT dielectric deposition

- Bottom etch to contact M1

Alignment marks BS/FS

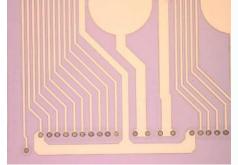

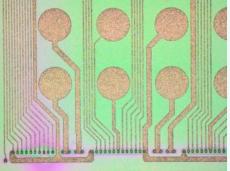

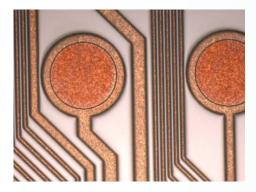

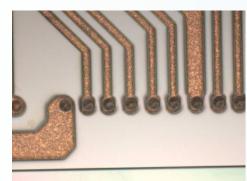

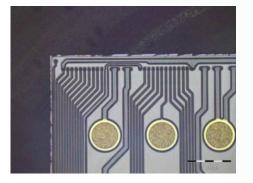

#### TSV Metalization + RDL

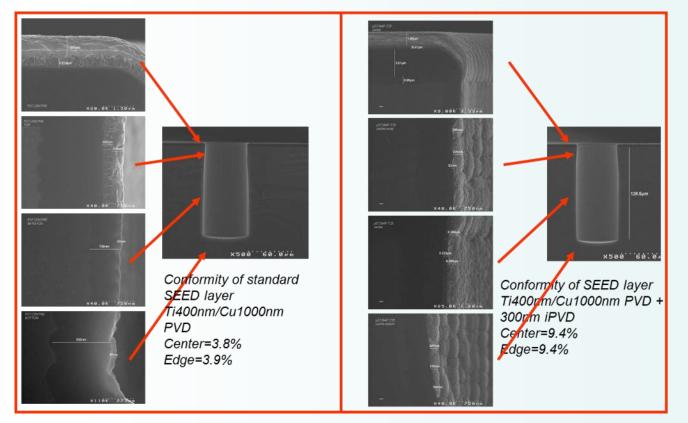

- P01 and P03: Seed layer deposition Ti 400nm / Cu 1000nm (PVD)

- P02: Ti 400nm/ Cu 1000nm (PVD) + Cu 300nm (IPVD)

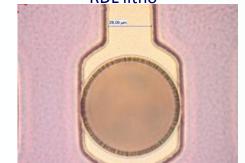

#### TSV Metalization + RDL

- RDL litho : Dry film 15 μm

- ECD Cu 9μm

- Stripping

- Seed layer Cu + Ti etch

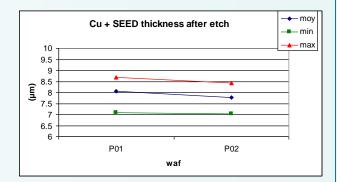

- RDL line thickness control

RDL Cu line thickness control (graph + map)

**RDL** litho

RDL Cu line on TSVs

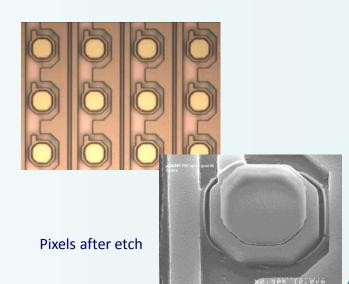

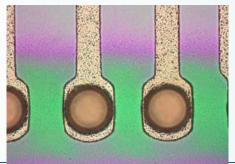

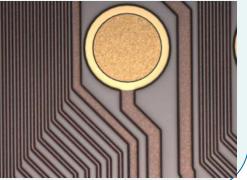

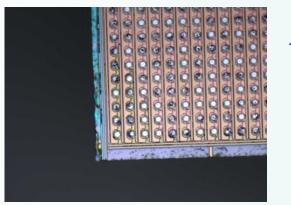

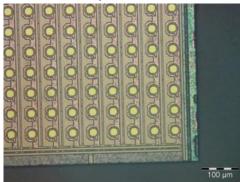

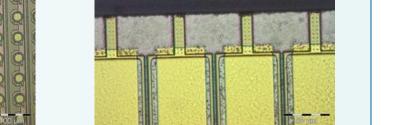

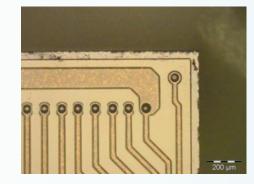

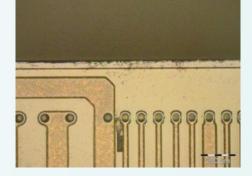

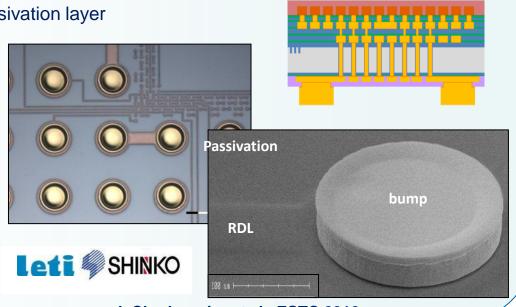

#### Passivation + backside UBM

- Litho process

- Photosensitive polymer

- UBM deposition (TiNiAu)

- UBM litho

- UBM etch, stop on polymer

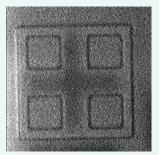

**BGA** matrix

Functional die after litho UBM

Polymer covering the TSV

Functional die after UBM etch

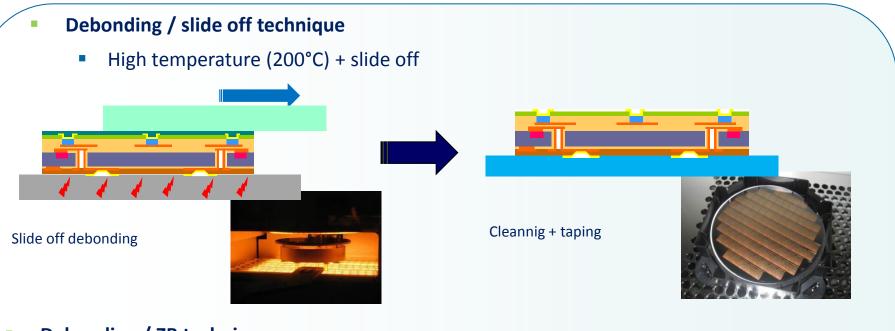

#### Debonding / Cleaning

- Debonding (slide-off)

- Cleaning with Wafer Bond remover

- Delivery for dicing

#### Slide off debonding

P02- After debonding

#### P01- After debonding

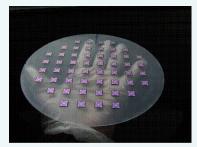

#### Chips Dicing & boxes packaging

- First delivered wafers :

- Metal delaminations on front side

- High chipping on the edges

- Chips breaking during pick out process

- Tape residues on pixel side

High chipping + pad delamination

leti

Tape residues

- Need to develop an optimized dicing process :

- DISCO collaboration

#### Backside chipping

#### **Dicing trials on DISCO plant (Munchen)**

- Taping of BGA side on the tape

- UV tape

- Fine blade

- High Blade rotation

- Low Blade speed

#### **Pixel side observations**

Chip I4

- Lower chipping compare to previous dicing

- Every defects localized on dicing streets

#### Pixel side observations

Chip I4

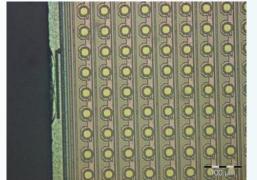

#### BGA side observations

leti

- Higher chipping than on the pixel side → contact with tape

- All defects localized on the dicing streets → polymer seal ring effect

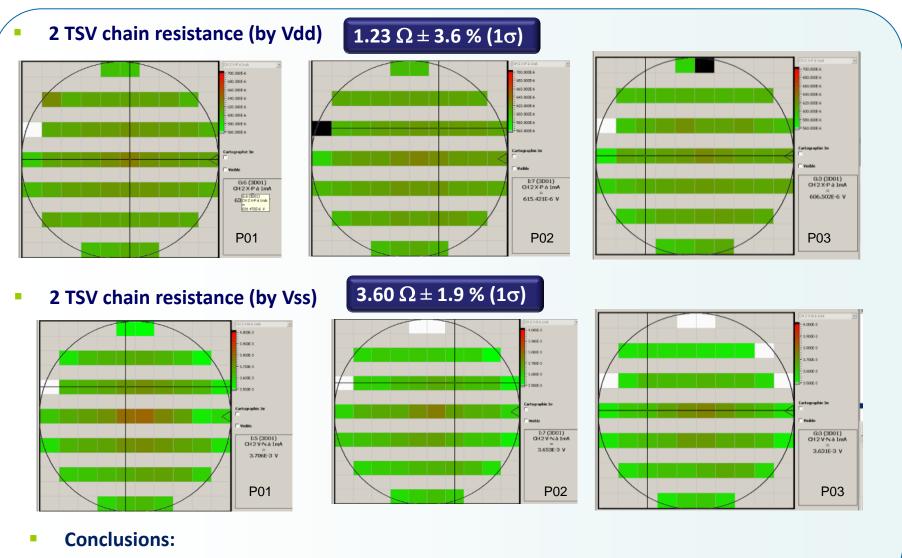

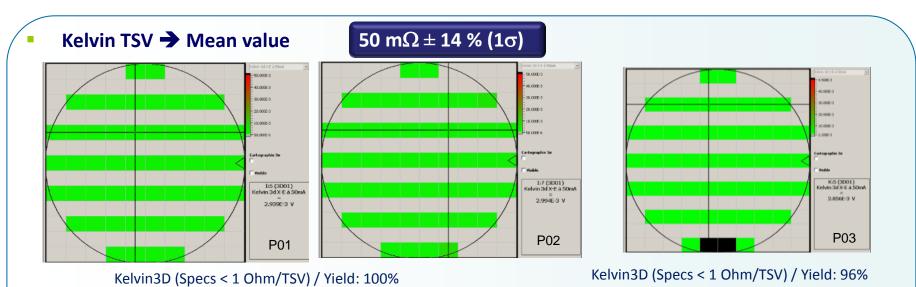

### Medipix 3 project results / electrical tests (non exhaustive)

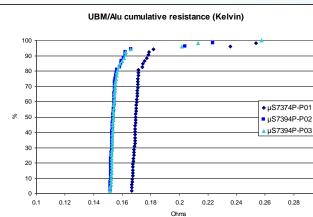

#### UBM/ Al contact resistance

#### Cumulative resistance UBM/Alu Mean value : ~ 150 mohms

#### Conclusions:

- © Isolation between UBM lines OK

- ☺ Alu/UBM contact resistance is OK

0.3

### Medipix 3 project results / electrical tests (non exhaustive)

$\odot$  Uniform distribution of values  $\rightarrow$  no comparizon with reference value possible

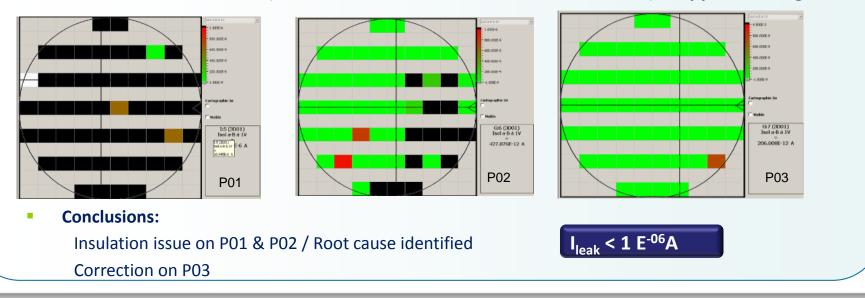

### Medipix 3 project results / electrical tests (non exhaustive)

#### Insulation between 2 TSV (1 connected TSV to M1 & 1 non connected) – Applied voltage : 1V

leti

3D activities @ CEA-LETI / CERN Workshop / 24-01-2013– D.Henry 22 © CEA. All rights reserved

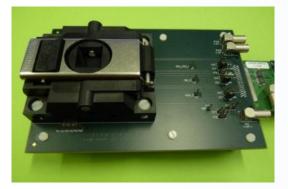

#### Test set-up :

- Test board realize the interface between Medipix3 chip and readout interface

- Test socket is embedded on test board to establish contact to the bga pads of the chip

- We are using a custom readout interface (USB) common to most of MEDIPIX chip family

Test board

Test socket

Readout interface

#### Test samples

- LETI sent a complete GELPAK of 16 diced chips. (DISCO dicing)

- Parts are from IBM wafer # AZNW5VH, at CERN it was identified as Wafer # 24

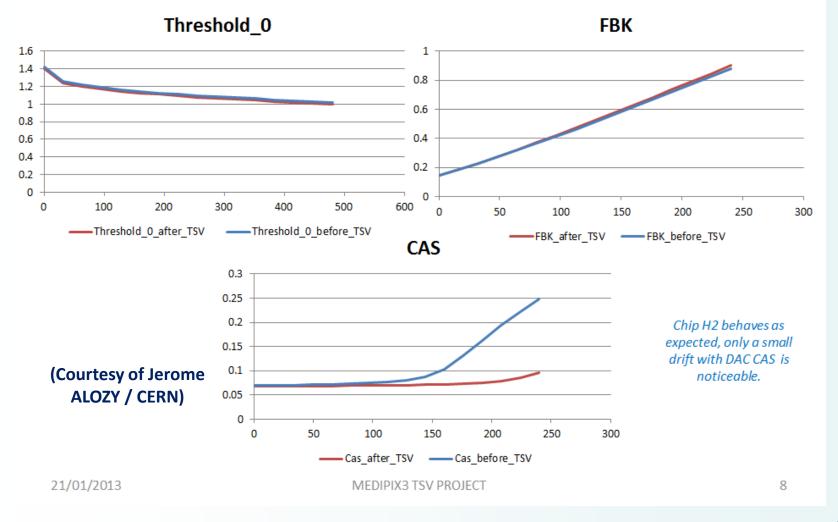

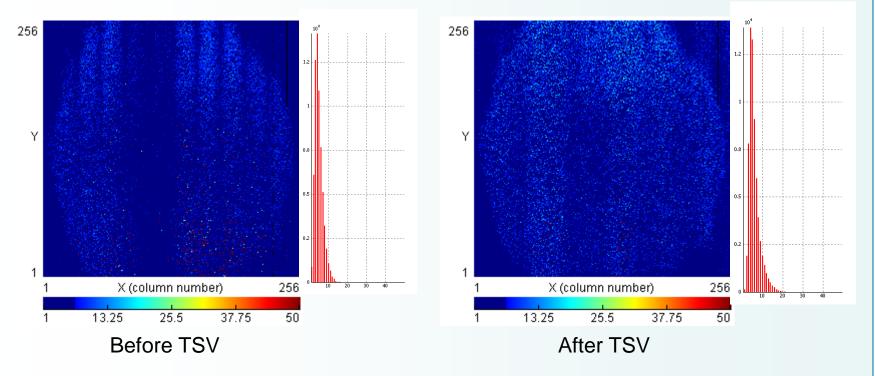

- W21-H2 Noise floor comparison

- View of the complete matrix behaviour

We could notice only a slight difference

leti

#### (Courtesy of Jerome ALOZY / CERN)

- Conclusion on preliminary tests @ CERN (16 chips)

- Result are really encouraging, again we have a limited number of samples to have good statistic and selected samples were not the one expected (for instance one class F was selected for electrical test). For me 10 device on 14 selected samples are functional and behave well.

|     |                    |                                  | For stat. | ОК |

|-----|--------------------|----------------------------------|-----------|----|

| H2  | ОК                 |                                  | 1         | 1  |

| H1  | ОК                 |                                  | 1         | 1  |

| 110 | BAD                | to be checked visually           | 1         | 0  |

| 19  | OK but a bit noisy | to be investigated               | 1         | 1  |

| 18? | BAD                | to be checked visually           | 1         | 0  |

| 17? | BAD                | wronlgy seleceted class F sample | 0         |    |

| 16  | ОК                 |                                  | 1         | 1  |

| 15  | ОК                 |                                  | 1         | 1  |

| 14  | BAD                | already bad during wafer probing | 0         |    |

| 13  | BAD                | to be checked visually           | 1         | 0  |

| 12  | ОК                 |                                  | 1         | 1  |

| 11  | ОК                 |                                  | 1         | 1  |

| 19? | BAD                | to be checked visually           | 1         | 0  |

| J8  | ОК                 |                                  | 1         | 1  |

| J7  | ОК                 |                                  | 1         | 1  |

| J6  | ОК                 |                                  | 1         | 1  |

|     |                    |                                  | 14        | 10 |

#### (Courtesy of Jerome ALOZY / CERN)

#### **Medipix 3 project perspectives**

- Tests of 84 new chips coming from wafer 02 Don going @ CERN

- Assembly of detectors on ROIC @ VTT

on going

- Dicing process implementation @ LETI

- One wafer stored @ LETI optimized wafer for detector assy

- Dissemination aspects :

- 3 common papers (CERN / LETI) in 2012 : Minapad / ISCDG / ESTC

- 1 abstract accepted to ECTC 2013

- Project starting with new design (Medipix RX ?)

#### Outline

- Introduction

- Medipix 3 project status

- **3D Technological toolbox @ LETI**

- Available technologies / short term projects

- Technological modules developments / Mid & long term projects

- Products examples

- Conclusions / prospects

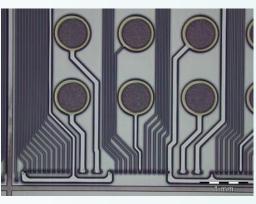

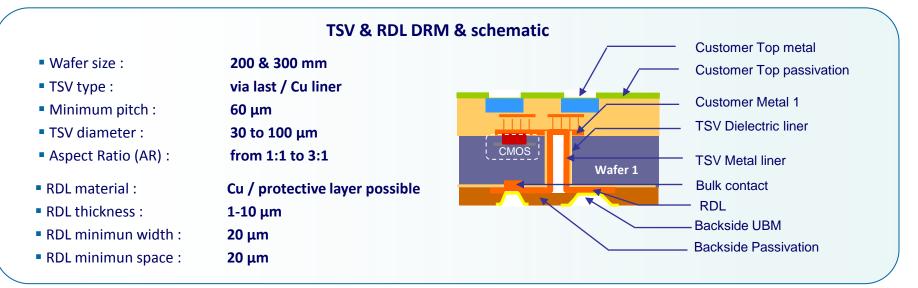

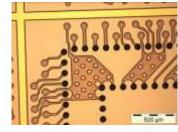

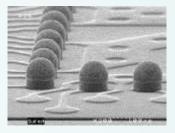

#### **Available technologies : TSV + RDL**

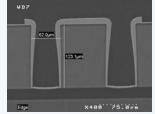

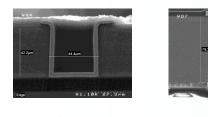

#### **TSV & RDL morphological results**

AR 2:1

41 0.0

AR 1:1

bump RDL

Ream Spot Mag Det FWD Tit

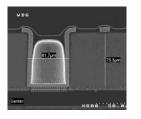

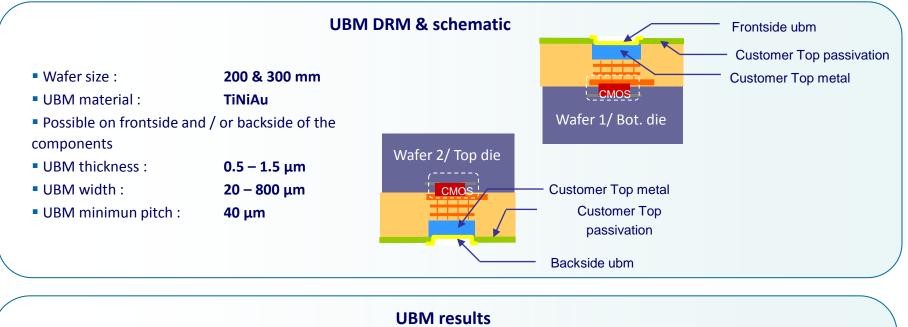

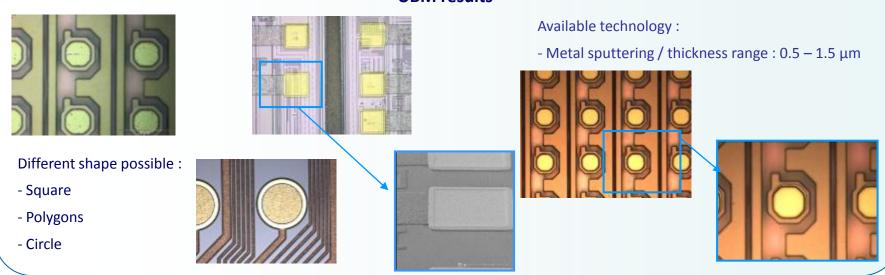

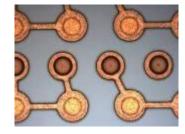

### Available technologies : Under bump metallurgy (UBM)

leti

3D activities @ CEA-LETI / CERN Workshop / 24-01-2013– D.Henry **30** © CEA. All rights reserved

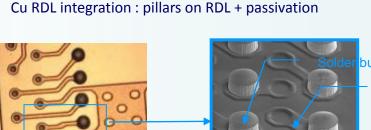

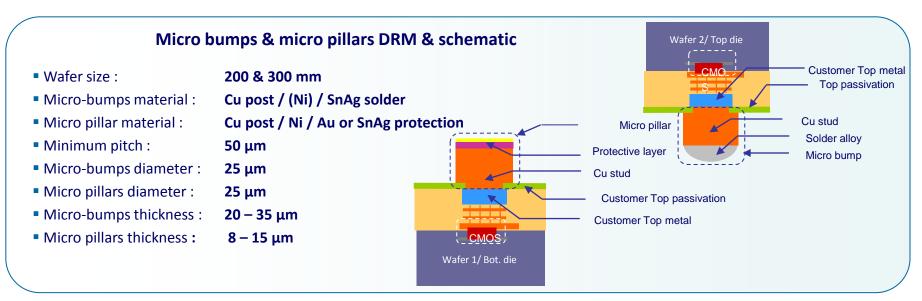

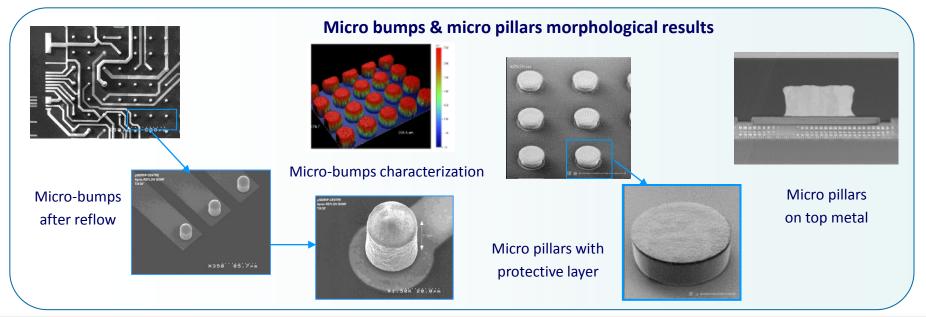

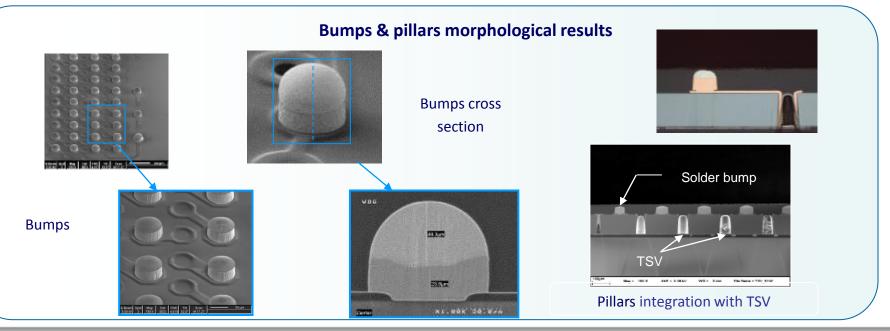

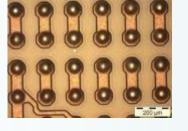

### **Available technologies : Micro bumps & micro pillars**

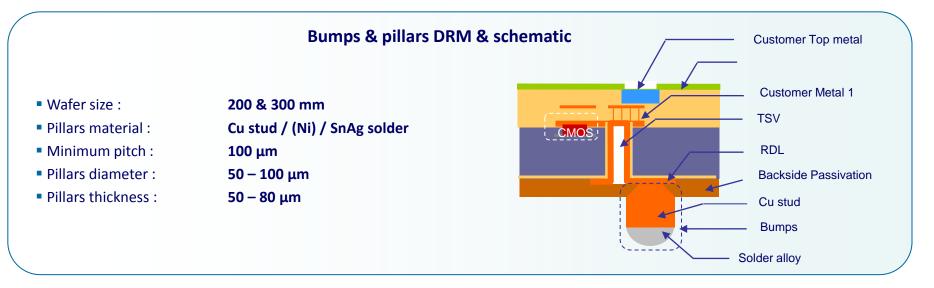

#### **Available technologies : bumps & pillars**

3D activities @ CEA-LETI / CERN Workshop / 24-01-2013– D.Henry **32** © CEA. All rights reserved

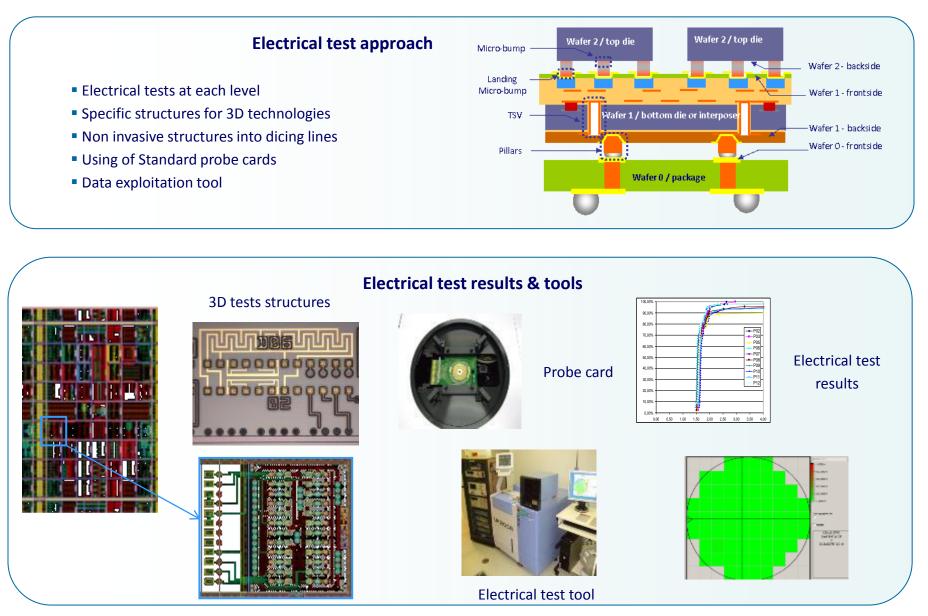

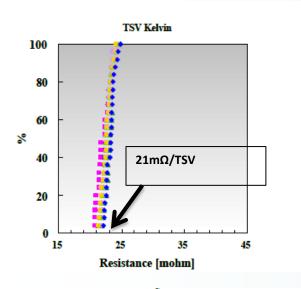

### **Available technologies : 3D electrical tests / reliability**

3D activities @ CEA-LETI / CERN Workshop / 24-01-2013– D.Henry 33 © CEA. All rights reserved

OPEN

#### Outline

- Introduction

- Medipix 3 project status

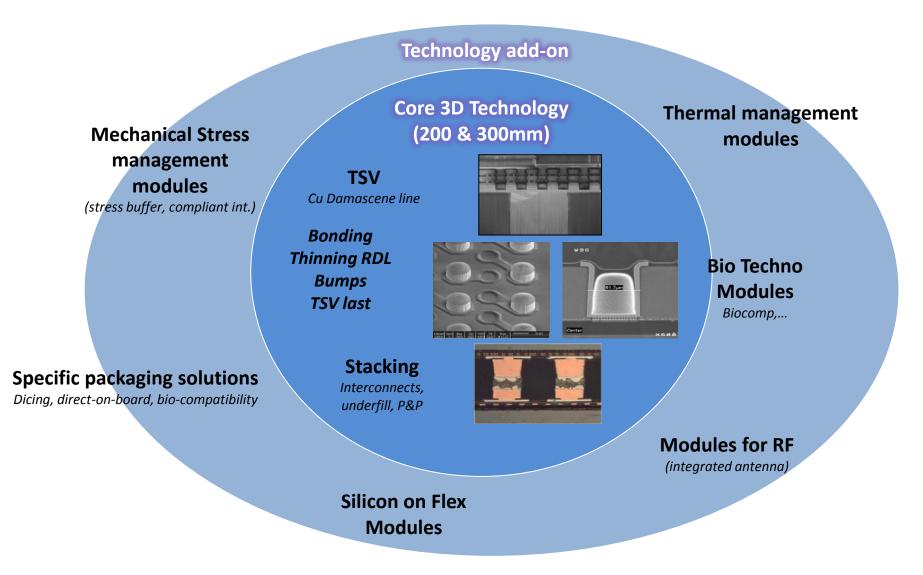

## 3D Technological toolbox @ LETI

- Available technologies / short term projects

- Technological modules developments / Mid & long term projects

- Products examples

- Conclusions / prospects

#### **Technological developements**

#### **Technological developements**

leti

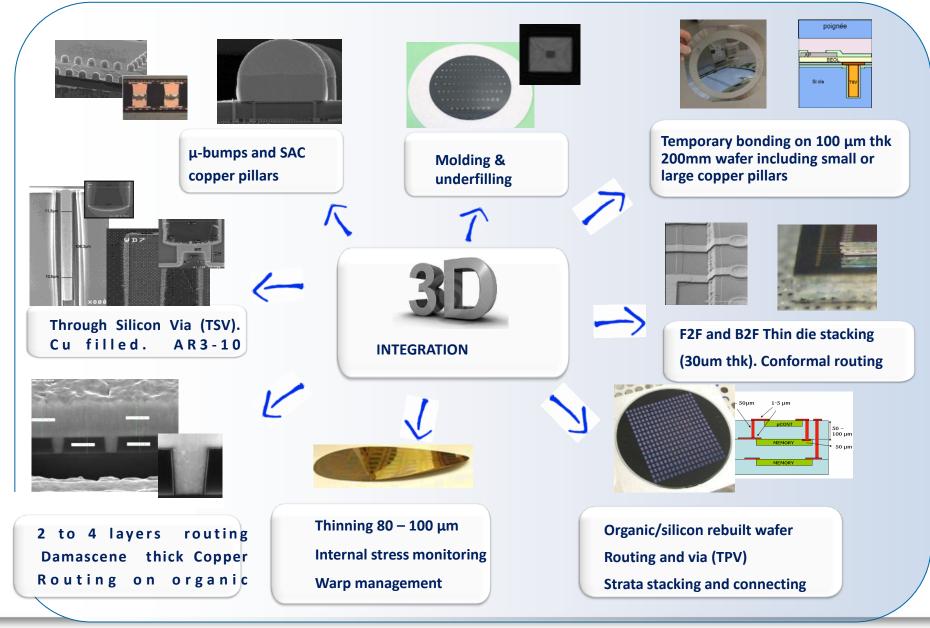

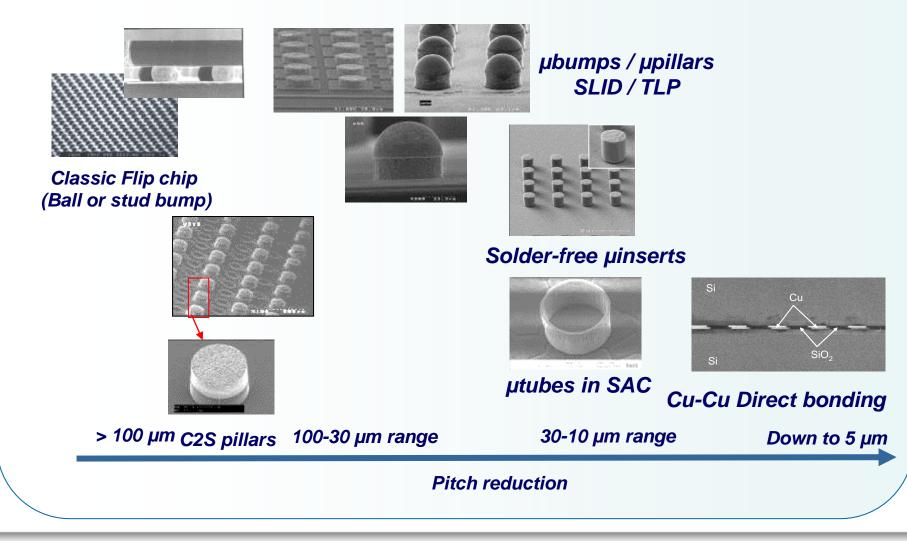

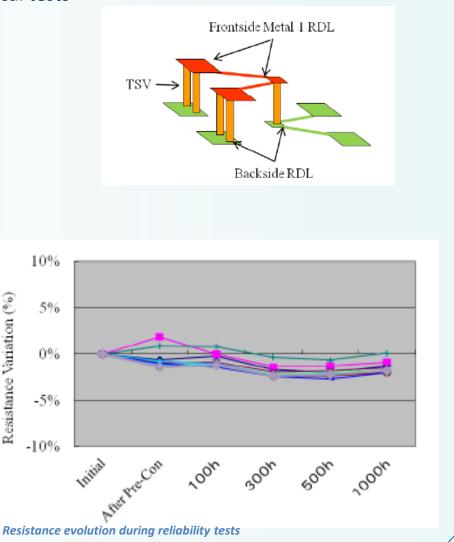

#### Tech.dev. : die to die interconnects

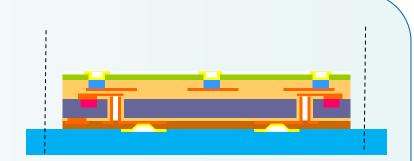

#### From solder balls to Cu-Cu bonding $\rightarrow$ A wide range of interconnections

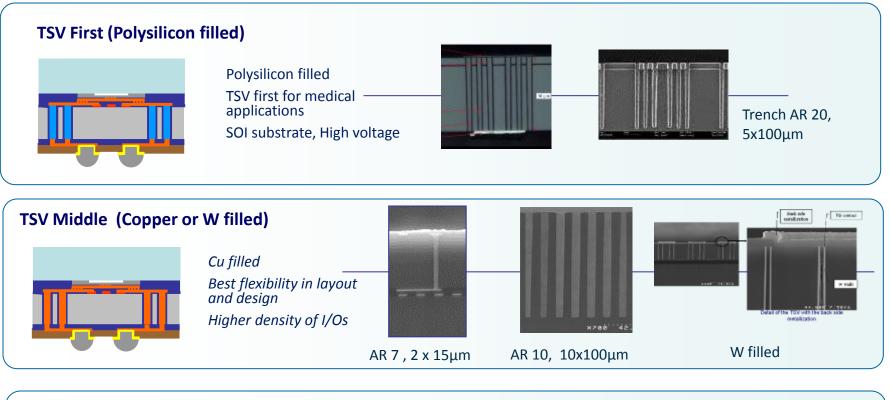

#### Tech.dev. : TSV families

#### Tech.dev. : RDL & Board connections

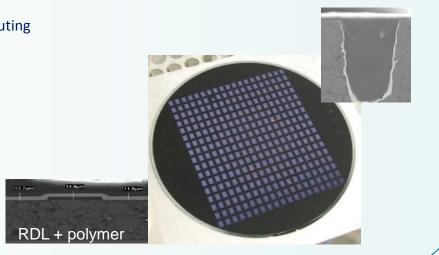

Two families of RDL with different targets and application fields Cu RDL with organic passivation layer

Few  $\mu m$ 's of Cu (1 – 10  $\mu m$ ), Polymers for IDL

Cu RDL (Damascene) with inorganic passivation layer

- RDL

- L/S=10μm

- Organic passivation by spin coating

- Large bumps

- Ø250μm and 500μm pitch pillars

- Cu/Ni/Au electroplating

- Stripping, seed layer wet etch

- Total thickness 70μm

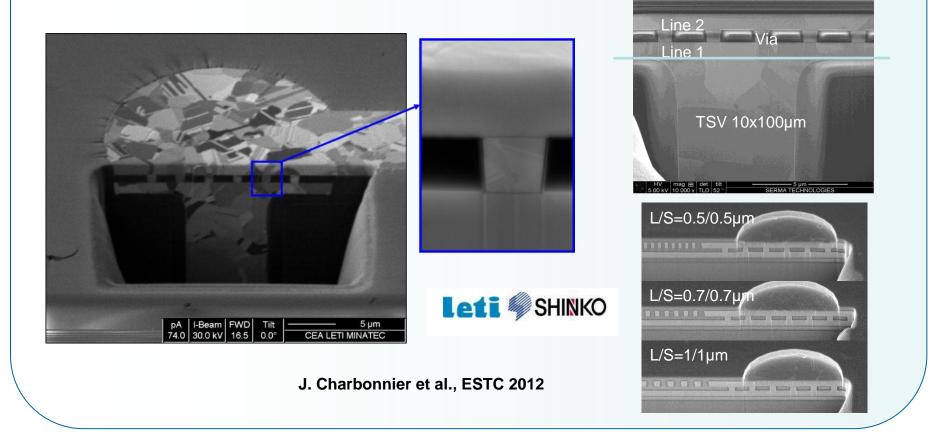

J. Charbonnier et al., ESTC 2012

#### **Tech.dev. : Front side routing**

- Dense routing 0.5/0.5μm

- Cross section after Line 2 copper Chemical Mechanical Polishing

- TSV integration with thick (>1μm) Line 1 Via Line 2 damascene levels

- Full integrity of via: no extrusion

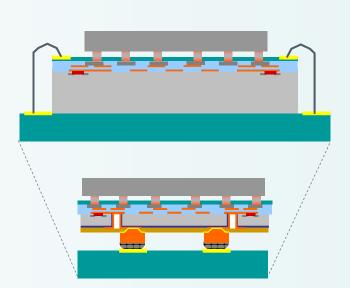

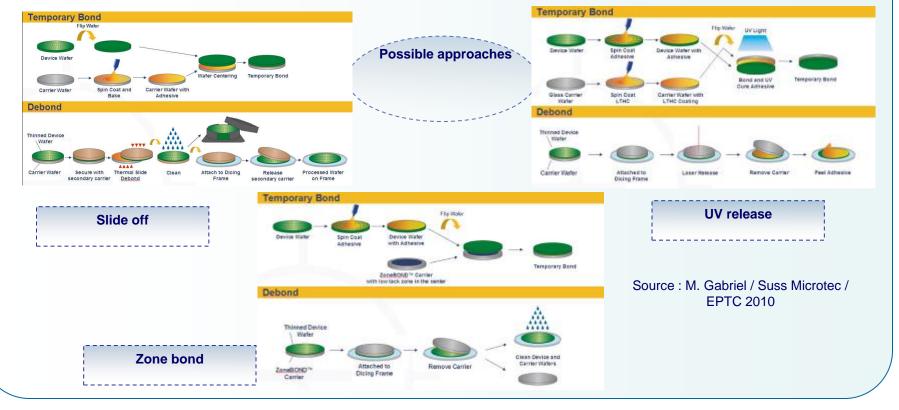

#### Tech.dev. : temporary bonding

#### Temporary bonding main challenges

- High temperature compatibility

- Low temperature debonding

- Wet processes compatibility

- Mechanical resistance : grinding & polishing

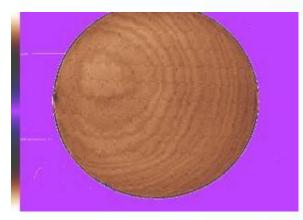

### Tech.dev. : temporary bonding & thinning

- Temporary Bonding / slide off technique

- HT10.10 glue / 19μm thick

- Scanning acoustic microscopy (SAM)

- Mechanical grinding

- Thinning to 100μm

- Edge trimming

- Silicon CMP

- Temporary Bonding / ZB & UV techniques under developments

J. Charbonnier et al., ESTC 2012

ZB bonding / SAM inspection on full wafers

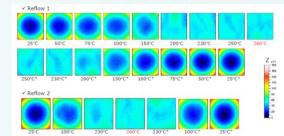

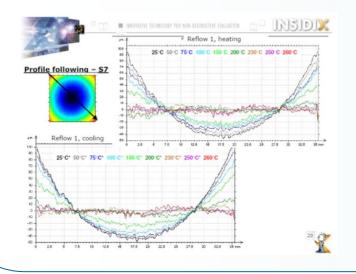

#### **Tech.dev. : Stress management**

- Objectives : to compensate the stress of the chip in order to be able to :

- Thin the chips until "ultimate" thickness (< 50 μm)</li>

- Assembly the chips on another chip without connections defectivity

bending effect

- Identification of the characterization method

- Preliminary trials on going :

- TDM method → Topography & deformation measurement under thermo mechanical load

- Full field technique / Optical deformation measurements

- Resolution : +/- 3μm

- Temperature scanning

leti

First experiment with stress compensation layers

Standard process

Compensation stress layers process

#### **Tech.dev. : Debonding**

- Debonding / ZB technique

- Glue chemical dissolution + pull in

Device on tape

J. Charbonnier et al., ESTC 2012

Back side

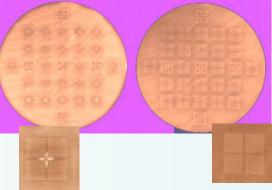

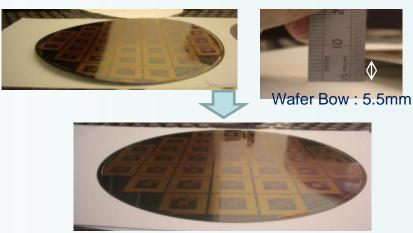

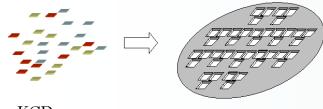

#### Tech.dev. : Rebuilt wafers

#### Embedded chips in silicon

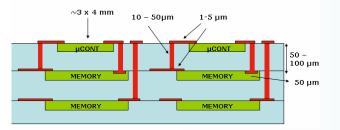

- Rebuilt wafers: CIWIS approach (Chip In Wafer for Integrated System)

- Deformation minimized (Low warpage) : high litho resolution

- Wafer fully compatible with classical silicon processes

- Higher temperature compatibility

- Process compatible with Si & glass frame

KGD

leti

Silicon frame

Chip in Silicon Wafer

Chip in Glass Wafer

#### Embedded chips in polymer

- multi-die embedded in organic wafer with via and routing

- die attach on tape + carrier / molding

- Through Polymer Via connecting (TPV) / routing

- hybrid wafer warp monitoring / control

- Waferlevel multi-strata stacking

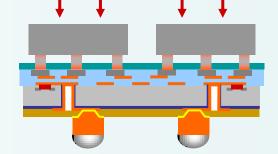

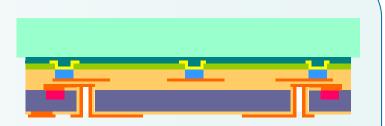

#### **Tech.dev. : Chips stacking**

- Two approaches for components stacking

- Chip to wafer

- High speed / low accuracy (+/- 3μm)

- Low speed / high accuracy (+/- 0.5 μm)

- Wafer to wafer

**SET FC 300**

3D activities @ CEA-LETI / CERN Workshop / 24-01-2013– D.Henry | 46 © CEA. All rights reserved

## Tech.dev. : electrical tests & reliability

OPEN

Specific patterns developments for electrical tests

Resistance Variation (%)

- **Reliability**:

- Environmental tests

TCT / HTS / HAST

- **Electro-migration**

| Reliability Test   | Condition                 |

|--------------------|---------------------------|

|                    | bake 125C, 24hrs,         |

| Pre Conditioning   | MSL-3 30C, 60%, 192hrs,   |

|                    | Rreflow 260C x 3times     |

| Temp. Cycle (TC)   | -55C-125C, 1000cycle      |

| High Temp. Storage | 125C, 1500hrs             |

| HAST               | 110C, 85%, 3V, 1000cycles |

#### Outline

- Introduction

- Medipix 3 project status

## 3D Technological toolbox @ LETI

- Available technologies / short term projects

- Technological modules developments / Mid & long term projects

- Products examples

- Conclusions / prospects

#### 3D activities @ CEA-LETI / CERN Workshop / 24-01-2013– D.Henry 49 © CEA. All rights reserved

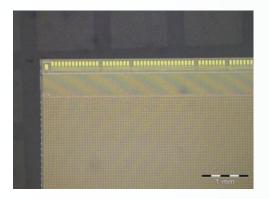

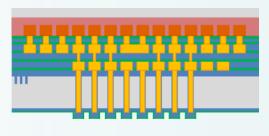

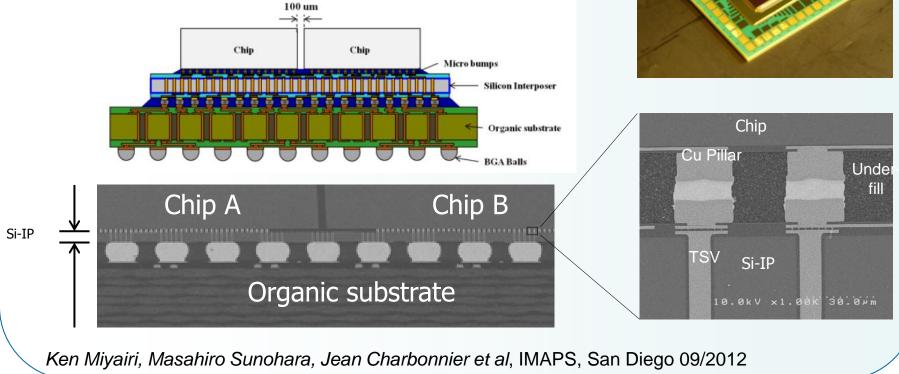

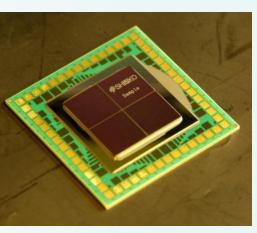

#### **Product example : Passive interposer**

#### Features

• Cu TSV, AR10

SHINKO

lei

- 2 to 4 layers routing, Damascene thick copper, L/W

0.5/0.5 x 1.4µm

- Temporary bonding

- Thinning, Stress Monitoring, Warp Management

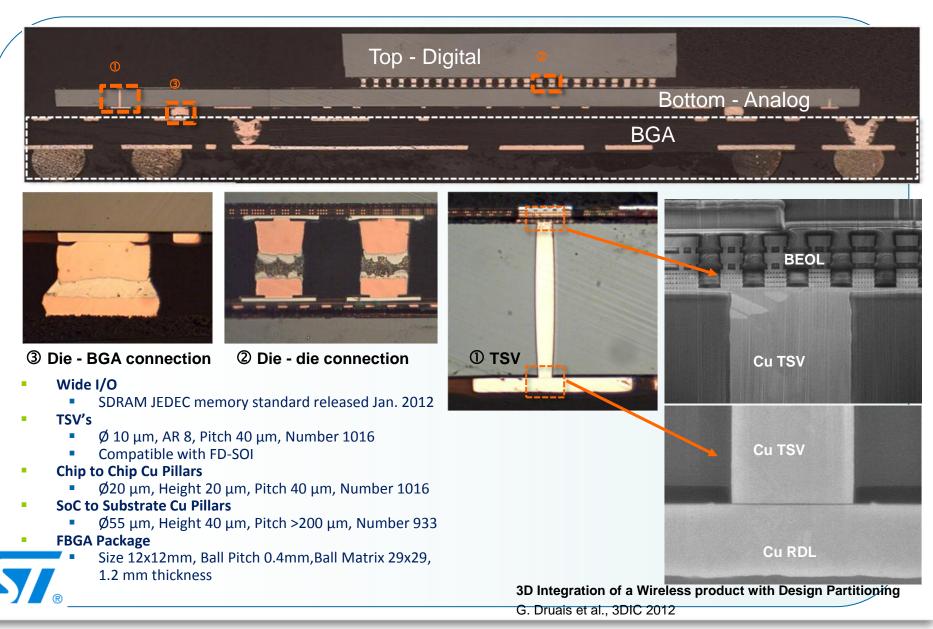

#### **Product example : Active interposer**

3D activities @ CEA-LETI / CERN Workshop / 24-01-2013- D.Henry | 50

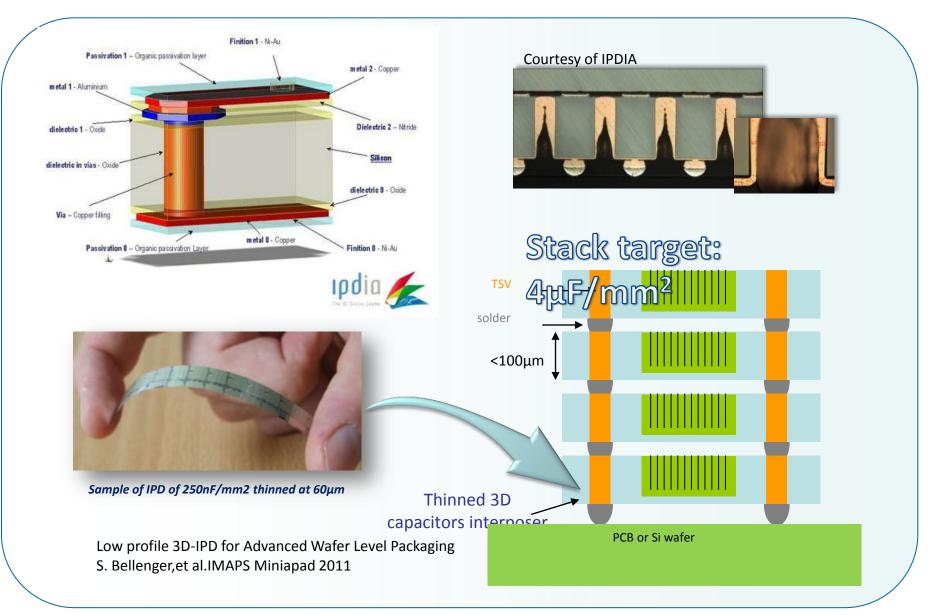

#### **Product example : Ultra thin 3D capacitors stacking**

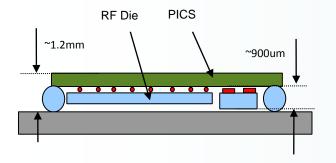

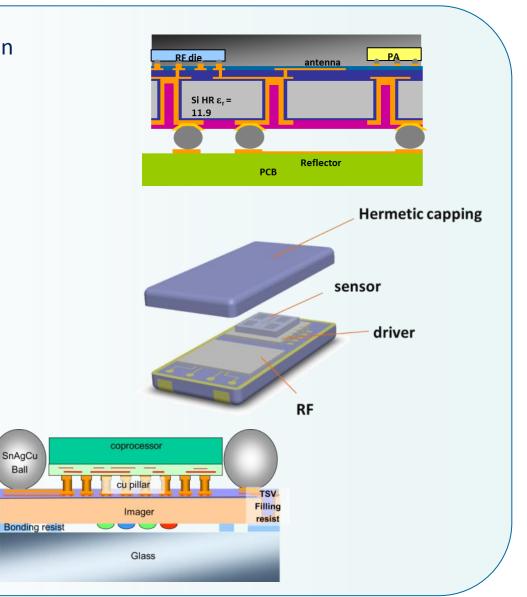

## **Product example : Other products in development @ LETI**

- Mobile

- Automotive

- Telecom

- Defense / space

- Smart interposer for medical :

- Implantable system

- 3D Imager

- Visible imager + coprocessor

- Packaging : BGA

#### Outline

- Introduction

- Medipix 3 project status

- 3D Technological toolbox @ LETI

- Available technologies / short term projects

- Technological modules developments / Mid & long term projects

- Products examples

- Conclusions / prospects

## **Conclusions / Prospects**

## Conclusions :

- LETI has a very long experience in 3D technologies developments

- We applied successfully our technologies on the wafers of the Medipix 3 project

- Generally speaking, the philosophy of the 3D developments @ LETI is :

- To create a technological toolbox supporting by R&D projects

- To applied those technologies on our customer products

- To open the "already developed" technologies for other customers

- To collaborate with material & equipment suppliers in order to access to advanced tools & materials

#### Prospects :

- To fill our toolbox with new technological modules by using new collaboration and R&D projects

- To Open our technologies access through our Open 3D<sup>™</sup> platform

# -

LABORATOIRE D'ÉLECTRONIQUE **ET DE TECHNOLOGIES DEL'INFORMATION**

www.leti.fr

# Thank you for your attention

range distants or provides attacted