# LAPP BPM Read-out Electronics

Louis Bellier, Jean Tassan, Sébastien Vilalte

### Foreseen equipments

For April, LAPP electronics to be installed:

**TL2:** 6 analog + digital for BPIs.

5 digital for 40mm BPMs (analog provided by CERN).

2 digital for BPR & WCM.

**TL2':** 4 digital for 40mm BPMs (analog provided by CERN).

**TBL:** 2 digital for 40mm BPMs (analog provided by CERN).

**TBTS:** 10 analog + digital for Uppsala 40mm BPMs.

Total of 16 analog modules and 29 digital front-end.

## Foreseen equipments: racks

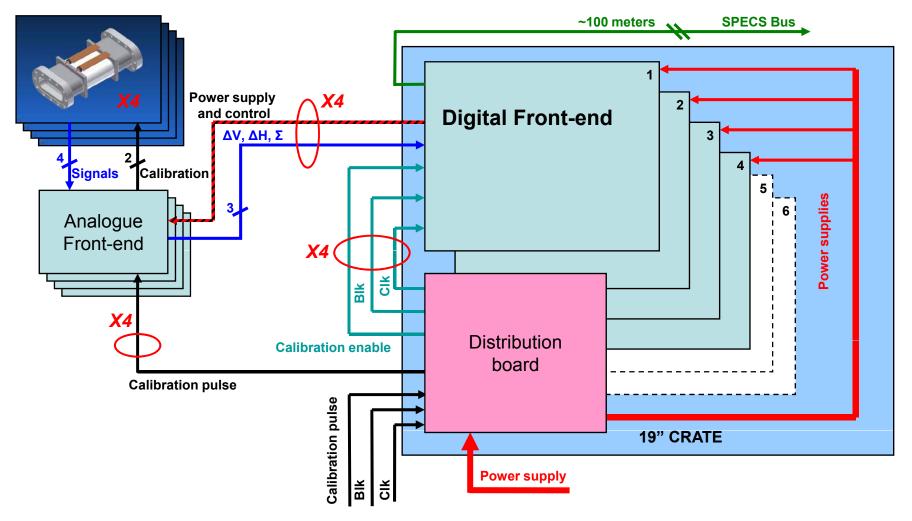

The digital front-end boards can be grouped up to 6 due to the Ethernet daisy chain link  $\rightarrow$  *use of 19" racks*.

A rack can host up to 6 digital boards and an extra distribution board provides signals: power supplies, clock, blocking, calibration.

→ divides the number of cables.

For TL2/CLEX we will group 4 boards in each rack

- → 9 racks to be installed under the girders.

See Lars Søby for layouts.

- → 2 possible remaining boards in a rack.

Lapp provides all cables from analog modules to DFE and from distribution board to DFE.

#### **Architecture**

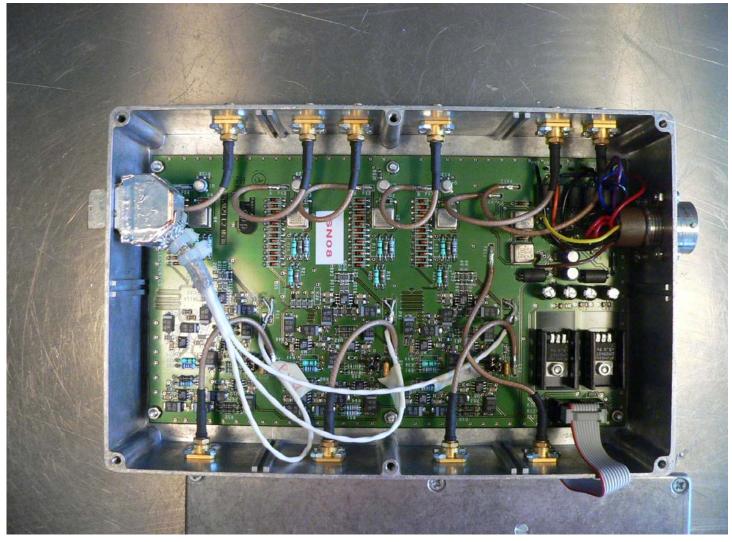

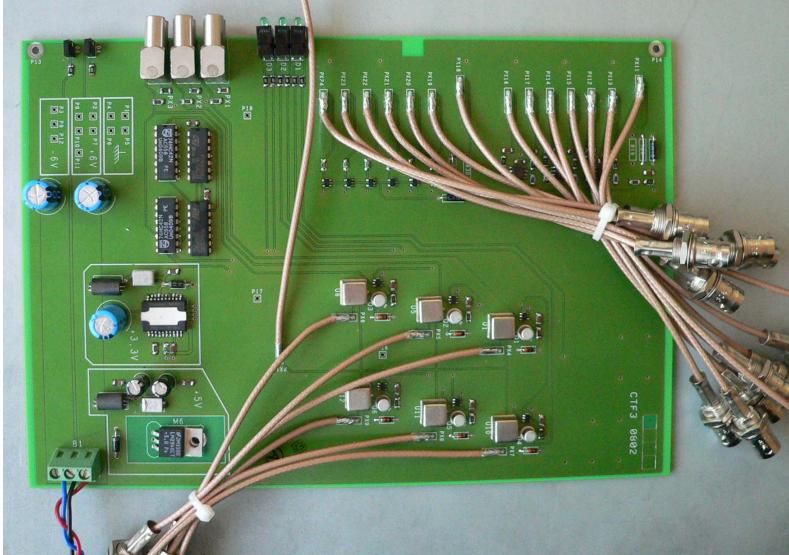

# Analogue Front-end

## Distribution board

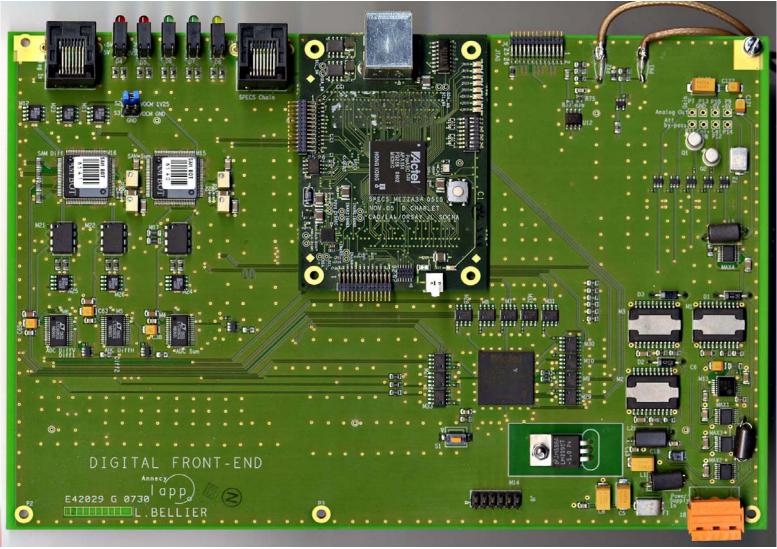

# Lapp Digital front-end board

## Specs PCI Board

ANALOG MODULES: 16 modules, 20 in production  $\rightarrow$  4 spares.

- boards currently in wiring.

- mechanical engineering ok.

- compensation filters and gains to be implemented and tested (BPM ≠ BPI)

- All cables already ordered or received.

after assembling, individual tests of signal processing with controls switching.

**DIGITAL FRONT-END**: 28 boards needed for 2008 but 50 in production

- → 43 foreseen for the whole machine and 7 spares.

- boards currently in wiring.

- front panels currently in production.

- software issues: adjustments and improvements to be performed on a first 4 boards rack according to the read-out system (network, FESA framework...).

Implementation of a blocking delay control for each board.

Louis Bellier is leaving end january: LAPP supports digital activities with the aid of a part-time digital electronics technician Jean Marc Nappa.

RACKS AND DISTRIBUTION: 9 racks, 9 distribution boards,

11 foreseen in production → 2 spares.

- racks ordered. To be assembled at reception. power supplies distribution to be implemented.

- front panels currently in production.

- tests with 4 and 6 digital boards to be finalized.

- All cables already ordered or received.

#### SOFTWARE APPLICATIONS: Jean Jacquemier

To drive the front-end and plot data, LAPP develops two applications :

- A JAVA application dedicated to the control of DFE: "specialist requirements" (gain, attenuation, blk delay...).

- The acquisition application on the gateway FESA server.

A third, "trajectory", a JAVA application to be defined.

#### Dates and conclusions

#### **MILESTONES**:

- We foresee a full rack for debug for end February.

- $\rightarrow$  test of an acquisition chain from pick-up to control room display.

- 9 racks for April with final versions of DFE soft and a first version user applications.

CONCLUSION: though the work still to provide, we think we will be on time for the beam.