# TBL BPM Electronics: Amplifier Status and Future Work

Gabriel Montoro<sup>(1)</sup>, Antoni Gelonch, Youri Koubychine Universitat Politècnica de Catalunya (UPC) <sup>(1)</sup>email: montoro@tsc.upc.edu

This work has been supported by the Spanish Government (MEC) under project FPA2005-25366-E

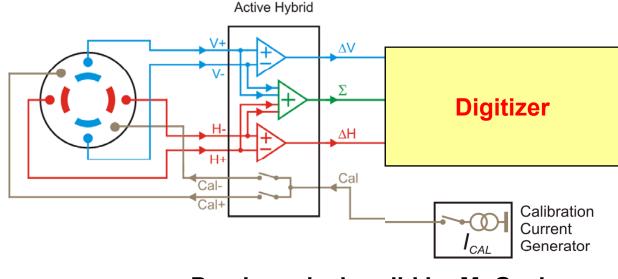

### General scheme of the analog head electronics

- The signals (V+,V-, H+ and H-) sensed by the IPU must be processed in order to obtain the signals difference and sum before being digitized.

- It must work as a digitizer front-end.

Previous design did by M. Gasior

| Tentative parameters of the BPMs for the TBL                        |                                                                   |

|---------------------------------------------------------------------|-------------------------------------------------------------------|

| <b>BPM analog bandwidth</b><br>(BPM with associated<br>electronics) | <u>10 kHz -100 MHz</u><br>(200 MHz is highly<br><u>desirable)</u> |

| Beam position range of interest                                     | +/-5 mm horizontal and vertical                                   |

| Beam aperture diameter                                              | 22.5 mm                                                           |

| Overall mechanical length                                           | < 100 mm                                                          |

| Number of BPM's in TBL                                              | 16                                                                |

| Resolution at maximum current                                       | <5 µm                                                             |

| Overall precision                                                   | <50 µm                                                            |

| Typical radiation levels                                            | <1000 Gray/year (or 100 Krads)                                    |

The BPM design for the DBL by M. Gasior cannot be applied directly. Modifications are required:

- a) The dimensions of the IPU should be reduced

- b) The amplifier bandwidth should be increased (desired up to 200 MHz)

### **Inductive pick-up**

Η

V

### **Analog front-end electronics**

MechanicsIPU electronics

•Amplifier

### **BPM Analog amplifier for the TBL**

Work done:

- 1. Specifications of the interface between the analog amplifier and the digitizer (developed by LAPP researchers) have been defined.

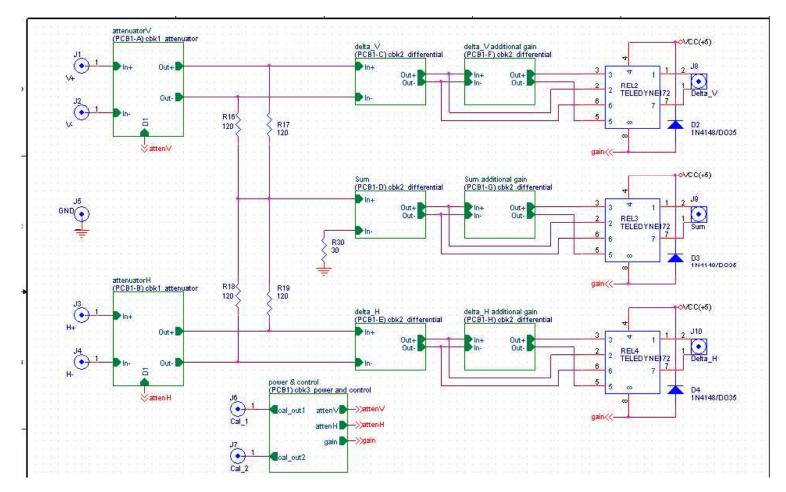

- 2. Design and schematics of the amplifier.

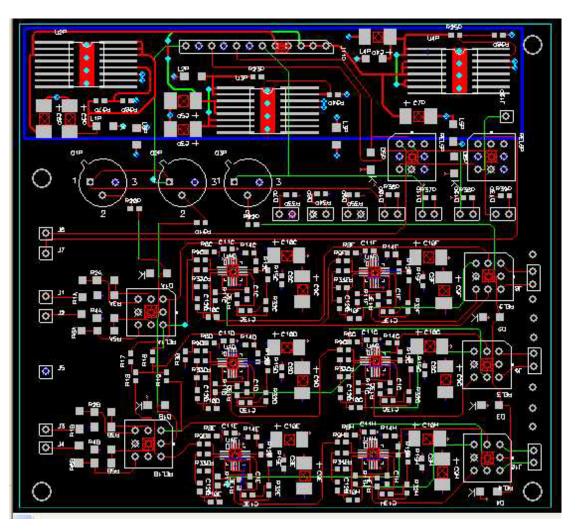

- 3. CAD design of the PCB and manufacturing.

- 4. Building and some tests in the UPC lab.

- 5. First tests in CERN.

# Specifications of the interface between the analog amplifier and the digitizer

The following information was obtained from the LAPP group:

- The analog outputs must be bipolars.

- Levels: +-0,75V max.

- The power and control connector pinout has been determined.

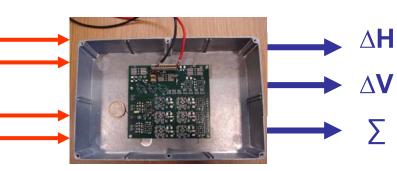

- The signal output must consist in 3 double (balanced) signals: 1 sum and 2 differences.

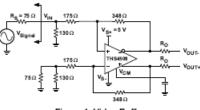

# Schematics done according to the previous specifications

# The CAD design of the PCB has been also finished

### The Bill Of Materials (BOM)

Item Quantity Reference Part Footprint Manufacturer Distributor Price

18 C1H,C1G,C1F,C1E,C1D,C1C,C8H,C8G,C8F,C8E,C8D,C8C,C11H,C11G,C11F,C11E,C11D,C11C 100n SMD0603 1 2 6 C2P, C3P, C4P, C5P, C6P, C7P 22u EIA-6032-28 3 12 C9H,C9G,C9F,C9E,C9D,C9C,C10H,C10G,C10F,C10E,C10D,C10C 1u EIA-6032-28 4 12 C12H, C12G, C12F, C12E, C12D, C12C, C13H, C13G, C13F, C13E, C13D, C13C CAP-NP/0603 SMD0603 5 7 D1B, D1A, D2, D3, D4, D5P, D6P 1N4148/D035 D035 6 7 D7P, D8P, D9P, D10P, D11P, D12P, D13P LEDPCB2/PIN 2PIN 7 1 J1 V+ 1PIN 1 J2 V- 1PIN 8 9 1 J3 H+ 1PIN 10 1 J4 H- 1PIN 11 1 J5 GND 1PIN 12 1 J6 Cal 1 1PIN 13 1 J7 Cal 2 1PIN 14 1 J8 Delta V 2PIN 15 1 J9 Sum 2PIN 16 1 J10 Delta H 2PIN 17 1 J11P CONPCB12/PIN 12PIN 100MIL 18 1 J12P CALIN 1PIN 19 6 L1P, L2P, L3P, L4P, L5P, L6P EMI IND SMD1206 20 3 Q1P, Q2P, Q3P IRHLF770Z4/T039 T039 21 7 REL1B, REL1A, REL2, REL3, REL4, REL5P, REL6P TELEDYNE172 TELEDYNE172 22 12 R1B, R1A, R2B, R2A, R3B, R3A, R4B, R4A, R5B, R5A, R6B, R6A R/1206 SMD1206 23 12 R7H, R7G, R7F, R7E, R7D, R7C, R15H, R15G, R15F, R15E, R15D, R15C 348 SMD0603 24 12 R8H, R8G, R8F, R8E, R8D, R8C, R14H, R14G, R14F, R14E, R14D, R14C 287 SMD0603 25 12 R9H, R9G, R9F, R9E, R9D, R9C, R12H, R12G, R12F, R12E, R12D, R12C 16.5 SMD0603 26 12 R10H, R10G, R10F, R10E, R10D, R10C, R13H, R13G, R13F, R13E, R13D, R13C 50 SMD0603 27 6 R11H, R11G, R11F, R11E, R11D, R11C 100 SMD0603 28 4 R16, R17, R18, R19 120 SMD0603 29 21 R2OP, R21P, R22P, R23P, R24P, R25P, R26P, R27P, R28P, R31H, R31G, R31F, R31E, R31D, R31C, R32H, R32G, R32F, R32E, R32D, R32C 30 1 R30 30 SMD0603 31 7 R33P,R34P,R35P,R36P,R37P,R38P,R39P 1K SMD0603 32 6 U1H, U1G, U1F, U1E, U1D, U1C THS4508 QFN16 TI TI 6 33 1 U2P RHFL7913A FLAT16 34 2 U3P, U4P RHFL4913 FLAT16

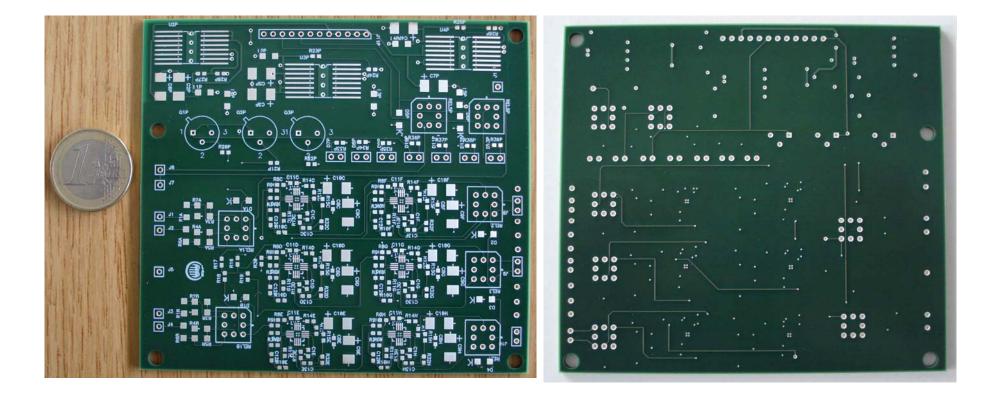

### **The 6-layers manufactured PCB**

### TOP

### BOTTOM

### The most critical components: IC amplifier

Rad-hard wideband IC amplifier: THS4508 (manufactured by TI and tested by up to 100 Krads).

Status:

We have received some samples from AVNET-SILICA (a TI distributor). It's possible to buy this IC online at Farnell distributor website.

####

×,

THS4508

SLAS469D-SEPTEMBER 2006-REVISED MAY 2007

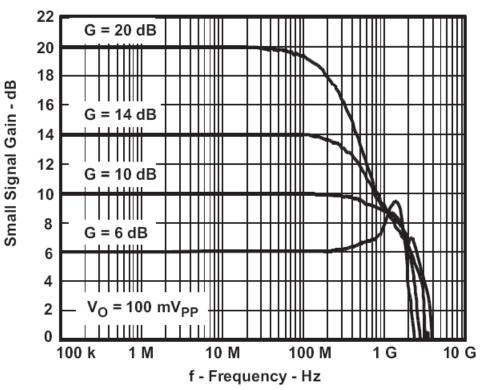

#### WIDEBAND, LOW NOISE, LOW DISTORTION FULLY DIFFERENTIAL AMPLIFIER

#### **FEATURES**

- Fully Differential Architecture

- Common-Mode Input Range Includes the Negative Rail

- Minimum Gain of 2 V/V (6 dB)

- Bandwidth: 2 GHz

- Slew Rate: 6400 V/µs

- 1% Settling Time: 2 ns

- HD<sub>2</sub>: –72 dBc at 100 MHz

- HD<sub>3</sub>: –79 dBc at 100 MHz

- OIP<sub>2</sub>: 78 dBm at 70 MHz

- OIP<sub>3</sub>: 42 dBm at 70 MHz

- Input Voltage Noise: 2.3 nV/\/Hz (f > 10 MHz)

- Noise Figure: 19.2 dB (G = 10 dB)

- Output Common-Mode Control

- 5-V Power Supply Current: 39.2 mA

- Power-Down Capability: 0.65 mA

#### **APPLICATIONS**

- 5-V Data-Acquisition Systems

- High Linearity ADC Amplifier

- Wireless Communication

- Medical Imaging

- Test and Measurement

#### DESCRIPTION

The THS4508 is a wideband, fully-differential operational amplifier designed for single-supply 5-V data-acquisition systems. It has very low noise at 2.3 nV/NFZ, and extremely low harmonic distortion of -72 dBc HD<sub>2</sub> and -79 dBc HD<sub>3</sub> at 100 MHz with 2 V<sub>pp</sub>, G = 10 dB, and 1-kΩ load. Slew rate is very high at 6400 Vµs and with setting time of 2 ns to 1% (2 V step) it is ideal for pulsed applications. It is designed for minimum gain of 6 dB, but is optimized for gain of 10 dB.

To allow for dc coupling to ADCs, its unique output common-mode control circuit maintains the output common-mode voltage within 5-mV offset (typical) from the set voltage, when set within 0.5 V of mid-supply. The common-mode set point is set to mid-supply by internal circuitry, which may be over-driven from an external source.

The THS4508 is a high-performance amplifier that has been optimized for use in high performance, 5-V single supply data acquisition systems. The output has been optimized for best performance with its common-mode voltages set to mid supply, and the input has been optimized for best performance with its common-mode voltage set to 0.7 V. High performance at a low power-supply voltage makes for high-performance single-supply 5-V data-acquisition systems with a minimum parts count. The combined performance of the THS4508 in a gain of 10-dB driving the ADS5500 ADC, sampling at 125 MSPS, is 82-dBc SFDR, and 68.3-dBc SNR with a -1-dBFS signal at 70 MHz.

The THS4508 is offered in a Quad 16-pin leadless QFN package (RGT), and is characterized for operation over the full industrial temperature range from  $-40^{\circ}$ C to  $85^{\circ}$ C.

#### SMALL-SIGNAL FREQUENCY RESPONSE

### The most critical components: regulators

- RHFL4913 (positive regulator). Tested up to 100 Krads by the manufacturer, ST.

- RHFL7913A (negative regulator). Tested up to 100 Krads by the manufacturer, ST.

Status:

- These IC's are manufactured by ST.

- The RHFL4913 and the RHFL7913A can be obtained with the help of CERN (available at CERN store): these regulators are considered to be used in the ATLAS experiment.

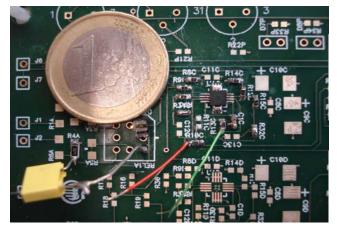

### **BPM Amplifier: UPC Lab tests**

UNIVERSITAT POLITÈCNICA DE CATALUNYA

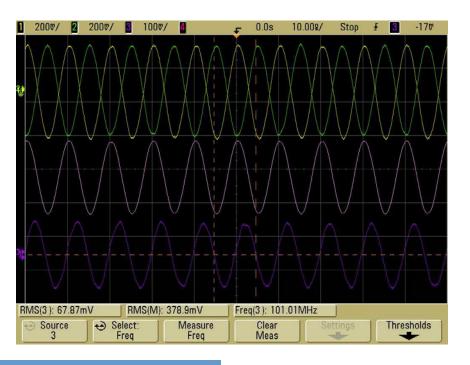

### UPC Lab. tests: Testing one channel

- Maximun gain of each stage: 10

- Measured bandwidth: up to 200 MHz.

- Input impedance of: 50 ohms ? (It will require a fine measurement and tunning).

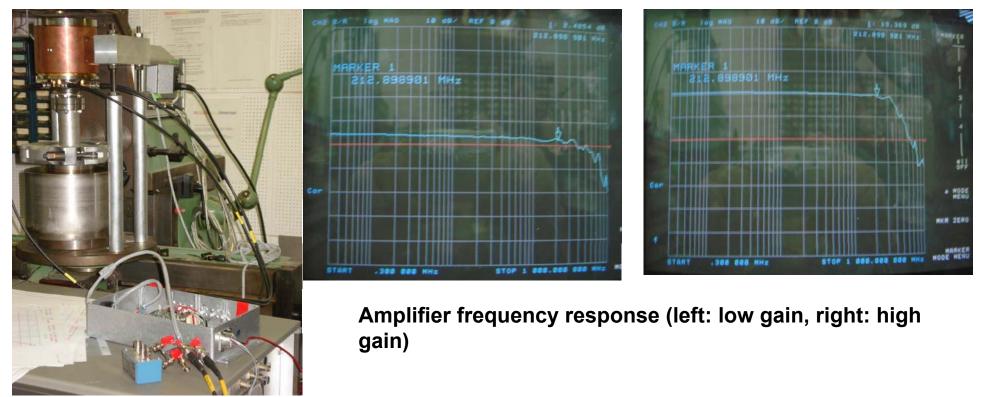

## First CERN testings: 10th December 2007

#### **UPC Amplifier + CERN test-bench**

Thanks to Lars Soby for his collaboration !!!

## Results

- The results, afther the testings in CERN, show that the amplifier is accomplishing the main electronic requirements:

- The gain (up to 10 or less) is OK.

- The bandwidth (up to 200 MHz) is OK.

- The output level can be accomplished: OK.

- ... but there are some improvements to do:

- Some input impedance decoupling was detected and must be adjusted to match 50 ohms.

- Some delay diferencies between channels must be compensated.

- The gain must be adjusted to meet the real IPU signal levels.

## Future work-project

- We have presented (last december) a project to the Spanish Ministry to request a Grant for finishing the amplifiers: to build 16+2 (for replacement).

- Our first scheduled action is to build 2 amplifiers during the first half (March ?) of 2008 (now, we have 1 quasi-finished).

# TBL BPM Electronics: Amplifier Status and Future Work

Gabriel Montoro<sup>(1)</sup>, Antoni Gelonch, Youri Koubychine Universitat Politècnica de Catalunya (UPC) <sup>(1)</sup>email: montoro@tsc.upc.edu

This work has been supported by the Spanish Government (MEC) under project FPA2005-25366-E