# Test Automation of 3D Integrated Systems

Stephen Pateras Mentor Graphics Corporation July 16<sup>th</sup>, 2013

# Agenda

#### Basic semiconductor test concepts

- Scan test

- Design-for-Test (DFT)

- Built-In Self-Test (BIST)

## 3D-IC Testing

- New challenges

- Known-Good-Die (KGD)

- Test access for stacked die

- Testing die within 3D stack

- Testing TSV connections between stacked die

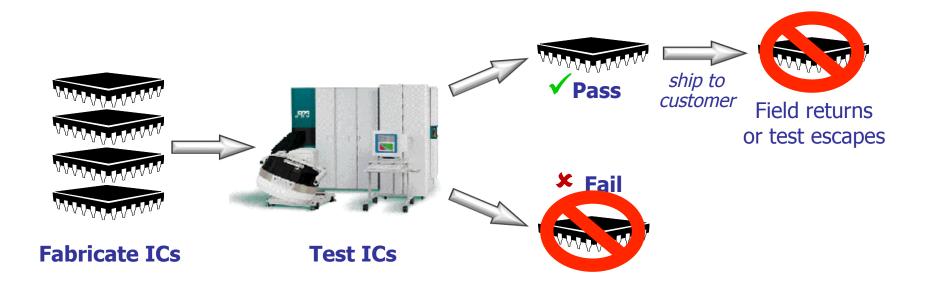

# Semiconductor Test – In a Nutshell

- Process to ensure fabricated IC works correctly

Tester applies stimulus to input and examines output data

- Test automation: input patterns and expected output data generated automatically

- Need to maximize defect detection and minimize patterns

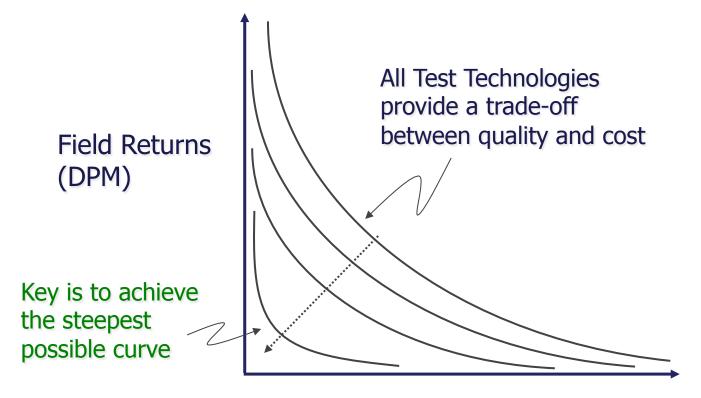

# **Field Returns vs Test Cost Correlation**

Test Cost

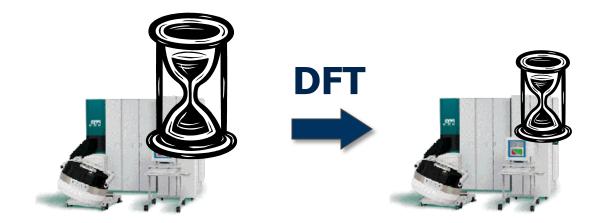

# **Design-For-Test (DFT)**

- Circuit modification and/or additions to make IC easier to test

- $-\operatorname{Scan}$  for ATPG

- Built-In Self-Test (BIST): all testing done on chip

#### **Reduced test time and hence cost**

#### Scan Design

#### Internal scan is a structured DFT technique that

- Replaces sequential storage elements with scan cells

- Stitches scan cells into a serial scan register (scan chain)

- Makes sequential circuitry appear combinational

#### Structural test technique

- Directly tests circuit structure rather than higher-level function

- Easier to automate

- Enables standardized defect coverage metrics

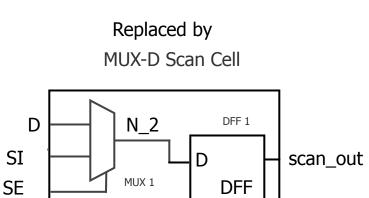

#### **Mux DFF Scan Cell**

- Multiplexer selects data input:

- D in normal mode

- Scan\_in (SI) scan mode

- Scan\_enable (SE) selects mode of operation

Q

CLK

- Increased propagation delay

- Adds 5-15% area overhead

Original

Flip-Flop

Standard approach today

D

CLK .

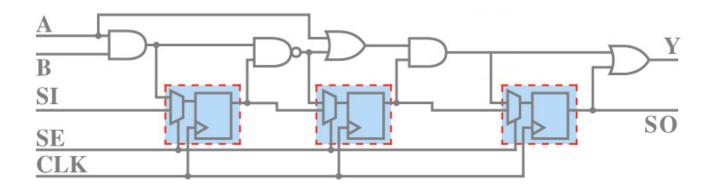

#### **Scan Chains**

Scan\_Enable (SE):

— When active allows scan data to enter the registers.

- Scan input port (SI):

- Data is loaded into scan cells.

- Scan output port (SO):

Data is read by shifting data out.

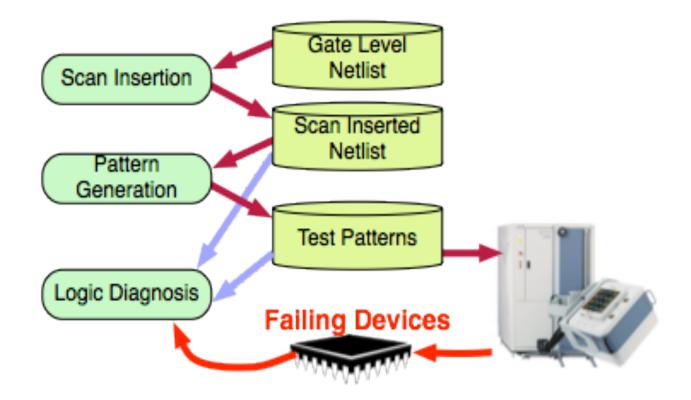

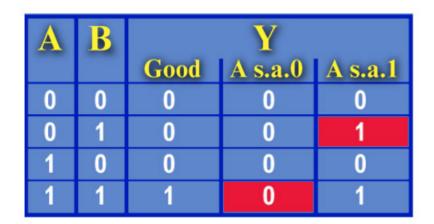

# **Typical ATPG Flow**

#### ATPG: Automatic Test Pattern Generation

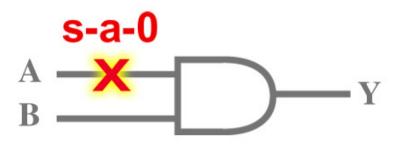

#### **Stuck-At Fault Model**

- Fault models are logic targets for defects.

- A fault is detected:

- When a difference is observed between a "good" and "faulty" circuit.

- Most defects are detected with the stuck-at fault model.

- A terminal of a gate is permanently stuck-at 0 or 1.

- Also detects other defects:

- Opens

- Shorts

- Bridging faults

- Others...

10

# **Fault Model Progression**

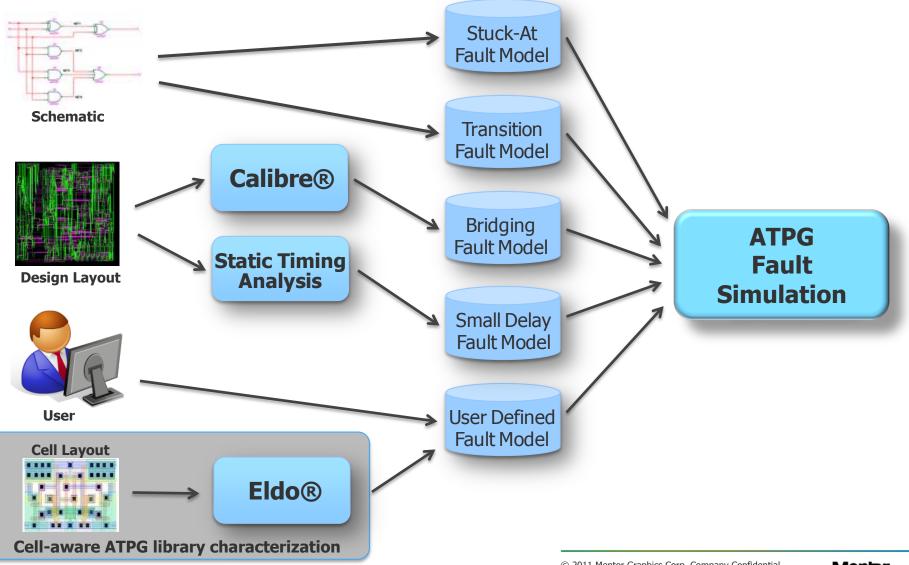

# Boundary Scan – IEEE 1149.1 Standard

# **Embedded Test IP - BIST**

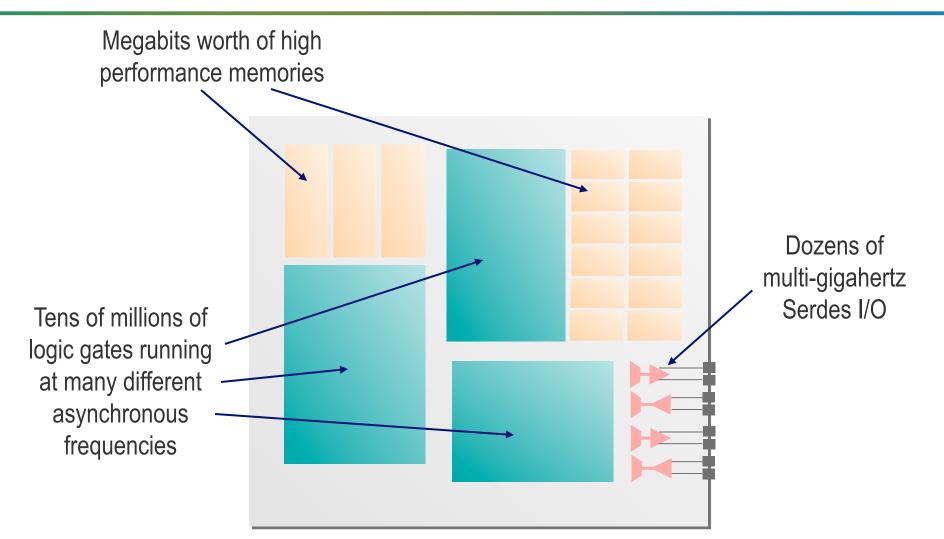

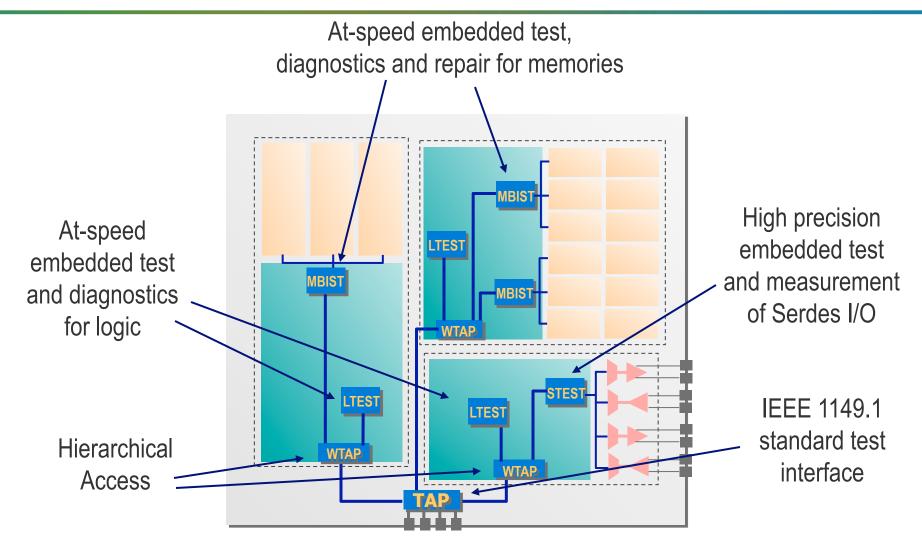

# **Embedded IP Architecture**

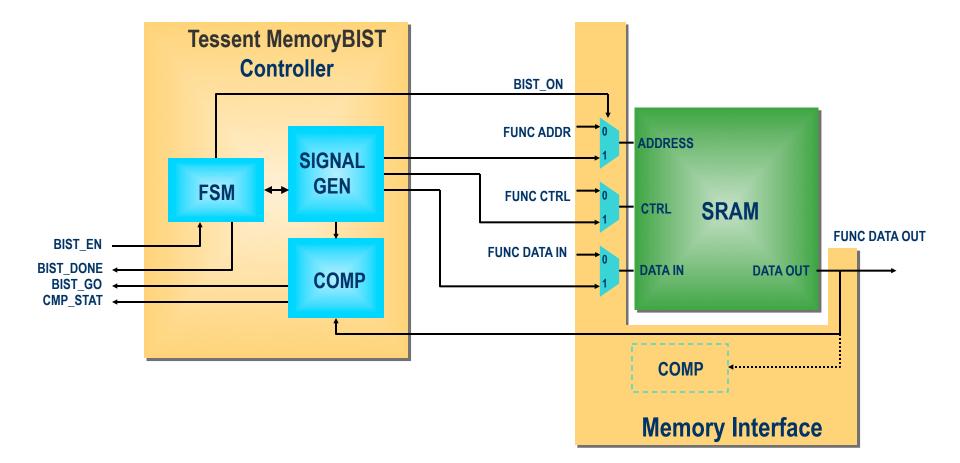

# **Memory BIST – Basic Architecture**

# **Logic Test Solutions**

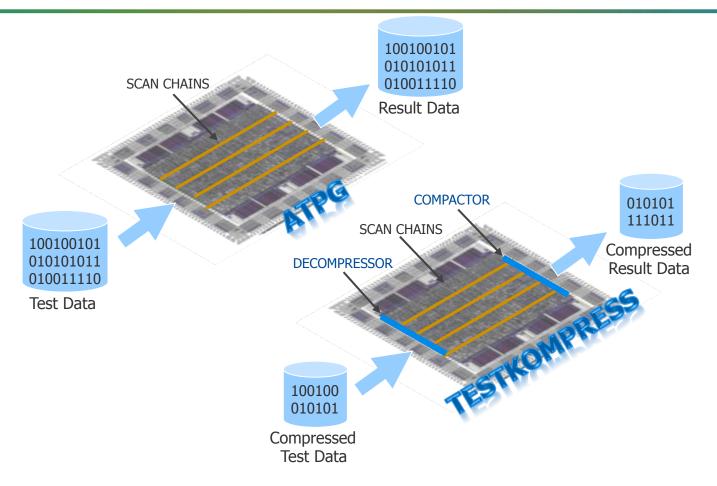

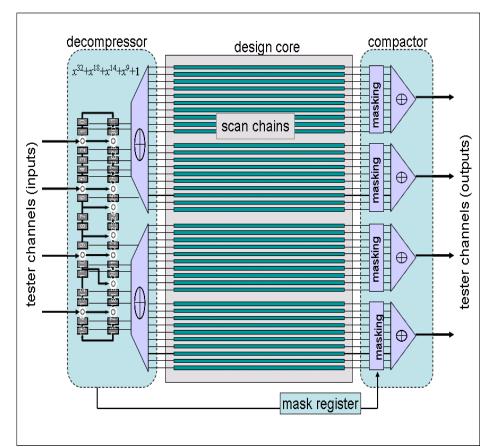

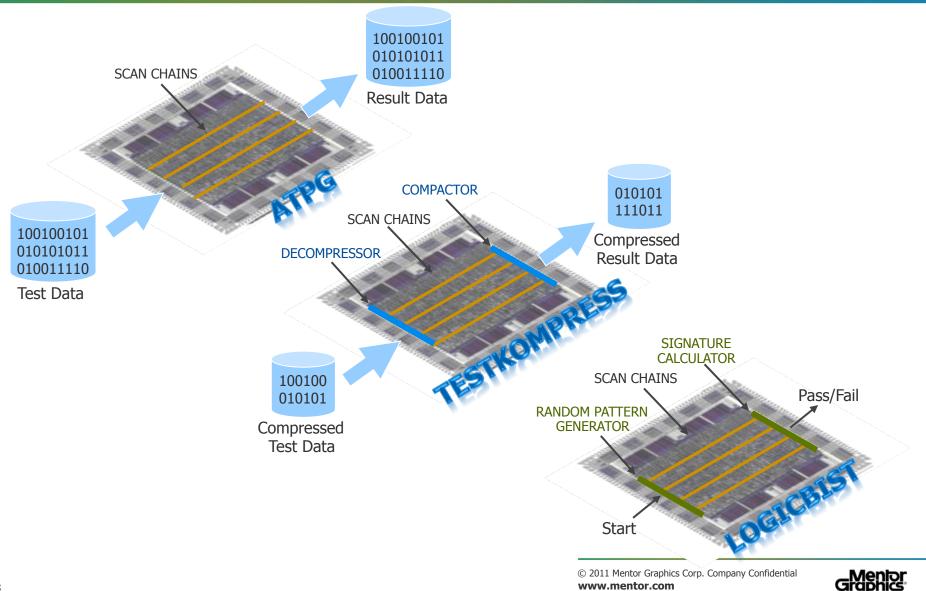

# **ATPG Compression Technology**

- Use logic to convert compressed tester stimulus to many short internal chains

- Cycles/time to load each pattern dramatically reduced

- 100X time & data compression enables higher test quality

- Patented X-masking ensures no loss in test coverage

# **Logic Test Solutions**

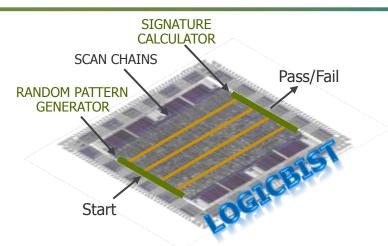

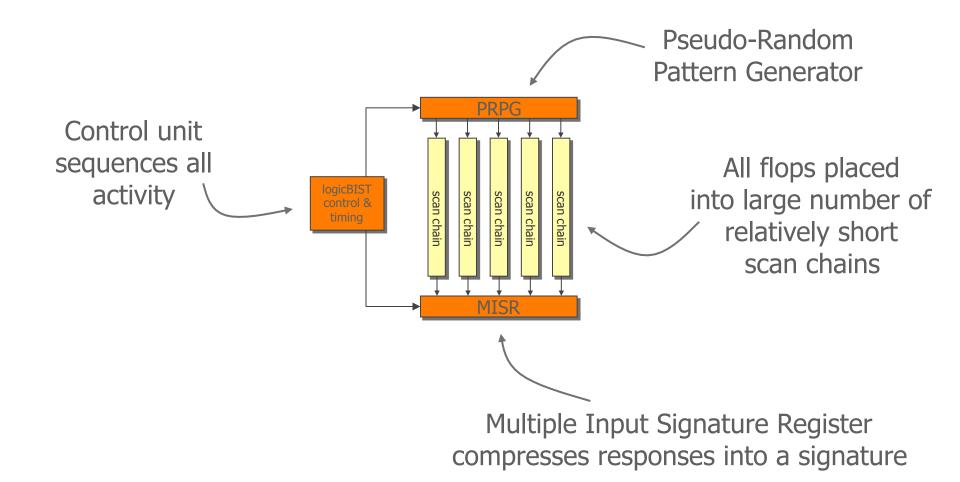

# **Logic BIST Overview**

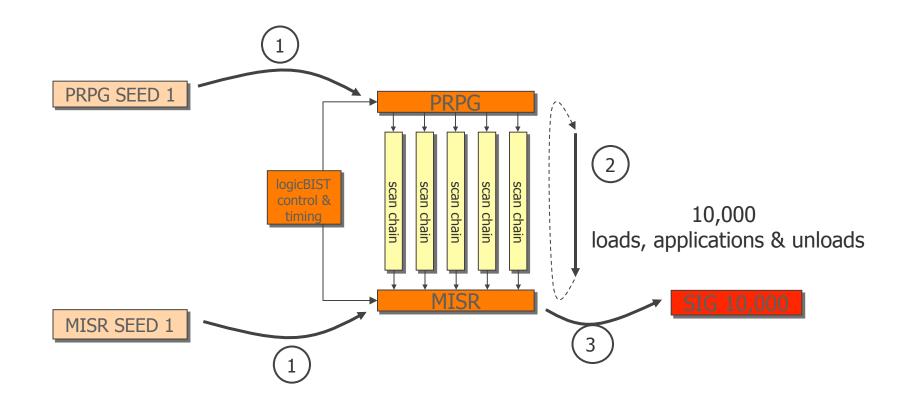

- On-chip random pattern generator (PRPG) creates test patterns on the fly

- On-chip signature calculator (MISR) accumulates all response data into single pass/fail signature

- Uses same scan architecture as ATPG

- Eliminates the need for stored patterns

- Not limited by tester memory or clock speed

- Perfect for test reuse and in-system test applications

- Addresses mil-aero, medical and automotive POR test requirements

## **Logic BIST –** Basic Architecture

#### Logic BIST – Test Sequence

# **3D-IC TEST**

# **3D IC Test Challenges**

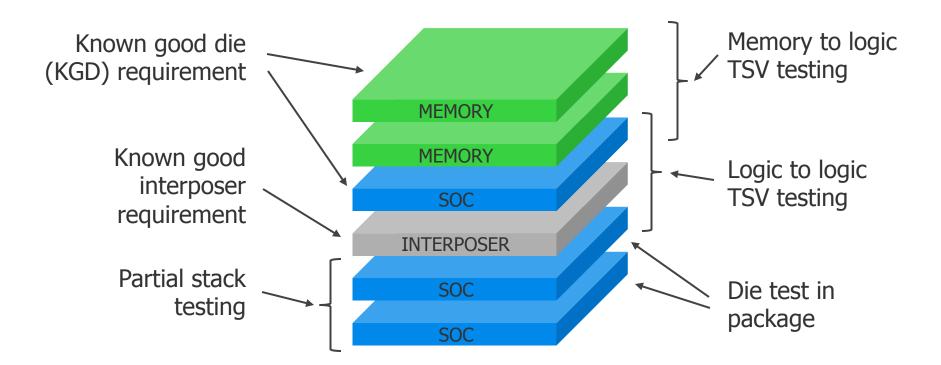

# ENSURING KNOWN GOOD DIE

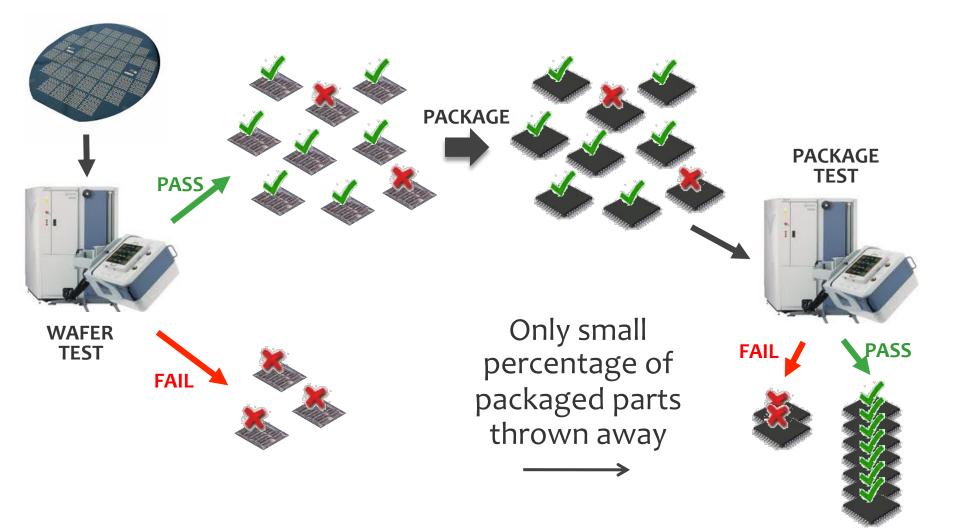

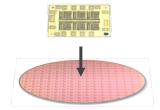

#### Wafer vs Package Test – Before 3D

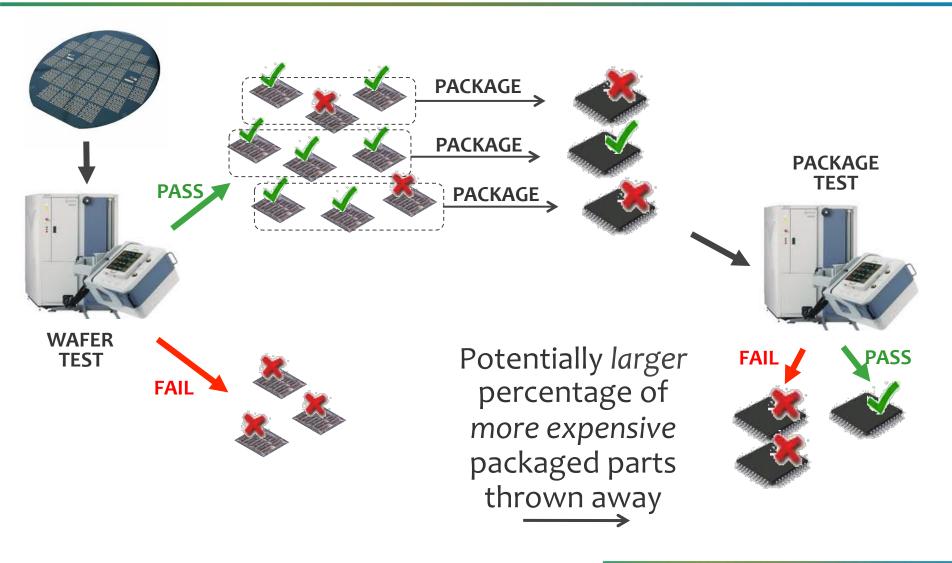

## Wafer vs Package Test – With 3D

# **Stacking Approaches**

#### Wafer-to-wafer (W2W) Bonding

Die-to-wafer (D2W) Bonding

Works only with homogeneous die

Very difficult to control individual stack yield

Necessary for heterogeneous stacked die

Stack yield controlled with KGD and partial stack testing

# **Known Good Die Requirement**

Die Defect Coverage =

$DC_D$

Bare die Low Cost Final Package Yield = II DC<sub>Di</sub>

3D Stack High Cost ... For 10 Die Stack:

| $DC_D$ | $\Pi \text{ DC}_{\text{Di}}$ |

|--------|------------------------------|

| 90%    | 35%                          |

| 95%    | 60%                          |

| 99%    | 90%                          |

| 99.9%  | 99%                          |

Still 10 times more wasted packages and test time

# **Known Good Die Requirement**

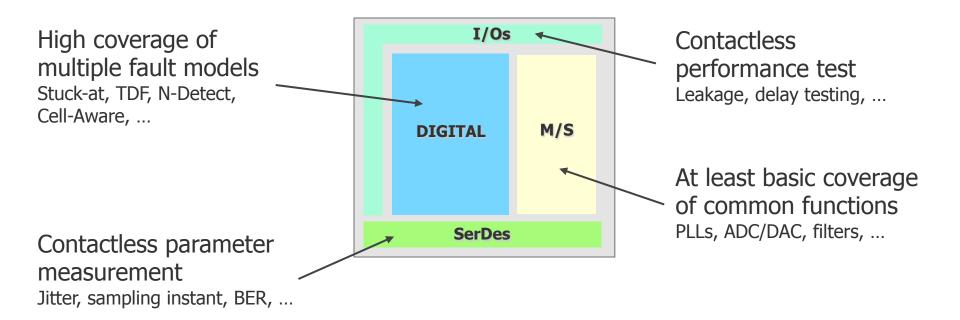

Need comprehensive wafer test coverage

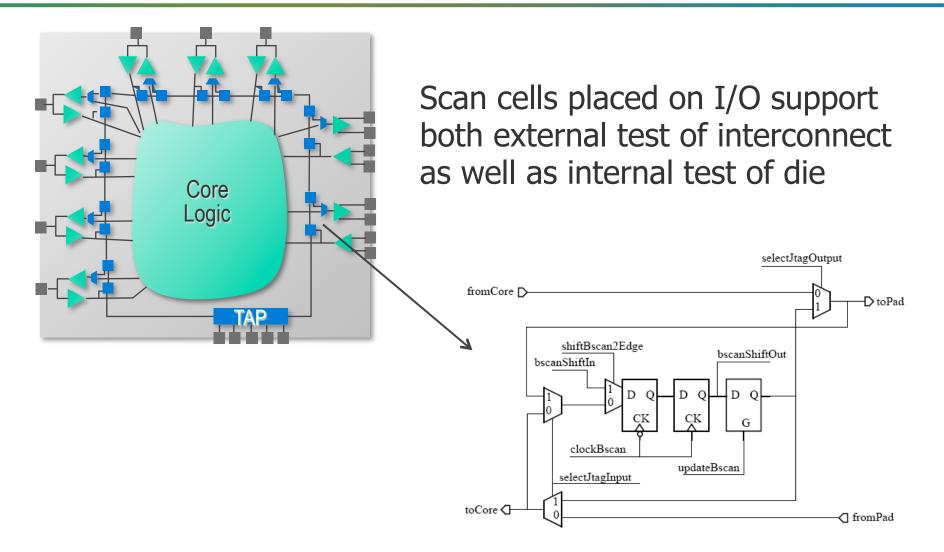

## High Logic Defect Coverage Transistor Level (Cell-Aware) ATPG

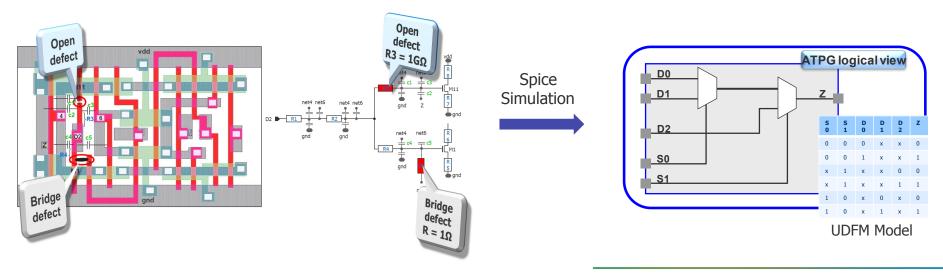

# Methodology for improving detection of defects internal to standard cells

- Layout defects mapped to transistor faults

- Spice simulation maps fault effects to UDFM model

- UDFM is generalized truth-table based fault representation

- ATPG engine enhanced to target UDFM-based faults

### **Cell-Aware ATPG** *Silicon Results - 32nm experiment*

The methodology has demonstrated an ability to target otherwise uncovered and hard-to-get-to defect sites

| Pattern Type             | #fails | DPM |

|--------------------------|--------|-----|

| Cell-aware<br>slow speed | 98     | 218 |

| Cell-aware<br>at-speed   | 268    | 597 |

#### Results from 400k tested ICs

Data source: AMD presentation at Mentor's ITC Theater 2011

# **KGD IO Test Requirements**

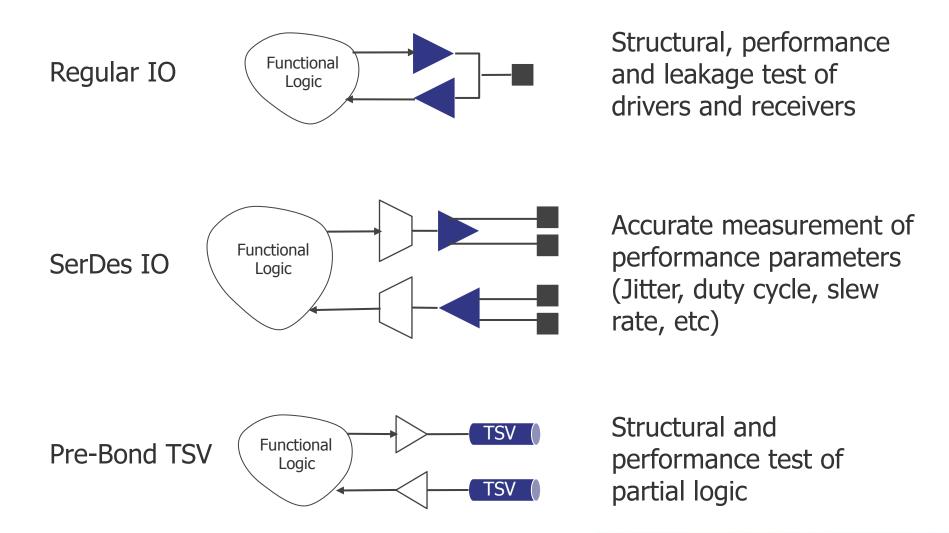

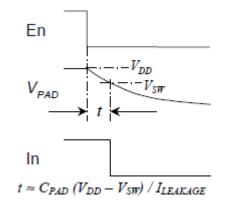

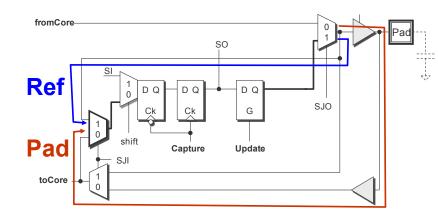

### **Contactless Test of Regular IO** Boundary Scan Based Solutions

- Test for structural I/O defects using wrap test approach

Standard Bidi Bscan cell used to drive and capture data

- Measure/test IIL, IIH, and inter-pin leakage without contacting bond pads on any tester

- IIH test procedure

- Drive pads to logic 1

- Disable drivers leakage current affects  $V_{PAD}$

- Capture pad logic values precise time later

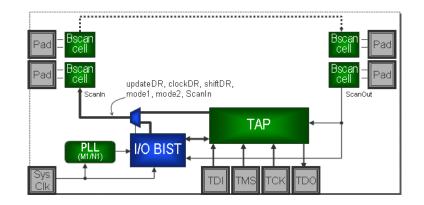

## **Contactless Test of Regular IO** IO BIST

- Propagation delay measurement using Bscan

- BIST provides high-speed Bscan control signals

- Delay-difference measurement eliminates signal propagation variations and noise

- Rise and fall delay measurement with resolution adjustable from nanoseconds to picoseconds

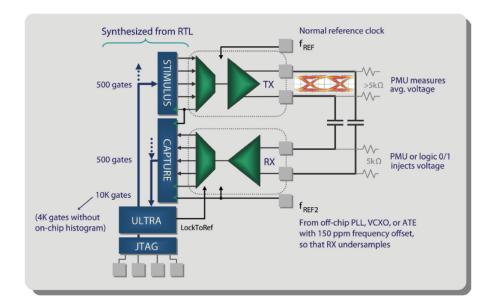

## **Contactless Test of SerDes IO** SerDes BIST

- Accurate picosecond measurements of critical parameters

- Jitter (Random, Total)

- Jitter Tolerance

- Rise/fall time, Slew rate

- RTL-based, vendor independent BIST

- No changes to physical IP under test

## **Contactless Test of SerDes IO** SerDes BIST

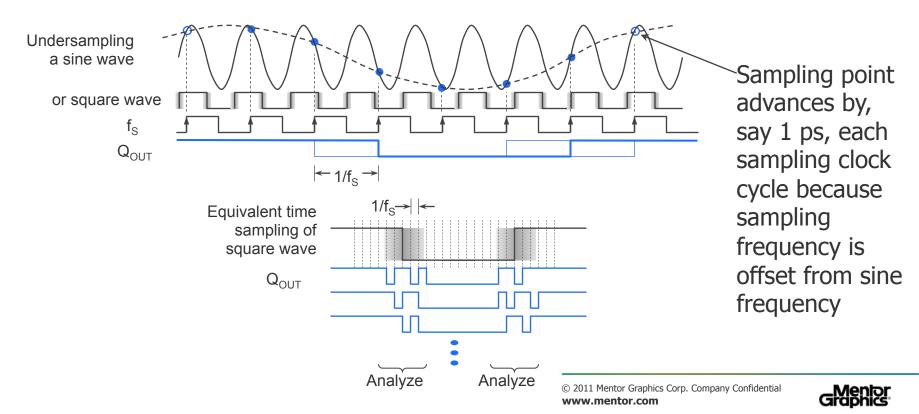

#### Undersampling-Based Approach

- Samples continuously, but only analyzes transitions

- Measures jitter and phase delays relative to median edge positions

- On-chip capture of histogram or RMS value of HF or LF jitter

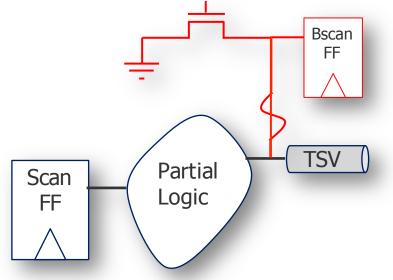

# **Contactless Test of Pre-Bond TSVs**

- All techniques described for regular IOs can be applied to pre-bond TSVs

- Boundary Scan based solutions

- IO BIST

- Extra load may be problematic due to lack of IO driver

- Fuse can be used to eliminate load after test

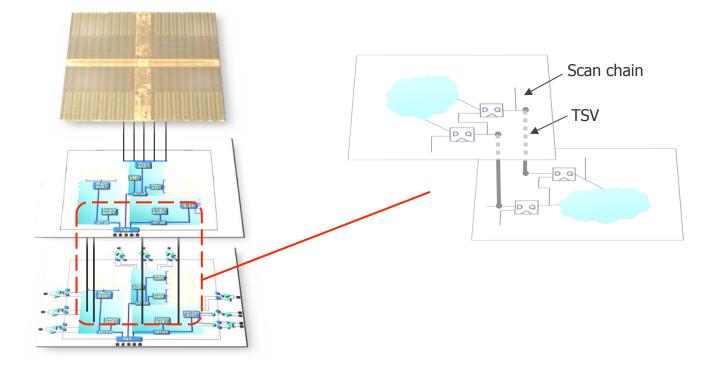

# TEST ACCESS FOR STACKED DIE

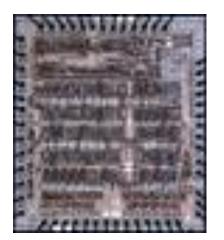

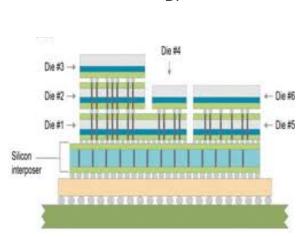

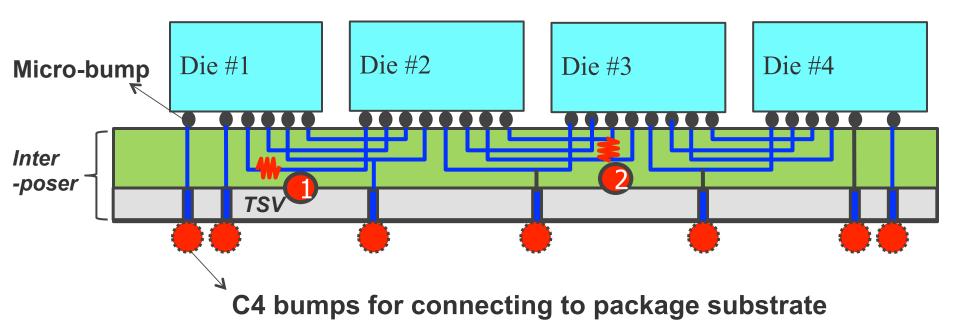

### **Generic 3D Package Components**

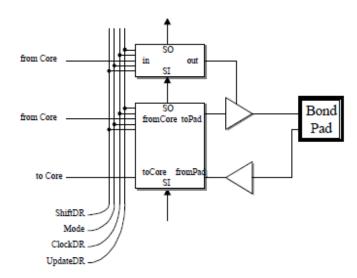

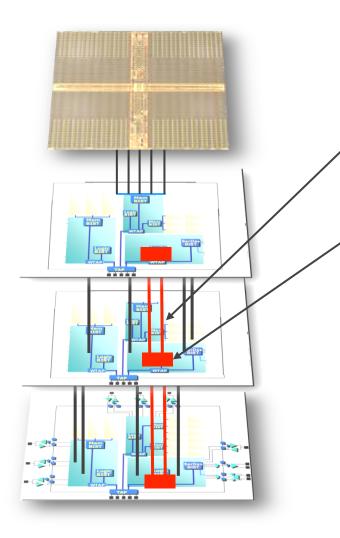

### **Test Access Within Stack**

- Dedicated TSVs used for test

signals between die

- Control hardware needed to route test data up and down stack

- Standard architecture necessary to support heterogeneous die from multiple vendors.

— IEEE P1838 under development

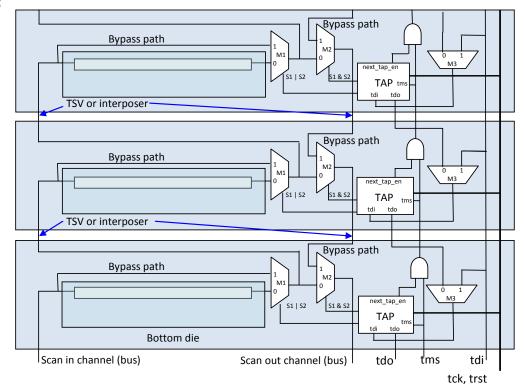

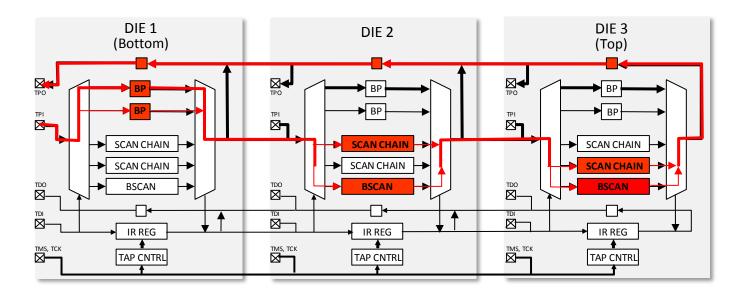

## **Mentor 3D Test Access**

#### Uses cascaded TAPs

- Each TAP can be instructed to enable the next higher TAP

- Default is bottom TAP only in path

- Standard structure for die independent of position

- Die can work directly if packaged as a standalone device

# TESTING DIE WITHIN 3D STACK

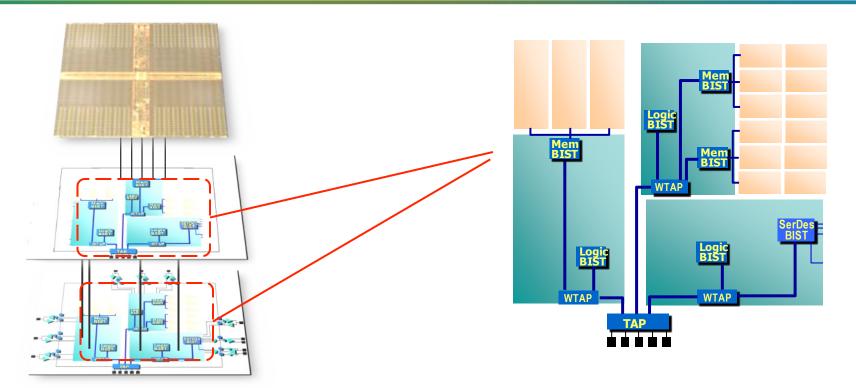

## **Die Test In-Package**

- BIST best suited for re-test of die within stack

- ATPG patterns can also be used

- Dies can be tested in parallel to minimize test time

- Screens for any new defects due to the packaging process

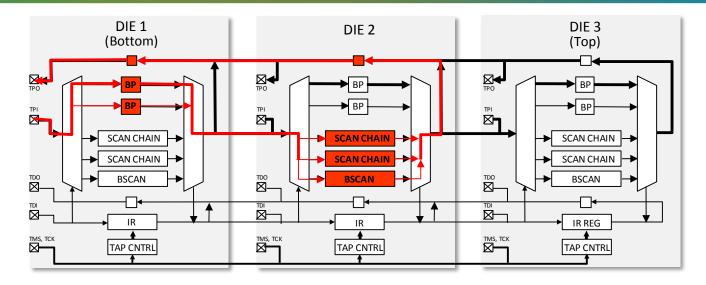

# **In-Package ATPG Application**

#### Options

- Die-level ATPG patterns generated at package level

- Full package netlist is used

- Non-targeted die are grayboxed

- Die-level ATPG patterns retargeted from wafer level

- Patterns resequenced in accordance to active bypass stages

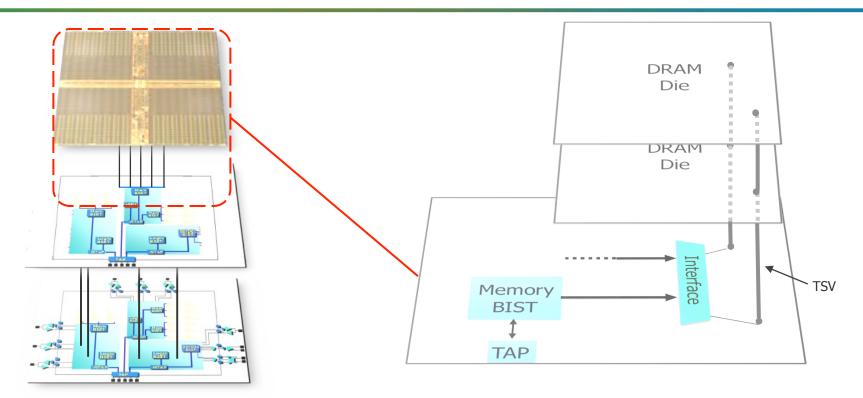

# **STACKED MEMORY TEST**

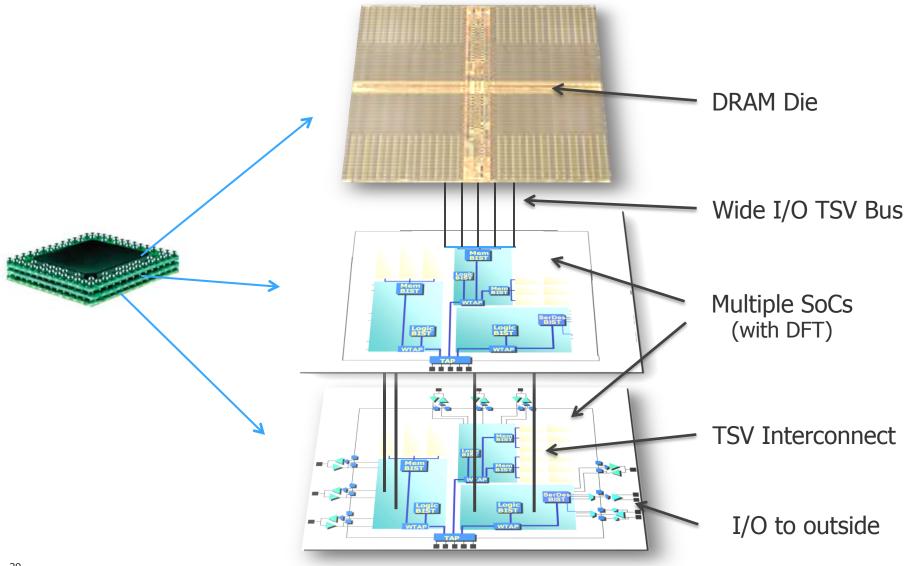

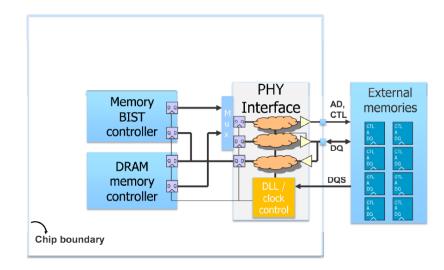

#### Stacked Memory Test BIST Approach

- External Memory BIST added to logic die

- Provides full-speed testing of memory die and bus

- Bus-only test algorithms can optionally be used

Post-silicon programmability supports changes in memory die

### Stacked Memory Test BIST Approach

- All BIST transactions performed through functional PHY interface

- Interface handles all signal synchronization

- Interface also handles mux/demuxing for DDRs

- BIST supports all forms of DRAM access

- Bursting, Refresh, etc

#### BIST highly programmable

- Address range and read/write operations for supporting different memories

- Algorithms for different quality and test cost needs

E.g. Interconnect only coverage

- Supports bussed memories

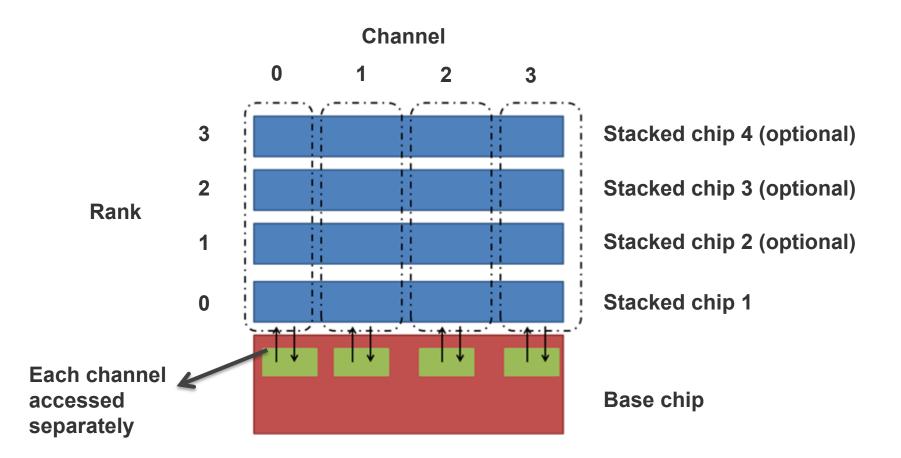

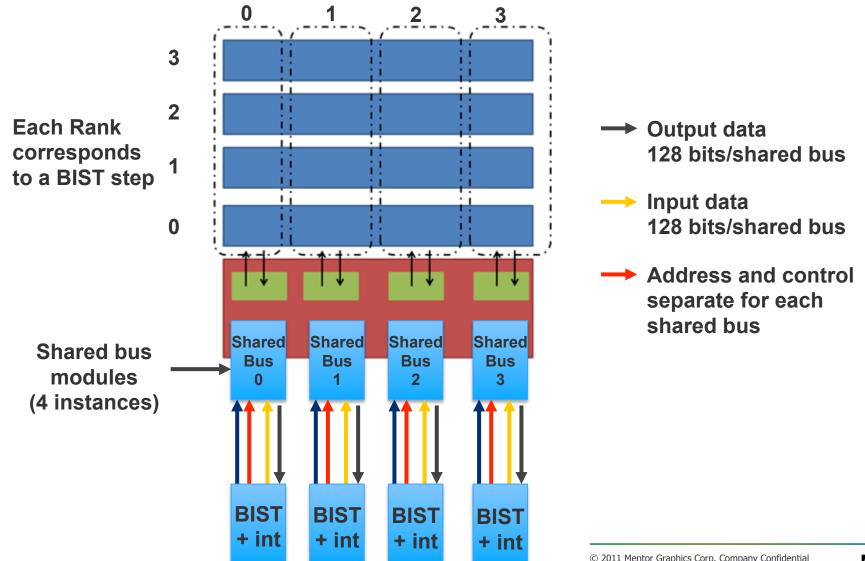

# Wide IO DRAM Example

#### **Wide IO DRAM Example Implementation** 4 shared buses, 4 DRAMs behind each shared bus, 128-bit bus

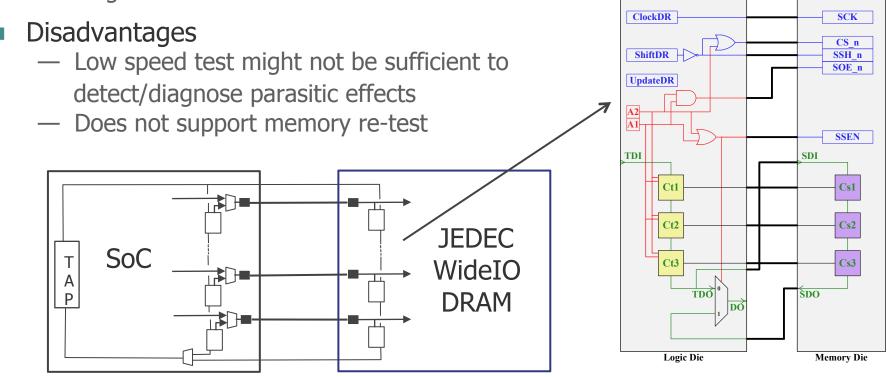

### **Stacked Memory Test Boundary Scan Approach**

- Interconnect test performed using boundary scan

- JEDEC WideIO standard defines bscan chain for DRAM

- Advantages

- Does not require functional DRAM core for test and diagnosis

# **STACKED LOGIC TEST**

#### **Logic Die to Logic Die Interconnect Test** Various Approaches

#### Traditional Boundary scan

- Boundary scan cell placed at each die TSV and IO

- Interconnect test patterns produced to find shorts or opens

- Test operation based on standard boundary scan board test approach

- Limitation: does not support at-speed test of TSV connections

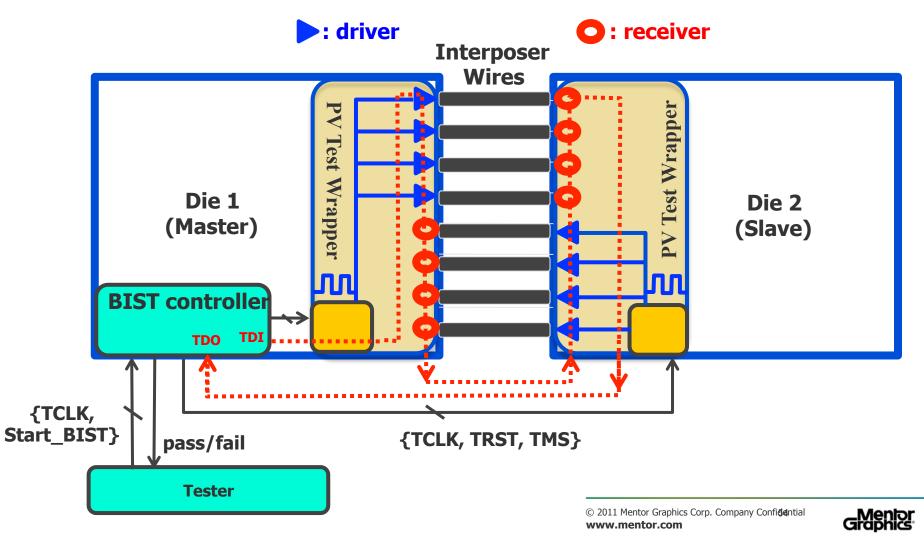

- Pulse-Vanishing

- Hierarchical ATPG Approach

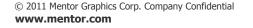

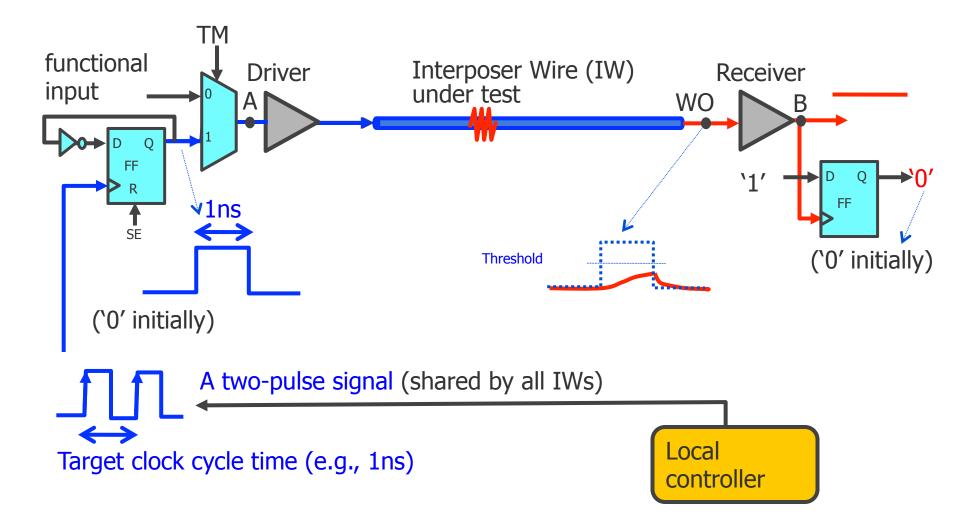

#### **Pulse-Vanishing Approach Targeted Faults in an Interposer**

(1) Parametric Open Fault in an interposer wire

(2) Parametric Bridging Fault between two interposer wires

#### **Boundary-Scan Based Architecture**

The proposed test methods can be built on top of the IEEE-1149.1

#### **Concept of Pulse-Vanishing Test**

#### When There is a **Delay Fault**...

#### Logic-to-Logic TSV Interconnect Test Hierarchical ATPG Approach

- Approach based on TSVs between scan-isolated cores

- Hierarchical ATPG tests signals between cores

- Cores on neighboring die conceptually the same

# **Logic TSV Test Pattern Generation**

- TSV test patterns applied using scan chains in two or more die

- ATPG engine generates patterns using full package netlist

- Non-targeted die and/or cores are grayboxed

- Only ATPG is supported

- BIST and Compression can not easily be extended across multiple die

- Less critical as TSV test set should be relatively small

## Summary

- 3D-ICs introduce new test challenges and requirements

- Critical test solution components include

- Known-Good-die test

- Standardized TSV-based test access to die in stack

- Programmable BIST for stacked memory die

- Scan based testing of logic-to-logic TSV connections

www.mentor.com