# **AMICSA 2014**

### Sunday 29th June 2014 - Wednesday 1st July 2014

Geneva, Switzerland

# **Proceedings**

# **Table of Contents**

### Need and Requirements for Radiation Hardened Analogue and Mixed-Signal ICs

Strategy for Radiation Tolerance Assurance of the A&T Electronic Equipment *M. Brugger*, *G. Spiezia*

Assessment of Mixed Signal Technology

M. Bacci, F. Bigongiari, C. Boatella Polo, R. Dittrich, M. Inversi, R. Jansen 18

**Applications for Radiation Hardened Analogue and Mixed-Signal ASICs: Instrumentation Front-End**

High performance analog Front End ASIC for interfacing with a Si Drift Detector and the control electronics

A. Bonzo, C. Gaillard, N. Letuvee, E. Grand, Y. Morandini, A. Cros, D. Rambaud, E. Moutaye, D. Barret, R. Clédassou, P. Bodin, JY. Seyler 27

Radiation hardness tests of the CLARO-CMOS chip: a fast and low power front-end ASIC for single-photon counting in AMS 0.35 micron CMOS technology

M. Andreotti, W. Baldini, R. Calabrese, P. Carniti, L. Cassina,A. Cotta Ramusino, M. Fiorini, A. Giachero, C. Gotti, E. Luppi,M. Maino, R. Malaguti, G. Pessina, L. Tomassetti34

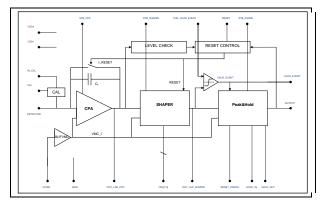

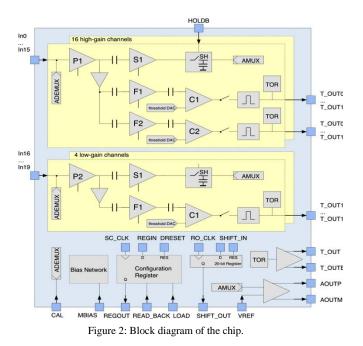

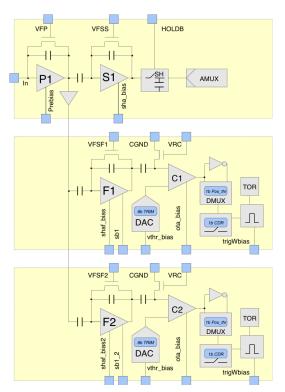

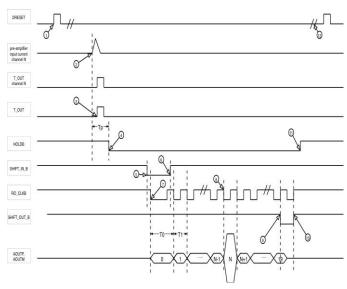

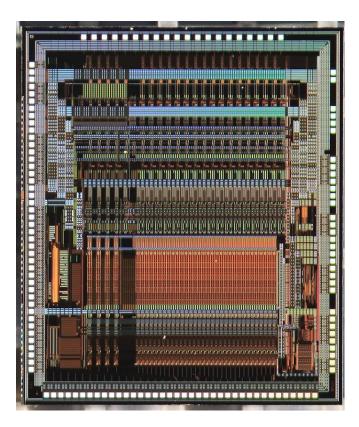

CMOS Analog Front End Design for Particle Energy Measurement in Space Environment

*Florent Bouyjou, Olivier Bernal, Hélène Tap, Jean-André Sauvaud, Pierre Jean*

39

7

An ASIC for Spaceborne Radiation Monitors

H. K. O. Berge, S. Azman, P. Pahlsson, D. Meier, A. Olsen, M. A. Altan, A. Hasanbegovic, J. Talebi, C. Gheorghe, T. M. Johansen, G. Maehlum 45

### **Applications for Radiation Hardened Analogue and Mixed-Signal ASICs: Read-Out-IC**

| FAIR, a front-end ASIC for infrared detector readout                             | 5 1  |

|----------------------------------------------------------------------------------|------|

| J.H.R. Schrader, K. Garakoui, D. Schinkel                                        | 51   |

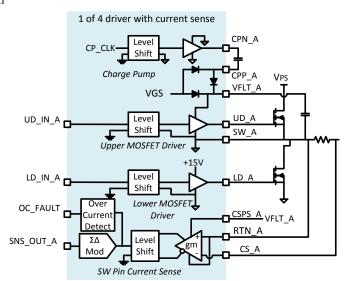

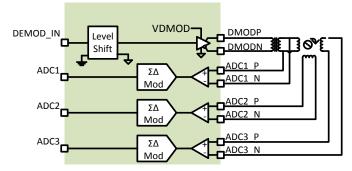

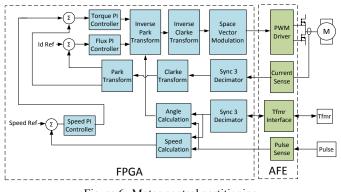

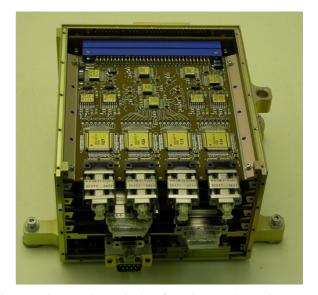

| Analog Front End Integrated Circuits for Mixed Signal Spacecraft Applications    |      |

| B. Ferguson                                                                      | 55   |

| A complete space based CCD biasing solution in a $0.35\mu m$ high voltage CMOS A | ASIC |

| Q. Morrissey, N. Waltham, S. Bell, M. Prydderch, M. Torbet, M. Clapp             | 59   |

| Applications for Radiation Hardened Analogue and Mixed-Signal                    |      |

| ASICs: Wired and Wireless Communication                                          |      |

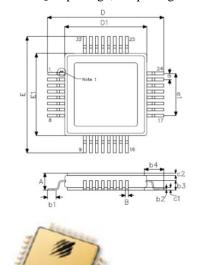

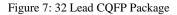

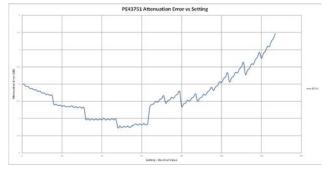

| Digital Step Attenuators for Microwave Applications                              |      |

| A. Christie                                                                      | 66   |

| Low-Power Analogue Receiver ASIC for Space Telecommand Applications              |      |

| S. Chicca, F. Bigongiari, G. Piscopiello, G. Tuccio                              | 73   |

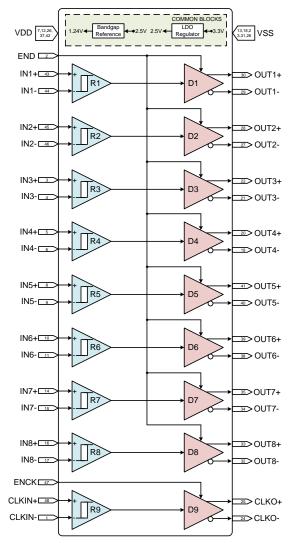

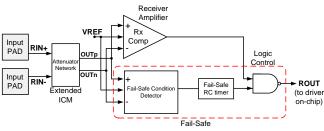

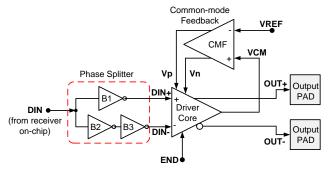

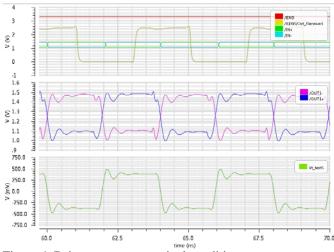

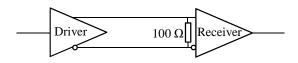

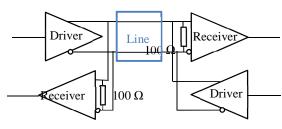

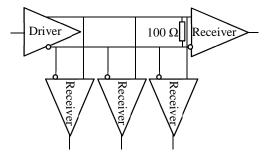

| Use of IHP's 0.25 $\mu$ m BiCMOS Process in the Development of European LVDS     |      |

| J. López-Sotoa, D. González-Gutiérrez, J. Ilstad, M. Cirillo , F. Korndörfer     | 82   |

| Rad-hard High Speed LVDS Driver and Receiver                                     |      |

| T. Masson, S. Nicolas, C. Morche, J. Jimenez                                     | 87   |

### **Applications for Radiation Hardened Analogue and Mixed-Signal ASICs: Power and Micro-controllers and Signal Processors**

| A radiation-tolerant Point-of-Load buck DCDC converter ASIC                                                                                                |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| F. Faccio , S. Michelis, S. Saggini, G. Blanchot , I. Troyano , C. Fuentes ,<br>S. Orlandi                                                                 | 96   |

| A Mixed-Signal Radhard Microcontroller: the Digital Programmable Controller (<br>M. Fossion, A. Van Esbeen, T. Van Humbeeck, Y. Geerts, E. Geukens,        | DPC) |

| S. Redant, R. Jansen, C. Monteleone                                                                                                                        | 101  |

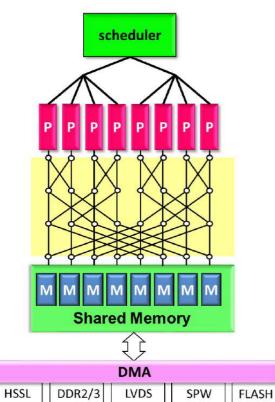

| Scalable Sensor Data Processor: A New Mixed Signal Processor ASIC for Harsh Environments                                                                   |      |

| R. Trautner, B. Glassa, R. Jansen                                                                                                                          | 106  |

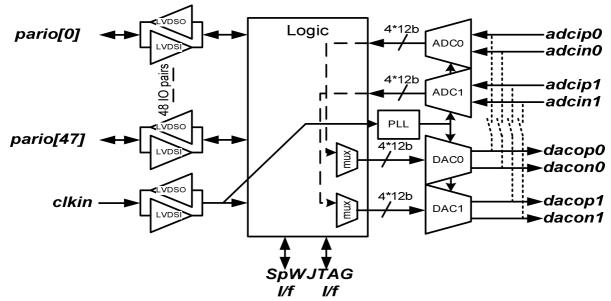

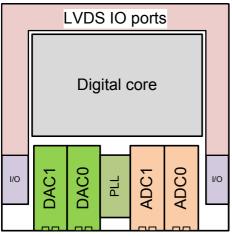

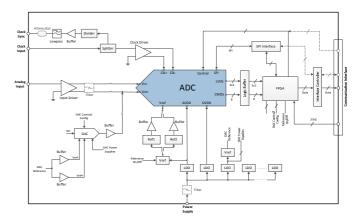

| <b>Applications for Radiation Hardened Analogue and Mixed-Signal</b><br><b>ASICs: Data Converters</b><br>RCADA - 65nm 12b 3Gspc Rad Hard dual ADC dual DAC |      |

| T. Liran , R. Ginosar, F. Lange, P. Aviely , D. Raphaeli , E. Kraus                                                                                        | 110  |

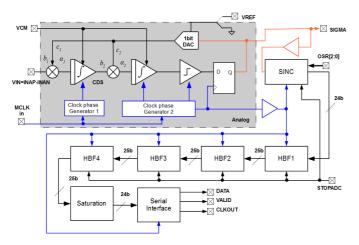

| Very High Resolution Analog-to-Digital Converter at 1 kHz for Space Application<br>K. Makris, D. Fragopoulos, L. Crespy, M. Karaolis, A. Hachemi,          | ns   |

| O. Dokianaki, C. Papadas, B. Glass                                                                                                                         | 114  |

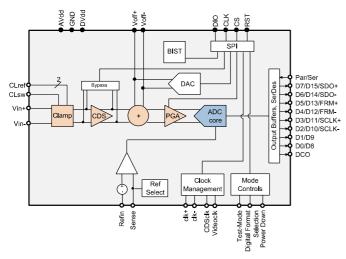

| Development of a high-speed and high-resolution ADC for image processing applications                                                                      |      |

| HV. Heyer, A. Koelnberger, H. Telle, E.T. Sarris, G. Kottaras, B. Glass                                                                                    | 121  |

|                                                                                                                                                            |      |

### Methodologies for Radiation Hardening on Analogue Circuits at Cell Level, Circuit Level, and System Design Level

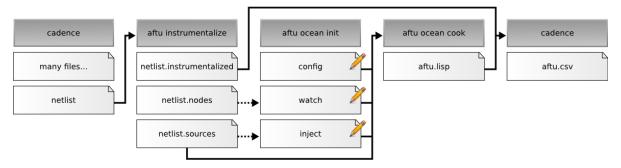

| AFTU, an Analog Single Event Effects Automatic Analysis Tool  |     |

|---------------------------------------------------------------|-----|

| F. Márquez , L. Sanz, F.R. Palomo , F. Munoz and M.A. Aguirre | 125 |

### **Radiation Hardened Technology for Mixed-Signal IC**

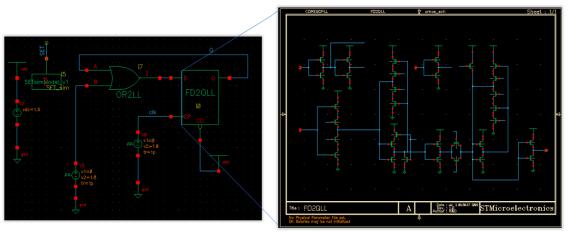

| SEE Characterization of a Magnetometer Front-End ASIC using a RHBD Digit<br>Library in AMS 0.35um CMOS                                          | tal       |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| J. Ramos-Martos , A. Arias-Drake, L. Carranza-González, S. Sordo-Ibáñez,<br>J. Ceballos-Cáceres, J. M. Mora-Gutiérrez, B. Piñero-García,        |           |

| M. Muñoz-Díaz, A. Ragel-Morales, S. Espejo-Meana, M. A. Lagos-Florido                                                                           | 130       |

| Mixed-Signal Design Methodology for Various Radiation Environments with Applications to a 0.35 µm, 65 V Quadruple-Well BCD Technology           |           |

| D. Kerwin, D. Walz, and K. Merkel                                                                                                               | 134       |

| New ID MOS PDK for Space Applications                                                                                                           |           |

| Florence Malou, Pierre-Emmanuel Martinez, Xavier Saboret,<br>Patrice Poulachon, Paul-Emile Latimier                                             | 138       |

| Radiation-hardened high-voltage ASIC technology qualification for space appli<br>Jérome Ducrot, Damien Leroy, Marc Souyri, Paul-Emile Latimier, | ication   |

| Romain Soubiraa                                                                                                                                 | 141       |

| 180nm CMOS Mixed-Signal Radiation Hard Library as base for a full ASIC su chain                                                                 | ipply     |

| J. Steinkamp, E. Oikonomopoulou, F. Henkel, V. Lück                                                                                             | 144       |

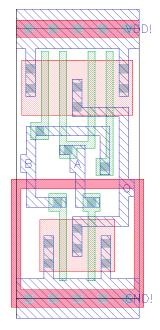

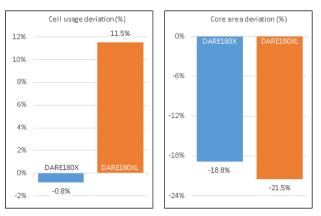

| DARE180X: A 0.18µm mixed-signal radiation-hardened library for low-power applications                                                           |           |

| G. Franciscatto, E. Geukens, G. Thys, S. Redant, Y. Geerts, M. Fossion,<br>A. Van Esbeen                                                        | 150       |

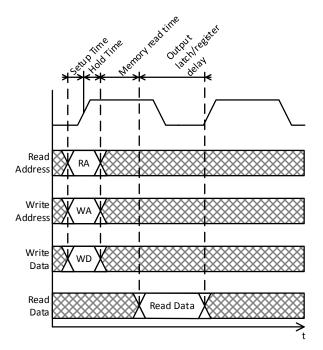

| The development of a radiation tolerant low power SRAM compiler in 65nm te                                                                      | echnology |

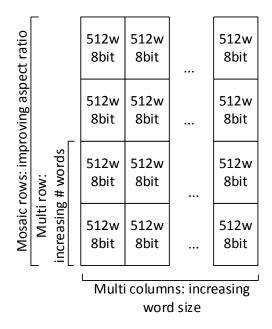

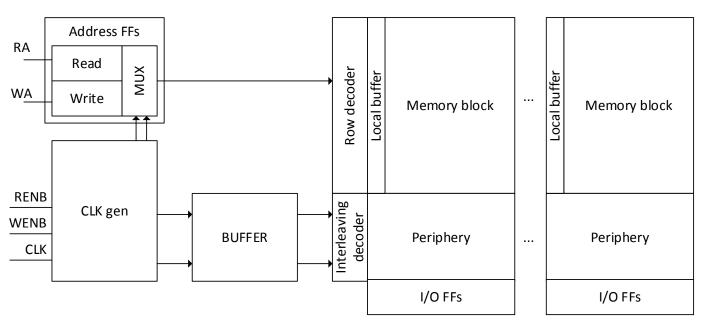

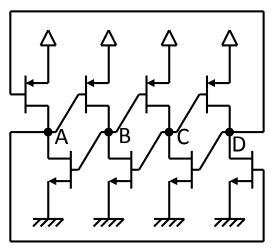

| R. Brouns, S. Bonacini , L. Berti , S. Verhaegen , K. Kloukinas , G. Thys ,<br>S. Redant, A. Marchioro                                          | 156       |

# Need and Requirements for Radiation Hardened Analogue and Mixed-Signal ICs

### Strategy for Radiation Tolerance Assurance of the A&T electronic Equipment

M. Brugger<sup>a</sup>, G. Spiezia<sup>b</sup>

<sup>*a*</sup>CERN, 1211 Geneva 23, Switzerland, EN/STI/EET on behalf of the R2E project <sup>*b*</sup>CERN, 1211 Geneva 23, Switzerland, EN/STI/ECE on behalf of the RADiation Working Group (RADWG)

### Abstract

This paper present an overview of the criteria for choosing radiation test facilities, the test strategy and procedures, adopted considering the type of the Accelerator Sector Equipment, its individual list of required components, as well as the radiation levels of the area where it will be installed.

### I. INTRODUCTION

The radiation environment encountered at high-energy accelerators differs from the environment relevant for space applications. The mixed field expected at modern accelerators is composed of charged and neutral hadrons (protons, pions, kaons and neutrons), photons, electrons and muons, ranging from very low (thermal) energies up to the TeV range [1].

This complex field is due to particles generated by primary particle collisions in the experimental areas, distributed beam losses around the machine, and the circulating beam interacting with the residual gas inside the beam pipe. Electronic components and systems exposed to a mixed radiation field will experience at once all three different types of radiation damages: Single Event Effects (SEEs), damage from Total Ionizing Dose (TID) and Displacement Damage (DD), where in all cases, not only the particle type, but also the respective energy distribution are to be considered. One important example of the latter are latchup errors (possibly destructive) where in the context of accelerator environments their cross section can still increase until energies in the GeV range, especially if high-Z materials are present near the device's sensitive region [2]. In addition, for some devices the impact of thermal neutrons is not to be neglected; and when it comes to dose, pure gamma test measurements are partly not fully representative.

For the CERN accelerator sector, the control and the functioning of the Large Hadron Collider (LHC) requires many systems and equipment partly to be installed in radiation areas, such as power converters providing up to 13 kA current to the super conducting magnets, safety and monitoring electronics, actuators for discharging the superconducting coils, pumps for creating the required vacuum conditions in the beam pipe, in the magnets, and in the helium distribution line, cryogenic systems to reach the temperatures down to a few Kelvin, and many others. Moreover, depending on the functionality, each system is replicated 10, 100 or 1000 times along the LHC and its injections lines, thus amplifying even low failure rates in terms of their possible impact to the accelerator operation.

Within these constraints, the conception of full custom solutions down to the component level is often not possible and must be adopted according to each individual design limitations, defined by the electrical specifications on the one side and the harsh radiation environment on the other. Depending on the latter, in the context of accelerators, equipment can thus be either a fully commercial system, or a custom development, based on hardened or qualified electronic components, or a mix of the two solutions.

Therefore, all exposed electronic systems have to be qualified for their radiation tolerance. The latter has to include a failure analysis and an estimation of the respective impact on accelerator operation. In this context, the device degradation due to cumulative effects, or its functional limitations due to single event failures, is not a limitation by itself, but must be quantified. In terms of respective design acceptance criteria, the performance degradation must not prevent the proper use of the component or the system up to its defined (and qualified) TID and DD targets, as well as the rate of SEE must remain sufficiently low in order to cause only a limited (and acceptable) number of stops of the accelerator, while also keeping as short as possible the consequent machine downtime.

Combining all accelerator operation, control and monitoring systems, the R2E project [3] aims for an accelerator operation with an overall radiation induced 'Mean-Time Between Failures' (MTBF) greater than or equal to one week for nominal, ultimate and later high-luminosity operation conditions, therefore finally assuming a peak luminosity of  $\sim 5 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> allowing for an annual integrated luminosity of more than 200 fb<sup>-1</sup>.

In order to keep the overall failure rate under control and to reach the goal defined by the MTBF target, one requires a long-term radiation test and qualification strategy trimmed to the needs of the accelerator radiation environment and its applications.

After presenting the structure of the R2E project and the mandate of the RADiation Working Group (RADWG), this paper will describe the radiation levels in the accelerator sector, the criteria for choosing radiation test facilities, both standard facilities as well as a new CERN-based one (CHARM), the test strategy and procedure, with flow charts of the radiation tests to be performed, taking into account the type of the equipment, its individual list of required components, as well as the radiation levels of the area where it will be installed. A generic architecture of the electronic systems used in the accelerator is described highlighting the critical parts which could be developed as radiation hard ASICs (Application-specific integrated circuit) for future applications.

### II. R2E PROJECT ORGANIZATION

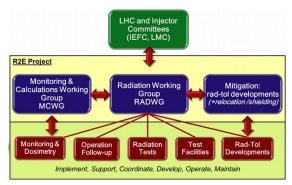

Figure 1 reports the organization of the R2E project which was set in 2007. In order to reduce the radiation failures, the equipment, which is or will be installed in areas where radiation levels are critical, must be radiation tolerant. The designers of that equipment participate to the RADWG meetings [4]. The R2E project advices that at least one member of each accelerator group has to attend the meeting. The RadWG provides support to the accelerator sector equipment groups for the assessment of radiation tolerance of electronic equipment to be installed in radiation exposed areas. The RADWG is as a forum for electronic engineers to discuss common design practices and appropriate radiation tests, as well as observed radiation induced failures in the accelerators and their follow-up. The group also coordinates radiation test campaigns within CERN and at external facilities. The RADWG assists the R2E Project leader for the evaluation of the technical aspects of the proposed mitigation actions with the representatives of the equipment groups, and is used by the R2E project leader to inform the equipment groups of the action proposed. The relocation of the equipment and the shielding of exposed areas are also among the possible countermeasures to protect electronics against radiation but are not discussed in this document. The RadWG furthermore informs about simulated and measured radiation levels in the various underground areas, delivered by the Monitoring and Calculations Working Group (MCWG). The MCWG studies the radiation levels of the LHC and its injection lines with FLUKA Montecarlo calculations and collects the on-field data of the monitoring devices (Beam Loss Monitor, Radiation Monitors, passive dosimeters) to weekly provide the evolution of the radiation levels during the operation.

Figure 1. Organization of the R2E project.

#### **III. ENVIRONMENT AND RADIATION LEVELS**

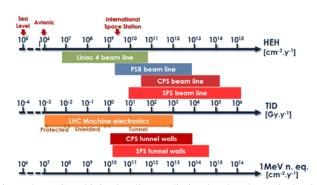

The variety of radiation source terms present in a particle accelerator results in a unique radiation field composed of different particles at various energies which will provoke the three different types of radiation damage [1]. High Energy Hadron (HEH, >20 MeV) radiation levels range from a few  $10^7 \text{ cm}^{-2}$  (protected, shielded areas) to  $10^{12} \text{ cm}^{-2}$  (tunnel areas) per year, corresponding to an annual TID range of 1 rad-100 krad(Si) [1]. In the CERN injection lines, several smaller particle accelerators which feed the main LHC ring, where radiation levels up to 100-1000 krad (Si) (with hadron fluence to  $10^{13} \text{ cm}^{-2}$ ) are to be expected at the location of the electronic equipment. Electronic systems containing only

COTS components, installed in the shielded areas, can already fail at hadron fluences as low as  $10^7$  cm<sup>-2</sup>; damage to COTS components, used in custom designed boards, is not negligible starting from doses of 1-10 krad (Si). Therefore, the LHC tunnel and its injection lines present radiation levels induced by a hadron fluence ranging from a few  $10^7$  to  $10^{13}$  cm<sup>-2</sup>. Figure 2 reports the range values in terms of HEH fluences, TID, and 1MeV neutron equivalent, considering the ratio among those quantities provided by means of the FLUKA Monte-Carlo calculations.

Figure 2. LHC and injection lines radiation levels. The typical values of radiation levels at sea level (New York), avionic altitudes and international space station are also indicated.

### IV. TEST FACILITIES CHOICE

Several areas close to the accelerator tunnel and partly not sufficiently shielded, are equipped with commercial or COTS based systems which are mostly affected by the risk of SEEs, whereas electronics installed in the accelerator tunnel, based on custom design, will in the long-term also suffer from additional cumulated damage (TID and DD, Figure 2). On this basis, all three types of radiation effects must be considered for testing although they will not impact in the same way the electronic systems. The radiation tolerance of electronic devices can be estimated by using different particle types. Protons are able to trigger all three types of radiation effects but create synergistic effects among SEE induced failures and total dose and displacement damage. Neutrons at ~1 MeV are used to test the robustness to displacement damage; neutrons at high-energy are exploited to study the SEE without creating total dose effect. Gamma irradiations are conceived to characterize the TID of the DUT (Device Under Test) without creating any displacement damage. Two, partly parallel, strategies can be pursued:

- The first one consists in selecting and using external facilities which are recognized by the radiation community: e.g., a) the Paul Scherrer Institute (PSI) providing a monochromatic proton beam, b) the Centre Energie Atomique (CEA) providing a neutron environment at ~1 MeV, c) Fraunhofer INT institute offering a <sup>60</sup>Co or neutron source, d) the European Space Agency (ESA) offering a <sup>60</sup>Co source and several others. In addition, specific facilities, such as the PTB (Physikalisch-Technische Bundensanstalt), the Nuclear Research Institute (NRI in Rez), and the nuclear reactor in Kijeller can be exploited for calibration purposes. (e.g., for the Radiation Monitor project).

- The second strategy aims at building a mixed radiation facility capable of reproducing the representative

accelerator environments (e.g., of both the shielded and tunnel areas). In the past, two test areas, CNRAD and H4IRRAD, have been used for this purpose, although their operation was not fully optimized for radiation testing (limited availability, intensity, etc.). On the basis of this experience, a dedicated new radiation facility (CHARM) has been built [5].

A collection of the available test facilities is available on the RADWG website [4].

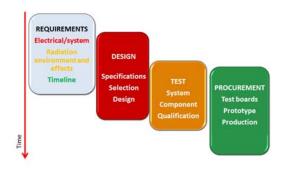

Figure 3: Timeline of a new electronic accelerator system development where radiation test is a dedicated phase of this process.

### V. TEST AND QUALIFICATION STRATEGY

The test of the components and/or the system is part of a process with defined phases which starts with the definition of the requirements of a given project (Figure 3). Once the designers will specify the type of systems to be used and its components, the radiation effects to be considered are analysed by knowing the environment, which depends on the installation area. The test strategy will then strongly depend on the radiation environment and the complexity of the electronic system to be qualified. The LHC equipment and its subsystems can be classified in two main categories:

- fully commercial system, here referred to as COTS system;

- custom electronic systems based on COTS components.

In order to define the test strategy and the requirements, first the location of the equipment is to be considered. We can distinguish the following areas where one usually can find electronic systems:

- Accelerator tunnel areas

- LHC areas close to experiments (*e.g.*, inner triplets) or areas with high losses (*e.g.*, collimation areas): very high radiation levels generally excluding the installation of electronic systems

- LHC Dispressor/suppressor (DS): tunnel area with higher radiation doses

- LHC ARC: tunnel area with lower doses

- Injectors: usually higher radiation doses, partly excluding the installation of electronic devices

- Shielded areas

- Critical zones (areas with annual fluences above  $10^6$  n/cm<sup>2</sup>)

- o Safe zones.

Radiation hardened devices as used in space or military applications are evidently advisable for custom solution, but are used only in a limited amount due to component costs and the additional limitation that they do not always offer the electrical performance required for an individual application. Therefore, keeping in mind the target radiation levels and the fact that repair interventions are not impossible but only have to be limited in terms of time and number, the use of radiation hardened parts is limited for the actual designs. In terms of radiation tolerance required for individual applications, starting from the radiation levels, one obtains for each application a list of locations and corresponding radiation levels for TID, DD and HEH. To this, depending on the location and the component or equipment type, one must take certain safety margins into account:

- i. the uncertainty of the radiation levels (if not known by measurements: x2),

- ii. the low dose rate effects (x3, to be considered only for bipolar devices),

- iii. the traceability of the components (x3, absence of lot codes or respective characterization).

The last two parameters only apply for the calculation of the TID levels in the tunnel for the test of COTS components, whose traceability and quality assurance strategy will be described later.

In order to obtain an estimate for the expected global failure rate, the equipment group needs also to specify the number of exposed systems/components. This collected information can then either be used to estimate the failure rate and life-time based on radiation test results, or determines the target levels required for radiation tests.

Based on the radiation levels already present at CERN accelerators and those expected for future operation, it can be concluded that:

- commercial systems: are ideally tested in order to allow for an estimate of the global failure rate and can only be installed in shielded and relatively low radiation areas, provided that mitigation measures (e.g., remote reset) reduce the impact on accelerator operation and that they are not linked to safety systems

- COTS based systems can be installed in tunnel areas but require a respective radiation tolerant design and dedicated radiation test program. Depending on the details taken into account during the qualification process (e.g., lot testing) more or less safety factors have to be applied

- systems based on hardened electronic components shall be considered for the most exposed location (in case these cannot be avoided).

Based upon this general framework, we describe the CERN test strategy and requirements per installation area and per type of equipment by indicating the goal of the test, the modality, the suggested facilities, and the consequent follow-up actions to be taken on the basis of the collected fault scenarios.

# VI. Shielded and low-radiation areas ( $<10^9$ HEH/cm<sup>2</sup>/y)

TID and the DD are not a concern for the equipment installed in the shielded areas where the SEEs remain the

unique source of radiation effects. The difference between safe and critical areas depends on the level of cumulated highenergy hadrons. We recall that radiation tests are not required for areas where the annual cumulated high-energy hadrons fluence is lower than  $10^6$  n/cm<sup>2</sup>.

### A. COTS system

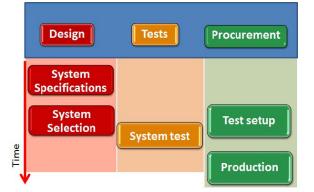

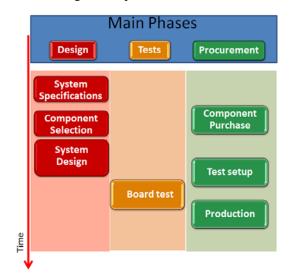

COTS systems are fully commercial devices. Among others, we can find an Uninterruptable Power Supply (UPS), a commercial solution to monitor the voltage distribution of the area, fire detectors with its central unit, PLC stations of different branches, and so far so forth. The traceability of this equipment is difficult. The products are purchased from external companies and there is no control of the single components whose reference can even change from one system to another. The main phases of the project development and the respective radiation test period are shown in Figure 4. It is important to note that depending on the annual radiation levels, as well as the failure impact of the system, each installation case must be evaluated individually

prior installation.

Figure 4: Design, Test and Procurement phases for a COTS system used in low radiation areas.

In this case it is required to qualify the entire system for their overall SEE vulnerability only. The test aims at finding an indicative cross section for soft SEEs and verifying if destructive events can occur. Those types of systems can only be tested in CERN test areas where big volumes can be placed. Although the system is almost a black box for the equipment owner, the survey of the total current consumption and the monitoring and logging of accessible analogue test points or digital data are required during the radiation test. The evaluation of the cross section for the different types of soft SEEs and the knowledge of the expected radiation levels provide a good indication if the system failure rate is acceptable in terms of MTBF. Should the failure rate not be acceptable, mitigation techniques at the system level, such as the implementation of automatic resets, software fault diagnostics, use of redundant subsystems, are to be put in place.

As far as hard single events are concerned, the evaluation of the cross section is usually not possible for such partly large and complex systems, especially if only one or two units were tested. If observed, the study of a mitigation technique is performed to verify if the destructive event can be intercepted and controlled. If this study does not provide a robust solution, either an overall equipment redundancy is to be considered, or the failure can be accepted in case the equipment responsible prepares a strategy to promptly replace the defective unit in case of a destructive SEE (without major impact on accelerator operation).

### B. Custom systems based on COTS components

Custom systems are electronic boards, devoted to control actuators, acquire signals, manage power converters, which have been designed by CERN engineers based on COTS components. Those systems are not black boxes for the equipment responsible who masters both the design and the component choice. Conversely to the case of COTS system, individual electronic boards are to be considered for the testing. Whenever it is possible, the designer uses components, which have already been tested or qualified. However, in this case the test of the single parts and the lot traceability against SEEs is not required because the radiation levels are sufficiently low. Thus, we do not apply the corresponding safety margin on the lot to calculate the required radiation tolerance criteria. The R2E strategy recommends at least a SEE test of the boards to investigate on SETs and quantify soft and hard SEE cross sections at the defined radiation tolerant levels (see Figure 5). The radiation test can be performed either at a CERN test area or at PSI. For the latter case, if the board is larger than a circle of 5 cm diameter, a scan, and thus multiple runs are required to irradiate all the components. The current consumption of the board and other analogue test points, which can suffer SETs potentially harmful for the board, are to be monitored and all numeric data of digital components are to be checked.

Figure 5: Design, test and procurement phases for custom board with COTS components used in low radiation areas.

The respective evaluation of the cross section for the different types of SEEs and the knowledge of the expected radiation levels indicate if the system failure rate is acceptable in terms of MTBF. Should the failure rate not be acceptable, mitigation techniques can be applied at design level for individual components, such as replacement of sensitive parts, the use of filters for SETs, or at system level, such as the implementation of automatic resets, software fault diagnostics, or the use of redundant subsystems. As far as hard single events are concerned, the evaluation of the cross section can be done if an active current consumption monitor is put in place during the test. The mitigation techniques can be applied at component level if the sensitive part is individuated or at board level by using an anti-latchup system. The latter anti-latchup circuit can then be also considered as final mean of mitigation, depending on the eventual application case. As an ultimate option the redundancy of the board can be considered. Table 1 summarizes the radiation test facilities, test modalities, and the possible mitigation actions for systems installed in shielded areas.

## VII. TUNNEL AND HIGH-RADIATION AREAS (>10<sup>9</sup> $HEH/CM^2/Y$ )

In this case all three types of radiation effects are to be considered for the installed equipment. The CERN injector areas, as well as the LHC DS zones impose a more severe limit on the TID and DD radiation tolerant criterions. In those areas, the installation of the equipment is allowed only when electrical and functional constraints make it necessary, i.e. no other reasonable installation solution can be found in more protected areas. The use of fully commercial system is not anymore allowed because of their possible high sensitivity and their traceability and qualification constraints; moreover their internal design is often not known.

Table 1: Summary of the test type, facilities, test modality and mitigation actions for systems of the shielded areas.

| Location | System<br>type       | Test<br>type | Facility                    | How                                                                           | Mitigation<br>actions                                              |

|----------|----------------------|--------------|-----------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Shielded | COTS<br>system       | SEE          | CERN<br>test<br>area        | Test points<br>for SET<br>Current<br>consumption<br>SEE on<br>numeric<br>data | System<br>Software<br>Redundancy                                   |

| area     | Custom<br>on<br>COTS | SEE          | CERN<br>test<br>area<br>PSI | Test points<br>for SET<br>Current<br>consumption<br>SEE on<br>numeric<br>data | Component<br>Board<br>design<br>Firmware<br>Software<br>Redundancy |

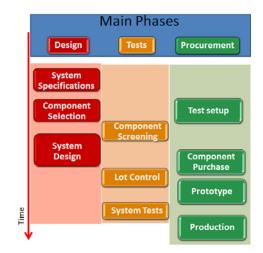

All custom developed systems must be radiation tested; moreover, the traceability and the qualification of the lots of the critical components are required, or respective safety margins are to be taken. The process of design, test and procurement is depicted in Figure 6. The ideal test process foresees a component screening test, the lot qualification after the component purchase and then an additional verification of the entire board/system with the chosen components. The component selection is a phase of the system design and depends on the project specifications. Apart a few exceptions, the design of a system can go in parallel with the screening tests, the purchase of the components lots and their qualification. Finally a prototype board is produced, populated with the qualified components, and tested for production acceptance, to be followed by the verification of the latter.

Figure 6: Flow chart of the test strategy for custom boards based on COTS components.

The lot qualification demands a significant amount of work and requires a defined time schedule, which might sometimes not fit within the overall available time planning of a new installation (often driven by accelerator requirements and available shut-down periods). In such cases, the management can decide to proceed with the production and installation of the boards whose components were selected on the basis of radiation screening tests but do not belong to a qualified lot. Since this is a scenario which CERN faced and might also face in the future, two general strategies (discussed in the following sub-sections) are defined to assure the radiation tolerance of custom equipment. Only the first one foresees the lot qualification of the critical components.

The definition of a "lot" for COTS components is not trivial. The components are often bought through vendors who collect the components from different foundries or assembly factories. Among the accelerator electronic groups, it was agreed to try as much as possible contacting vendors in order to get the samples from the same foundry (e.g., through combined purchases). However, that is not always feasible since the number of parts required for the accelerator projects is often not sufficiently high to justify a dedicated production follow-up. However, to a certain extend one can rely on the assumption that COTS samples belong to the same lot when they have the same imprinting on the chip as well as the same production date. That definition is often used for accelerator applications although there is no absolute guarantee that all the samples will have the same internal design; that risk can be accepted depending on the component importance and failure consequence in the design.

Saying this, it is useful to clarify also the definition of a "critical component". A component is critical if:

- the main functionalities of the board depend on it

- it can potentially suffer or trigger destructive events

- the performance degradation due to radiation cumulative effects makes it useless for the application.

Those definitions are generic and the list of components of a custom board to be considered as 'critical' needs to be decided upon a dedicated analysis.

In the following we briefly describe the two general test strategies and, then, guidelines will be given on the radiation test methods of the components against TID, DD, and soft and hard SEE, high-lightening the facilities which can be exploited for each type of the test.

### A. Test strategy with lot validation

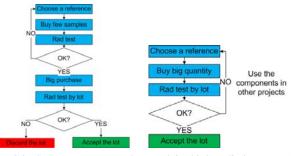

The first strategy to select a COTS component for a custom developed board is sketched in Figure 7.

Figure 7: COTS components (to be used in high-radiation areas) selection process with (left) and without (right) the screening phase.

This method is applied when there is the necessity to evaluate different candidates for the same type of the required component (ADC, DAC, differential amplifier, or voltage regulator). The candidates fulfilling the electrical and functional requirements of the application, which they are chosen for, are tested against radiation to determine the best choice. In this case, the best radiation test facility is the one which allows the test of all three types of radiation effects (in a representative way), thus

- PSI, where the test can be done in short time, although ELDRS, which can be an issue for bipolar devices, is then not taken into account and also safety margins for the maximum beam energy have to be taken into account for destructive effects.

- CERN mixed-beam test facility is usually a very good and efficient alternative.

If only TID is a concern for the device under test, then a <sup>60</sup>Co source can be used. The DD test is used as a screening test only if the device under test has to work until relatively high fluences (>1x10<sup>13</sup> n/cm<sup>2</sup>) or is known to be very sensitive to non-ionizing damage (e.g., optical components). Concerning destructive single events, Section VIII will give the details of the applied strategy. The final facility and test choice is then to be confirmed by the CERN radiation test expert on a case-by-case study depending also on the contingency plan of each individual project (Table 2). Once a component candidate has been chosen, a quantity of parts is bought to fulfil the requirement of the project at long term (including spare parts). If possible, the manufacturer will be asked to provide the samples from the same lot, according to the definition we have provided. The number of samples to be tested for each lot has to be between 5 and 10. The lot should ideally be tested in the same facility where the screening test was performed. If the SEE test is not possible because of time-line constraints, the lot must be qualified against TID.

|                            | Facility                             | Features        | Comments                                                      |

|----------------------------|--------------------------------------|-----------------|---------------------------------------------------------------|

| Proton                     | PSI                                  | TID, DD,<br>SEE | Fast test<br>No ELDRS<br>(bipolar)                            |

| Mixed<br>field             | CERN                                 | TID, DD,<br>SEE | Individual<br>components,<br>Batch screening,<br>System tests |

| <sup>60</sup> Co<br>source | ESA,<br>Fraunhofer,<br>CERN (>=2015) | TID             | ELDRS option                                                  |

| 1 MeV<br>neutron           | CEA                                  | DD              | Recommended if $\Phi > 1 \times 10^{13} \text{ n/cm}^2$       |

Table 2: Screening tests and facility option summary.

The respective risk is acceptable since the literature shows that SEE vulnerability does not change that much from lot to lot. If a TID test at low dose rate (100-400 rad/h) is to be performed, then a dedicated <sup>60</sup>Co source at Fraunhofer INT or at ESA (and in the near future also at CERN) can be used.

For urgent projects, the above strategy can be simplified, without any impact on the final quality, but still allowing to avoiding the screening test (Figure 7 right). However, the required component is then purchased immediately for the full required quantity, thus ideally only when (i) a good component candidate already exists and was already tested for, or (ii) the component is not that expensive and also used in other projects of the groups at CERN. Then, the same test criteria as for the previous case are applied.

#### B. Test strategy without lot validation

Tight time schedules or emergency upgrades sometimes do not allow for a proper selection of the COTS components followed by a detailed lot qualification. In these cases, the designer tries to use components which have been already tested for and whose behaviour under radiation is known. Whenever that is not possible and a new unknown component is used, a radiation test is to be foreseen for each of the most critical components and/or for the entire board. The flow chart of the process is the same as in Figure 5. As far as the test of the single component is concerned, the same criteria described in the previous subsection (A) apply. This then has to be validated by a verification of the entire board once produced (see test criteria of Section VI-B), however including TID and DD effects, as well as ideally a larger random sample in order to compensate for possible lot variations, if not traced during the production process. The CERN R2E strategy foresees as such a series of tests of individual random boards to qualify for SETs and determine soft and hard SEE cross section at the defined radiation tolerant levels, as well as the TID and DD limits, either by including a larger random sample or by applying required safety margins. In this case radiation tests can be done preferably in a CERN test facility (allowing to test a larger set of boards at the same time) or also at PSI. For the latter, if the board is larger than a circle of 5 cm diameter, a scan, and thus multiple runs, is required to irradiate all the components. The current consumption of the board and other analogue test points are to be monitored in detail. The numeric data of digital components are to be checked in a continuous way. The evaluation of the TID and DD limits will indicate if the board can stand the radiation levels at which it

will be exposed; the calculation of the cross section for the different types of soft SEE and the knowledge of the expected radiation levels will determine if the system failure rate is acceptable in terms of MTBF. Should the failure rate not be acceptable, or the TID, DD limits be lower than the radiation acceptance criteria, then the critical components must be replaced with better candidates. In addition, mitigation techniques can be applied at design level, such as filters for SET, drift correction; or at system levels, such as the implementation of automatic resets, software fault diagnostics and correction, or the use of redundant subsystems. As far as hard single events are concerned, the evaluation of the cross section can be done if an active current consumption monitor is put in place during the test. A respective mitigation technique can then be applied at component level if the sensitive part is individuated or at board level by using an anti-latchup system. As an ultimate option the redundancy of the board can be considered.

### VIII. BASIC GUIDELINES

In the following sub-sections, more details are given on the guidelines for the component test, which can also be adopted for the test of custom boards. In particular, specific considerations will be added for the test of the destructive single events.

### A. TID and DD testing

Total ionizing dose affects almost all types of components and must be carefully considered for the qualification of components that will be used in accelerator tunnels. The TID test requires following the main parameters of a component during the test in an on-line mode, by means of a continuous acquisition during the run, or in off-line mode by performing the measurements at intermediated dose steps (with shortest possible annealing times). It is advised to power the component and to bias it as it will be used in the real application. Measurements in a different bias mode can be done to better understand the behaviour of the DUT at intermediate dose steps. If the real application case is not known, the test must aim at figuring out the DUT characteristics as a function of the dose. The main parameters indicated in the datasheet are to be checked. In this case, the test can get longer and more complicated as more setups are to be foreseen. Only as a last option the DUT can be tested in passive mode without the powering and the bias; however this test mode is not advised for most applications and component types. For comparison purposes, the parallel test of a chip which is not irradiated and checked as a reference is strongly recommended. In addition, often a careful temperature logging is required as it can provide valuable input for the final data analysis. An available test standard [6] requires checking the components after irradiation to verify if the observed effects are stable in time or if annealing effects occur. This is especially important as the average dose rate in accelerator tunnels is usually relatively low and unpractical to be tested for. Therefore, a dose rate range 100-360 rad/h (ESCC22900 [7]) is usually chosen for bipolar components as a trade-off for testing of low dose rate effects in a reasonable time. CMOS components can be tested at higher dose rate which is considered a worst case condition for this technology. TID test for CERN equipment are usually performed at:

- the <sup>60</sup>Co source at Fraunhofer INT or ESA/ESTEC and in the future also at CERN: this allows for lot validation of components which are known to be immune to destructive events and displacement damage, as well as optional low dose rate tests.

- Proton beam at PSI: DUTs will also suffer DD and any destructive single event can stop the test. Synergetic effects can thus occur, but often also provide a more global picture of the device under test. However, low dose rate tests are not possible and available beam dimensions do not allow for testing many DUTs at the same time.

- CERN mixed-beam test areas: here tests can be carried out in representative environments and – if required– also at sufficiently low dose rates in order to account for ELDRS. Synergetic effects of DD and destructive SEE have to be accounted for.

For most of the CERN accelerator radiation environments and applications, displacement damage can be considered as a second order problem when compared to the TID effects for two main reasons: the DD only affects a specific category of components (optical components, Zener and integrated bipolar circuits); in addition, in many accelerator areas of concern the expected levels of 1-MeV-equivalent neutron fluence are not that high  $(<5x10^{11} \text{ n/cm}^2/\text{y})$  to induce significant damage to the components. In addition, 1 MeV conversion tables for proton tests and also the mixed-beam environment are available and are often sufficient to characterize the DD behaviour alongside the TID tests when performed in proton or mixed-field facilities. It is important to note that the equivalence also depends on the material and is given for Si generally. DD tests can be conducted with bias or in passive mode. As for the TID case, it is advised either to test the device at intermediated fluence levels in bias conditions close to the real application or to verify all generic parameters of the DUT. The flux at which the irradiation is carried out does not play a significant role as DD effects are generally stable along time. The test facilities usually used in the CERN accelerator context are:

- CEA, nuclear reactor: allowing for an almost pure DD test since only very low TID levels will be accumulated along the test. The facility is usually used either (i) to specifically check for DD effects on optical and other sensitive devices, or (ii) to reach relatively high fluences ( $\sim 1 \times 10^{14}$  n/cm2) in the order of one day

- The neutron gun of the Fraunhofer institute, especially indicated for small components and intermediate fluence range ( $<10^{13}$  cm<sup>-2</sup>)

- Proton beam at PSI: It is important to note that synergetic effects of TID can occur. In this sense, the test is more representative for the final accelerator application where also both effects are present at the same time. The equivalence of the proton fluence in 1 MeV-equivalent neutron fluence depends on the used proton energy and on the material substrate of the DUT. As previously noted for SEE and TID testing, beam dimension limitations do not allow for testing many DUTs at the same time.

- CERN mixed beam test area: as for the PSI case, synergetic effects of TID can occur. However, as representative fields of the final application are used, test results are fully appropriate for the final installation.

### B. SEE testing

SEE is a common name to refer to a large category of stochastic radiation effects on electronics due to singleparticle interactions. Here we focus on the distinction between soft and hard or permanent single events.

Soft single events can happen on digital devices (upset of a memory or register bit) or analogue devices (transients on an amplifier output) or mixed signal devices such as ADCs or DACs. SEFIs, single functional interrupts possibly freezing the component operation, form a border case of the category of the soft single events. All those effects are non-destructive and respective SEE testing requires reading the numeric data of the DUT, checking for data coherence, eventually rewriting the data after a failure is observed or making a power cycle after a SEFI, finally counting the number of failures. Respective radiation tests can be either static (e.g., fixed register data until an upset occurs) or dynamic (e.g., continuous read/write operation on numeric registers). In many cases a tester board, based on a FPGA or microcontroller is used to control the test. Concerning the SET, which is an analogue transient, it can be either detected via a dedicated hardware circuit and then counted for, or transmitted along a cable to acquire its shape on a scope. These few general lines are intended to illustrate that the setup for SEE tests can easily get complicated also imposing cable length constraints, as the maximum distance between the DUT and the tester or the scope often has to be limited in order to conserve the signal integrity and assure the correctness of the test. For direct monitoring during accelerator operation, or tests in large mixed-beam facilities, this has to be correctly accounted for. Since soft SEUs are due to the flux of high-energy hadronic particles, the actual radiation flux is a very important parameter to set in order to have an error rate which can be monitored and allow to correctly counting the events. In addition, also the representativeness of the radiation environment (e.g. the energy of the hadrons) has to be considered (for SEUs in a limited amount, but possibly important for calibration applications which have to consider also the contribution of hadrons at energies between few MeV and tens of MeV). Soft SEU tests for accelerator applications are usually performed at:

- PSI (proton beam): monochromatic beam from 30 to 230 MeV; generally the beam energy of 230 MeV is used; the irradiation flux can be accurately regulated, however not lower than  $\sim 10^7$  cm<sup>-2</sup>s<sup>-1</sup>; synergetic effects of TID and DD have to be considered, but are often of advantage as also representative for accelerator applications. Specific tester boards can be installed close to the DUT and scanning can allow compensating for limited beam dimension which do not permit testing of many DUTs at the same time.

- CERN mixed-beam test area: the radiation field is not monochromatic but representative of the accelerator areas; the radiation field and flux can be regulated by

choosing the installation position; synergetic effects of TID and DD have to be considered, but are often of advantage as also representative for accelerator applications; specific tester boards have to be used in the facility, considering that not only DUTs but also the directly surrounding components are exposed to radiation. - Neutron beam facilities (e.g., at Uppsala): this test avoids having synergetic TID effects. The flux can be regulated but the beam is not monochromatic (distributed or white spectrum with lower high energy tail as applicable to accelerator applications).

Special care must be taken when analysing hard or permanent single events radiation failures as they can lead to device damage if the cause which provoked them, is not removed in due time (e.g., a power switch can be affected by a Single Event Burnout, or a mixed signal device as an ADC can suffer a Single Event Latchup). Without going into the details of the mechanism, in both cases, a current higher than in normal condition, passes through the device and can lead to a possible damage. Therefore, protection methods are required to limit the current and save the device in order to continue the test and cumulate the necessary statistics. Moreover, during the test all critical parameters of the DUT must be checked to verify if the occurrence of a hard single event did not compromise its overall and representative functionality. In addition, if there is no protection method applied or possible, then a significant quantity of DUTs has to be tested. As for soft SEEs, the hadron flux must be regulated in order to be able to count the events in a significant way (i.e. reset cycles and downtime have to be short as compared to failure periods). The setup might also require a scope to acquire the current shape when the event occurs in order to carefully analyse the impact on the system level (e.g., accelerator control). The choice of the facility for testing hard single events is not easy as accelerator environments are characterized by the presence of high-energy hadrons up to several GeVs and there is no mono-energetic test facility easily and sufficiently available providing such high energies. In a mixed beam and high-energetic hadron environment, destructive events are caused by the secondary recoil products created by the impinging particle on the material used within the DUT. The production probability and the LET of the recoil depend on the energy of the impinging particle and on the atomic number of the DUT material. As a rule of thumb, the higher the atomic number of the material, the higher the maximum recoil LET can be with the production probability largely increasing for heavy elements as a function of the impinging beam energy. E.g., if one considers Tungsten of the metallization layer and the vias of the integrated circuit, which is the material with the highest atomic number among the ones used, the recoil can have an LET of up to 40 MeV.cm<sup>2</sup>/mg. In case mono-energetic facilities (e.g., PSI) are to be used, a safety margin on the target fluence has to be taken into account, in order not to under-test the device, ranging from a few up to more than 10 (depending on the radiation hardness of the application location) [2], [8]. This consideration and the respective safety margin are also to be considered for the characterization of soft single event cross section of critical devices. The criteria to apply the safety factor are reported in [8] for three cases:

- I. a low LET onset case (for which the tungsten volume is irrelevant)

- II. a high LET onset example with 0.5 mm3 of tungsten per cell, using a simulated cross section of a COTS SRAM

- III. a simulated, worst-case, tungsten-dominated response, taking the geometry of the SRAM of case (II) while considering 10 times more tungsten per cell and a stepfunction heavy ion cross section with a threshold value of 20 MeV.cm2/mg and therefore above what can be produced in silicon

In order to evaluate the impact of the specific energy dependence on the estimated SEL rate value for a given operation environment, we fold the response functions of the above three cases with the HEH energy spectra of different environments. The respective failure rates per unit HEH fluence are presented in Table 3 for the different environments, normalized to the 100 MeV proton value.

Table 3. Expected failure rate for different responses and environments normalized to the 100 MeV case. Marked in bold are environments for which the respective cross sections are at least 3 times larger that at 100 MeV. For these cases, the increase with respect to the 230 MeV case is also shown in brackets [8].

| Environment         | Case I | Case II          | Case III         |

|---------------------|--------|------------------|------------------|

| 230 MeV             | 1.8    | 2.8              | <b>3.4</b> (1.0) |

| LHC- high Shielding | 0.7    | 0.8              | 0.9              |

| Polar Orbit         | 0.9    | 1.6              | 2.5              |

| Atm 375m            | 1.0    | 2.1              | <b>3.3</b> (1.0) |

| LHC Low Shielding   | 1.3    | <b>5.2</b> (1.9) | <b>9.7</b> (2.8) |

| LHC tunnel          | 1.5    | 9.6 (3.4)        | 20 (5.8)         |

| Atm 20 km           | 1.2    | 10 (3.6)         | 23 (6.7)         |

| LHC Exp             | 1.6    | 18 (6.3)         | 40 (12)          |

As can be seen in Table 3, for Case I (low LET onset, saturated proton cross section example) the failure rate for all environments is within a factor 2 of the 100 MeV value, which can therefore be considered as representative for them. However, for Cases II and III (tungsten driven, saturating at  $\uparrow$  3 GeV), the dependence of the SEL rate with the environment is very strong. For cases with tungsten present near the SV and high LET onset values, the differences are significant (e.g. the LHC tunnel cross section for the Case II model is a factor 3-4 larger than that at 230 MeV). The failure rate is underestimated by a factor ~20 if one considers the 100 MeV cross section for a component with a response of the type of Case III used in an LHC tunnel or atmospheric 20 km altitude environment. Even considering the 230 MeV monoenergetic response, the operational SEL rate could be 6-7 times larger than the one extracted experimentally, which depending on the application can lead to crucial limitations. Therefore, the representativeness and corresponding safety margins to be applied for each case need to be carefully considered.

However, radiation tests can be carried out without taking these important (and possibly costly) safety margins if performed in a CERN test area where the detailed accelerator environment is correctly reproduced. Alternatively, an optional or additional heavy ion test can be performed in order to analyse the threshold LET. This allows for a partial answer; if the DUT shows a threshold larger than 40 MeV.cm<sup>2</sup>/mg, then it can be safely used for accelerator applications. Conversely, if the threshold LET turns to be lower than 40 MeV.cm<sup>2</sup>/mg, it means that destructive failures can happen with a rate which is difficult to evaluate as it is not trivial to translate a heavy ion cross section into a hadron cross section without applying again significant safety margins.

In summary, the radiation test facilities that can be used in these cases are:

- CERN mixed beam test facility: as it reproduces exactly the accelerator radiation spectra

- Proton beam at PSI: one possibly underestimates the risk of destructive events unless a proper safety margin is applied on the target proton fluence (Table 3).

- Optional or additional heavy-ion tests in order to decide on a possible usability of a component candidate.

Table 4 provides a brief overview of the radiation effects, test facilities and methodologies for COTS components and COTS based boards used for accelerator applications in relatively high radiation areas. Furthermore guidelines and standards from the space community can be consulted: a list is provided in Figure 8 and the on-line links are available at [9].

| Standard                       | TID | DDE      | SEE                   |

|--------------------------------|-----|----------|-----------------------|

| ESCC 22900-4                   | X   |          |                       |

| ESCC 25100-1                   |     |          | X                     |

| MIL-STD 883J<br>Method 1019.9  | x   |          |                       |

| MIL-STD 883J<br>Method 1017.3  |     | Neutrons |                       |

| EIA JESD57                     |     |          | Heavy ions            |

| EIA JESD59                     |     |          | Neutrons              |

| MIL-STD 750-1<br>Method 1080.1 |     |          | MOSFETS<br>Heavy ions |

ESCC

European Space Component Coordination

MIL-STD

US Military Standard

EIA-JESD

Electronic industries Association / JEDEC Standard

JEDEC

Joint Electron Device Engineering Council

Figure 8. List of test standards used by the space community.

### IX. TYPICAL ARCHITECTURE OF THE ACCELERATOR EQUIPMENT

Figure 9 reports the list of the accelerator groups which develop radiation tolerant equipment. The column *System* indicates if the equipment is entirely designed at CERN (*Custom*) or partially uses commercial solutions (*Semi-Custom*). Most of the applications are based on COTS components and only a few groups use in their designs radiation hard devices, developed by the Microelectronic group of the Physics (PH) department at CERN. Medium and high power components are especially used for the power converters and the kicker magnets applications. The other groups use analogue, digital or mixed devices to have equipment which is able to read external sensors and inputs, threat the signals, and execute commands by means of actuators.

Table 4:Summary of the test type, facilities, test modality andmitigation actions for COTS components and COTS based boardsused in high-radiation accelerator areas.

| Test | Facility                                 | How                                                                        | Mitigation<br>actions                                                           |

|------|------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| SEE  | CERN test area<br>PSI<br>Heavy Ion       | Test points for<br>SET<br>Current<br>consumption<br>SEE on numeric<br>data | Filter<br>TMR<br>De-Rating<br>(Power<br>switches)<br>Anti-latchup<br>Redundancy |

| TID  | Fraunhofer<br>ESTEC<br>CERN Co-60<br>PSI | Test points for<br>drift checking<br>and parameter<br>degradation          | Foresee the<br>drift effect at<br>design stage                                  |

| DD   | CEA,<br>Fraunhofer                       | Test points for<br>drift and<br>parameter<br>degradation                   | Foresee the drift effect at design stage                                        |

| Team   | A settister.              | Devices<br>components |                        |   | Custom      | Trans         |

|--------|---------------------------|-----------------------|------------------------|---|-------------|---------------|

| Team   | Activity                  | Analog                | Digital<br>Mixed Power |   | System      | Туре          |

| TE/MPE | QPS                       | x                     | x                      |   | Custom      | COTS          |

| TE/EPC | Power Converter           | x                     | x                      | x | Custom      | COTS          |

| TE/CRG | Cryogenics                | x                     | x                      |   | Custom      | COTS/Rad hard |

| BE/ABT | Interlock and Kicker      | x                     | x                      | x | Semi-Custom | COTS          |

| EN/STI | Radiation Monitor         | x                     | x                      |   | Gustom      | COTS          |

| BE/BI  | Beam instrumentation      | x                     | x                      |   | Custom      | COTS/Rad hard |

| BE/RF  | RF Cavities               | x                     |                        | x | Custom      | COTS          |

| BE/CO  | Control equipment         | x                     | x                      |   | Custom      | COTS          |

| EN/MEF | Survey                    | x                     | x                      |   | Custom      | COTS          |

| TE/VSC | Vacuum equipment          | x                     | x                      |   | Semi-Custom | COTS          |

| IT     | IT tools                  |                       | x                      |   | Semi-Custom | COTS          |

| EN/EL  | Light, LED                | x                     |                        |   | Semi-Custom | COTS          |

| GS/ASE | Safety, Alarms            | x                     | x                      |   | Semi-Custom | COTS          |

| EN/STI | Radiation test activities | x                     | x                      | x |             |               |

Figure 9. List of the Accelerator groups developing radiation tolerant equipment.

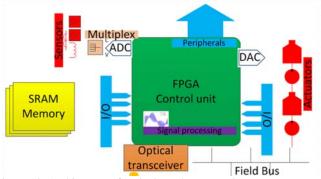

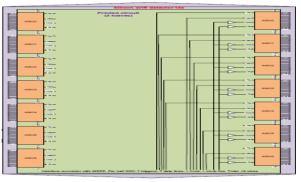

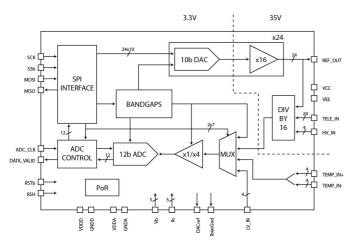

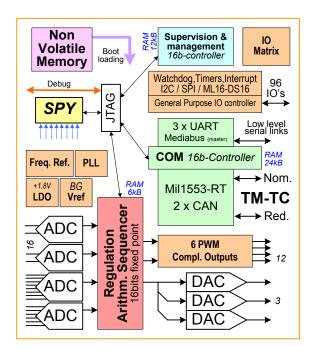

A typical board of a radiation tolerant equipment installed in the LHC tunnel (e.g. power converter controller, Quench Protection System cards, beam screen heaters, RadMon), is based on the architecture depicted in Figure 10. The block diagram, extremely simplified with respect to the real implementation, aims at showing the parts which are common to several designs. The FPGA is the core unit which manages the analogue and digital inputs, the other peripherals, the outputs, the signal processing and the communication with the high level front-end via a field bus. Analog to Digital (AD) and/or Digital-to-Analog (DA) converters are used to acquire signals from sensors and send analogue waveforms to actuators. In many cases, multiple inputs and outputs signals are to be managed, requiring the use of multiplexer and analogue switches. Depending on the dynamic range of the input/output signals, amplifiers are integrated. Each system uses about 50-200 number of digital I/O. For a few applications, optical transceivers are used to treat high rate data from optical fibres. Furthermore Flash and RAM memories are used to store fix configurations and buffer data, respectively.

Making this typical board radiation tolerant requires a significant amount of testing if COTS components are used. As explained above, several candidates are to be tested in

order to choose a good candidate; then a batch of component is acquired and qualified.

Figure 10. Architecture of typical accelerator equipment.

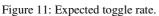

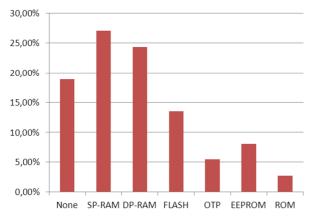

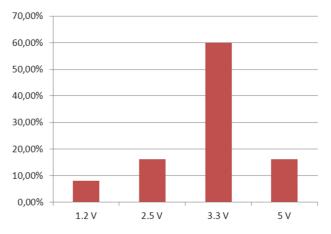

Although each application has its own peculiarities and requires specific electrical performance for a given component, there are several parts which are common to different projects and are reported in Figure 11. The Intellectual Property (IP) of functionalities very similar to those in Figure 11 exist and can be implemented with radiation hard library of semiconductor fabrication facilities. Although the rad-hard single ASIC is more expensive than an equivalent COTS part, proposed by the manufacturers for large markets, the price can still be competitive if an ASIC is used by several groups and a volume of 1000-5000 units is required. Furthermore, the accelerator applications require neither special packaging, nor the qualification of the part over large temperature range and against mechanical vibrations, as it happens for the space projects. On this basis, implementing the required commune functionalities with radiation hard ASICs could be an option to be considered for future developments and design.

### X. CONCLUSIONS

This paper described the test strategy and procedures to be applied for the radiation qualification of the equipment installed in the LHC and its injectors. The type of equipment, its location, the actual impact of radiation induced failures on the overall accelerator operation are considered to drive the most convenient and appropriate radiation assurance. The radiation environment encountered at CERN accelerators, the large number of electronic systems and components, as well as the actual impact of radiation induced failures on the overall accelerator operation, strongly differ from the environment and systems usually relevant for space applications. Additional constraints, but in some cases also simplifications, which have to and can be considered with respect to the test and monitoring standards, have been respectively summarized. To date, most of the accelerator applications rely on COTS devices; however, there are a few functionalities, needed and critical for the single application, such as AD converters, optical transceivers, or analogue switches, which are very demanding in terms of electrical performance. Thus only a few (and in some cases just one) candidates can be chosen from the COTS market; furthermore this selected device must be radiation tolerant. Up to now it was always possible to find a good solution but in the future it can be considered to implement the critical functionalities,

which are in common to several applications, in order to have a significant volume of unit, in radiation hard ASIC.

| ADC                   | 18-24 bit resolution, Sampling rate 10-50 <u>kSps</u> 16-18 bit resolution, Sampling rate 50-200 <u>kSps</u> 14-16 bit, Sampling rate 60 <u>MSps</u>     |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAC                   | <ul><li>12-16 bit resolution</li><li>10 V range</li></ul>                                                                                                |

| Signal process        | • FIR filter<br>• Median filter                                                                                                                          |

| MUX                   | Multiple channels for AD/DA                                                                                                                              |

| Peripheral Management | <ul> <li>ADC, DAC (if not embedded)</li> <li>Field bus</li> <li>Optical transceivers</li> <li>Serial ports</li> </ul>                                    |

| ULA                   | Programmable logic                                                                                                                                       |

| 1/0                   | 100 to 200     LVDS drivers     SERDES input for optical transceivers (2.4 Gb/s-5 Gb/s)                                                                  |

| SRAM                  | No SEL (> 40 MeV.cm <sup>2</sup> /mg)     No SEFI on the reading/writing circuitry     Limited TID effect     Sensitive to SEU to measure hadron fluence |

Figure 11. List of ASICs of interest for the accelerator groups.

### XI. ACKNOWLEDGMENT

The authors would like to thank the members of the R2E project and accelerator Radiation Working Group (RADWG) and the equipment groups for their collaboration.

### XII. REFERENCES

- [1] K. Roed, M. Brugger, and G. Spiezia, "An overview of the radiation environment at the LHC in light of the R2E irradiation test activities," CERN ATS Note 2011-077, 2011.

- [2] R. Garcia Alia et al., "Energy dependence of tungstendominated SEL cross sections", submitted to IEEE TNS.

- [3] Radiation to Electronics (R2E) Taskforce at CERN. Available: r2e.web.cern.ch R2E project

- [4] RADiation Working Group (RADWG) list of facilities. Available: radwg.web.cern.ch

- [5] CHARM website, <u>www.cern.ch/charm</u>

- [6] ESA Standard, F. Sturesson, "Total Ionizing Dose (TID) testing," 9 June 2009. http://space.epfl.ch/webdav/site/space/shared/industry\_media/0 4%20TID%20Testing%20F.Sturesson.pdf.

- [7] Total Dose Steady State Irradiation test, European Space Standard. Available: https://escies.org/download/specdraftapppub?id=29

- [8] R. Garcia Alia et Al., "SEL Cross Section Energy Dependence Impact on the High Energy Accelerator Failure Rate", submitted to IEEE TNS.

- [9] http://radwg.web.cern.ch/RadWG/Pages/links.aspx

### Assessment of Mixed Signal Technology

### M. Bacci<sup>*a*</sup>, F. Bigongiari<sup>*a*</sup>, C. Boatella Polo<sup>*b*</sup>, R. Dittrich<sup>*b*</sup>, M. Inversi<sup>*a*</sup>, R. Jansen<sup>*b*</sup>

<sup>a</sup>SITAEL, 56122 San Piero a Grado (Pisa), Italy <sup>b</sup>ESA, 2200 AG Noordwijk, The Netherlands

amicsa2014@cern.ch

### Abstract

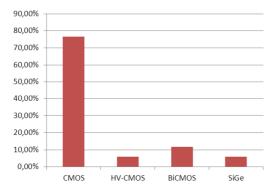

In 2013, within the ECI (European Component Initiative) program of the European Space Agency, the activity "Assessment and characterisation of Mixed Signal Technology" has been initiated. In this paper the activities performed for the assessment of an European mixed signal technology for the development of ASICs for space applications will be described. The assessment has been conducted through different surveys and the results obtained from them will be presented and analysed. Finally a brief description of the test vehicle for the technology characterization will be provided.

### I. INTRODUCTION

The "Assessment and characterisation of Mixed Signal Technology" activity has been funded by European Space Agency in order to collect information of mixed signal ASIC processes with particular focus on their capability for space applications. The information on requirements to be supported by mixed signal technologies have been collected from [1], [2] and [3] and through a survey with the collaboration of space community. The tentative was addressed to look for information about similar on-going activities and on existing analogue, digital and mixed signal libraries or ASICs for space applications already manufactured or designed to avoid to duplicate the efforts.

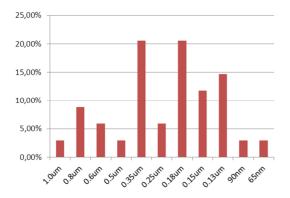

The collected data on the user need has been compared against the processes capabilities available in Europe for mixed signal ASIC manufacturing. At the end of this review one particular process has been choosen for a further reliability and radiation characterization.

The paper is organized as follows: in the Section II the surveys carried out will be described. The results will be shown and discussed in Section III. In Section IV, a description of the test vehicle will be reported together to the test procedure and the list of the parameters to be measured; finally the conclusion will be reported in Section V.

#### **II. DESCRIPTION OF SURVEYS**

The assessment of an European mixed signal technology for ASIC design and manufacturing has been driven by 3 different surveys. In the first survey a comparative assessment and verification about the availability of several existing European mixed signal technologies has been performed. In the second survey, inputs covering the needs for mixed-signal ASICs from the space community and the Agency's planned missions have been collected. In last survey, information about the existing rad hard libraries and design kits in terms of primitive devices, SEEs, TID and reliability performances have been collected.

In the next paragraphs each survey will be described and detailed.

### A. First Survey: Mixed Signal Technologies Availability

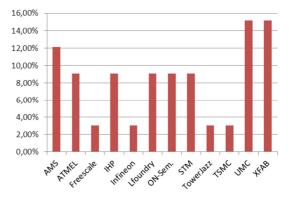

This survey has been addressed to European foundries accessible to the Agency's member states. Twelve (12) European and Non-European manufacturers have been contacted obtaining reply from six (6) of them: Atmel, Austria Micro Systems (AMS), IHP Microelectronics, ON Semiconductor, Telefunken Semiconductor and XFAB. In total, data from 18 technology processes have been collected and analyzed.

The survey was split into 2 sections. The first part focused on general items related to the foundry availability, in particular addressing following questions:

- o Licensing and conditions for use

- Foundry expected lifetime

- o Foundry loading and product range

- Foundry process options

- Manufacturing turnaround time

- Manufacturing options (Full mask, MPW, MLM; Runs per year; longer availability) and their cost

- Cost of the supported tool chain (external and custom)

- Cost of the digital and analogue design-kit (front- and back-end)

- Supported batch manufacturing

- Supported Digital and Analogue development flows and constraints

- Foundry macro libraries cost

- Third party macro libraries access, conditions, cost and license

- Design kit for usage within space user community and the right for modifications

- Eventual technical support and maintenance of space-DK/libraries for European Space community

In the second part of the survey, specific information about environment, quality, digital performances and analogue performances of different processes have been collected.

### i. Environment

The questions related to environment features have been:

- Temperature range (operational and storage)

- o Voltage range

- Radiation tolerance (TID, SEE: SEL, SEU, SET, SEGR, ...)

- o ESD and EMC levels supported

### ii. Quality

The questions related to quality features have been:

- Intrinsic reliability data/performance

- Wafer thickness

- Process lifetime

- Mean time to failure (FIT)

- Manufacturing yield

- o Manufacturing quality systems

- Inspectibility of the manufacturing quality system and PID

- o Cost associated with quality inspection

- Reporting and inspectibility of the process control monitors

- Process stability reporting the manufacturing process changes

- Failure analysis support

- Manufactured high-reliability and space qualified flows/components

#### iii. Digital Performances

The questions related to digital performances features have been:

- o Gate density

- Power consumption

- o Clock frequency

- Supply voltage range

- Number of metal layers

- o Leakage

- Cell library (combinational and sequential; commercial and radiation hardened variants)

- Foundry and/or Third party digital macro libraries (commercial or radiation-hardened; development/qualification state)

- IO Pads (Voltage levels, ESD, EMC, ...)

- Manufacturing spread (power consumption, clock frequency, leakage)

- Accuracy of the models

- o Development tool flow supported

- Sign-off tool chain

### iv. Analogue Performances

The questions related to analogue performances features have been:

- Analogue IO Pads (Voltage levels; ESD; EMC; ...)

- Number of poly layers

- o Sub-threshold conducting model

- Accuracy of the models

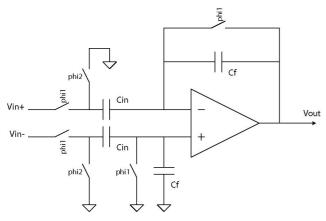

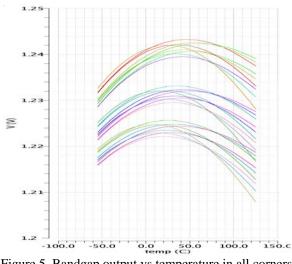

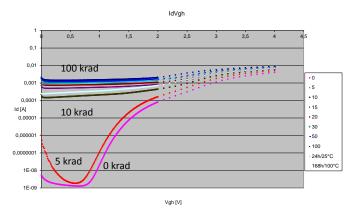

- MOS transistors availability

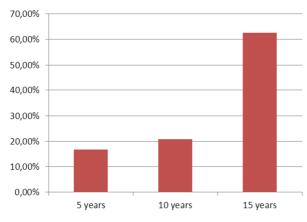

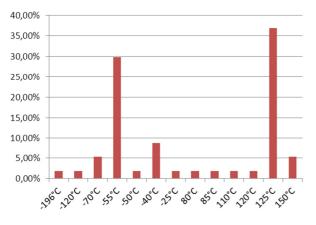

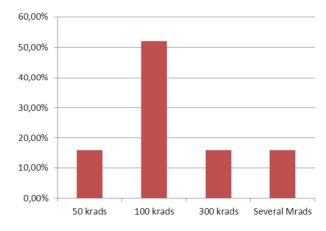

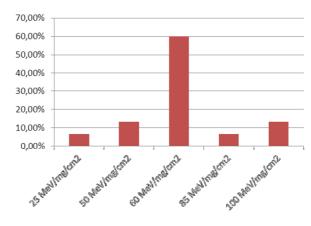

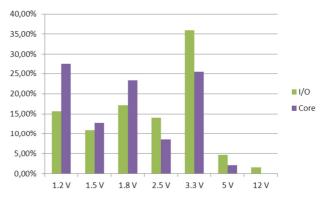

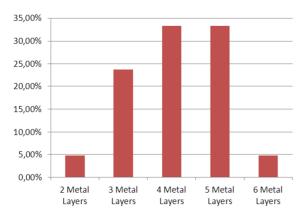

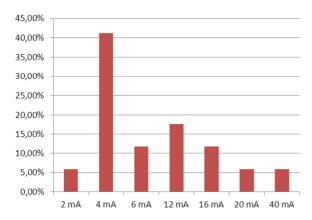

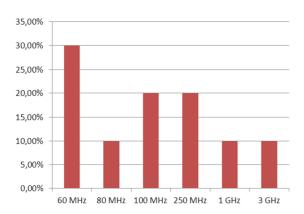

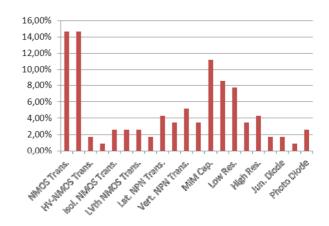

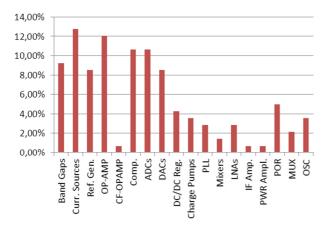

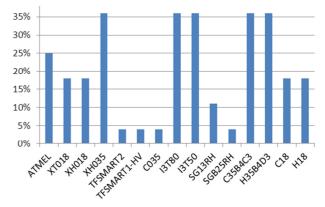

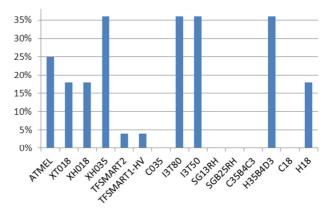

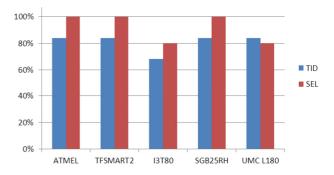

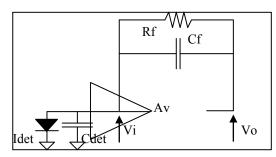

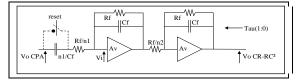

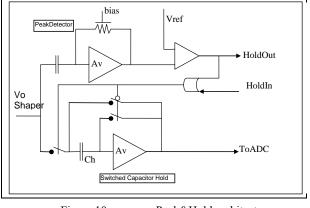

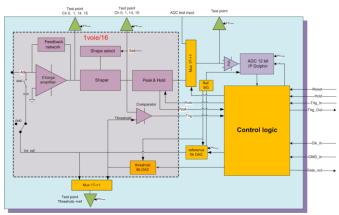

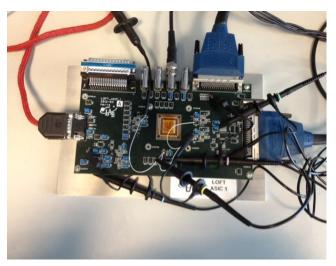

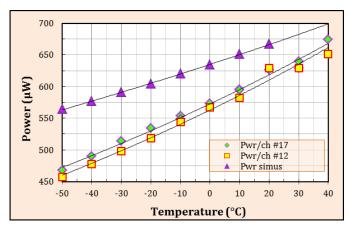

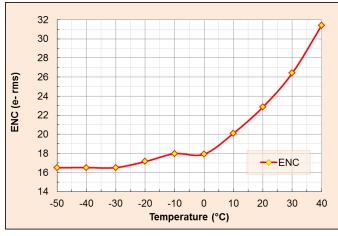

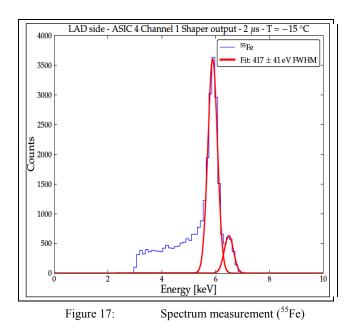

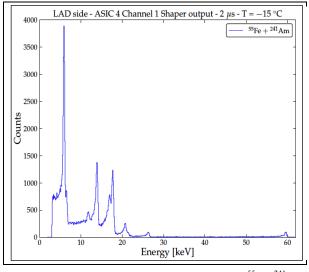

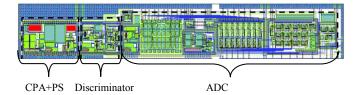

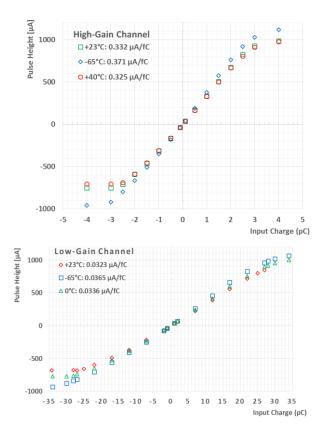

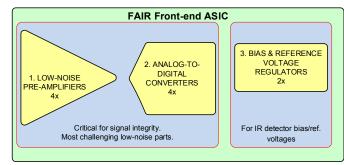

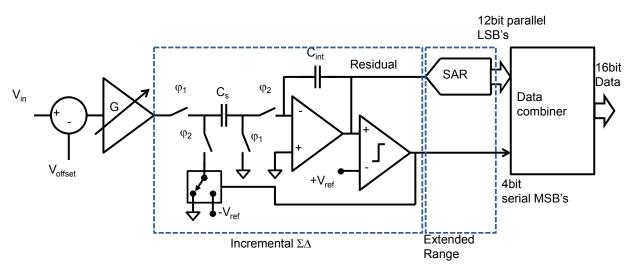

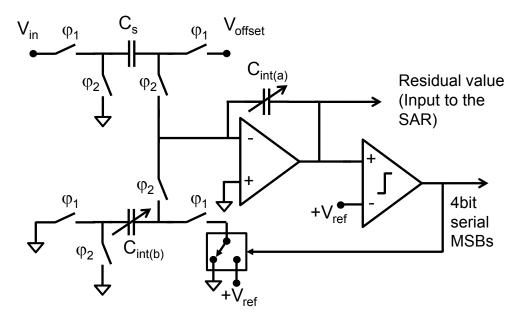

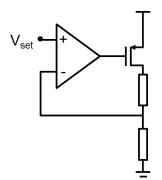

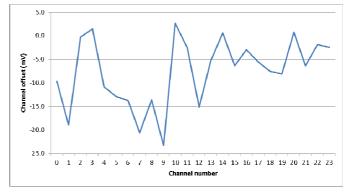

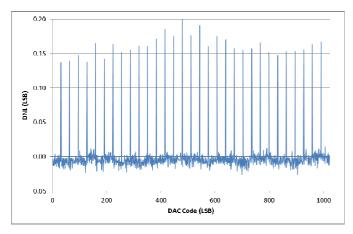

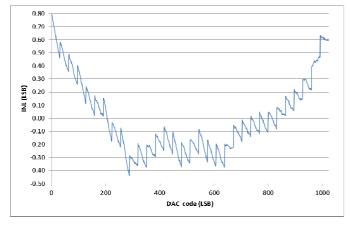

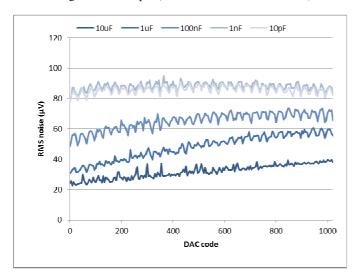

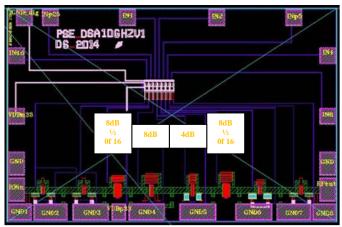

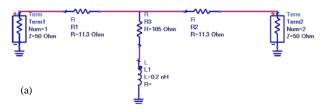

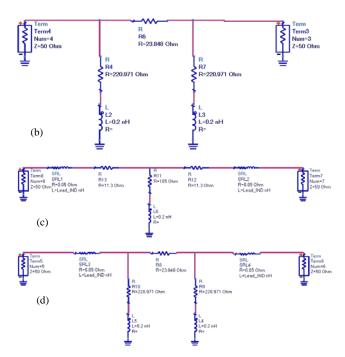

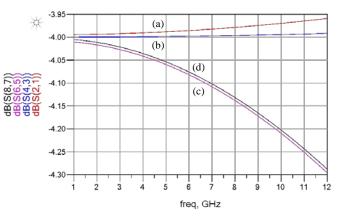

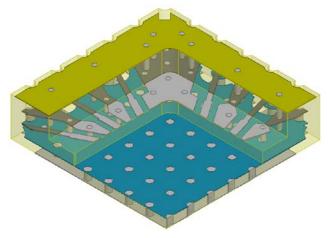

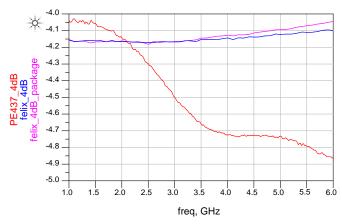

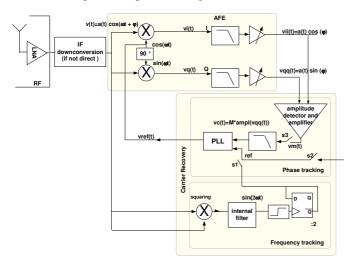

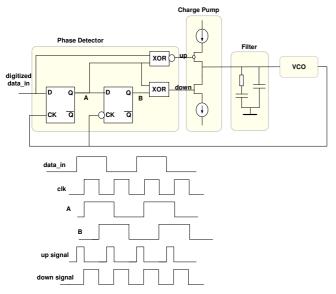

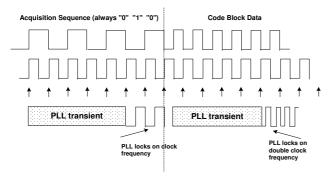

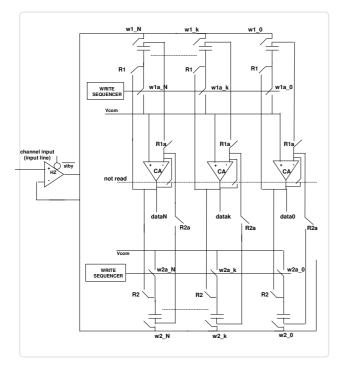

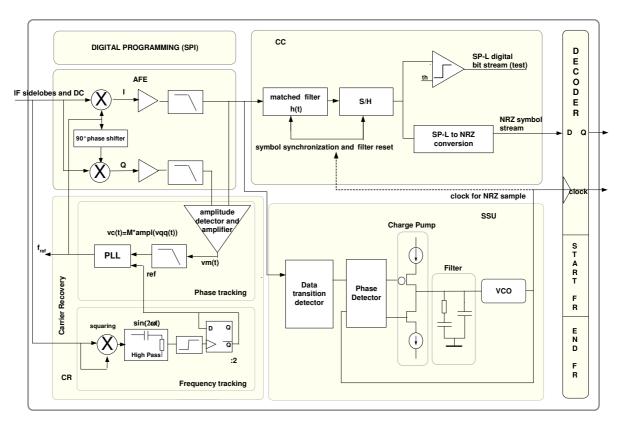

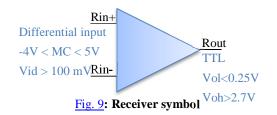

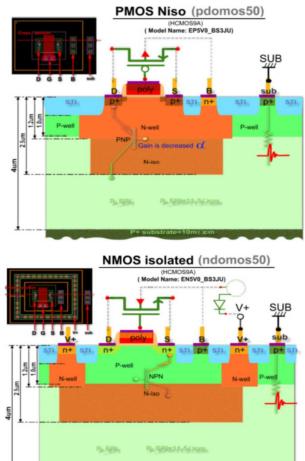

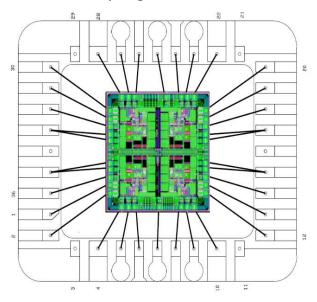

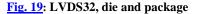

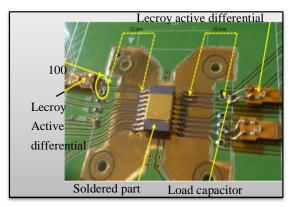

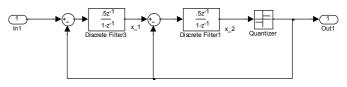

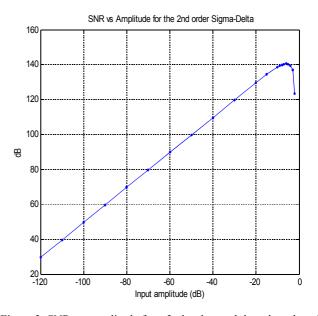

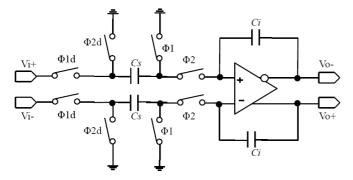

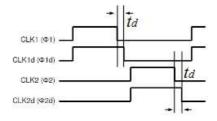

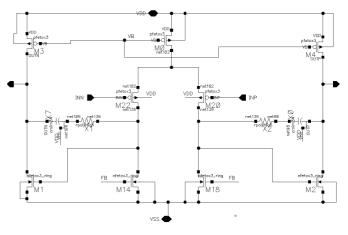

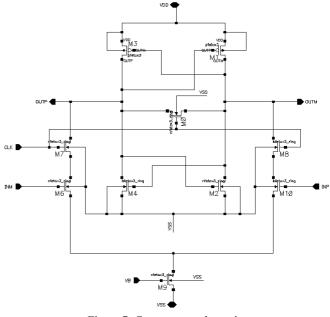

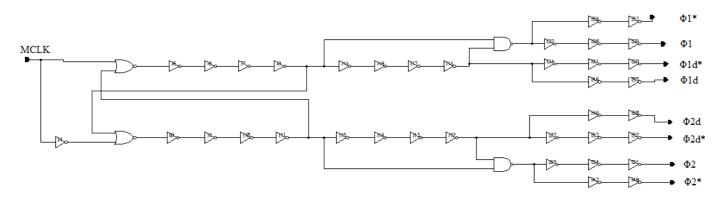

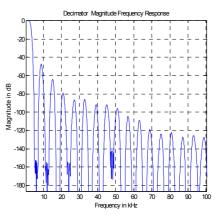

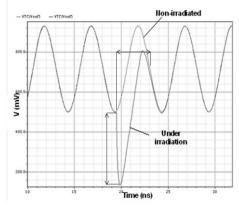

- o Bipolar transistors availability