# IMB-CNM R&D Activities on Silicon Detectors for ILD

S. Hidalgo, P. Fernández-Martínez, M. Baselga, V. Greco, D. Quirion and G. Pellegrini

> Centro Nacional de Microelectrónica (IMB-CNM-CSIC) Barcelona, Spain

#### **Outline**

#### 1) Tracking Silicon Detectors with Internal Gain and Proportional Response

- ✓ PiN Detectors

- ✓ Low Gain Avalanche Detectors (LGAD)

#### 2) Low Gain Avalanche Detectors

- ✓ Why Internal Gain?

- ✓ Why Low Gain?

- ✓ Linear Mode Operation. Gain Definition

#### 3) Pad Diodes with Internal Gain

- Multiplication Layer. Design considerations

- Design of the Edge Termination. JTE Concept

- Numerical Simulation of Irradiated Devices

- ✓ Fabrication Process

- Electrical and Technological Characterization

- Experimental Results (Vbr, Ileak, Charge Collection Capabilities)

- ✓ Irradiation Studies

#### 4) Low Gain Microstrips and Pixels Detectors

- ✓ Fabrication Process

- ✓ Preliminary Electrical Performances

#### 5) Extension of the Low Gain concept to Thin Detectors

6) Target: Low Gain Thin Resistive **MicroStrips and Pixels Detectors Fabrication**

### Tracking Silicon Detectors with Internal Gain and Proportional Response

#### **PiN** based Diodes

- **Proportional Response**

- **Good efficiency**

- **Good spectral range**

- Segmentation is technologically available (strip and pixel detectors)

#### **Internal Gain**

#### Low Gain Avalanche Detectors (LGAD)

- **Proportional Response (Linear** Operation)

- **Good efficiency**

- **Good spectral range**

- **Better Sensibility**

- Thin detector integration with the same signal and higher collection efficiency

- Better signal/noise ratio

- **After Irradiation**

- Worse signal to noise ratio (lower quality signal + noise increment)

- **Increment of the power consumption**

- Radiation Damage damage (specially relevant on n-on-p structures)

- → After Irradiation

- Similar pre & post irradiation signal (higher quality signal + lower noise increment)

- Lower increment of the power consumption

- Radiation Damage (specially relevant on n-on-p structures)

### Why Internal Gain?

Increases the radiation hardness of the detector, leading to similar signals before and after irradiation: Charge multiplication off-sets the charge lost due to trapping during the drift of the carriers [1]. Higher electric fields reduce the collection times, reducing the trapping probability. Charge Collection Efficiency is improved, keeping a proportional response. Thinner detectors are available with the same signal. Fast detectors are also foreseen [1]. The noise components are not increased at the same pace than the multiplied signal. As a consequence the signal to noise ratio is improved.

#### Why Low Gain?

| _ | riigii daili lilipiles liigilei levels di lilulupileation noise (lililei ent to the stochastic process |

|---|--------------------------------------------------------------------------------------------------------|

|   | of multiplication [2]), spoiling the improvement of the Signal to Noise ratio.                         |

|   | Collection times are increased with gain (more charge to be collected), increasing the                 |

|   | trapping efficiency and avoiding the off-setting of the charge loss.                                   |

Avoid cross-talk among adjacent pixels/strips.

[1] H. Sadrozinski, et al. 20th RD50 Workshop, Bari (Italy), 2012

[2] R.J. McIntyre. IEEE TED-13, No.1 p.164-168, 1966

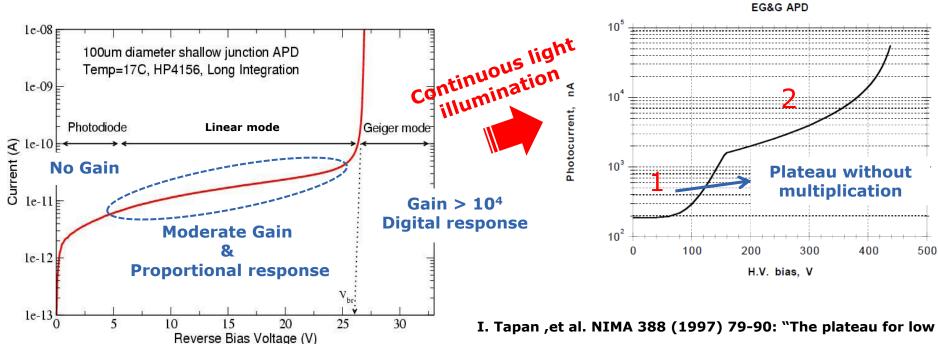

### Linear Mode Operation. Gain Definition

- **Diodes with multiplication can operate in Linear or Geiger mode**

- **Linear** mode: Moderate gain & Proportional response

- **Geiger** mode: Very high gain & Digital response

**Gain Definition**

[1] A.G. Stewart et al. in Proc. of SPIE, Vol. 6119, 2006

bias voltage may be taken to correspond to unit gain [...] and the gain for higher bias measured simply as the ratio of the pulse size to that plateau"

#### Pad Diodes with internal Gain

M. Bruzzi, IEEE TNS-48(4) 2001: "The general approach followed by the HEP community in radiation-damage studies has been to investigate the radiation effects in silicon detectors using the simplified geometry of a single pad detector."

#### Pad Diodes with internal Gain

M. Bruzzi, IEEE TNS-48(4) 2001: "The general approach followed by the HEP community in radiation-damage studies has been to investigate the radiation effects in silicon detectors using the simplified geometry of a single pad detector."

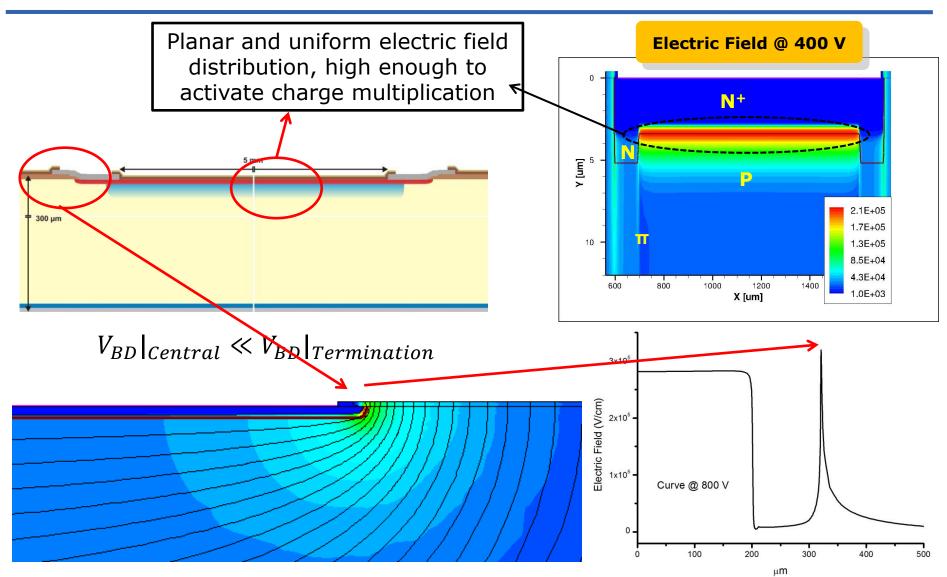

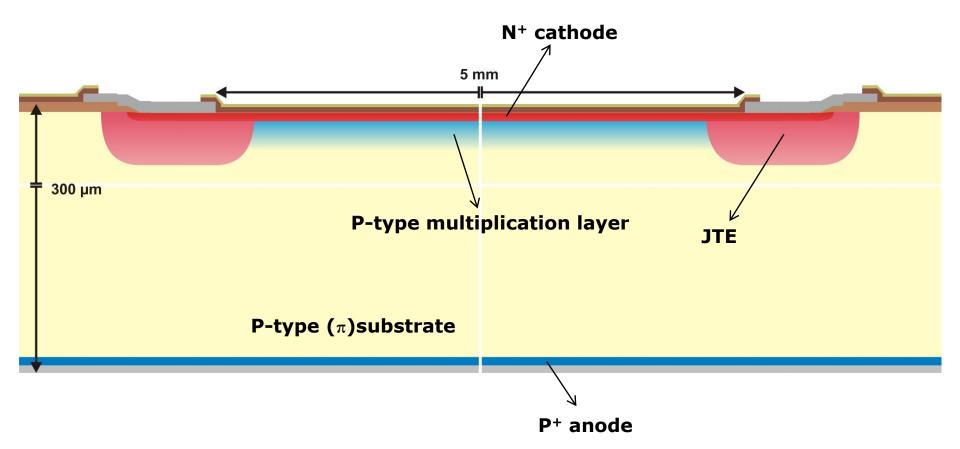

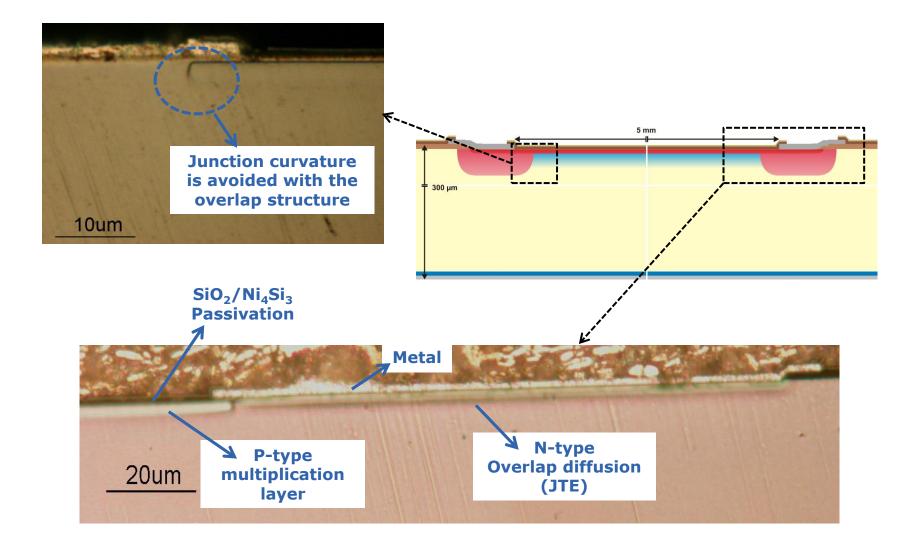

#### Design of the Multiplication Region

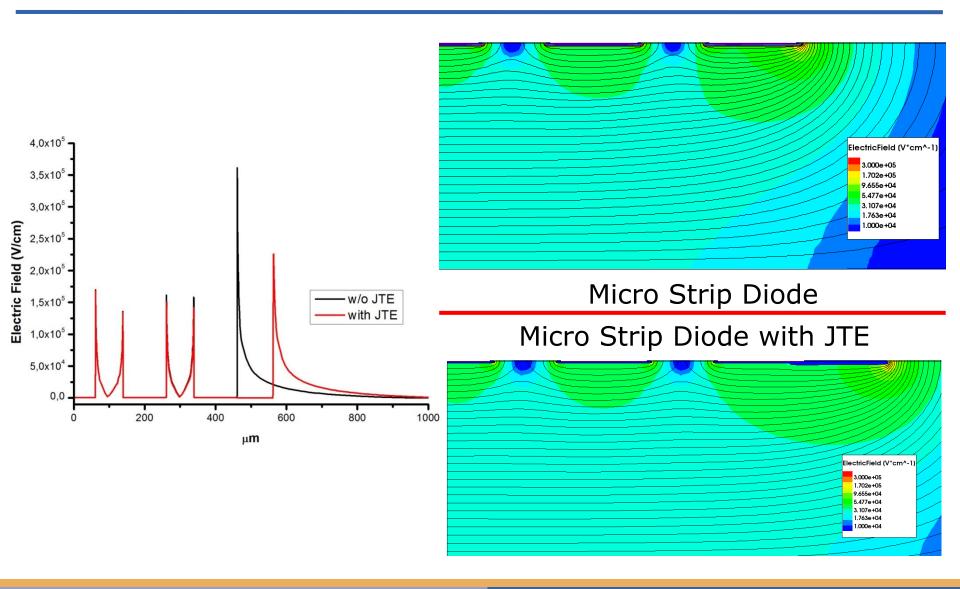

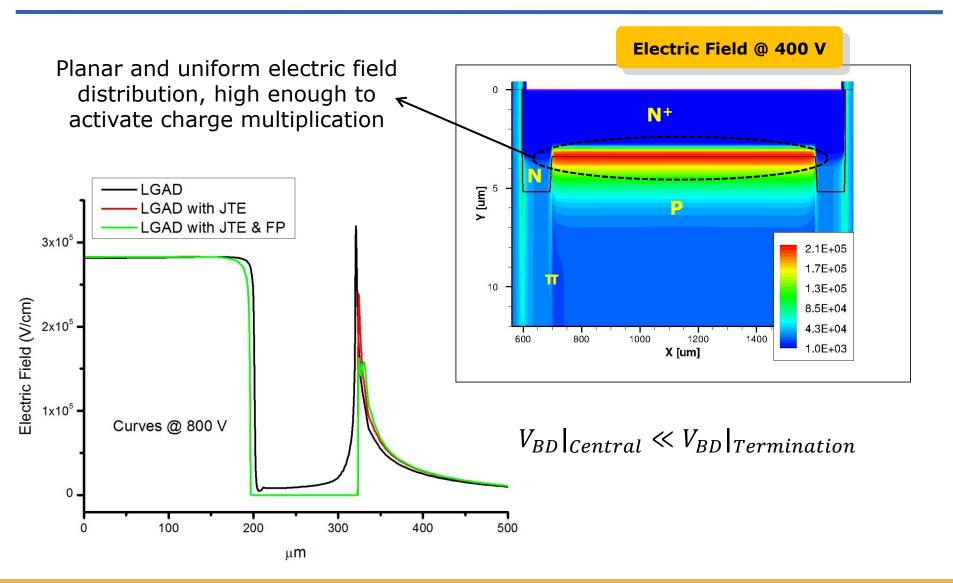

Junction Termination Extension (JTE). Peripheral low doping N-well to increase the voltage capability of this area, reducing the Electric Field in the periphery, allowing the maximum Electric Field is reached in the multiplication area (N+/P junction)

TABLE 3.1. High-Voltage Device Termination Techniques

| Technique                        | Typical Breakdown<br>Voltage (%) <sup>a</sup> | Peak Surface<br>Electric Field<br>(%) <sup>b</sup> | Typical Device Size | Device<br>Types  | Remarks                                                                                |

|----------------------------------|-----------------------------------------------|----------------------------------------------------|---------------------|------------------|----------------------------------------------------------------------------------------|

| Planar junction                  | 50                                            | 80                                                 | Small (<100 mils)   | BJT, MOSFET      | Seldom used for high-<br>voltage devices                                               |

| Planar junction with field ring  | 80                                            | 80                                                 | Medium (≤1 in.)     | BJT, MOSFET, SCR | Well suited for a large<br>number of devices<br>per wafer                              |

| Planar junction with field plate | 60                                            | 80                                                 | Medium (≤1 in.)     | BJT, MOSFET      | Usually used in<br>conjunction with<br>field ring                                      |

| Positive bevel                   | 100                                           | 50                                                 | Large (>1 in.)      | Rectifier, SCR   | Well suited for single<br>device per wafer                                             |

| Negative bevel                   | 90                                            | 60                                                 | Large (>1 in.)      | SCR              | Well suited for single<br>device per wafer                                             |

| Double positive bevel            | 100                                           | 80                                                 | Large (>1 in.)      | SCR              | Well suited for single<br>device per wafer only                                        |

| Positive etch contour            | 90                                            | 60                                                 | All                 | BJT, MOSFET, SCR | Well suited for a large<br>number of devices<br>per wafer                              |

| Negative etch contour            | 80                                            | 60                                                 | All                 | BJT, MOSFET, SCR | Well suited for a large<br>number of devices<br>per wafer                              |

| Junction termination extension   | 95                                            | 80                                                 | All                 | BJT, MOSFET, SCR | Well suited for both<br>single devices and a                                           |

|                                  |                                               |                                                    |                     |                  | large number of<br>devices per wafer;<br>high leakage current<br>passivation sensitive |

<sup>&</sup>quot; As percentage of parallel-plane case.

b As percentage of bulk.

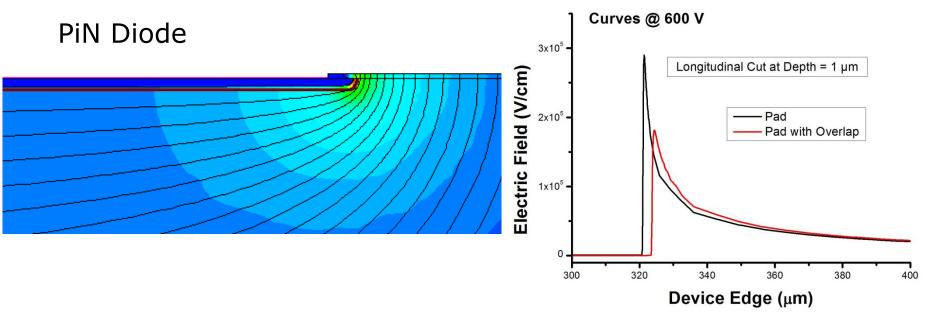

PiN Diode with JTE

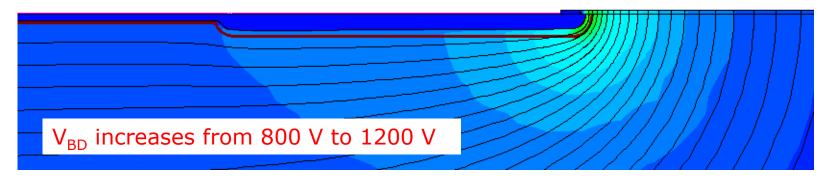

### Strip Detectors Edge Termination

15/35

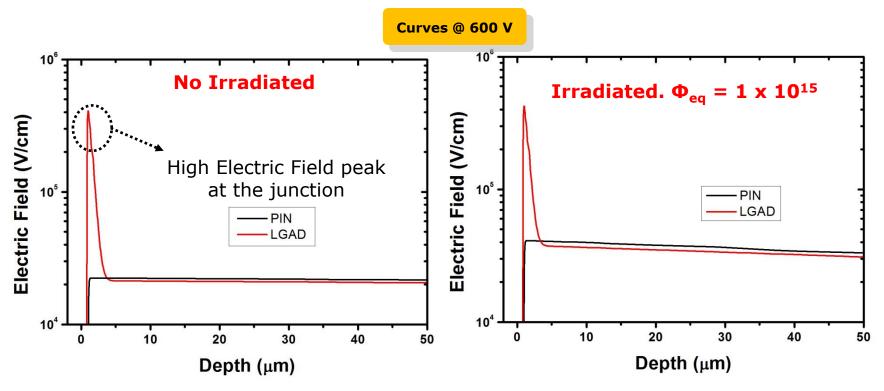

#### Simulation of the Irradiated Devices

- **PiN**: electric field strength at the junction increases after irradiation

- **LGAD**: electric field strength at the junction is held after irradiation

#### •Impact Ionization Model:

**Universty of Bolonia**

#### • Irradiation Trap Model (Perugia Model):

Acceptor;  $E = E_c + 0.46 \text{ eV}$ ;  $\eta = 0.9$ ;  $\sigma_e = 5 \times 10^{-15}$ ;  $\sigma_{\rm h} = 5 \times 10^{-14}$  $\sigma_h = 2 \times 10^{-14}$ Acceptor;  $E=E_c + 0.42 \text{ eV}$ ;  $\eta=1.613$ ;  $\sigma_e = 2 \times 10^{-15}$ ;  $\sigma_h = 2.5 \times 10^{-15}$ Acceptor;  $E = E_c + 0.10 \text{ eV}$ ;  $\eta = 100$ ;  $\sigma_e = 2 \times 10^{-15}$ ; E= E<sub>v</sub> - 0.36 eV;  $\eta$ =0.9;  $\sigma_{e}$  = 2.5 x 10<sup>-14</sup>;  $\sigma_{h}$  = 2.5 x 10<sup>-15</sup> Donor;

$Conc = \eta \cdot \phi$

16/35

#### Simulation of the Irradiated Devices

| CCE | @ | <b>400</b> | V |

|-----|---|------------|---|

|     |   |            |   |

| Φ <sub>eq</sub> [cm <sup>-2</sup> ] | Simulated | Measured |

|-------------------------------------|-----------|----------|

| No Irrad                            | 7         | 10       |

| 1e14                                | 6         | 6        |

| 5e14                                | 3         | 2        |

See G. Kramberger at RD50 Albuquerque

First estimation by simulation. We must work to enhance this study

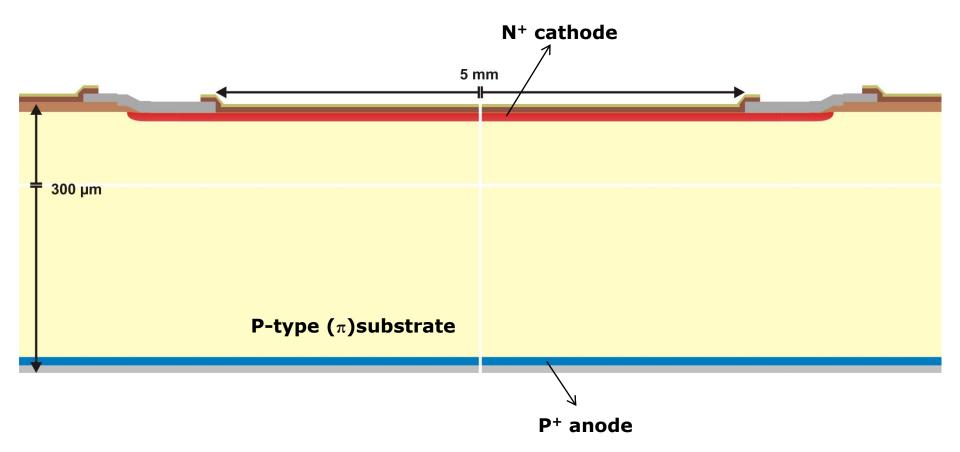

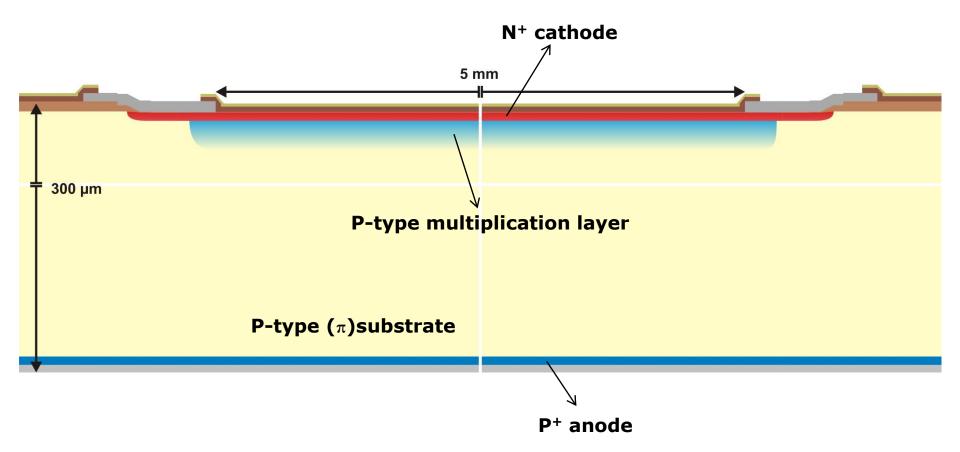

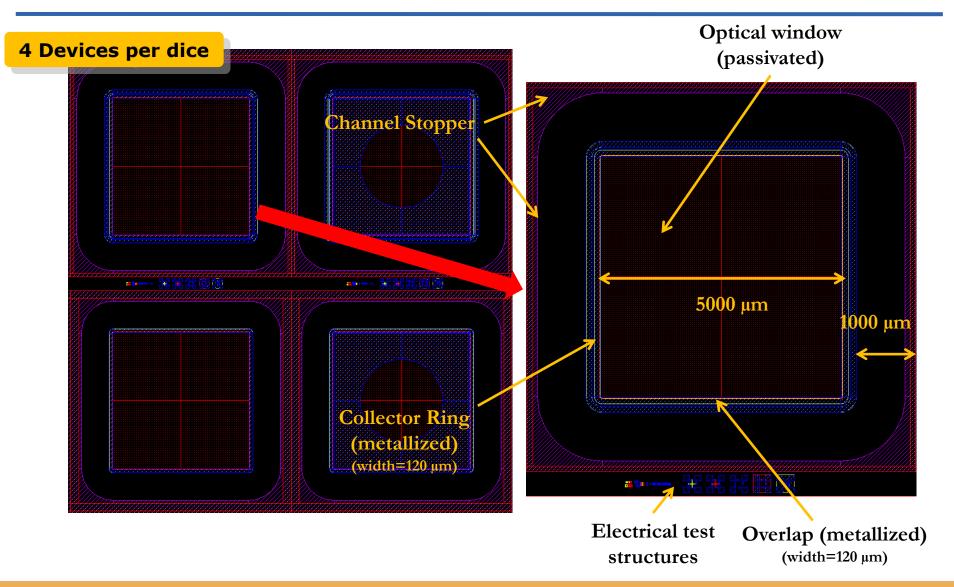

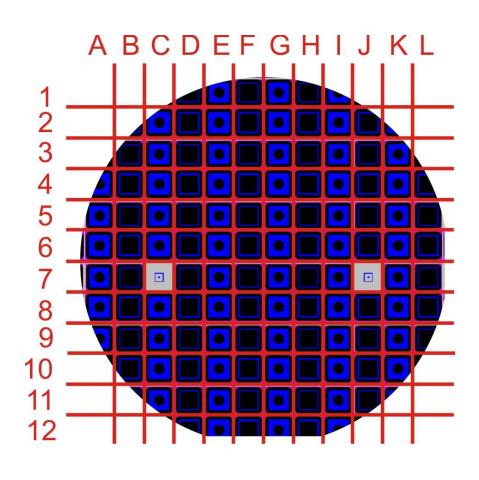

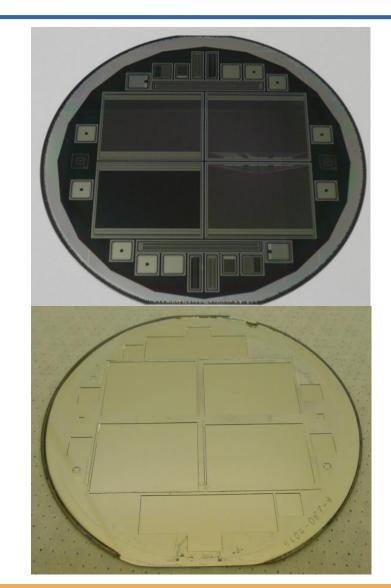

### Fabrication (I)

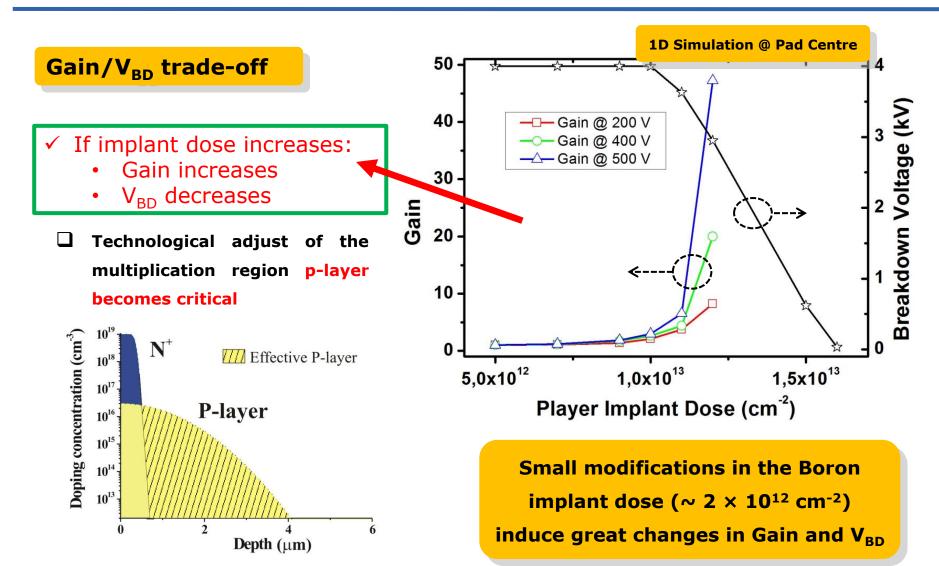

# Fabrication (II)

| Wafer<br>Number | P-layer Implant<br>(E = 100 keV)        | Substrate features                                                      |

|-----------------|-----------------------------------------|-------------------------------------------------------------------------|

| 1               | 1.0 × 10 <sup>13</sup> cm <sup>-2</sup> | HRP 300 (FZ; $\rho$ >10 KΩ·cm; <100>; T = 300±10 μm)                    |

| 2               | $1.1 \times 10^{13}  \text{cm}^{-2}$    | HRP 300 (FZ; $\rho$ >10 KΩ·cm; <100>; T = 300±10 μm)                    |

| 3               | 1.2 × 10 <sup>13</sup> cm <sup>-2</sup> | HRP 300 (FZ; $\rho$ >10 KΩ·cm; <100>; T = 300±10 μm)                    |

| 4               | $1.3 \times 10^{13} \text{ cm}^{-2}$    | HRP 300 (FZ; $\rho$ >10 KΩ·cm; <100>; T = 300±10 μm)                    |

| 5               | $1.4 \times 10^{13} \text{ cm}^{-2}$    | HRP 300 (FZ; $\rho$ >10 KΩ·cm; <100>; T = 300±10 μm)                    |

| 6               | $1.5 \times 10^{13} \text{ cm}^{-2}$    | HRP 300 (FZ; $\rho$ >10 KΩ·cm; <100>; T = 300±10 μm)                    |

| 7               | $1.6 \times 10^{13} \text{ cm}^{-2}$    | HRP 300 (FZ; $\rho$ >10 KΩ·cm; <100>; T = 300±10 μm)                    |

| 8               | $2.0 \times 10^{13} \text{ cm}^{-2}$    | HRP 300 (FZ; $\rho$ >10 KΩ·cm; <100>; T = 300±10 μm)                    |

| 9               | (PIN wafer)                             | HRP 300 (FZ; $\rho$ >10 KΩ·cm; <100>; T = 300±10 μm)                    |

| 10              | $1.1 \times 10^{13} \text{ cm}^{-2}$    | HRP OXG (DOFZ; $\rho$ = 5-15 K $\Omega$ ·cm; <100>; T = 285±25 $\mu$ m) |

| 11              | $1.3 \times 10^{13}  \text{cm}^{-2}$    | HRP OXG (DOFZ; $\rho$ = 5-15 K $\Omega$ ·cm; <100>; T = 285±25 $\mu$ m) |

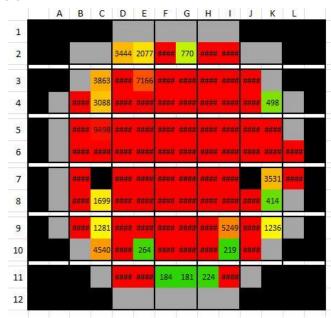

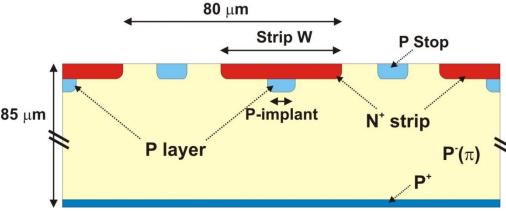

### Technological Characterization

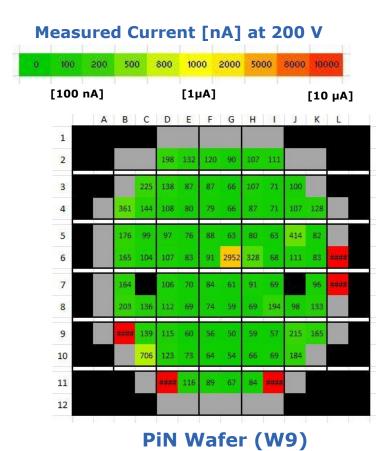

#### **Electrical Characterization**

Fabrication yield worsens with increasing implant dose for the p-type multiplication layer.

Wafers were fabricated in the same run, following exactly the same fabrcation steps. Only difference between W9 and W8 is that PiN wafer was not implanted with the multiplication implantation.

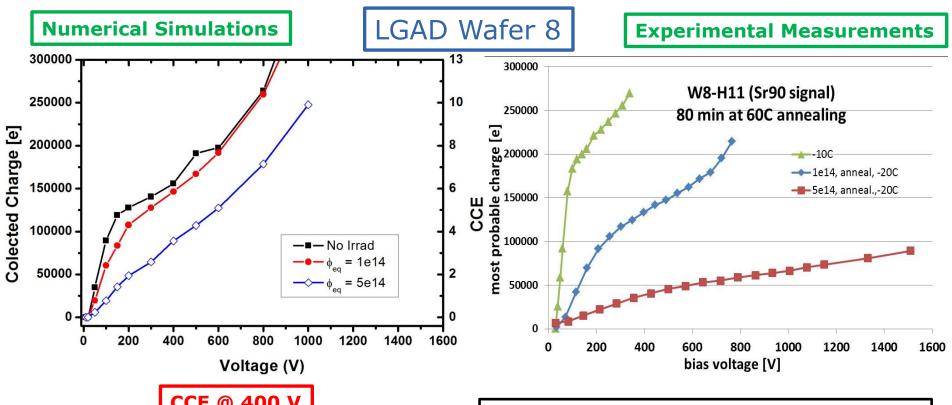

Wafer 8 (Implant dose =  $2 \times 10^{13}$  cm<sup>-2</sup>)

We are working in the yield improvement

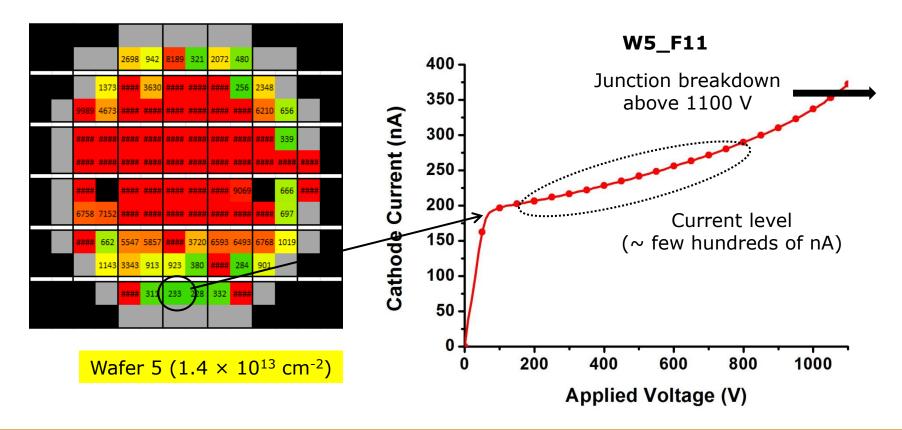

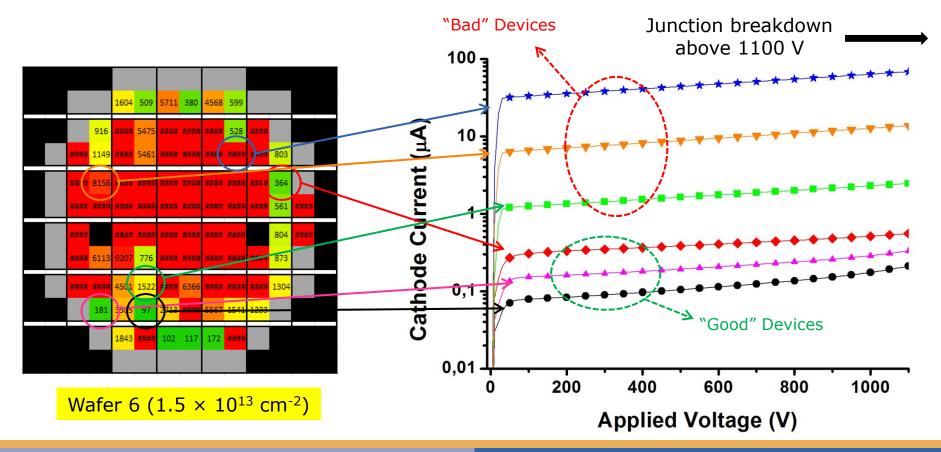

### Experimental Results (I)

# **√** "Good" Devices

- Current levels below 1 µA thorough the whole voltage range

- → Junction breakdown above 1100 V (\*Except Wafer 8: < 800 V, still good)

### Experimental Results (II)

# **X** "Bad" Devices

- Current levels above 1 µA thorough the whole voltage range

- → Junction breakdown above 1100 V (\*Except Wafer 8)

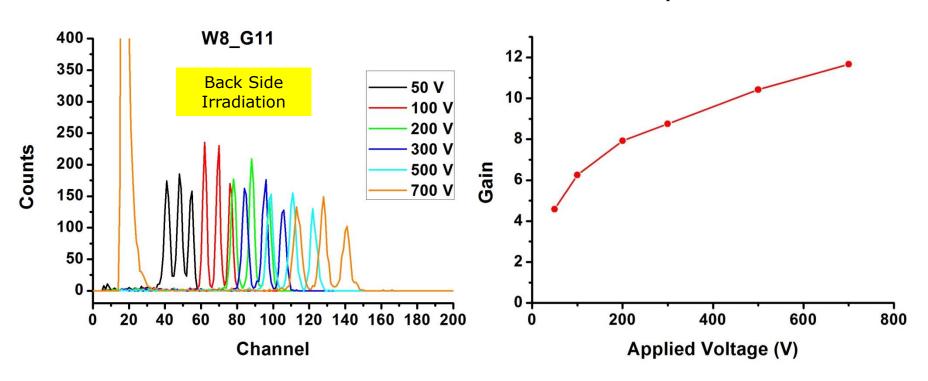

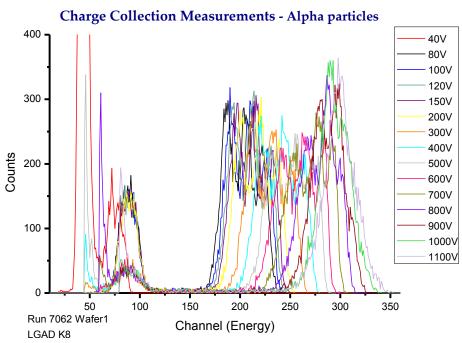

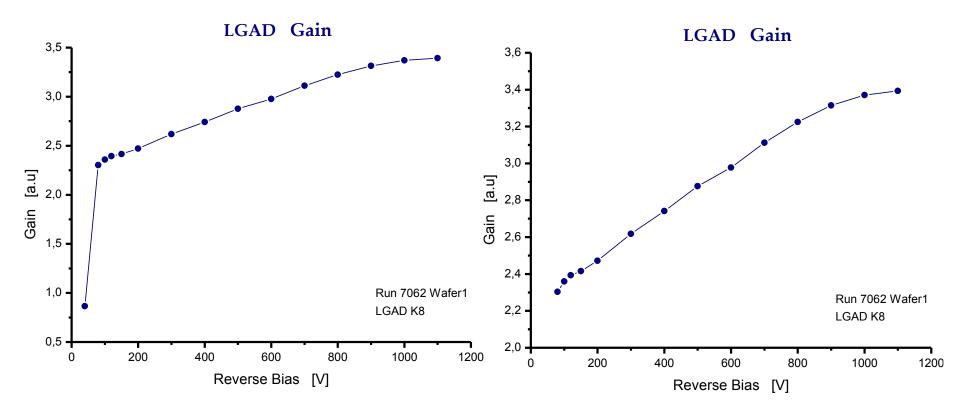

### Charge Collection (Alpha)

Multiplication factor has been tested with tri-alpha (239Pu/241Am/244Cm) source.  $\rightarrow$  Irradiation through the anode (back side, 1  $\mu$ m Aluminum):

$$Gain_{@V} = \frac{Channel\ Central\ peak_{@V}}{Channel\ Central\ peak_{No\ multiplied}}$$

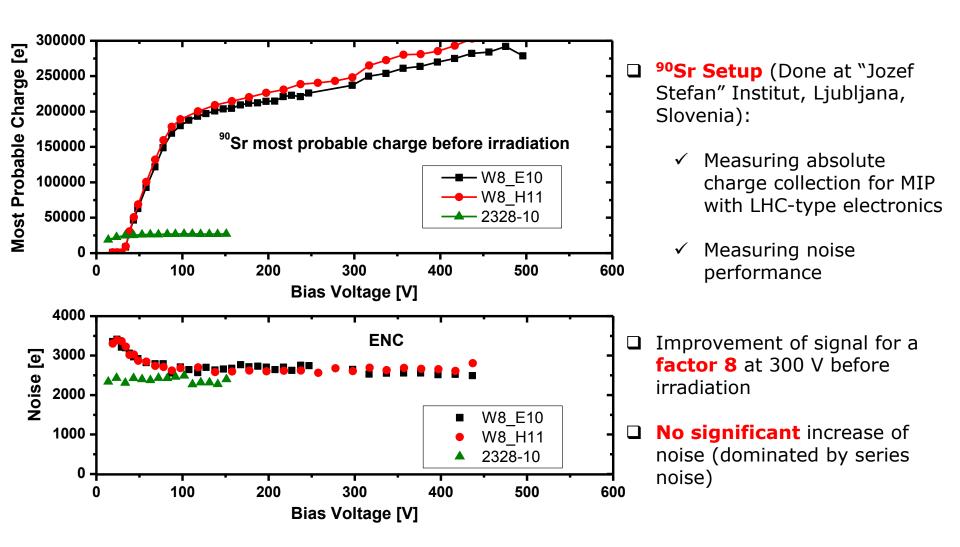

### Charge Collection (Mips)

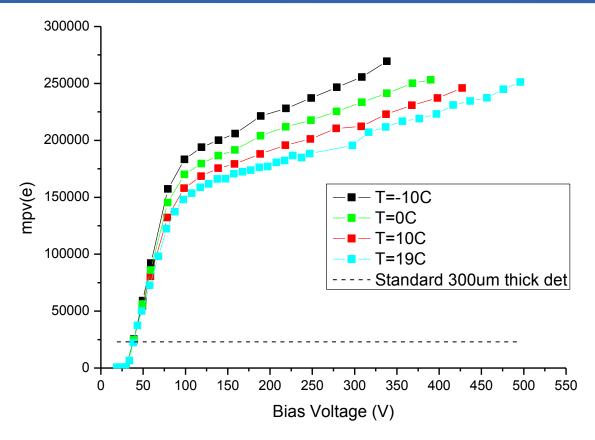

### Temperature Dependence of Multiplication

- ☐ Increase of multiplication at lower temperatures is expected do to larger impact ionization coefficients.

- ☐ It seems that there is a limit on multiplication of around a factor of 10.

26/35

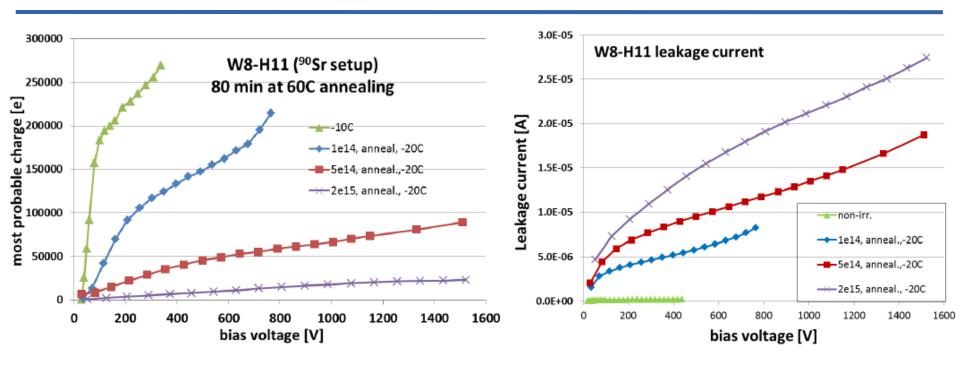

#### **Irradiation Studies**

- ☐ Detectors irradiated with **neutrons** in IJS (Ljubljana)

- Multiplication **decreases** significantly with irradiation:

- ✓ Breakdown performance is good,

- ✓ Leakage current increase is not linear with fluence,

- $\checkmark$  I<sub>leak</sub> increase with fluence is smaller due to **degradation** of multiplication.

$$I_{leak} = M_I \cdot I_{gen} = M_I \cdot \alpha \cdot \Phi$$

For more details see G. Kramberger's talk at 22nd RD50 Workshop, University of New Mexico, Albuquerque, USA

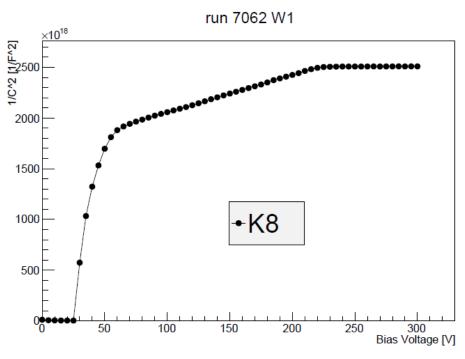

#### Electrical Characterization (New Run, W1)

## Electrical Characterization (New Run, W1)

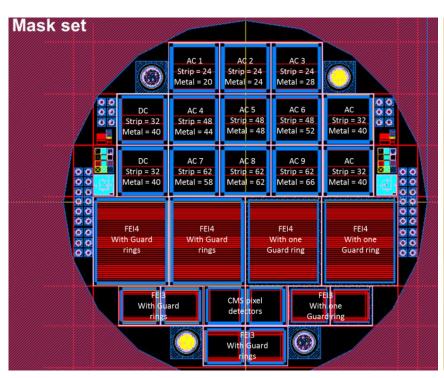

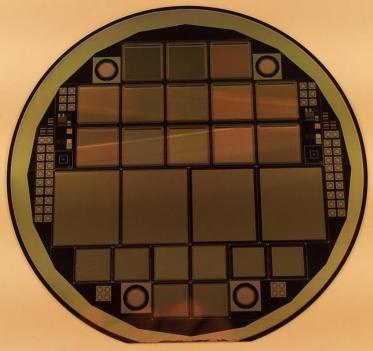

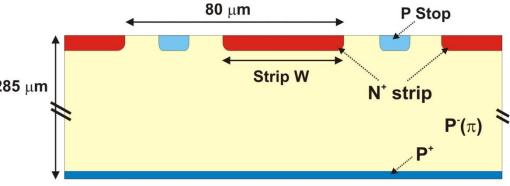

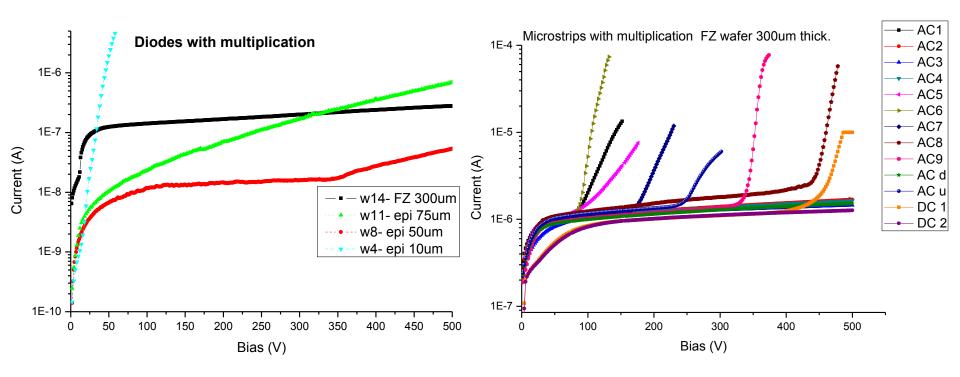

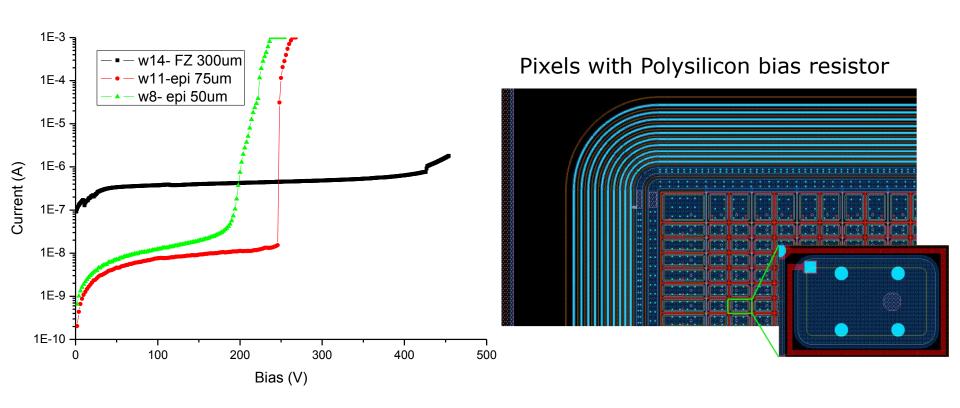

### New Fabrication Run: Low Gain Microstrip and Pixel Detectors

- Project financed by CERN RD50 Collaboration.

- Fabrication **run** already **finished**, very preliminary measurements.

- Different geometries (pad, microstrip, pixel), implant doses and substrates.

- Junction termination extension (JTE) not implemented for this first run: **Lower** breakdown voltage may be expected.

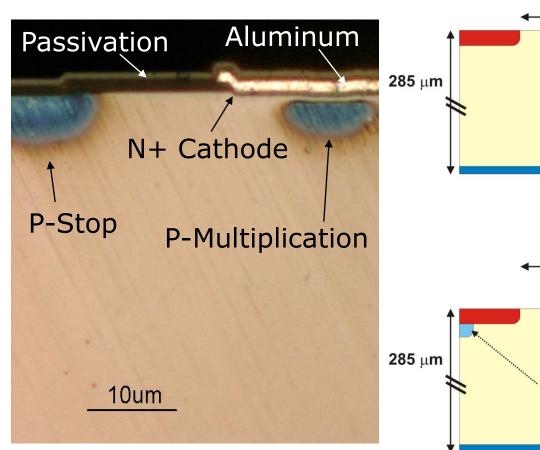

### Low Gain Microstrip and Pixel Detectors Technology

### Electrical Characterization. Low Gain Pad and microStrips

- □ Breakdown performance is good although the JTE was not used for these devices ( $V_{BR} > 500 \text{ V}$ ).

- Variations in breakdown voltage due to different metal layer over implant overlapping (Field Plate Overlapping).

#### Electrical Characterization. CMS pixel detectors

- All pixels are connected through a 1 Mohm polysilicon bias resistor.

- □ Breakdown is again very good before irradiation.

- □ **Current** scales with volume, but for **thinner** devices breakdown occurs at lower voltages due to higher electric fields.

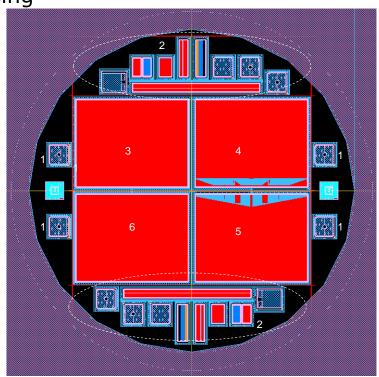

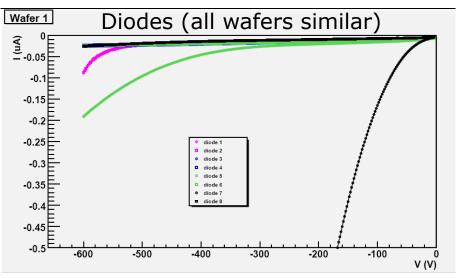

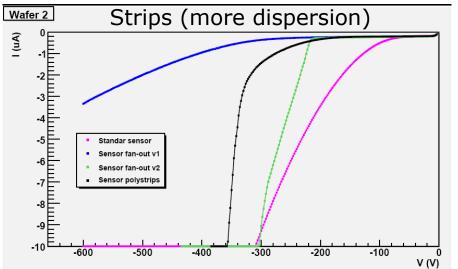

#### New Fabrication Run: Thin Detectors

- Fabrication run with 6 inch wafers (285 microns thick)

- 5 more wafers ready to be thinned (100 microns thick)

- **Double metal** technology to implement integrated fanout

- **Polysilicon strip** detectors included in the mask

- Further **characterization** and **test-beam** missing

- Future **Low Gain** Implementation

- 1. Standard CMS pad diodes

- 2. CMS test structures

- 3. Standard AC strip det.

- 4. Strip det. with fan out v1

- 5. Strip det. with fan out v2

- 6. Detector with poly strips

34/35

#### **New Fabrication Run: Thin Detectors**

#### **Conclusions**

- We have presented the IMB-CNM activities on Silicon Detectors for ILD,

- Our work is focused to improve the performance and stability against radiation of silicon detectors for tracking applications,

- The concepts of avalanche and internal gain in pads, strips and pixel detectors are introduced

- LGAD is presented and compared with the PiN diode,

- First LGAD detectors have been fabricated,

- Excellent breakdown performance of the diodes before and after irradiation,

- Diodes with gain perform very well before the irradiation,

- Gain of  $\sim 10$  for  $^{90}$ Sr electrons,

- After irradiation the multiplication drops significantly:

- ightharpoonup At 2e15 cm<sup>-2</sup> is around ~1.5 at 1000 V,

- Current and noise scale as expected with multiplication,

- ✓ New fabrication run with low gain strips and pixel detectors under test. Preliminary results are very promising.

- Extension to thin detectors,

- Target: Fabrication of low gain thin resistive microstrips and pixels detectors.

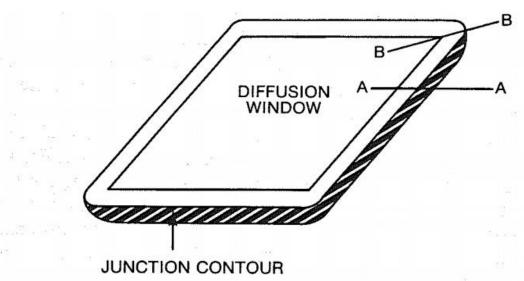

#### **Diffused Planar Junctions**

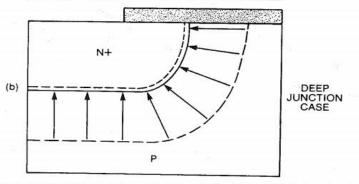

- Using a planar diffusion technology we can fabricate a large number of devices on a single wafer by selective diffusion of impurities through a silicon dioxide masking layer.

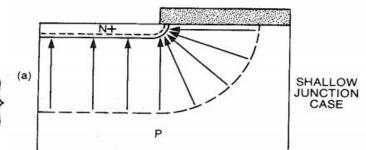

- Due to the lateral doping extension through the window periphery, we can identify three important areas at the junction formed using this technology.,

- Plane into the diffusion window,

- Cylindrical at the mask edges (Line A at the figure), and

- Spherical at the sharp corners (Line B).

- This curvature effects produce a reduction in the voltage capability (till 50 % of the ideal value).

Fig. 3.11. Planar junction formed by diffusion through a rectangular diffusion window.

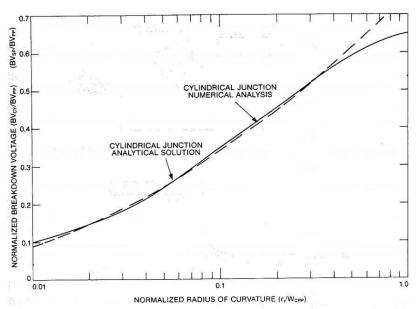

### **Cylindrical Junction**

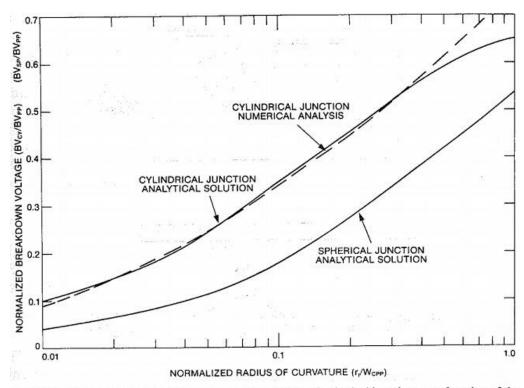

The breakdown voltage is given by,

$$\frac{BV_{\rm CYL}}{BV_{\rm PP}} = \left\{ \frac{1}{2} \left[ \left( \frac{r_{\rm j}}{W_{\rm c}} \right)^2 + 2 \left( \frac{r_{\rm j}}{W_{\rm c}} \right)^{6/7} \right] \ln \left[ 1 + 2 \left( \frac{W_{\rm c}}{r_{\rm j}} \right)^{8/7} \right] - \left( \frac{r_{\rm j}}{W_{\rm c}} \right)^{6/7} \right\}$$

Expression that can be approximated by,

$$\frac{BV_{\text{CYL}}}{BV_{\text{PP}}} = \left[0.871 + 0.125 \ln\left(\frac{r_{\text{j}}}{W_{\text{c,PP}}}\right)\right]^2$$

Fig. 3.16. Normalized breakdown voltage of cylindrical and spherical junctions as a function of the normalized radius of curvature.

3.17. Electric field crowding at the edges of (a) shallow and (b) deep junction.

- BVcyl is always less than BVpp.

- increases (which implies junction depth) increase increases and reduces the difference with BVpp.

#### **Spherical Junction**

The breakdown voltage is given by,

BVsp is always less than BVcyl.

$$\frac{BV_{\rm SP}}{BV_{\rm PP}} = \left(\frac{r_{\rm j}}{W_{\rm c}}\right)^2 + 2.14 \left(\frac{r_{\rm j}}{W_{\rm c}}\right)^{6/7} - \left[\left(\frac{r_{\rm j}}{W_{\rm c}}\right)^3 + 3\left(\frac{r_{\rm j}}{W_{\rm c}}\right)^{13/7}\right]^{2/3}$$

Fig. 3.16. Normalized breakdown voltage of cylindrical and spherical junctions as a function of the normalized radius of curvature.