Abstract

The next generation of silicon pixel detectors for

the phase-II upgrade of ATLAS and CMS at the

High Luminosity LHC sets unprecedented requirements to the microelectronic readout

systems. Front-end integrated circuits must

provide advanced analog and digital functions in

pixel readout cells with a pitch of a few tens of a

$\mu {\rm m}.$  Operating at low power dissipation, they must

handle huge data rates and stand extreme

radiation levels. The community of designers is

studying the 65nm CMOS technology as a tool to

achieve the ambitious goals of these future pixel

systems, and has organized itself in the RD53 project to tackle the challenges associated with

mixed-signal design in this process.

## The RD53 effort towards the development of a 65 nm CMOS pixel readout chip for extreme data rates and radiation levels

Valerio Re on behalf of the RD53 collaboration valerio.re@unibg.it New challenges of the RD53 collaboration

## 95% digital, Charge digitization ~256k pixel channels per chip

- Pixel regions with buffering

- Data compression in End Of Column

Chip must work with large pixels for outer layers

## ATLAS and CMS Phase 2 **Pixel Detector Requirements:**

- Small pixels: 50x50 µm² (or 25x100 µm²)

- Large chips: > 2cm x 2cm (~1 billion transistors) • Hit rates: ~3 GHz/cm<sup>2</sup>

- Radiation: 1 Grad, 10<sup>16</sup> n/cm<sup>2</sup> (unprecedented)

- Trigger: 1 MHz, 10 μs (~100x buffering and readout)

- Total power budget: ≤ 1 W/cm²

- Minimum threshold: 1000 electrons

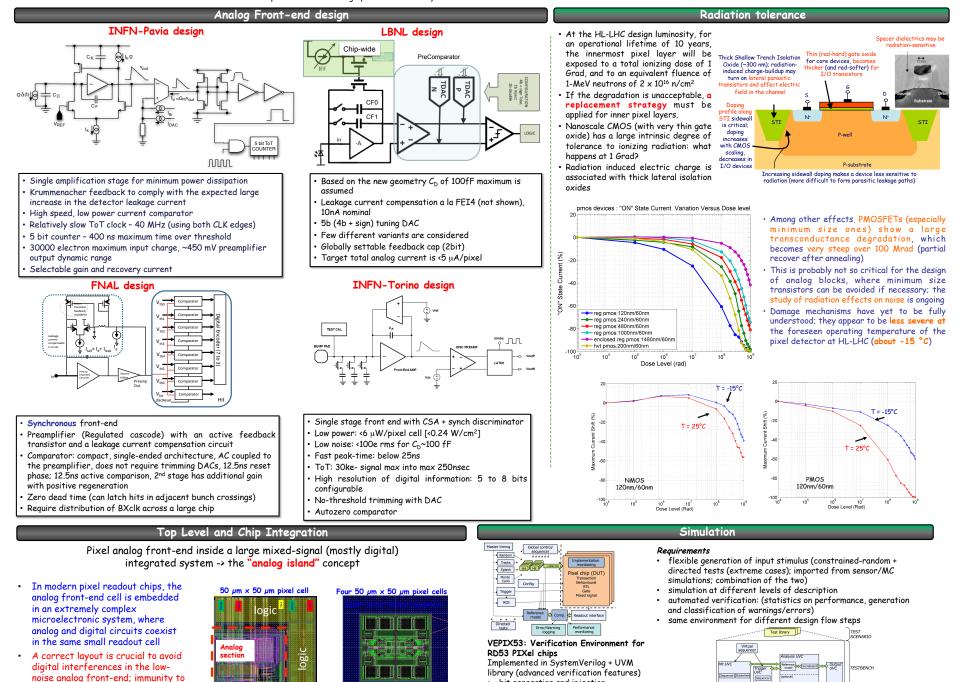

- Detailed understanding of radiation effects in 65nm

RD53 Goals

- Development of a simulation and verification framework with realistic hit generation

- Design and test of small-medium size pixel readout chips

- Design of a shared rad-hard IPs library

ver Monitor Driver

INFN Torino and University of Torino University of Sevilla and Instituto de Fisica de Cantabria

Monitor Subscribers

(if) output if

TOP MODULI

• Design, characterization and test beam of common engineering run with full sized pixel array chip > 1cm<sup>2</sup>

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | collection                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IP Blocks                                                                                                                                                                                                                                         | RD53 Institutes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Requirements         1. Single (differential) input line -> Encoding Clock and Data         2. Continuous triggering Capability         3. DC balancing (8b/10b encoding)         4. Run length less or equal to 6 (like in 8b/10b encoding)         5. Clock Phase alignment (needed because Clk frequency > 40MHz)         6. LPGBT compatibility         7. Low Trigger latency         8. Immunity to (at least) one bit flip on the line per data word         9. Full chip operation (during Run and Configuration phases) | <ul> <li>Band Gap</li> <li>Monitoring ADC</li> <li>Temperature Sensor</li> <li>Radiation Sensor</li> <li>Config. Memories</li> <li>DAC</li> <li>SRAM Pix/EOC</li> <li>SLVDS driver/receiver</li> <li>PLL</li> <li>SER/DES</li> <li>CDR</li> </ul> | <ul> <li>INFN Bari and Politecnico di Bari</li> <li>Bonn</li> <li>CERN</li> <li>CPPM</li> <li>Fermi National Accelerator Laboratory</li> <li>Laboratoire de Physique Nucléaire et de Hautes Energies, Paris</li> <li>Laboratoire de Physique Subatomique et de Cosmologie (LPSC)</li> <li>Laboratoire d'Annecy-le-Vieux de Physique des Particules (LAPP)</li> <li>NIKHEF</li> <li>University of New Mexico</li> <li>INFN Milano and University of Milano</li> <li>INFN Pavia, University of Pavia and University of Bergamo</li> </ul> |

| <ul> <li>Two possible solutions</li> <li>Input speed baseline will be 160 Mbps</li> <li>DC balancing is achieved without using 8b/10b encoding</li> <li>Using 8 bit wide data symbols -&gt; 2 machine clock cycles per symbol</li> </ul>                                                                                                                                                                                                                                                                                         | <ul> <li>Shunt LDO</li> <li>Rail-to-Rail Analog Buff</li> <li>Power-ON Reset</li> <li>VCO</li> <li>EFUSE</li> </ul>                                                                                                                               | <ul> <li>INFN Taking, initial stry of Para</li> <li>INFN Perugia and University of Pisa</li> <li>INFN Perugia and University of Perugia</li> <li>Institute of Physics and Czech Technical University</li> <li>Paul Scherrer Institute</li> <li>Rutherford Appleton Laboratory</li> <li>University of California Santa Cruz</li> </ul>                                                                                                                                                                                                   |

Frontier Detector for Frontier Physics - 13th Pisa Meeting on Advanced Detectors, May 24 - 30, 2015, La Biodola, Isola d'Elba (Italy)

Provide DC balancing choosing data symbols only amongst the 70 available ones

disturbances on analog supply lines

("PSRR") is also essential

hit generation and injection

conformity checks and statistics

monitoring of pixel chip input and output