# BPIX Integration: Lessons learned 2013 Pixel Replacement/Upgrade Discussion Meeting

Stefan Koenig, PSI

stefan.koenig@psi.ch

### The Task

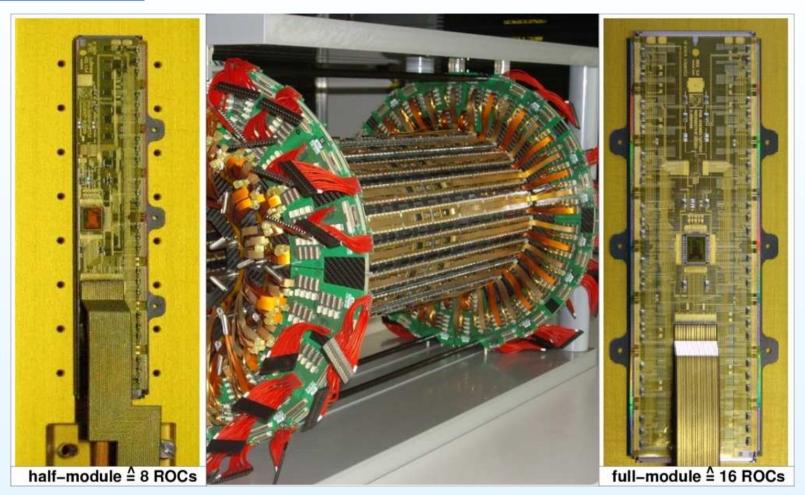

- integrate 700/100 full/half modules on 2x3 barrel shells

- verify function & connectivity through endring prints

- test HV connections

PAUL SCHERRER INSTITUT

### The Tools

- module mounting tools

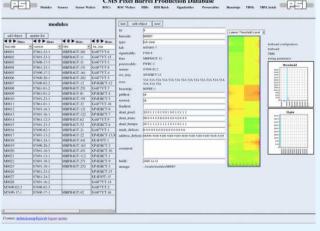

- integration DB + web-interface:

- draw the right module

- cut/set right properties

- record keeping

- testboard + Laptop for testing

- HV-connection test:

- multimeter, torchlamp + HV-supply

# Integration of a Module

- draw one mounting group (4 modules) from storage \*

- verify module usability (Hub id's possible & cables long enough) \*

- set Hub-ID \*

- put module in protective cover

- cut cables \*

- prepare powercable & solder & pott new power plug

- bend & scotch cables \*

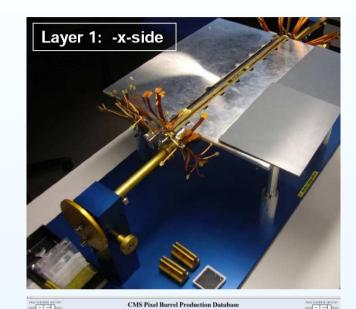

- mount modules on strukture \*

- connect cables to endprint

- \* with help of DB webinterface

# ...testing

- layer 1+2:

- 1. test modules after mounting

- 2. test through endprint after shells are combined

- layer 3:

- test modules as group through endprint

- final testing done with supply tubes attached

# ...Problems???

found in first test stage(s):

- wrong Hub-ID  $\Rightarrow$  easy replacement/repair

- cables to short  $\Rightarrow$  replacement/reusing on other position possible

- (unstable) connection ⇒ replugging/resoldering power plug

found in system test mostly/only:

- bad HV connection undetected before/ created during final handling

- strange/no readout in test with final configuration

each of the latter caused disassembly of whole 3 layer system:

• MUCH WORK - repair not 100% efficient!

after 3 iterations decided to stay with given result

PAUL SCHERRER INSTITUT

#### lessons learned

- try to avoid human factor in cable cutting/resoldering next time

- reduce need/number of un/plugging modules next time individually handle-& testable layers!

- testprocedures during/before integration and in final system should exactly match to avoid system effects (1% of modules!)

- manual mounting of modules worked like a charm! KEEP THIS!!!

- only ONE type of modules next time!

- record keeping work intensive & only possible with local production DB - KEEP!

- at least TWO integration tools/stations next time ! (reduced working peoples 'deadtime' esp. @ the end)

# next talk...

2013 Pixel Replacement/Upgrade Discussion Meeting – p.8

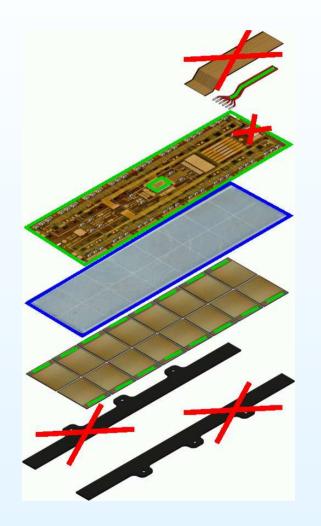

### trimm fat @ modules for 'Phase-1':

- fewer/thinner but longer cables

→less connectors

→move connectors/portcards out of active

→compatible with fast digital transmission

- no/smaller HV-capacitor

- thinner ROCS ( $175\mu m \Rightarrow 75\mu m$ )

- no basestrips (modules glued on structure)

module production almost 'as is' - verify/develop:

- bumpbonding of thinner chips

- connection of long cables to HDI

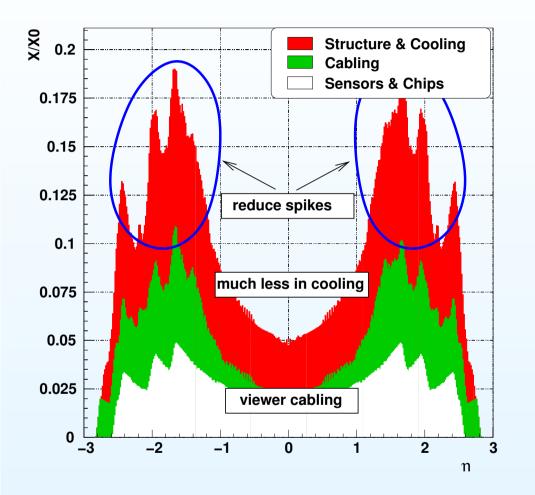

#### trimm fat @ modules for 'Phase-1'- Outcome

reduction potential (incl. CO2):

- structure, cooling & cabling ~ 50%

- module: ~30%

- extra reduction in spikes:

- connectors/portcards moved out of active

- no cooling manyfolds

- overall ~33%

phase I SCMS pixel tracker could have three layers for the material of two...