### Progress on the CMS Pixel front-end system

ACES Workshop CERN

4. March 2009

R. Horisberger Paul Scherrer Institut

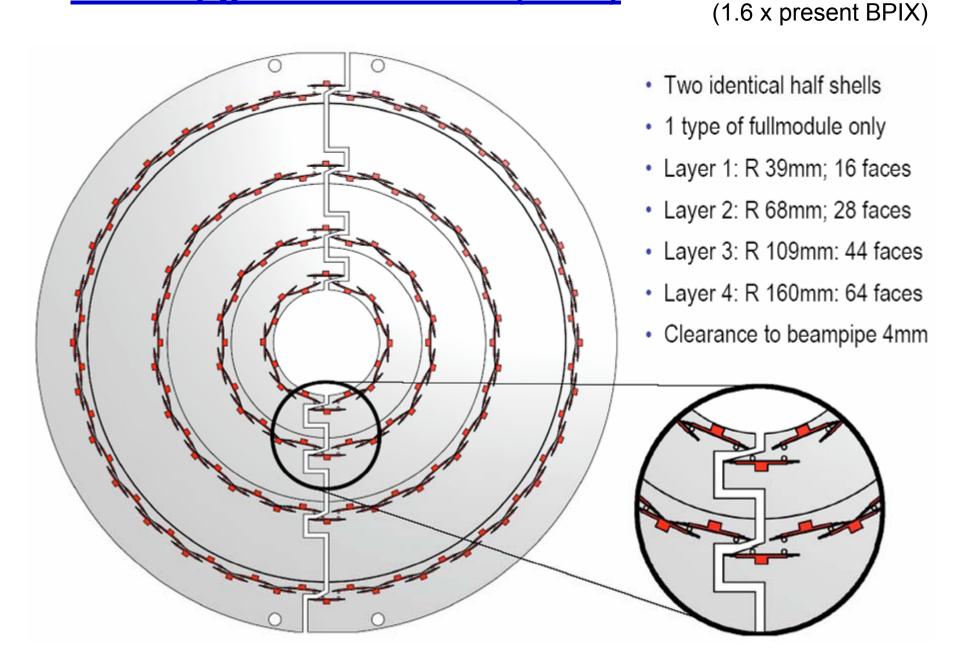

### BPIX Upgrade Phase 1 (2013)

- 4 layer pixel system 4, 7, 11, 16 cm  $\rightarrow$  1216 full modules

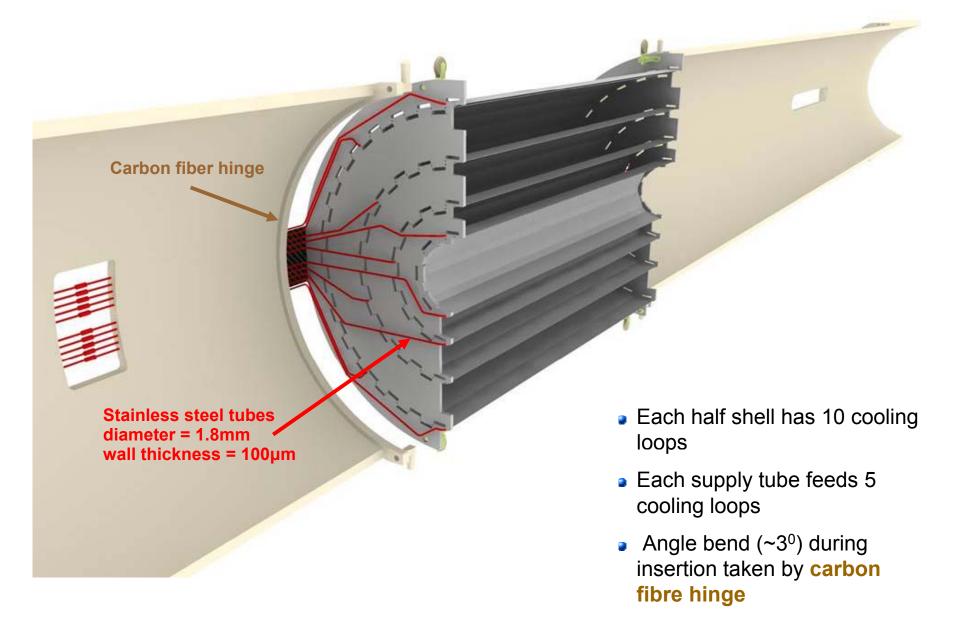

- CO2 cooling based

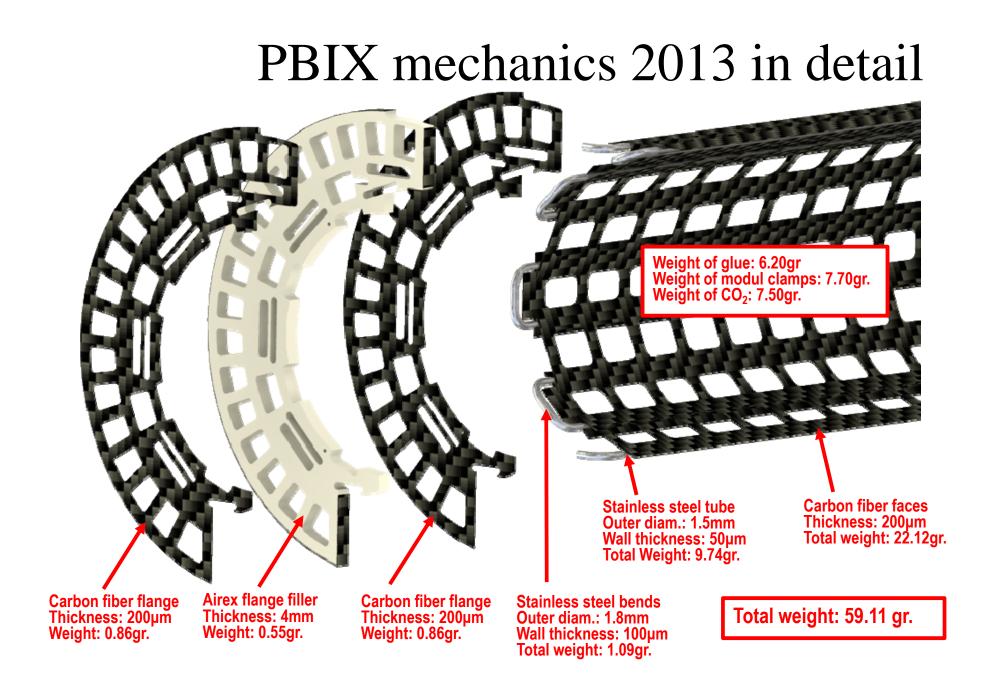

- Ultra Light Mechanics

- BPIX modules with long 1.2m long microtwisted pair cables

- Shift material budget from PCB & plugs out of tracking eta region

- Modify PSI46 ROC for 160MHz digital readout & Increase depth of ROC buffers

- Serialized binary optical readout at 320 MHz to old, modified px-FED

- Recycle & use current AOH lasers  $\rightarrow$  320MHz binary transmission

- Same FEC's , identical TTC & ROC programming

- Keep LV-power supply & push more current through cables

### BPIX Upgrade Phase 1 (2013)

$\rightarrow$  1216 modules

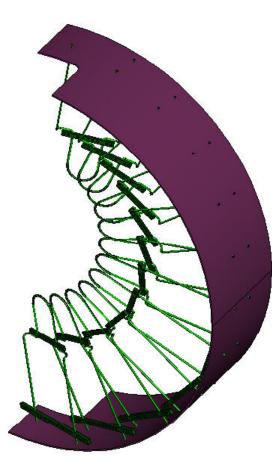

#### **CO2 Cooling Loops and Connection to Supplytubes**

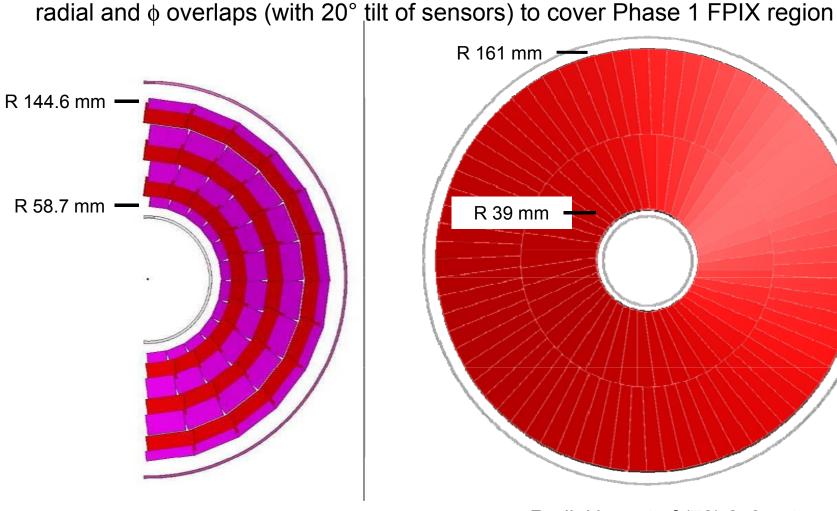

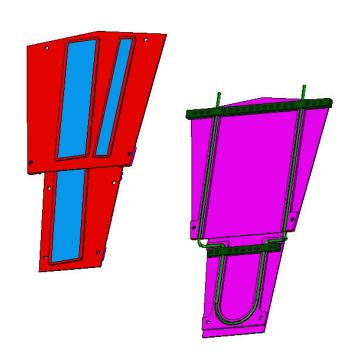

#### **Conceptual Disk Module Layout**

- Current Fpix module layout

- 7 module geometries

- 168 modules per disk  $\rightarrow$  1080 ROCs

- Radial layout of (72) 2x8 outer and (44) 2x8 inner radius modules

- 1 module geometry

- 116 modules per disk  $\rightarrow$  1856 ROCs

### **The Complete FPIX Assembly**

CO<sub>2</sub> cooling structure

Conceptual design of new blade with TPG substrate and cooling pipe

Total Quantity per half disk: Outer: 2X8 : 24 modules, 384 ROCs 1X8 : 24 modules, 192 ROCs Inner: 2X8: 24 modules, 384 ROCs

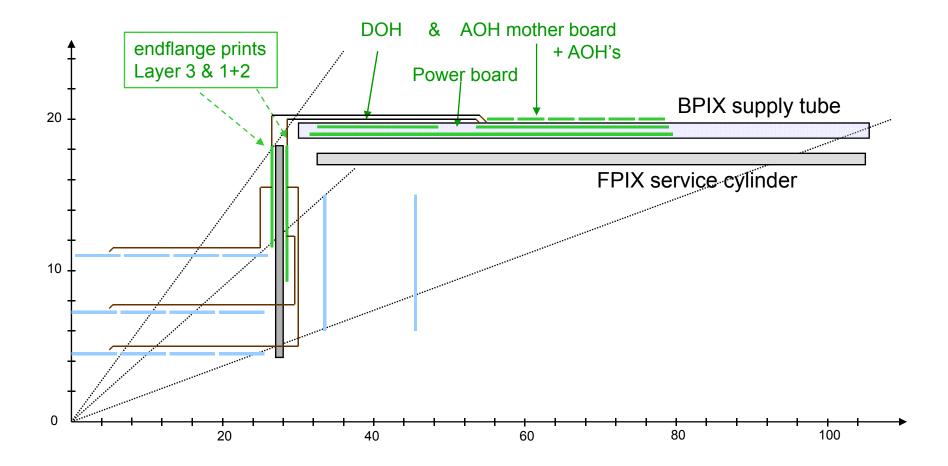

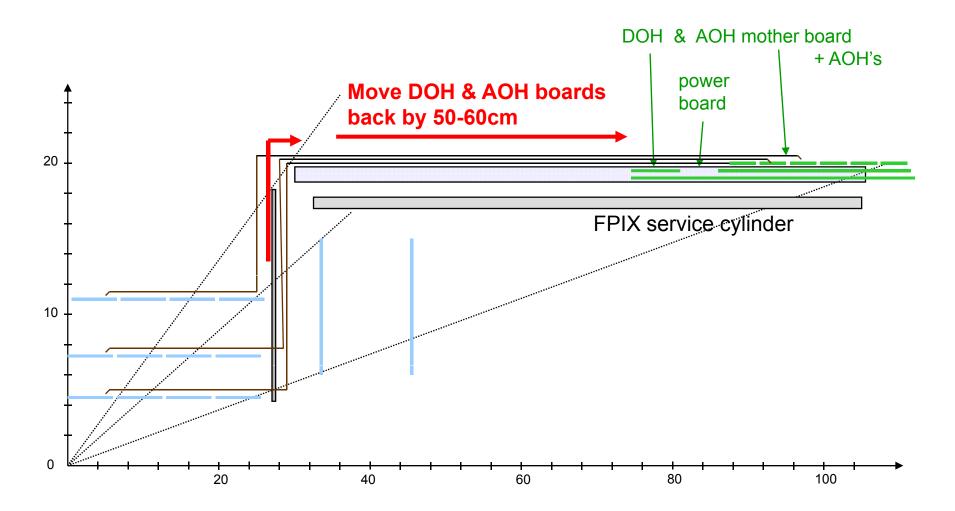

#### **Current Pixel System with Supply Tubes / Cylinders**

#### BPIX Cabling & flexible cooling pipes

#### **Shift PCB/Plug Material out of tracking Volume**

• Modules with long pigtails (1.2m) CCA wires  $16x(2x125\mu)$

#### **BPIX module**

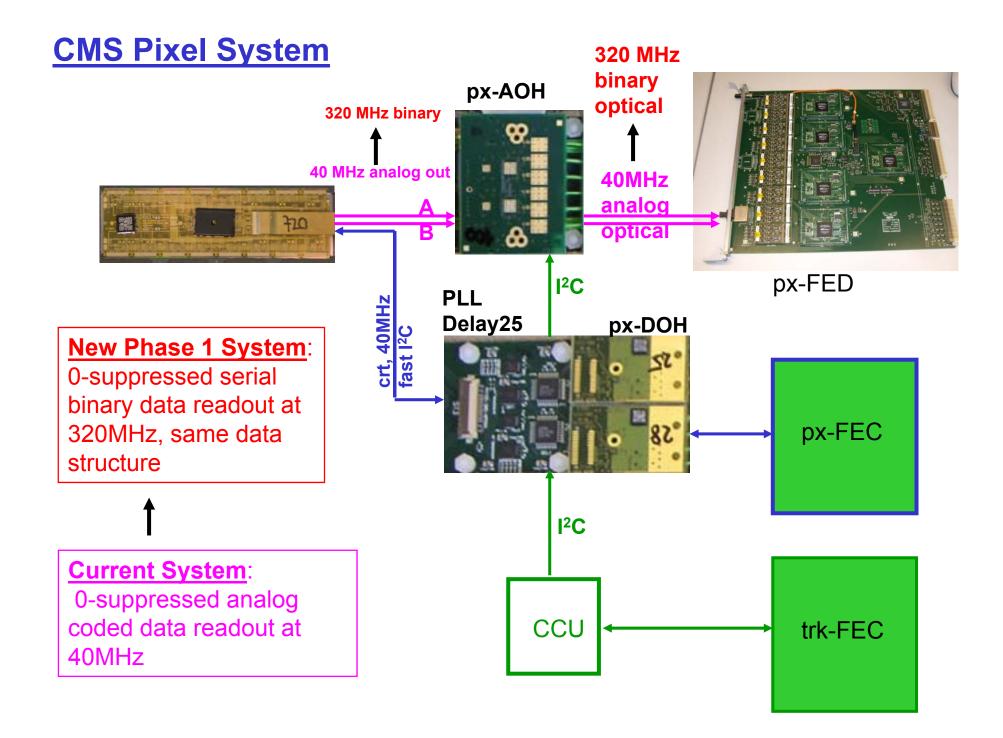

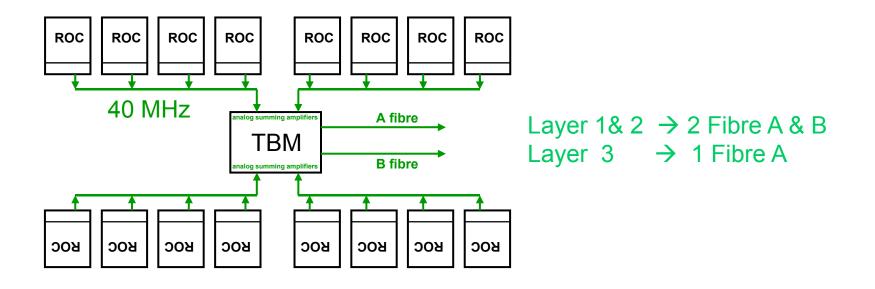

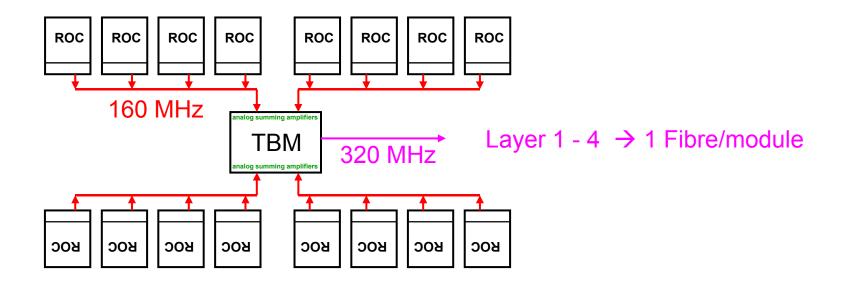

#### $4 \times 4 \text{ ROC} \rightarrow \text{TBM} \rightarrow \text{AOH} \rightarrow \text{pxFED}$

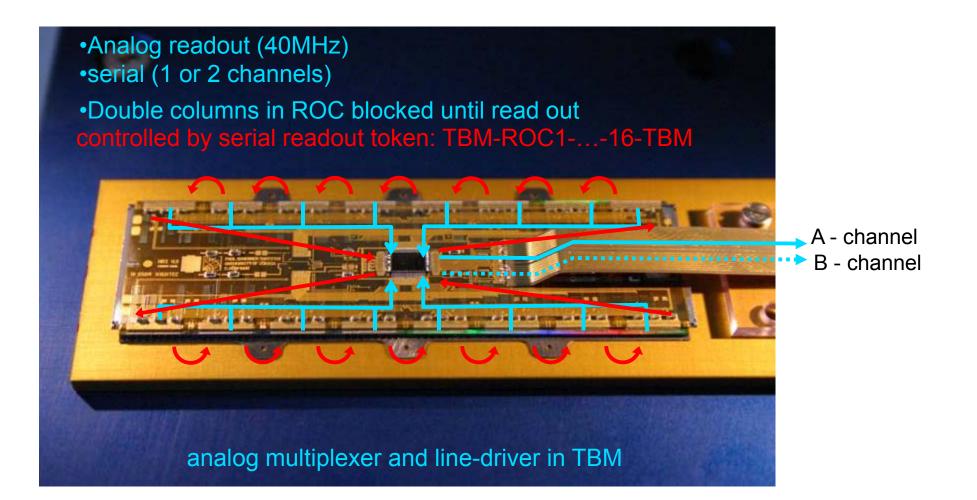

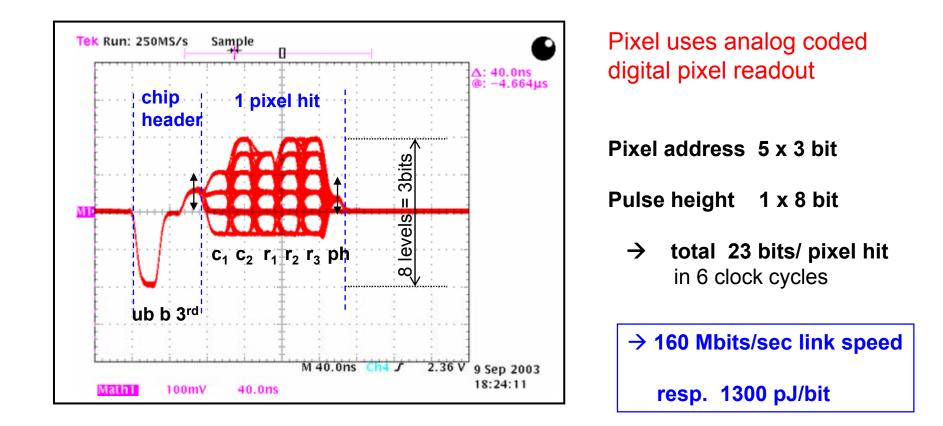

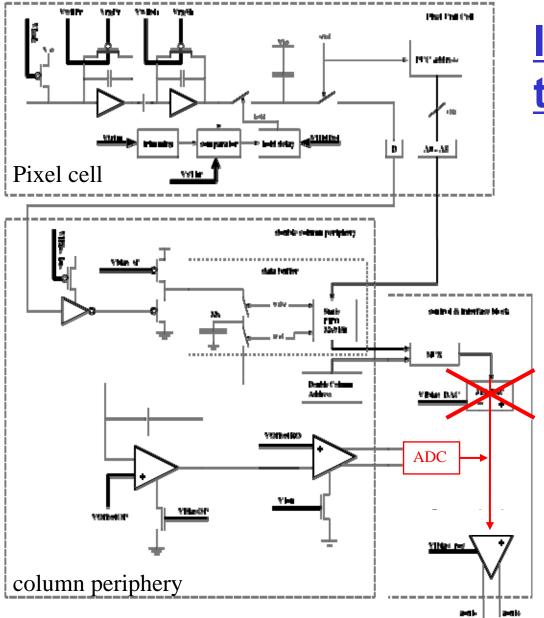

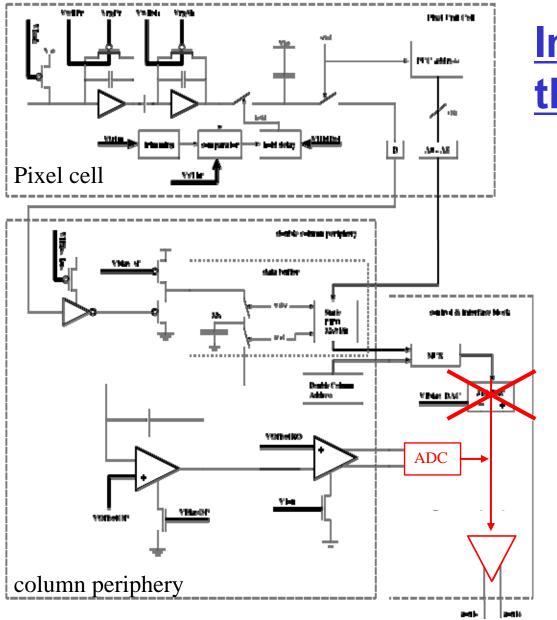

**Current Pixel Module Readout**

$ROC \rightarrow TBM$  : 40 MHz analog readout

TBM  $\rightarrow$  pxFED : 40 MHz analog readout

#### Present analog coded data transfer of pixel system

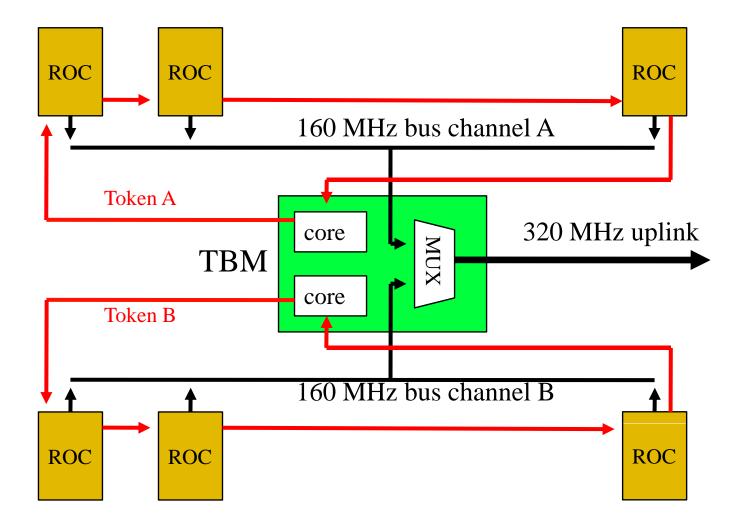

**New Serialized Binary Pixel Module Readout**

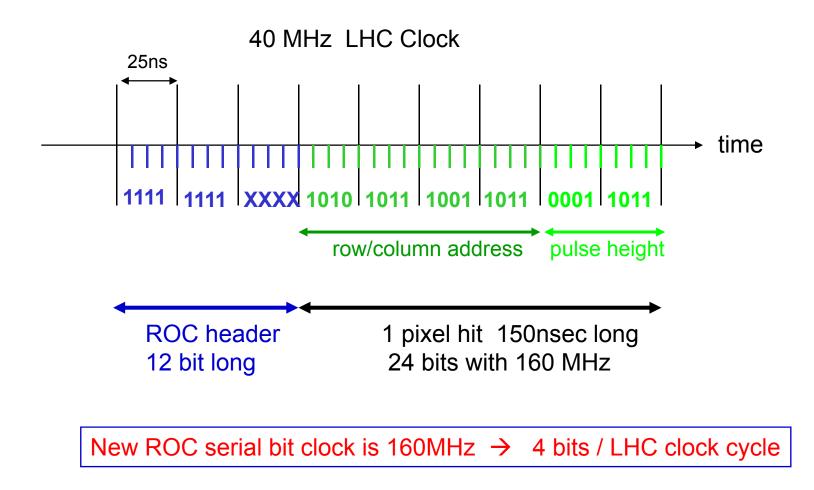

$ROC \rightarrow TBM$  : 160 MHz digital readout

TBM → pxFED : 320 MHz digital readout

#### New serial binary data transfer of pixel system

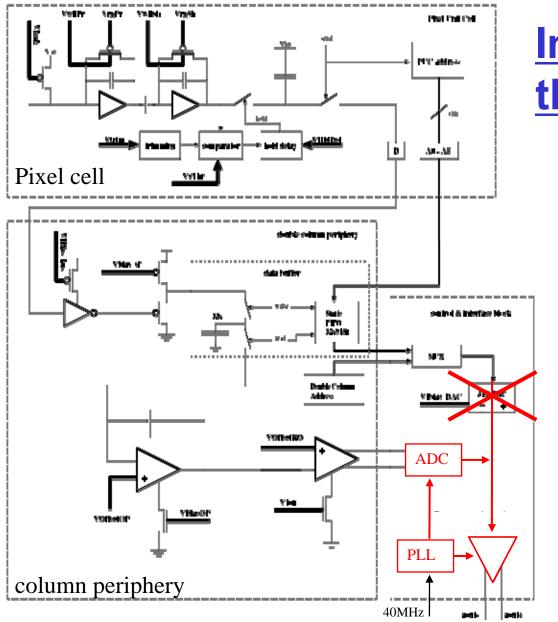

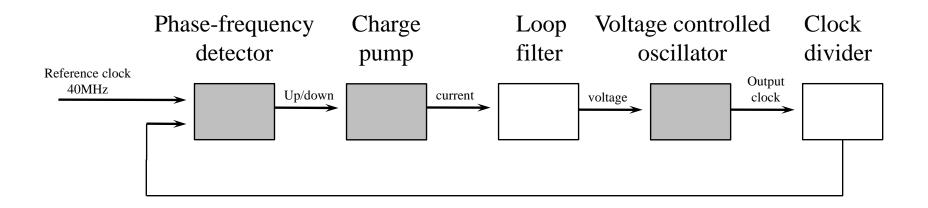

160 MHz clock to be generated in each ROC by 40 MHz  $\rightarrow$  160 MHz PLL circuit

→ See talk H-C. Kästli

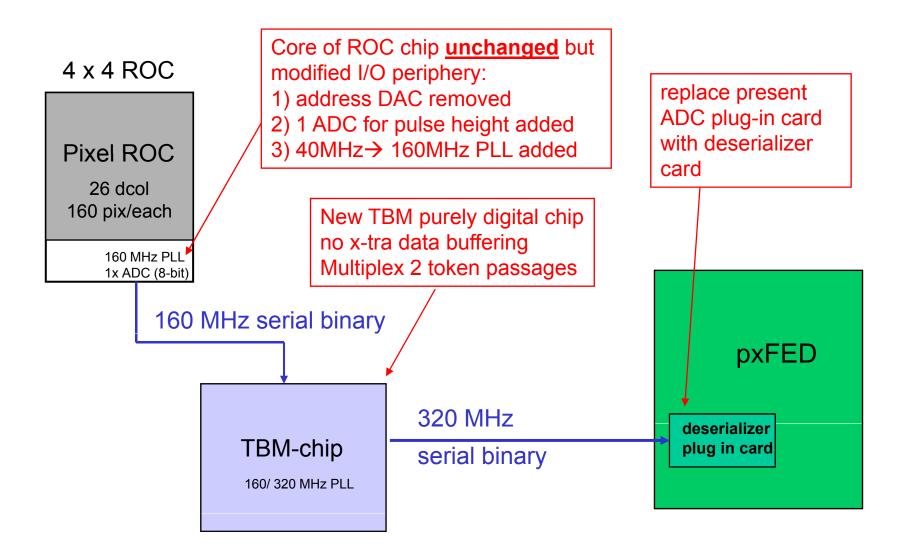

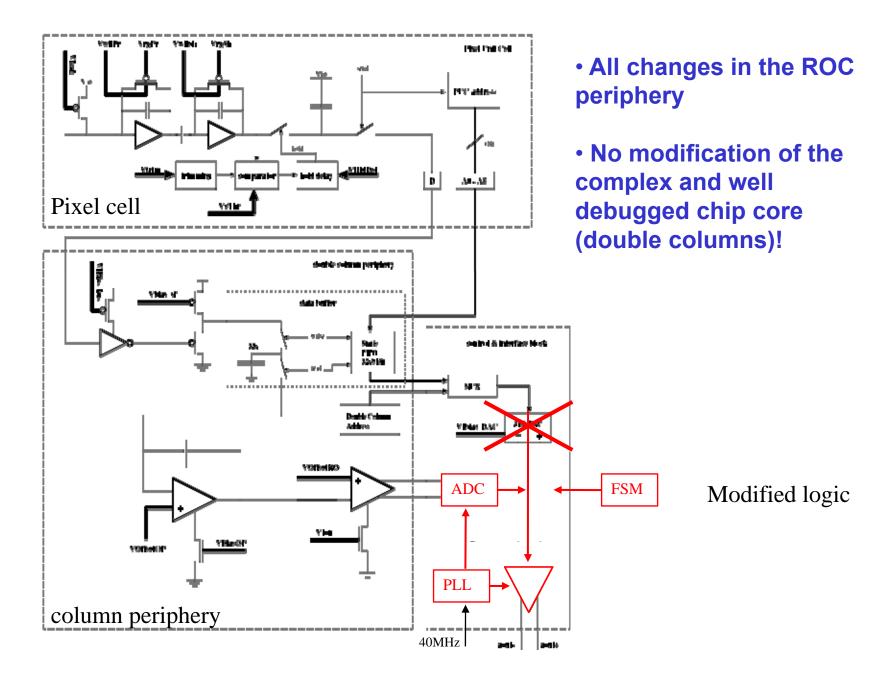

### **Basic Idea of digital module**

#### Changes for 160/320 MHz serial binary readout

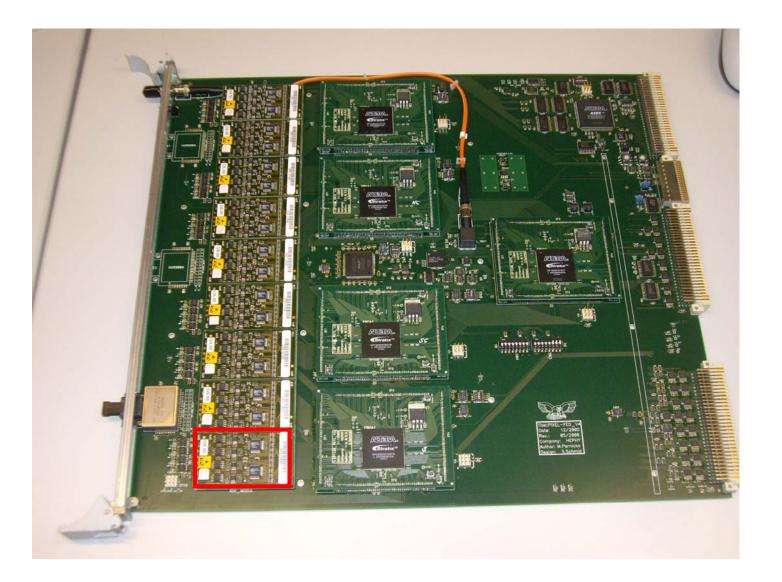

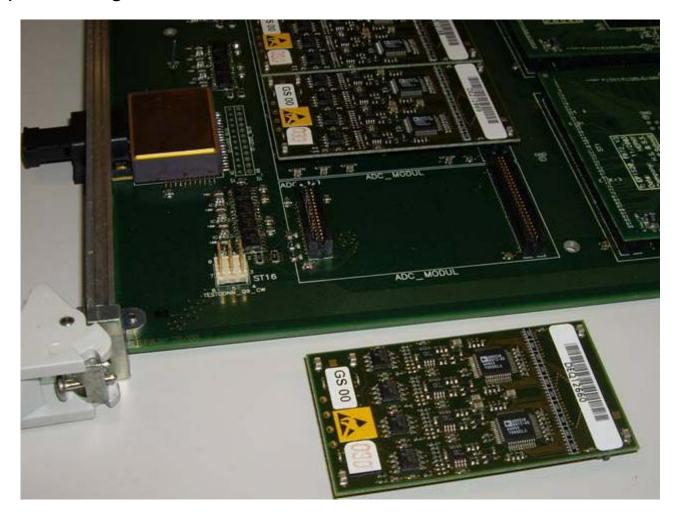

#### 3x 12 channels with 9 piggy-back ADC cards

HEPHY, Vienna M.Pernicka H. Steininger

Discussions with M. Pernika, M. Friedl, H. Steininger from HEPHY about replacement of ADC card with deserializer card look technically promissing.

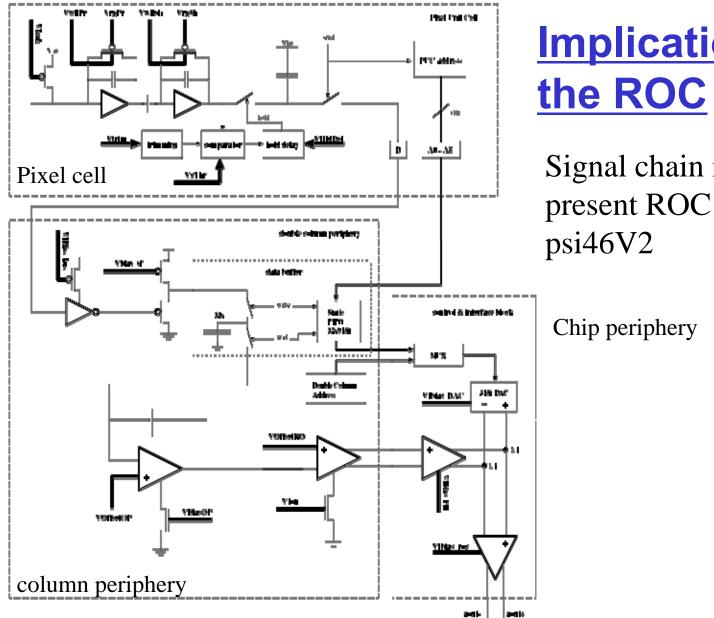

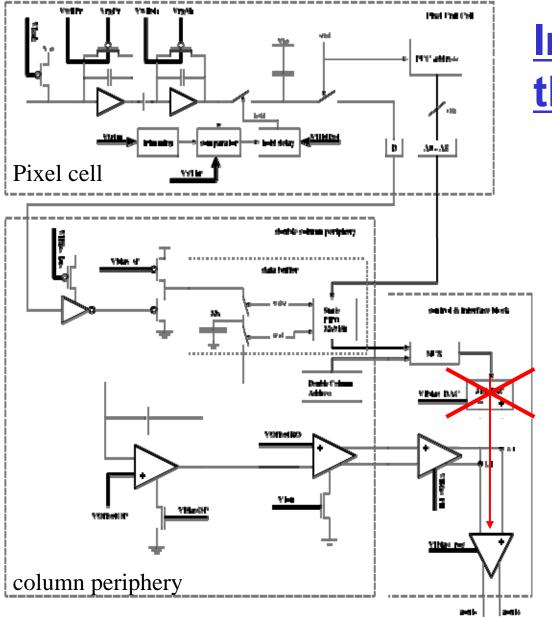

**Implications for**

Signal chain in

Implications for the ROC

Address internally already digital →Remove DAC →trivial

# Implications for the ROC

Need to digitize pulse height information →Need fast 8 bit ADC

### Implications for the ROC

New fast and low power output driver

### Implications for the ROC

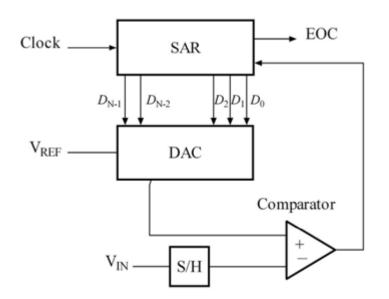

# **Pulse Height ADC**

- 8 Bit successive approximation current ADC

- Not pipelined → need 8 clock cycles conversion time

- Last year first 4 Bit prototype in 0.25µm produced and tested @ PSI

- Works well up to 80MHz

- Noise problems and non-linearity discovered

- Improved version resubmitted (B. Meier)

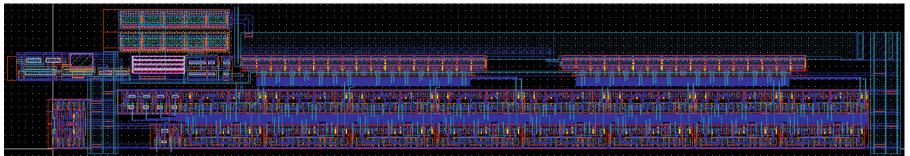

## **Pulse Height ADC**

$\rightarrow$  one per ROC

B. Meier PSI

- Improved 8 Bit version submitted in February 09

- Added sample/hold circuit at input

- 8 bit DAC

- Added capacitance to power rails

- Size: 640µ x 90µ

- 80 MHz conversion clock  $\rightarrow$  100nsec/conversion

# **Clock multiplier / PLL**

- Some building blocks (grey) submitted in IBM 0.25µm in 4/08

- Tested individual components and complete PLL with external filter / divider

- Works as expected from simulation, appeared very robust

- Locks immediately for 80/160/320 MHz output

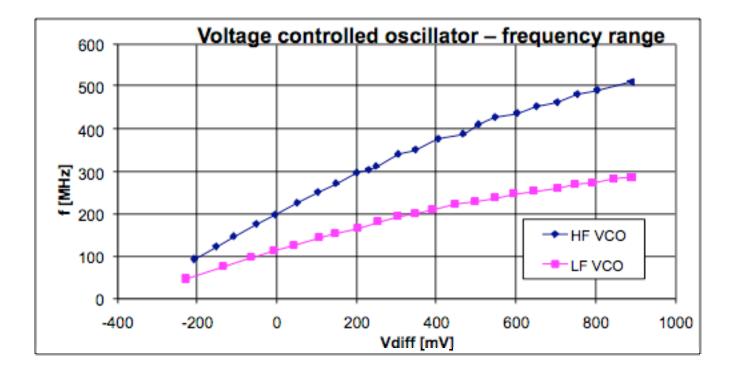

### PLL – Voltage Controlled Oscillator

- Measured frequency range of 2 VCOs in 0.25µm

≈ possible target output frequencies

- Doesn't fit well with simulations (not a surprise)

→ large margin

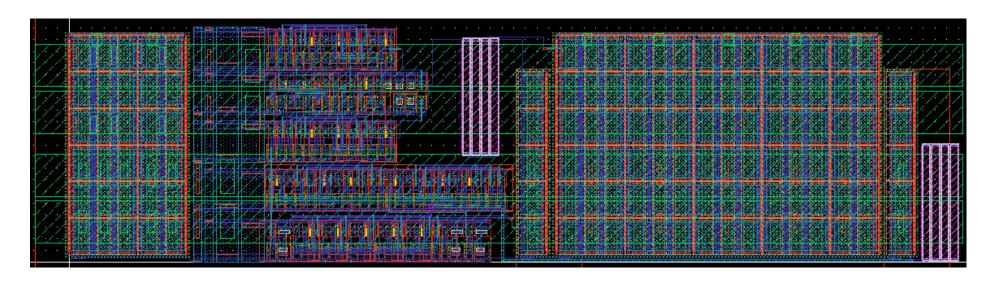

# **Clock multiplier / PLL**

- Complete clock multiplier cell Size:  $380\mu m \times 100\mu m$

- No external components, but added pads to change filter characteristics with external R/C (diagnostics)

- Improved design ready (Beat Meier)

- To be submitted in February 09

# **Conclusion & Outlook**

- 4 layer system needs higher uplink bandwidth

- Only feasible with digital links

- Implementation with minimal impact on overall system

- Changes in present 0.25mm ROC limited to small regions in interface block

- No change in down link chain

- All new functional blocks were submitted mid February on MPW.

- ROC modifications planned until November 09

- Changes in TBM restricted to uplink signal path. Target speed:

320 MHz

#### **Schedule & Crucial Dates**

1<sup>st</sup> R&D Sumission of PLL, ADC & LCDS blocks on 0.25um March 2008 done Fall 2008 done Design of UL Barrel Mechanics 2<sup>nd</sup> Submission of final 160 MHz PLL & 8bit ADC Feb. 2009 done Fabrication of 1 Layer prototype barrel mechanics March 2009 now Phase 1 TDR Summer 2009 Submission of digital pixel ROC (PSI46dig) Nov. 2009 Submission of new digital TBM Nov. 2010 Start of module production (18 month) Spring 2011 Start of module integration onto mechanics Summer 2012 Feb. 2013 Install new 4 layer pixel detector