# Phase 2 ATLAS pixel system architecture and requirements

### Work in progress

- Pixel upgrade system task force started in 2008 to draft specifications and system architecture recommendations (chair A. Grillo)

- Work still in progress

- Will show selected tables from working draft

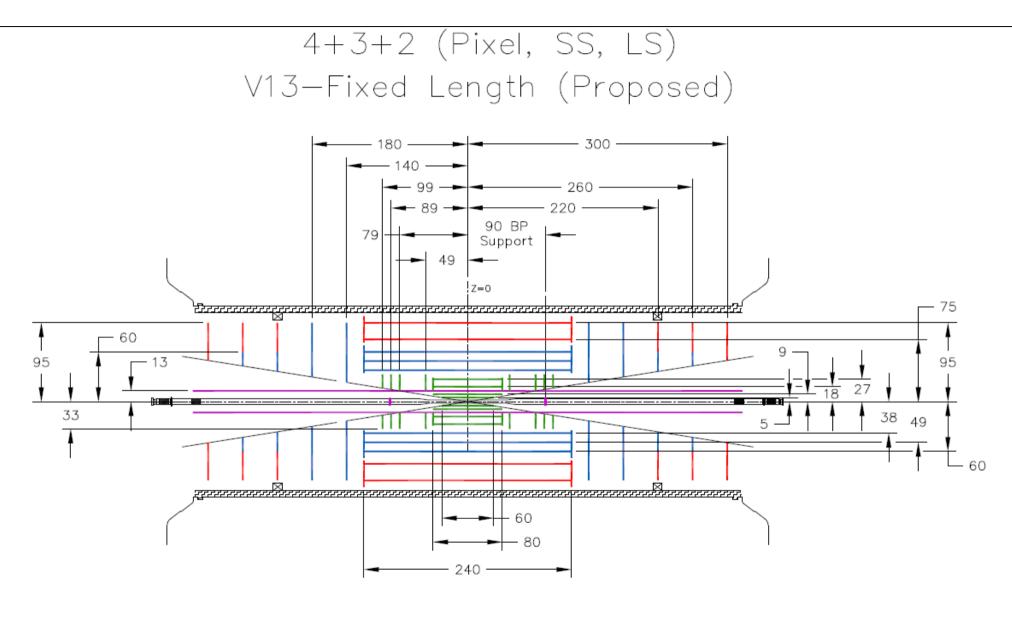

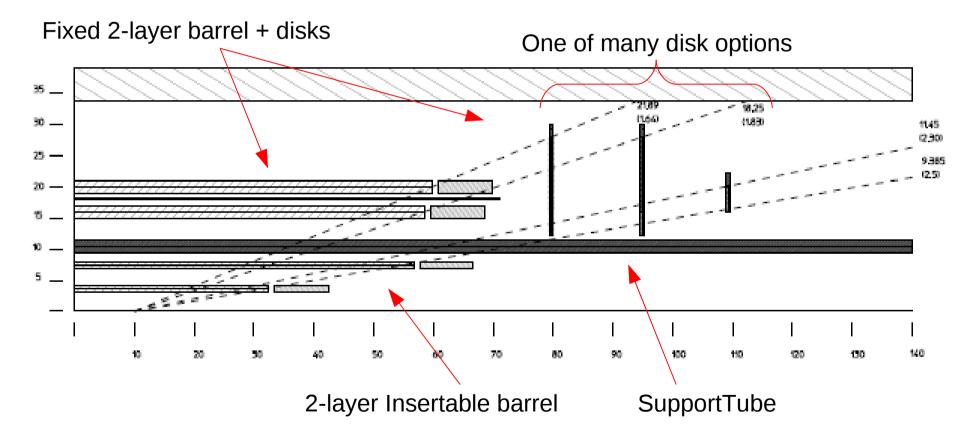

#### **Detector layout**

- System requirements are based on this basic working layout

- The final layout will surely be different

M. Garcia-Sciveres -- Phase 2 pixel system

## Radiation dose in pixel region

- Done with PHOJET pp event generator and FLUKA particle transport code.

- In pixel region, 3000fb<sup>-1</sup> prediction fit well by  $\left(\frac{270}{r^2} + \frac{14}{r}\right) x 10^{15}$

- Negligible z-dependence.

- Use smaller safety factor for insertable layers

| Layer | Ionizing dose in MRad<br>(included safety factor) | NIEL dose x10 <sup>15</sup> (included safety factor) | SEE Flux (for SEU)<br>particles / cm <sup>2</sup> /s |

|-------|---------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| 0     | 750 (1.5)*                                        | 13.4 (1.0)                                           | 1.2 x 10 <sup>9</sup> (1.15)                         |

| 1     | 275 (1.5)*                                        | 4.5 (1.0)                                            | 0.5 x 10 <sup>9</sup> (1.15)                         |

| 2     | 150 (2.5)*                                        | 2.5 (2.0)                                            | 0.2 x 10 <sup>9</sup> (1.15)                         |

| 3     | 105 (2.5)*                                        | 1.8 (2.0)                                            | 0.1 x 10 <sup>9</sup> (1.15)                         |

| disks | 150 (2.5)*                                        | 2.5 (2.0)                                            | 0.2 x 10 <sup>9</sup> (1.15)                         |

(\*) ionizing dose based on older estimates => bigger safety factor

## Readout chip and pixel size

- In addition to layout, a readout chip format is assumed based on the FE-I4 now under design for Phase 1.

- FE-I4 active area =  $1.68 \times 2.0 \text{ cm}^2$

- Pixel surface area x recovery time must be compatible with hit rate for total dead time < 1%</li>

- Pixel aspect ratio is a matter of preference

- FE-I4 values are: 50um x 250um x 400ns

- Assume these values where occupancy allows

## Number of components

| Layer      | Radius or Z<br>(cm) | N. of staves<br>or wedges | Modules /<br>stave or<br>wedge | Chips /<br>module | End cards /<br>stave or<br>wedge |

|------------|---------------------|---------------------------|--------------------------------|-------------------|----------------------------------|

| 0          | 3.7                 | 16                        | 32                             | 1                 | 2                                |

| 1          | 7                   | 16                        | 24                             | 4                 | 4                                |

| 2          | 16                  | 36                        | 32                             | 4                 | 4                                |

| 3          | 21                  | 44                        | 32                             | 4                 | 2                                |

| <br>disk 1 | 140                 | 8?                        | 16?                            | 4                 | 2                                |

| disk 2     | 150                 | 8?                        | 16?                            | 4                 | 2                                |

| disk 3     | 160                 | 8?                        | 16?                            | 4                 | 2                                |

| disk 4     | 170                 | 8?                        | 16?                            | 4                 | 2                                |

| disk 5     | 180                 | 8?                        | 16?                            | 4                 | 2                                |

Maximal disk system

> Total number of FE chips = 15,000 . = Total active area Estimated chip power = (nominal for FE-I4)

5.0 m<sup>2</sup>

13 KW (~twice present detector)

## Power delivery

- A constraint for the new detector is that it must be able to use the cable plant of the present detector

- Can take this literally to mean re-use same cables where possible

- Or simply that it must fit into the same space and no more.

- But total power is X2

- And FE chip internal voltage is  $\sim /2$

- This means supply current is X4 at chip

- =>To keep the same power loss in the cables, need on-detector power conversion of at least factor of 4.

- Options under consideration are

- Serial power (8 modules in series, but could be 4)

- 2 stage DC-DC conversion, factor of 2 in chip x another 2 or 4 near detector

- Both options have ratio in the 4-8 range and can look remarkably similar to rest of system (cables only care about ratio, for example)

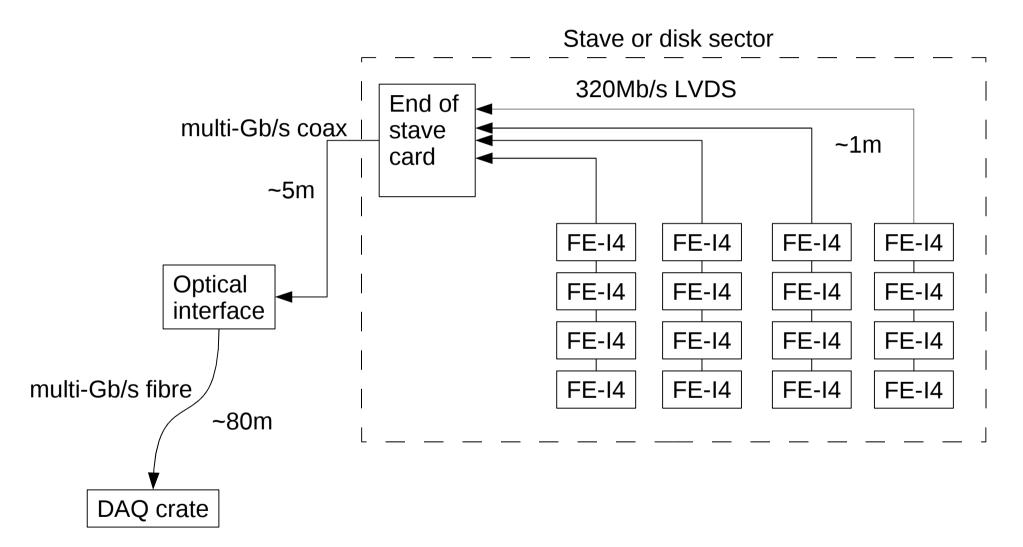

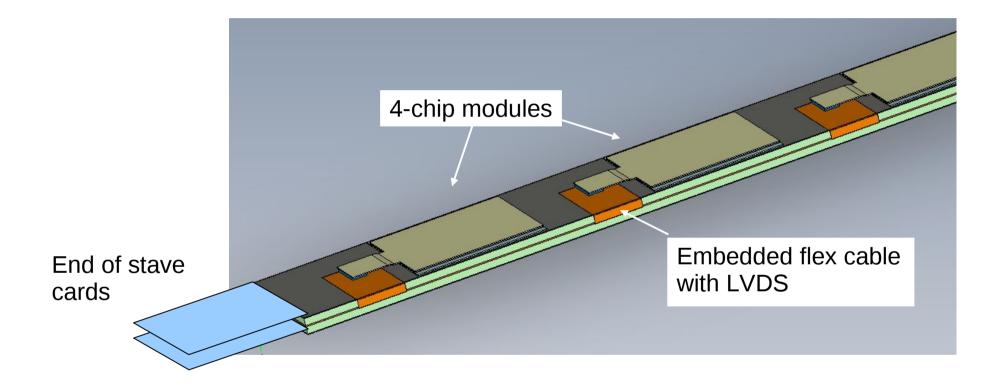

#### Readout system architecture

#### Example of stave concept

#### Data output parameters

| Trigger rate                            | 100 kHz                                                                                        | ]                              |

|-----------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------|

| Interactions per crossing               | 400                                                                                            |                                |

| Max. trigger latency                    | 256 x 25ns                                                                                     |                                |

| Sensor model used in simulation         | 260um planar, unirradiated                                                                     |                                |

| Comparator threshold                    | 4000e                                                                                          | to                             |

| Output format for analog data           | Fixed frame dynamic 2 pixel phi pairing                                                        | )<br>Dply<br>L1                |

| Bits / pixels per analog output frame   | 26 / 2                                                                                         | Can apply to<br>higher L1 rate |

| Output format for binary data           | Fixed frame dynamic 2 pixel phi pairing (L2, L3)<br>Fixed frame dynamic 4 pixel group (L0, L1) | Ca                             |

| Bits / pixels per binary output frame   | 24 / 4 (L2, L3) ; 20 / 2 (L0, L1)                                                              | ]                              |

| Encoding, parity, redundancy or headers | None                                                                                           |                                |

| Design margin                           | Factor of 2                                                                                    | ]/                             |

#### Data rate requirements

| Layei | comp. firing<br>per cm^2<br>per BX | Required bandwidth<br>per chip (Mb/s)<br>(analog / binary) | chips/<br>module | 320Mb/s LVDS<br>outputs / module<br>(analog / binary) | EOS card data<br>volume (Gb/s)<br>(analog / binary) | FE-I4 chip<br>data losses<br>(*) x 10 <sup>-4</sup> | 50x250u<br>x400ns<br>pixel<br>pileup |

|-------|------------------------------------|------------------------------------------------------------|------------------|-------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|--------------------------------------|

| 0     | 60.0                               | 749 / 454                                                  | 1                | 3 / 2                                                 | 12.0 / 7.3                                          | n/a + 3                                             | >1%                                  |

| 1     | 18.4                               | 230 / 140                                                  | 4                | 3/2                                                   | 5.5 / 3.4                                           | n/a + 1                                             | ~1%0                                 |

| 2     | 6.6                                | 75 / 58                                                    | 4                | 1/1                                                   | 2.4 / 1.8                                           | 18 + 0.5                                            |                                      |

| 3     | 3.9                                | 42 / 32                                                    | 4                | 1/1                                                   | 2.7 / 2.1                                           | 10 + 0                                              | <1%                                  |

| disks |                                    | 80 max?                                                    | 4                | 1                                                     | 2.9?                                                | 10 to 20?                                           |                                      |

- Outer is a good match to FE\_I4 chip under design and to data links like GBT

- Inner is not a "solved problem" yet. Plan a further IC design generation Pixels must be smaller, or faster, or both

•

## Token passing

• Recall this from a few slides ago:

- Concept is that 4 FE chips share one single LVDS output

- A read token passing scheme is necessary

- Various options under study for LVDS rate of 320Mb/s

- Could be shared bus (4 tri-state drivers), daisy chain (1 repeater per chip), or star (1 master and 3 slaves).

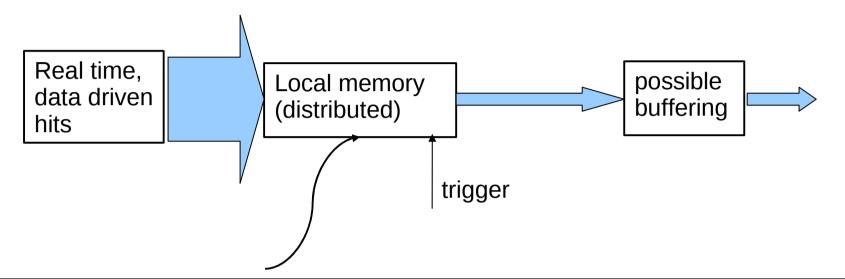

## **Trigger Latency**

- Local memory size ~ Latency \* hit\_rate

- Memory size limited by pixel size

- Will have as much as can fit, no more

- => Latency \* hit\_rate limit given by IC technology

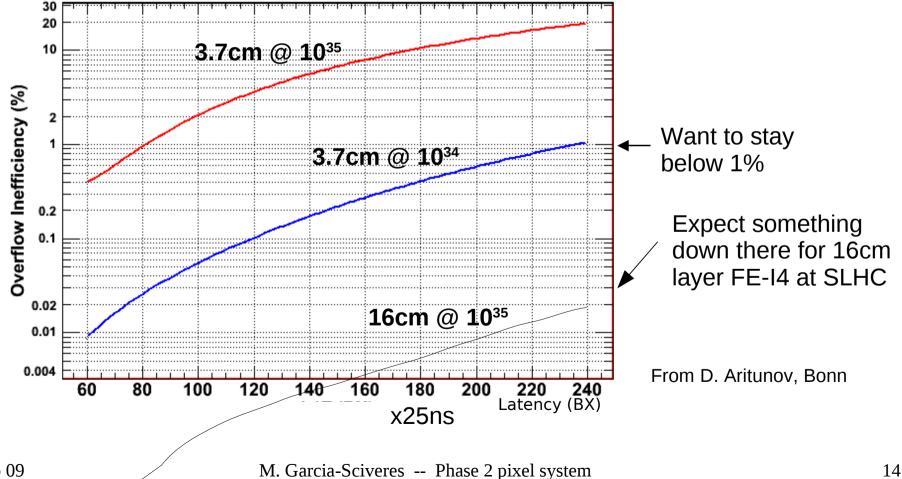

#### Memory overflow inside FE-I4 chip (see M. Barbero talk, Wednesday for more details)

>This is basically a source of dead time.

Increases ~1 order of magnitude with every latency doubling.

>This is a representative simulation, not the final FE-I4 architecture

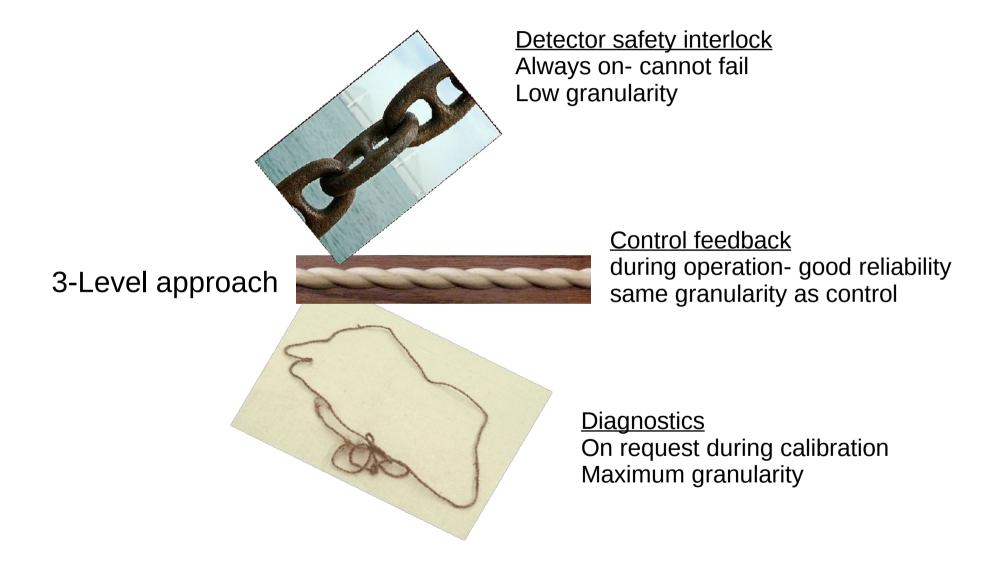

## Control and monitoring

## Control and monitoring specific cases

| Function                                   | Reliability | processed<br>where | smallest<br>group | largest<br>group | Live time     |

|--------------------------------------------|-------------|--------------------|-------------------|------------------|---------------|

| HV bias on/off,<br>set voltage             | very high   | @ power supply     | sensor tile       | SP stage         | All use cases |

| feedback HV voltage &<br>current readings  | high        | @ power supply     | sensor tile       | SP stage         | All use cases |

| switch LV current<br>on/off, set current   | very high   | @ power supply     | half-stave        | half-<br>stave   | All use cases |

| feedback LV<br>voltage reading             | high        | @EOS card          | 4-chips           | SP stage         | All use cases |

| SP stage<br>bypass switch on/off           | high        | @EOS card          | SP stage          | SP stage         | All use cases |

| monitor chip LV                            | low         | in FE chip         | 1 chip            | 1 chip           | upon request  |

| temperature interlock<br>on module NTC     | very high   | off-detector       | sensor tile       | half-<br>stave   | always        |

| feedback temperature reading of module NTC | high        | @EOS card          | sensor tile       | 1/4 stave        | All use cases |

| monitor chip<br>temperature                | low         | in FE chip         | 1 chip            | 1 chip           | upon request  |

## Summary

- ATLAS pixel system requirements taking shape for present upgrade concept

- Some options and details to be resolved

- But concept, physics needs, can still change

- Technology development for outer layers rapidly converging

- Inner layers need more R&D

- Did not cover trigger or details of power delivery whole sessions devoted to these

- Did not cover mechanical issues- mass, cooling.

## BACKUP

## ID layout