# **CMS Pixel Upgrade**

2<sup>nd</sup> ACES workshop, CERN

Hans-Christian Kästli, PSI 3.3.2009

# Scope

- Phase I (~2013):

- CMS pixel detector designed for fast insertion/removal

- Can replace system during normal shutdown

- Planned to insert new 4 layer system in 2013

- Phase II (>2017):

- For pixels, there is no proposal yet, nor a strawman design

- This talk gives general considerations and personal thoughts

- Assume that the same 4 layer/3disk mechanical

CMS Pixels Astructure as for Phase 120 Will be used

- Phase I:

- Layout of 4 layer / 3 disk system

- Electronics upgrade

- Phase II:

- Overview of present front end and ist limitation

- ROC considerations

- Hit / data rates

- Powering scheme

• Phase I:

#### - Layout of 4 layer / 3 disk system

- Electronics upgrade

- Phase II:

- Overview of present front end and ist limitation

- ROC considerations

- Hit / data rates

- Powering scheme

### Present barrel layout

- Two identical half shells

- 3 layers at R = 4.3, 7.2 and 11cm

- Empty volume

- Strip tracker starts at R = 20cm

- Track seeding in pixels. Have to extrapolate through ~9cm gap

- More difficult at higher track rates

- A = 0.75 m<sup>2</sup>, 784 modules

- 1 type of full module

- 2 types of half modules

- At least 100 different

cable lengths

5/33

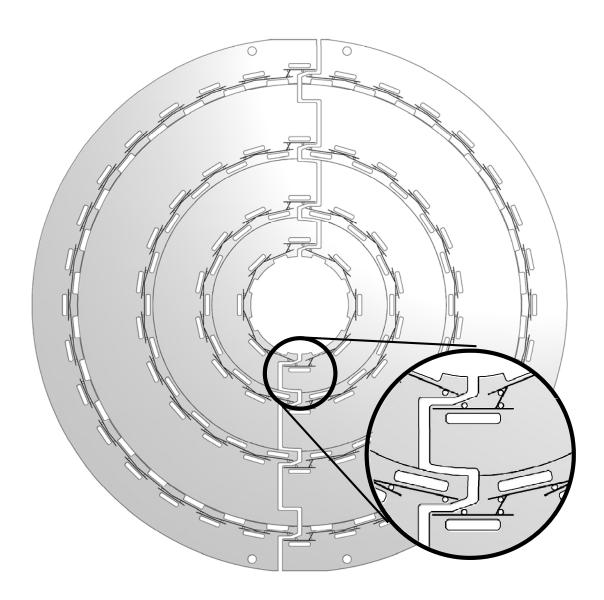

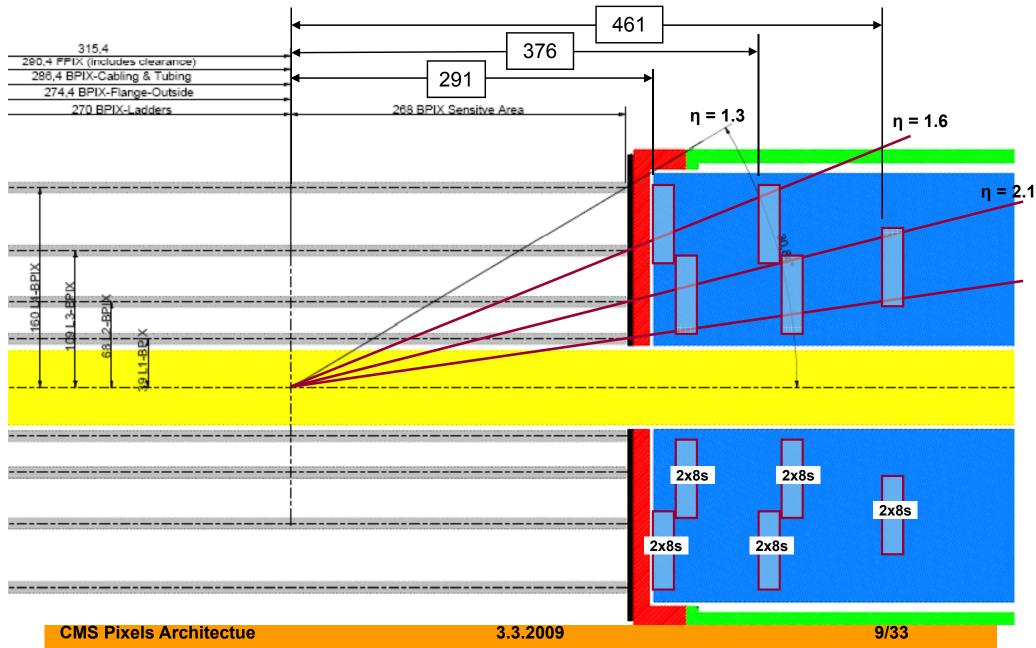

# New 4 layer layout

- Two identical half shells

- 4 layers at R = 3.9, 6.8, 10.9, 16.0 cm

- No large empty volume, excellent pointing precision of track seeds

- A ≈ 1.21 m<sup>2</sup>, 1216 modules

- Full-modules only

- Clearance to beam-pipe 4mm

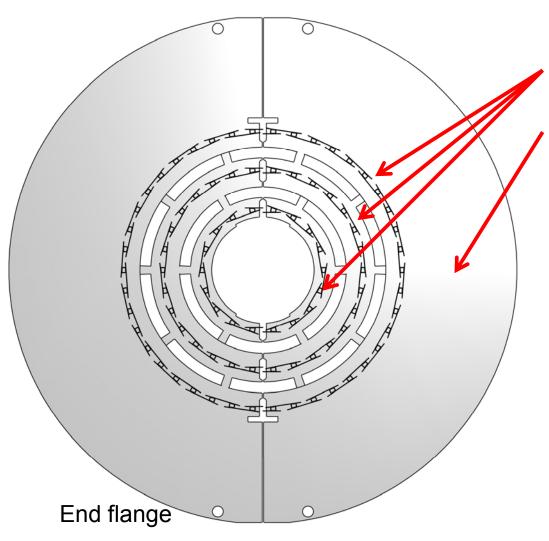

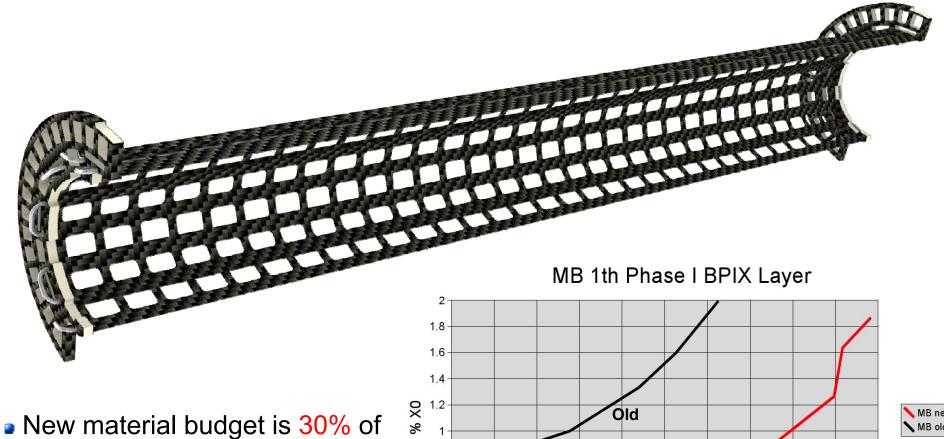

#### New layer 1 mechanics

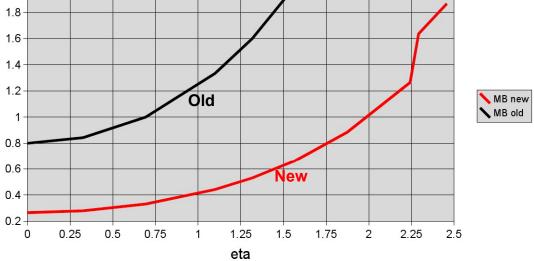

- New material budget is 30% of current barrel

- → new 4 layer system will have smaller MB than present 3 layer system

**CMS Pixels Architectue**

3.3.2009

7/33

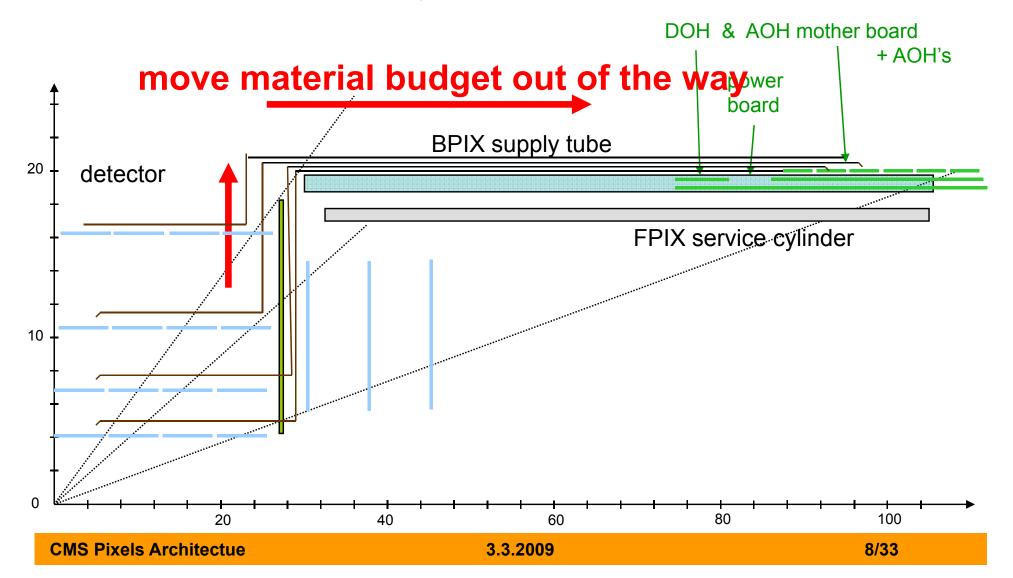

- Cooling  $C_6F_{14} \rightarrow CO_2$

- Modules with long pigtails (1.2m) CCA  $\mu$ -twisted pairs 16x(2x125 $\mu$ )

- Move DOH & AOH boards back by 50-60cm

#### Third disk

#### • Phase I:

– Layout of 4 layer / 3 disk system

#### - Electronics upgrade

- Phase II:

- Overview of present front end and ist limitation

- ROC considerations

- Hit / data rates

- Powering scheme

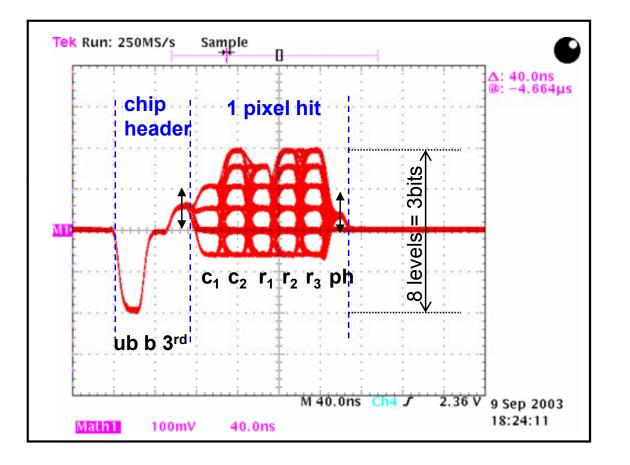

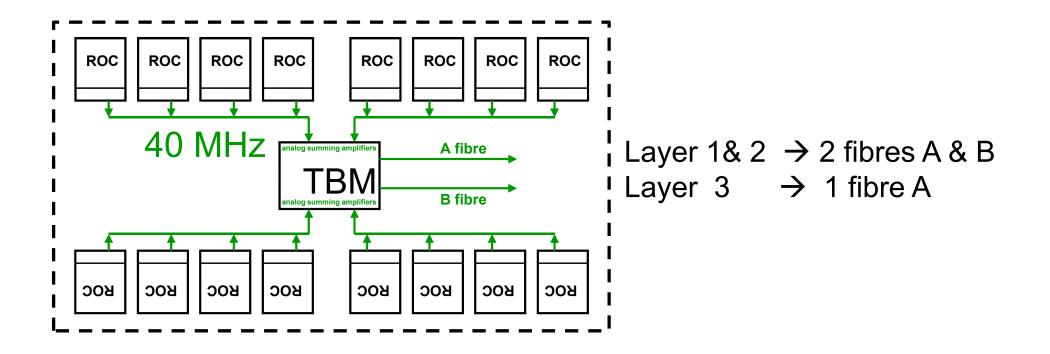

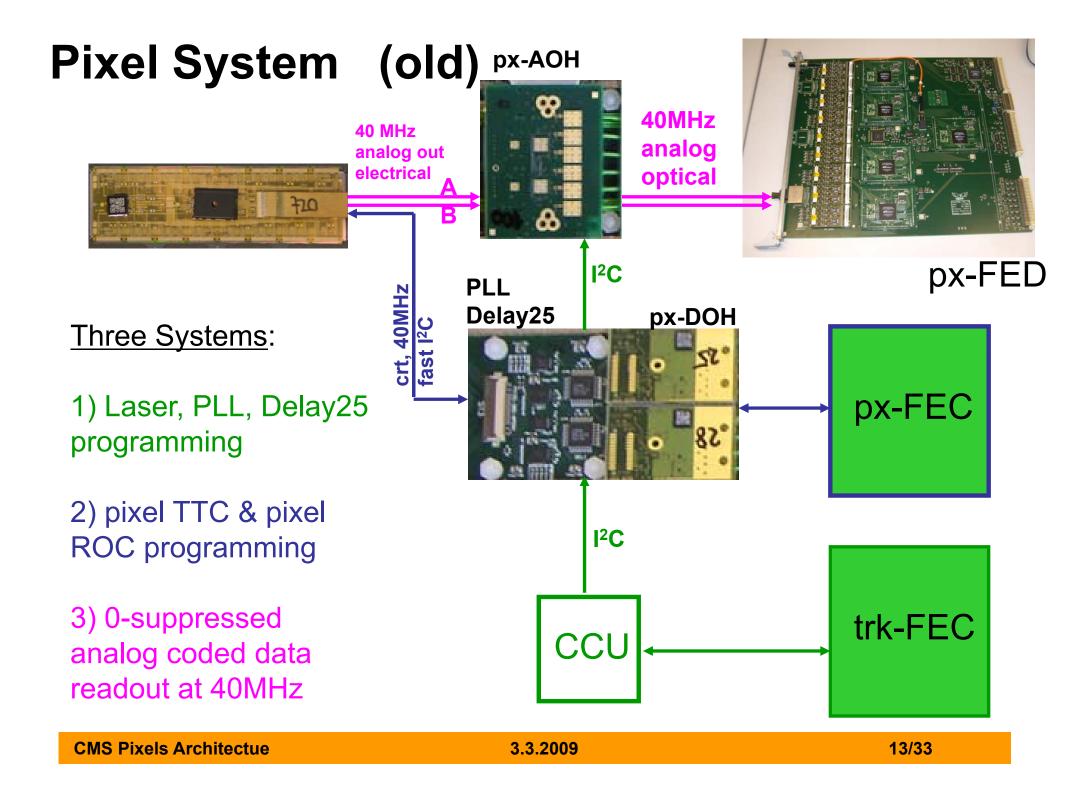

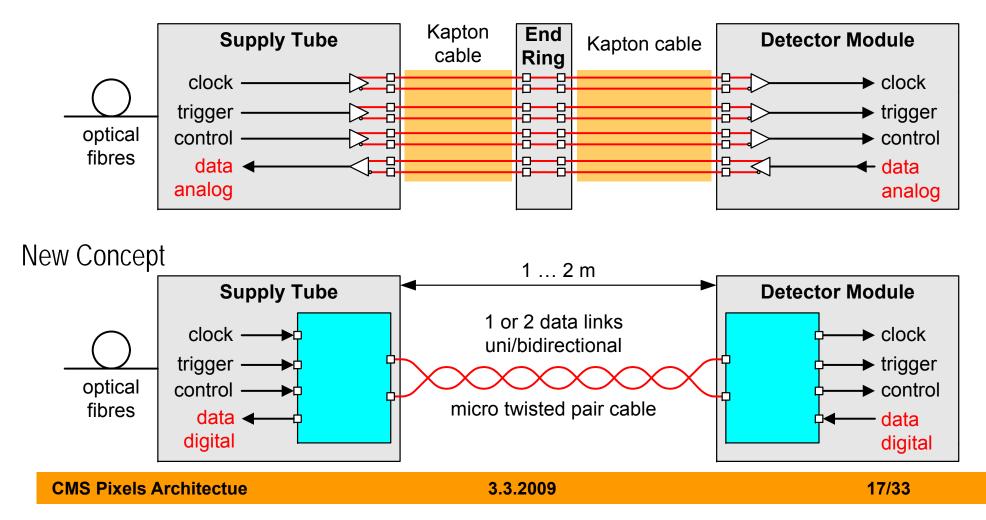

### Present analog link

Pixel uses analog coded digital pixel readout

Pixel address 5 x 3 bit

Pulse height 1 x 8 bit

→ total 23 bits/ pixel hit in 6 clock cycles

→ 160 Mbits/sec link speed

#### Present module readout

ROC  $\rightarrow$  TBM : 40 MHz analog readout TBM  $\rightarrow$  pxFED : 40 MHz analog readout

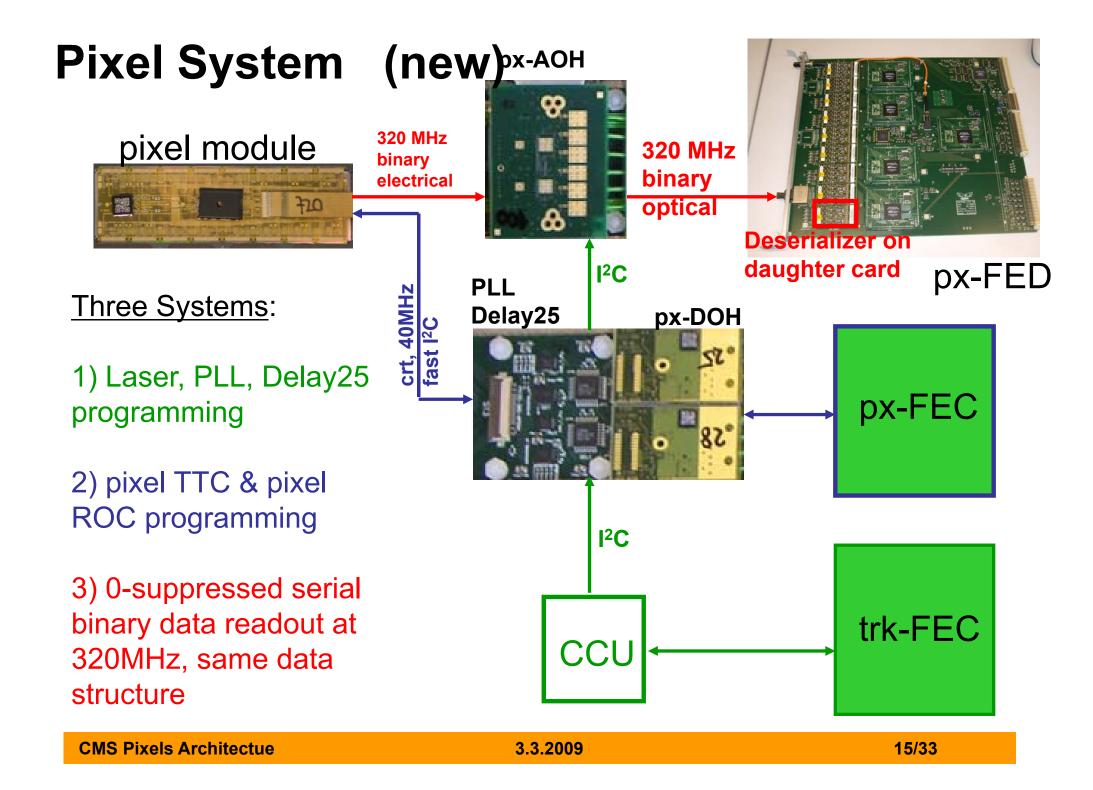

# New digital readout

- In 4 layer barrel pixel system we will have 1216 modules (128 / 224 / 352 / 512)

- We will have to re-use existing fibres from PP1 out. 1536 fibres mounted (including spares)

- → can only use one fibre per module everywhere. (now 2 fibres per module for layer 1 and 2)

- Present analog links too slow. Hard to make faster.

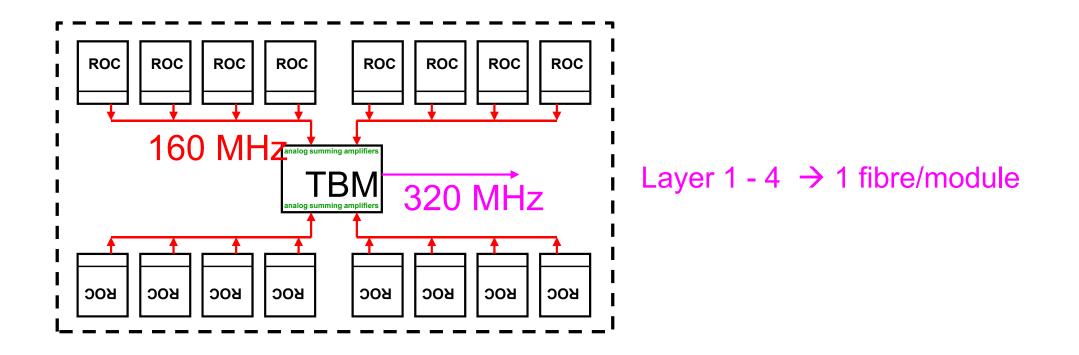

- New readout with 320 MHz digital links (160 MHz from FE to TBM)

- Development of fast very low power copper links at PSI (see talk W. Erdmann)

- Development of fast low power ADC, clock-multiplier with PLL at PSI (see talk of R. Horisberger)

### New digital module readout

$ROC \rightarrow TBM$  : 160 MHz digital readout (digitized Pulseheight, 8t TBM  $\rightarrow$  pxFED : 320 MHz digital readout (digitized Pulseheight, 8t

# New copper links

#### Idea: reduce connectivity (no endring prints) and material

#### Existing System in CMS Pixel Detector

#### Micro Twisted Pair Cable

cross section 20 µm Self Bonding Enamel Polyamide Isolation Polyesterimide Cu Al core 125 µm Al core + Cu 1 INOX2

First Choice:

- twisted pair self bonding wire

- 125 µm wire diameter (4um Cu)

- 10 mm per turn

Electrical characteristics:

- Impedance: 50 Ohms (very low for differential line)

- Impedance change: 1.3 Ohms per 1 µm distance variation (Calculation done with ATLC by Sandra Oliveros UPRM)

- v = 2/3 c<sub>0</sub> (5 ns/m)

- C = 100 pF/m, L=250 nH/m

- Phase I:

- Layout of 4 layer / 3 disk system

- Electronics upgrade

- Phase II:

- Overview of present front end and ist limitation

- ROC considerations

- Hit / data rates

- Powering scheme

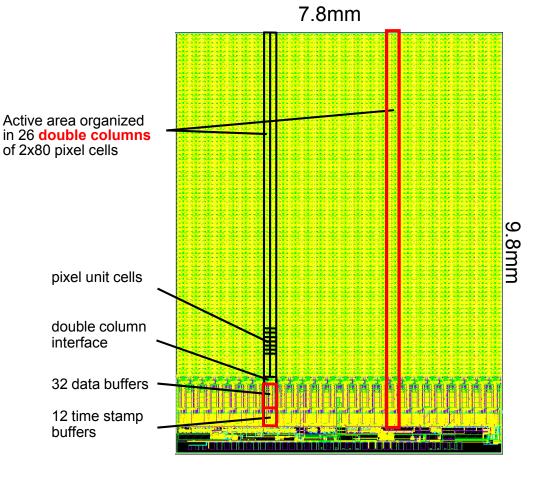

### Readout Chip PSI46V2

0.25 mm technology

Pixel size 100x150µm<sup>2</sup>

4160 pixels in array of 52x80

Pixels organized in double columns.

Column drain architecture

Size of double column periphery: 900µm. Mainly due to time stamp and data buffers (800µm)

Chip periphery contains voltage regulators, fast I<sup>2</sup>C interface, 28 DACs for chip

s Architectue

3.3.2009

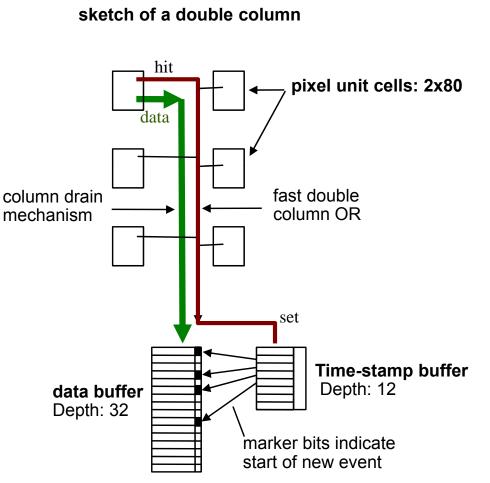

### Column drain architecture

•Designed for 10% occupancy (≈7cm layer at 10<sup>34</sup>)

•Pixel hit information transferred to time stamp and data buffers

•Kept there during L1 trigger latency

•Double column stops data aquisition when confirmed L1 trigger → dead time

Double column resets after readout

→loosing history

•Serial readout: Controlled through readout token passing from chip to chip and double column to double column. Chips daisy chained 8 (16)

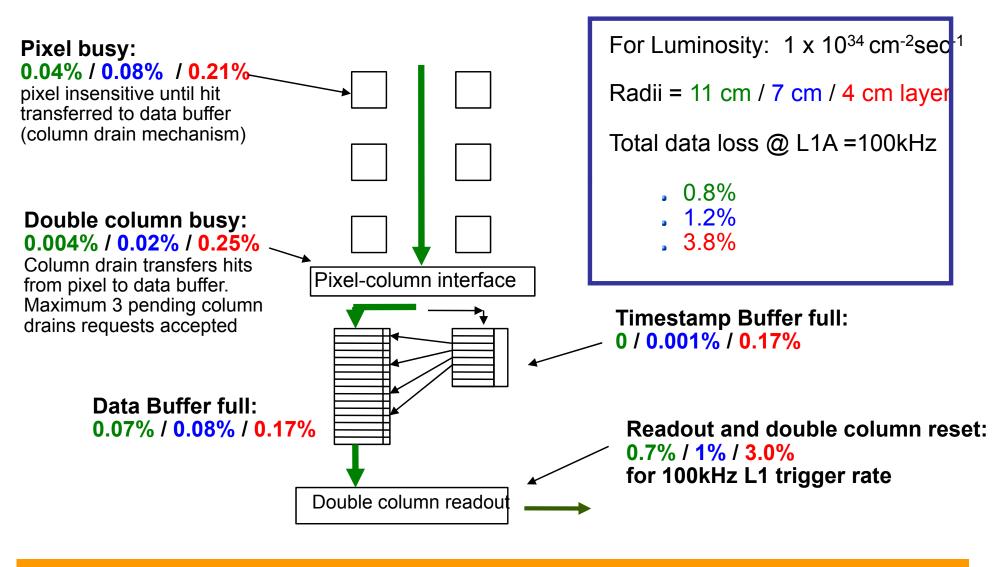

#### Data loss mechanisms

3.3.2009

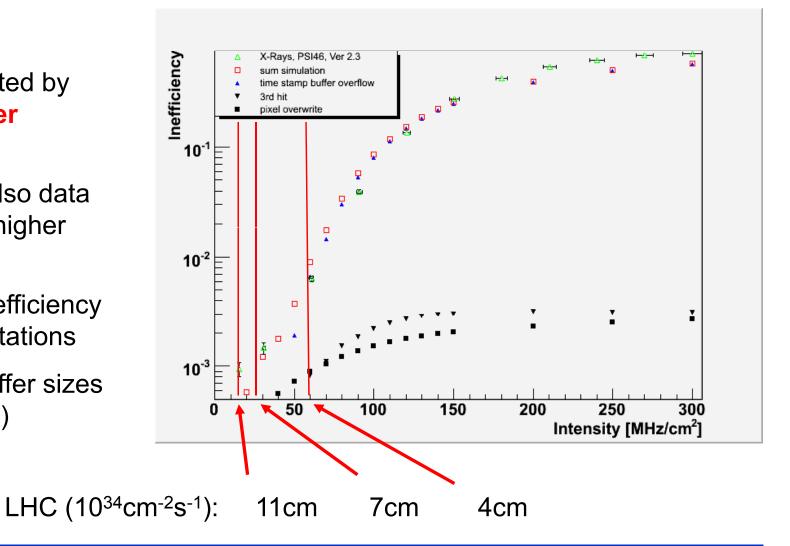

### Contributions to data loss

Entirely dominated by timestamp buffer overflows

In experiment also data buffer overflow (higher pixel multiplicity)

Steep rise of inefficiency due to buffer limitations

Extension of buffer sizes is trivial (no R&D)

SLHC rate data losses strongly dominated by finite buffer

CALE Prixels Architectue

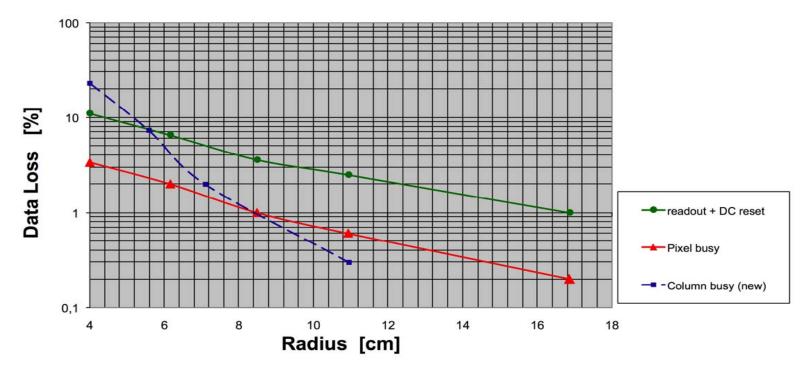

#### Inefficiency vs radius for SLHC rates

Buffers can be enlarged (trivial). What is next?

- 1. Next dominating effect are readout losses. The column is stopped after a L1 accept and reset when read out

- 2. Column drain is overloaded at low radii

- 3. Pixel size not really an issue

### Need for new architecture

•Readout losses can be reduced by more intelligent buffer logic, such that column can contineously take data (not trivial, but feasible)

•What stays is the busy column drain. All hits are copied down to the perifery  $\rightarrow$  huge data traffic

•Column drain architecture breaks down below 8cm at SLHC rates

Need entirely new architecture for SLHC

#### No proposal yet

- Phase I:

- Layout of 4 layer / 3 disk system

- Electronics upgrade

#### • Phase II:

Overview of present front end and ist limitation

#### – ROC considerations

- Hit / data rates

- Powering scheme

### Pixel size

Has impact on track resolution and data traffic. Should be as small as possible for physics (less (no) charge sharing after heavy irradiation), but this will increase data traffic

– Can be reduced by using thinner sensors (i.e.  $225\mu$ m)

- We want to keep good z-resolution. Physics benefit from 3D vertexing. New pixel size could be 75 μm x 100 μm (half the area of today)

- Has to be studied in detail, but: must be considered together with FE architecture from the beginning.

### Future ROC

Column drain architecture as in present ROC doesn't work. Two options:

- 1. Broader buses for column drain (CD)

- More metal layers allow for higher connectivity

- DMILL (2.5 metals): analog CD needed due to limitation in connectivity

- IBM 0.25µm (5 metals): address digital in CD, 9 bit bas

- 130/90nm (up to 8 metals): could go to broader buses, eventually recover CD

- 2. Store hits in pixel during trigger latency (preferred)

- Only ≈ 0.2% of hits need to be read out, but column drain copies all hits to periphery

- This data traffic needs power and time

- $\rightarrow$ Store hit in pixel cell.

- →have to distribute clock across whole chip. Power penalty decreases for smaller technologies (C/2 V<sup>2</sup>)

- Phase I:

- Layout of 4 layer / 3 disk system

- Electronics upgrade

#### • Phase II:

- Overview of present front end and ist limitation

- ROC considerations

- Hit / data rates

- Powering scheme

#### Estimated data rates

Assumptions:

•Peak lumi = 10<sup>35</sup> cm<sup>-2</sup>s<sup>-1</sup>

•Trigger rate = 100 kHz

•32 Bits/hit (8 ROC address, 16 pixel address, 8 pulse height

•GBT: 2.5 Gbit/s per link usable for data

| Layer      | Area      | Pixel hits<br>[MHz/cm²] | Pixel readout<br>[MHz] | Bit rate<br>[Gbit/se<br>c] | GBT<br>links | % of total<br>bandwidt<br>h |

|------------|-----------|-------------------------|------------------------|----------------------------|--------------|-----------------------------|

| 3.9 cm     | 1280      | 1400                    | 4480                   | 143                        | 57           | 31                          |

| 6.8cm      | 2236      | 690                     | 3857                   | 123                        | 50           | 27                          |

| 10.9<br>cm | 3514      | 380                     | 3338                   | 107                        | 43           | 23                          |

| 16.0cm     | 5112      | 220                     | 2812                   | 90                         | 36           | 19                          |

| Total      | 1214<br>2 |                         |                        | 463                        | 186          |                             |

- Phase I:

- Layout of 4 layer / 3 disk system

- Electronics upgrade

#### • Phase II:

- Overview of present front end and ist limitation

- ROC considerations

- Hit / data rates

- Powering scheme

# Powering

Have to supply (a lot) more power through existing cables

- Baseline concept is DC-DC conversion to reduce currents (serial powering still pursued at lower priority as backup solution)

- Design studies of 3:2 step down converter with switched capacitors at PSI (see talk B. Meier). Idea: put converter in FE chip. Reduce number of supply voltages (i.e. generate analog voltage from digital supply).

- Cons: cannot regulate, works only for small currents (or efficiency drops too low)

- Other solution: DC-DC conversion on supply tube

- Need higher currents/power

- Charge pump ( $\rightarrow$ LBL, M. Garcia)

- Inductor based converter

- $\rightarrow$  air coil is difficult to build for high power

**CMS Pixels Architectue**

3.3.2009

### Conclusion

CMS plans to replace pixel system ~2013 with new 4 layer barrel + 3 disk system

Will reuse parts for Phase II

- •Mechanical structure with CO<sub>2</sub> cooling

- •Low power copper links

- •ADC, PLL (migration to new technology)

For Phase II we will need entirely new FE architecture To deliver the higher currents through the existing cables, CMS plans to use DC-DC converters on the detector