# CMS strip tracker at SLHC Requirements and Architecture

Karl Gill

# Outline

- Perspective of existing CMS Si-strip Tracker and electronic system

- Upgrade roadmap

- Requirements

- General CMS Outer Tracker requirements

- Tracking

- Trigger

- Environment

- Boundary conditions

- P5 existing services

- Progress on Architecture

- Outer tracker readout (more details from Mark Raymond)

- Conclusion

Thanks to G. Hall, M. Raymond, D. Abbaneo, M. Pesaresi and other TK colleagues

# Outline

- Perspective of existing CMS Si-strip Tracker and electronic system

- Upgrade roadmap

- Requirements

- General CMS Outer Tracker requirements

- Tracking

- Trigger

- Environment

- Boundary conditions

- P5 existing services

WARNING : WORK IN PROGRESS

- Progress on Architecture

- Outer tracker readout (more details from Mark Raymond)

- Conclusion

Thanks to G. Hall, M. Raymond, D. Abbaneo and other TK colleagues

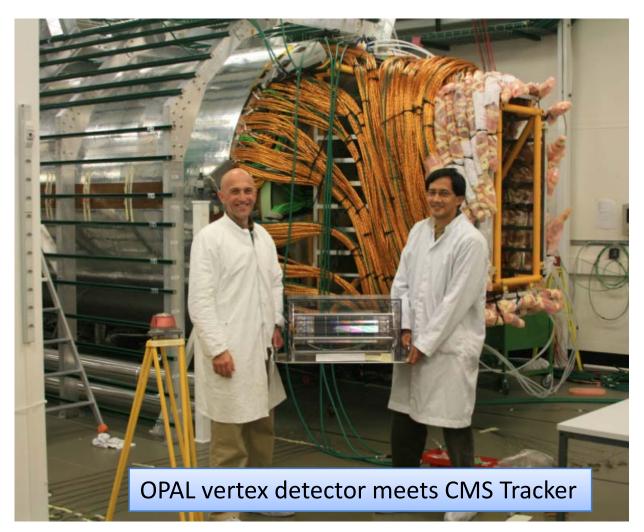

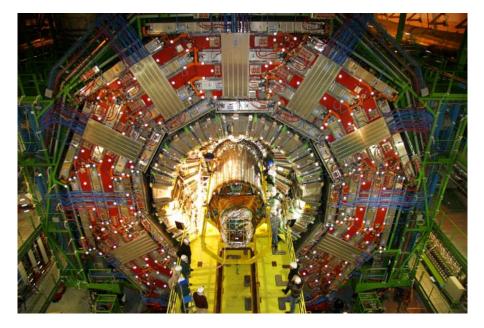

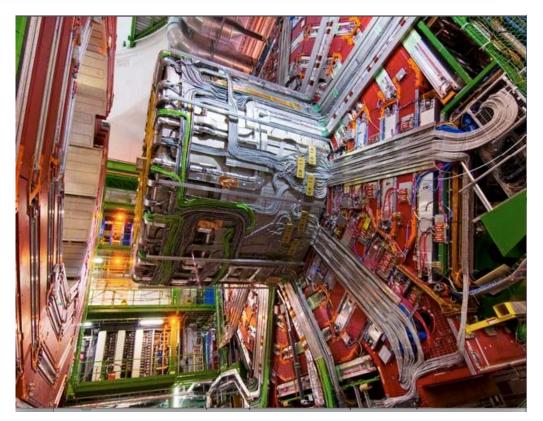

# Experience with the current CMS strip Tracker

### Current CMS Si-StripTracker

- 200m<sup>2</sup> Silicon in 22m<sup>3</sup>

- 300-500μm thickness

- 9.3M channels

- 50μm to 180μm

- Occupancy ~1%

- η coverage up to 2.5

- 16,000 Modules

- 27 types

- 73k APV Chips

- 250nm IBM CMOS

- 40k Optical link channels

- 440 Front End Drivers

- 2000 Power Supplies and power cables

- P=33kW inside TK, 20kW in cables, I=15kA

- 180 Cooling Loops

- $(C_6F_{14}, TK \text{ to } -30^\circ\text{C})$

- Including pixels

- >500 Physicists and Engineers

- 54 Institutes in 10 Countries

### CMS Si-Strip Tracker 2008/9

- 15 years R&D, Production, Assembly and Testing

- 1 day to install, 3 months to connect

- 3 months to commission (99%)

- 3 further months practising operations

- Including 1 month cosmic running at 4T (CRAFT).

- Very successful experience

- 96% TK up-time, >98% TK working, 8M events with TK tracks

- S/N >25, alignment to 25  $\mu$ m in barrel, 70  $\mu$ m in endcaps

- Efficiency per layer >99%

http://cms-tracker.web.cern.ch

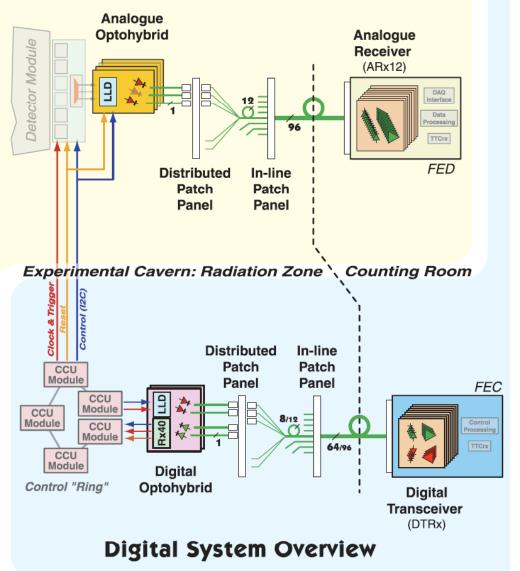

### Current strips electronic system

- Readout System

- Unsparsified, synchronous analogue front-end

- 100kHz readout, 3.2µs trigger latency

- 73k readout chips

- Noise spec <2000e-, 50ns shaping,</li>

- Deconvolution or Peak mode

- 38k optical links

- Most novel development

- 440 FEDS

- 40MSamples/s

- 10 bit resolution, 8MSB kept

- Digital Control System

- 44 FECs

- Token ring@ 40Mbit/s

- 3k optical links

- I2C at front end

- BER < 10<sup>-12</sup>

- Also TTC and APVE (x4 partitions)

- Commercially available technologies

- Used rad-tolerant parts (eg IBM 250nm)

- Rad tolerant system design (eg links)

#### **Analogue System Overview**

Fig: Jan Troska, NSS 2003

## Some of the lessons learned

- Development/Production/Construction

- Profited from good relationships with industrial partners and strong QA/QC

- Maintain good contacts, make use of proven technologies

- To ease logistics during production, assembly and reduce cost of spares

- Minimise number of variants at front-end

- Make common development (only) where appropriate

- eg optical links

- Many same parts across readout and control system

- Also across systems: CMS TK strips (then pixels, ECAL, EE,..)

- Operations

- Complexity/scale of system:

- (Re-)Commissioning time is long

- Days/weeks, should not increase

- (Re-)Configuration time is long at start of run

- ~minutes, should not increase

- Electronic system proving to be high quality and robust

- Only relatively few experts needed to operate and maintain

# Some of the lessons learned (ctd)

- Architecture choice (readout): Synchronous, analogue system worked well

- Minimal power dissipated inside Tracker, intelligence put mainly at back-end (FED)

- Power consumption is stable and uniform

- Tracker always in known state

- Robust against overflow

- APV emulator (and FED) can throttle L1

- Few problems in operation (credit of course also to developers)

- Setup, checkout, calibration, synchronization, debugging and diagnostics

- Scaled well from smaller test-systems to final system

- Modest test system can still used for deep investigations and development

- Tracker digital control ring system also works very well

- Have to find best way to build on these solid foundations

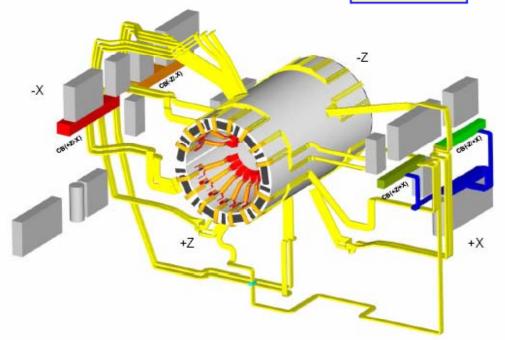

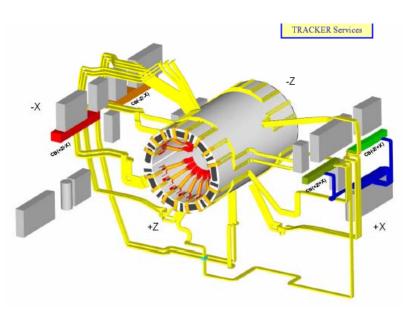

# Boundary conditions for upgrade: Re-use of existing TK services

### Services constraints

- Power cabling

- From TK PP1 to 33 specific racks distributed across 6 balconies

- Impossible to remove and re-route

- Optical cabling

- From TK PP1 to 14 racks in USC

- Impossible to reroute on YB0 or in UXC

- Difficult also to re-route in USC

- Cooling

- Pipes (2x 91 circuits) for TK cooling available

- Current monophase C<sub>6</sub>F<sub>14</sub>

- 33kW inside TK, 20kW in cables

- Near limit (pipes, cables)

- Hope to upgrade to biphase CO<sub>2</sub> cooling

- building on pixel Phase 1 R&D

- Cannot take this for granted today

- Tracker PP1 patch panels inside solenoid

- See extra slides

# Efficiency for re-use?

- Conclude we have to live with what we have now

- from PP1 patch-panel outwards

- It was (and will be again) a daunting task to make sensible combined grouping of cooling, power, control and readout channels throughout the Tracker.

- Optimised for operation and reliability as well as power, material

- Should do as soon as we arrive at a good layout

- Feed back into detail specification and design of mechanical structures and cooling

- Guess efficiency factor for re-use?

- Power cables, crates and racks

- e.g. aiming high  $0.9^3 \approx 0.7$

- Then add in fibres, pipes

- An impressive puzzle!

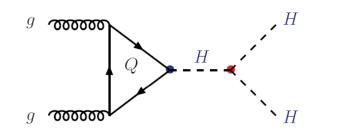

# Roadmap for CMS Tracker Upgrade

### Physics case

- Essentially unknown until LHC data come

- general guidance as for LHC granularity, pileup...

- Improve statistics in rare and difficult channels

- eg: whatever Higgs variant is discovered, more information on its properties than LHC can provide will be needed

- Expected HH production after all cuts in 4W -> I<sup>+/-</sup>I<sup>+/-</sup> + 4j mode

- $-\sigma$  = 0.07-018 fb for m<sub>H</sub> = 150 200 GeV

- with  $3000 \text{ fb}^{-1} \approx 200 600 \text{ signal events}$

- An excellent detector is essential...

- plus significant background

- ...even better than LHC to cope with particle density & pileup

- which should also be flexible to adapt to circumstances

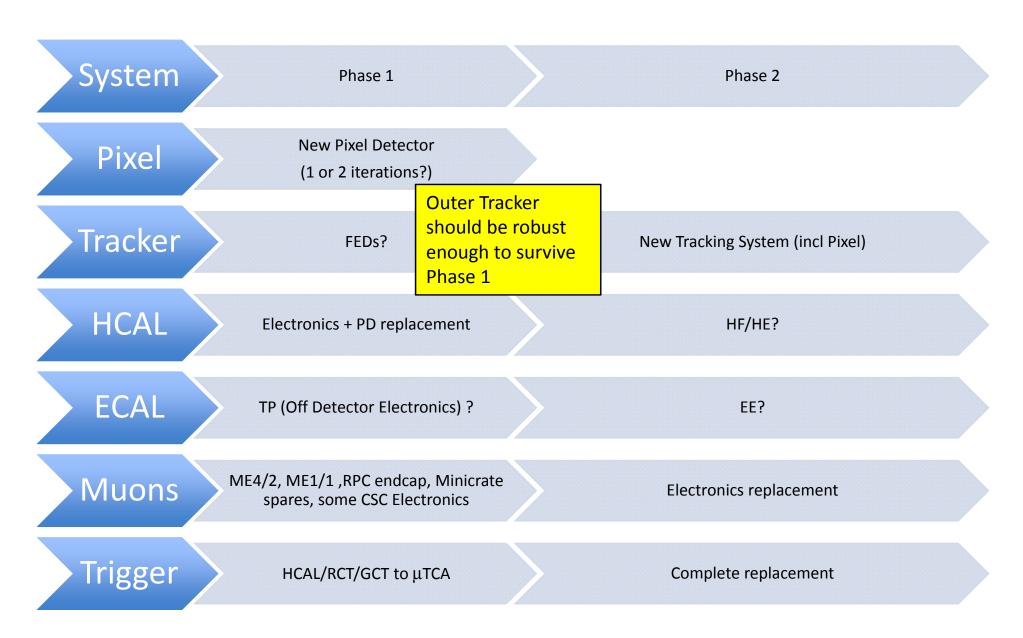

# **Overall CMS Upgrade Scope**

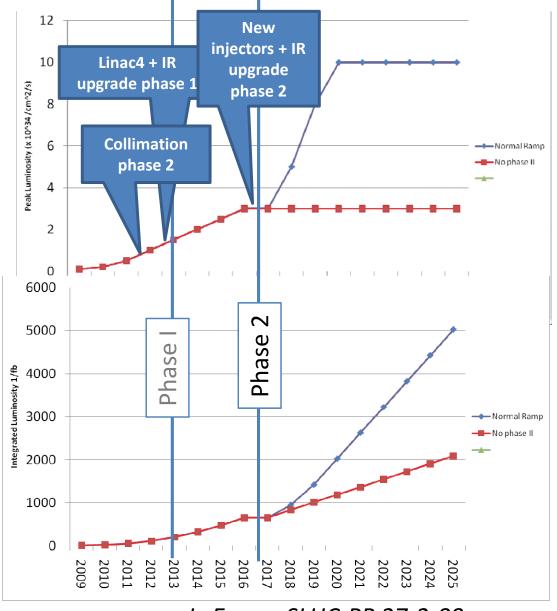

# CMS Tracker Upgrade Roadmap

- Phase 1

- Replace pixels after radiation damage

- Opportunities:

- Add 4th barrel layer pixel

- Ultra-light mechanics

- Light copper links

- Move connections further away

- CO<sub>2</sub> cooling

- Upgraded power system

- 60% increase inside detector

- DC-DC attractive

- Good flexibility for when to do this upgrade in terms of (de)installation

- Rapid removal/installation procedure

- Also, maybe Si-strip FEDs need upgrade (TBC)

### • Phase 2

- Totally new TK and pixel systems

- Higher granularity outer TK

- L1 Trigger capacity

- Improved cooling

- Improved power

- DC-DC

- New high speed readout and control

• L. Evans, SLHC-PP 27-2-09

### SLHC Outer Tracker requirements

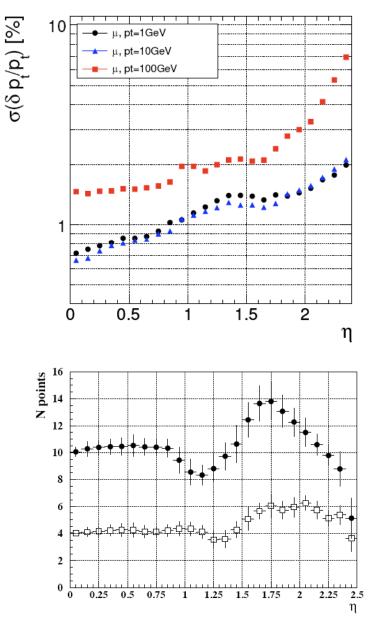

# Tracking performance

- Maintain current TK performance

- Reconstruct all tracks >1GeV in  $\eta$ <2.5

- $P_T$  resolution ~1% for 100GeV muons

- Pitch remains the same

- Strip length has to decrease to keep occupancy <few %</li>

- Resolve primary vertices

- To be seen whether stereo layers still needed in outer barrel, or if 4 layer pixel sufficient

CMS paper, JINST, 2008

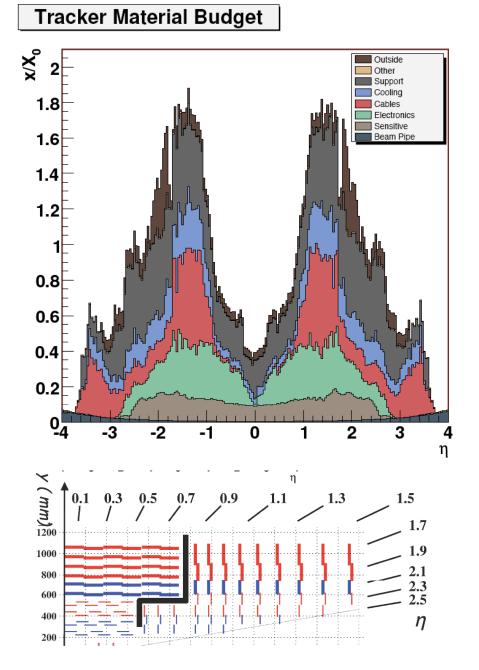

### Material budget

- Where we should try hard

- May be only way to improve tracking performance

- Aggressively minimise material

- Optimise layout and mechanics

- Support structure and PCBs

- Cooling pipes and thermal contacts

- Minimize power dissipation, optimise:

- Layout, granularity

- Front-end functionality

- Data transfer inside TK

- Use of data link capacity

- Data concentrator needed?

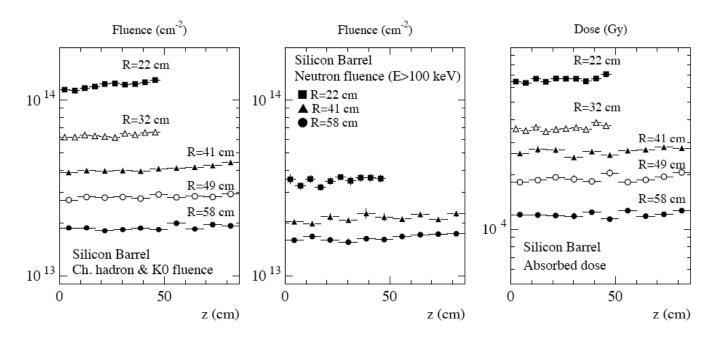

### Tracker Environment

- Expect to be able to scale up factor 10 total from LHC estimates of radiation levels

- Will still need to run cold to avoid reverse annealing (<0°C)</li>

- and possible thermal runaway

- CMS Magnet to remain at 3.8T

Fluences and doses after 500fb<sup>-1</sup> (LHC lifetime) Totals are factor 10 higher at SLHC Inner layers dominated by ~200MeV pions M. Huhtinen, CMS TK TDR, 1998

Detector will be, like now, <u>inaccessible once installed</u> Need lifetime of parts to be qualified for 10yrs operation in this environment.

Deep QA Programme needed. COTS issues will resurface. Must apply ALARA principles to upgraded TK installation.

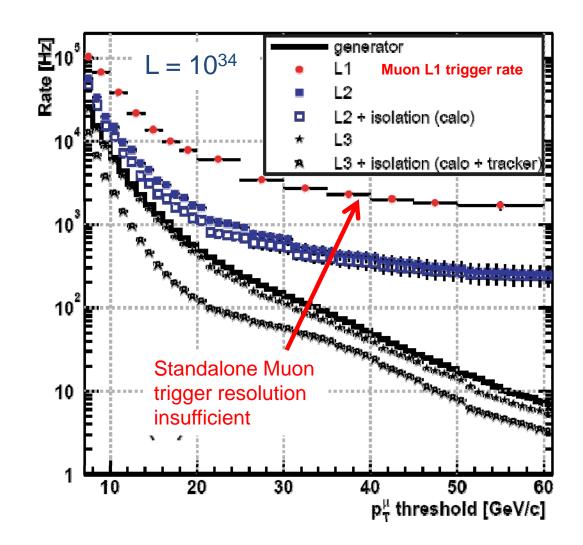

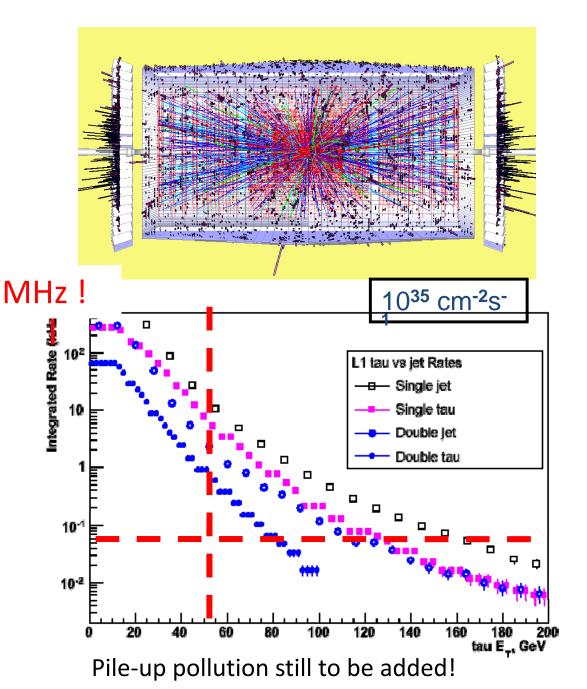

### SLHC Track-Trigger requirements

### SLHC: Track Trigger Requirement: Muons

- Standalone L1 muon rate too high at 10<sup>35</sup>cm<sup>-2</sup>s<sup>-1</sup>

- HLT currently brings in TK info, giving efficient P<sub>T</sub> discrimination

- TK should provide info in L1

- trigger primitive up to  $\eta$ =2.5

- high  $P_T$  track 'stub' at precise  $\eta, \phi$

- To see if 1 or 2 doublet layers suffice

# SLHC: Track Trigger Requirement: e, $\tau$

- Normal isolation cuts will not work

- Problem of combination of backgrounds plus pile-up

- jet rejection against  $\tau$  lost

- fluctuations in pile-up fake  $\tau$  !

- e/γ QCD backgrounds

- ECAL trigger towers never empty

- Need primary vertex info, plus tracks > ~1GeV to recover isolation cut

- Hundreds of primary vertices!

## Track-Trigger impact on Outer TK system

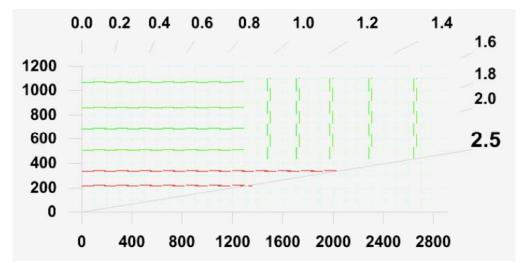

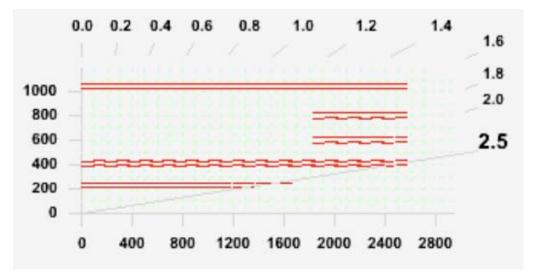

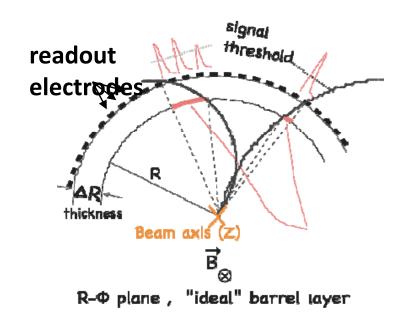

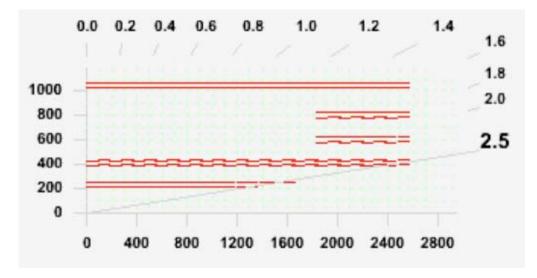

- The location and geometry of the "P<sub>T</sub> layers" have to be integrated into the layout of the 'outer' Tracker

- These layers the most challenging

- Will require very dense services: power, cooling, readout

- Note,  $\mathsf{P}_{\mathsf{T}}$  layers should also contribute to 'regular' tracking

- Number of dedicated  $P_T$  layers and their position within the "outer Tracker" being studied

- Layout, Simulation and Trigger Task Forces

- Strawmen under study (besides development of the study tools, already a lot of work in itself)

- Full η coverage

- Long-barrel PT layers

- 2x2 layers at ~20cm, 30cm radii

- Full long barrel outer tracker of stacked triggering layers (FNAL strrawman geometry)

- Outer barrel only

- Stacked layers (several ideas)

- Cluster size method

- Aim to converge on best geometry

- providing the needed rejection at L1

- Other criteria good tracking performance (power, material budget), costs, and challenges

### Layout geometry tool

#### Modules

Cost estimates:

| • | Produce layouts                         |                         | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub> | B <sub>5</sub> | E <sub>7</sub> | Total                 |

|---|-----------------------------------------|-------------------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|

|   | from parameter<br>set                   | Tag                     | PTBARRELL1     | PTBARRELL2     | TOBL1          | TOBL2          | TOBL3          | ENDCAPR7       |                       |

|   |                                         | Туре                    | pt             | pt             | rphi           | rphi           | rphi           | rphi           |                       |

|   |                                         | Area (mm <sup>2</sup> ) | 8580.5         | 8580.5         |                |                |                |                | $26.9(m^2)$           |

|   | <ul> <li>Size, pitch, radii,</li> </ul> | Area (mm <sup>2</sup> ) |                |                | 8580.5         | 8580.5         | 8580.5         | 8516.7         | 87.7(m <sup>2</sup> ) |

|   |                                         | Occup (max/av)          | 0.7/0.3        | 0.3/0.2        | 4.3/3.4        | 2.4/2.1        | 1.5/1.4        | 1.4/1.3        |                       |

| • | Calculates                              | Pitch (min/max)         | 90             | 90             | 120            | 120            | 120            | 108/119        |                       |

|   | occupancy, power                        | Segments x Chips        | 48x8           | 48 <b>x</b> 8  | 2 <b>x</b> 6   | 2 <b>x</b> 6   | 2 <b>x</b> 6   | 2 <b>x</b> 6   |                       |

|   | estimate                                | Strip length            | 1.9            | 1.9            | 46.3           | 46.3           | 46.3           | 48.7           |                       |

| • | For a given                             | Chan/Sensor             | 49152          | 49152          | 1536           | 1536           | 1536           | 1536           |                       |

| • |                                         | N. mod                  | 512            | 1056           | 1120           | 1344           | 1680           | 760            | 12640                 |

|   | architecture                            | N. sens                 | 1024           | 2112           | 1120           | 1344           | 1680           | 760            | 13408                 |

|   | estimate readout                        | Channels (M)            |                |                | 1.72           | 2.06           | 2.58           | 1.17           | 17.01                 |

|   | bandwidth                               | Channels (M)            | 50.33          | 103.81         |                |                |                |                | 154.14                |

|   | Rough cost                              | Power (kW)              | 5.0            | 10.4           | 1.0            | 1.2            | 1.5            | 0.7            | 25.6                  |

| • |                                         | Cost (MCHF)             | 17.6           | 36.2           | 3.8            | 4.6            | 5.8            | 2.6            | 88.9                  |

|   | estimate                                |                         |                |                |                |                | Ň              |                |                       |

Material budget to be added soon to tool

Pt modules: 200.0 CFH/cm2 - Strip modules: 40.0 CHF/cm2 Power estimates:

Pt modules: 0.10 mW/chan - Strip modules: 0.60 mW/chan

http://abbaneo.web.cern.ch/abbaneo/tkgeometry/summaries/

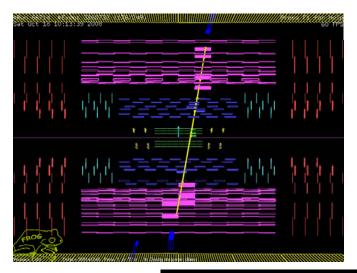

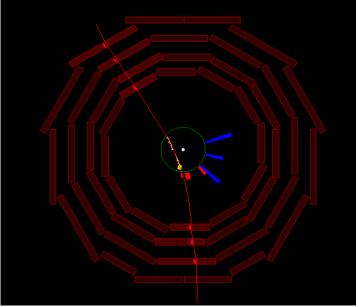

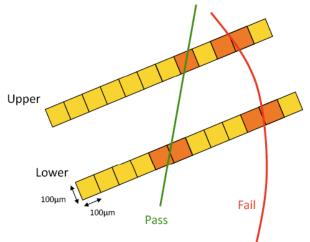

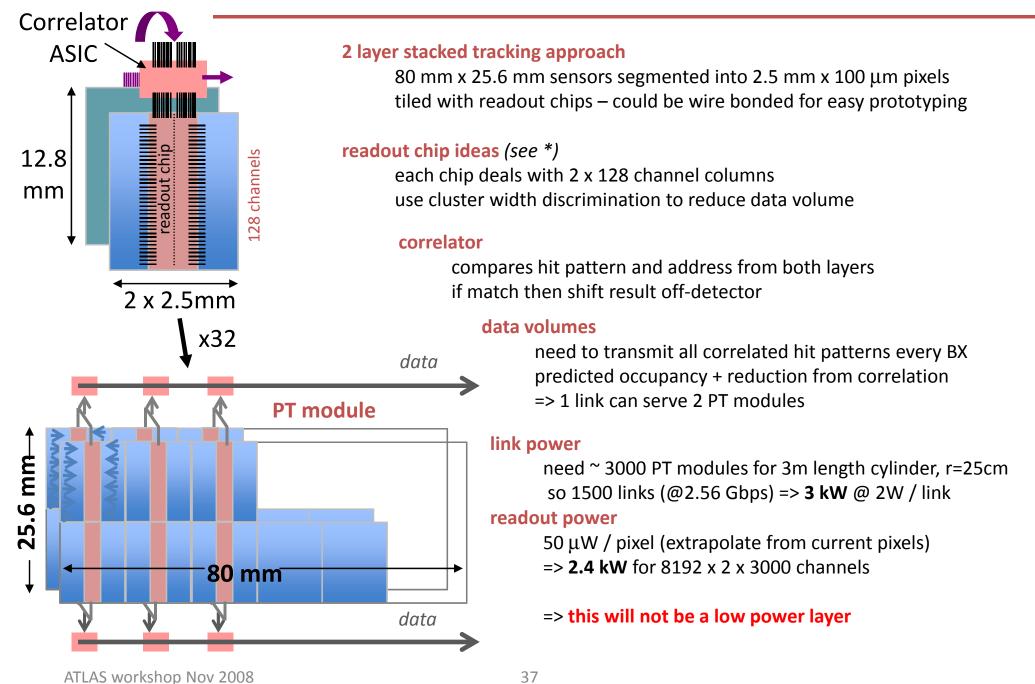

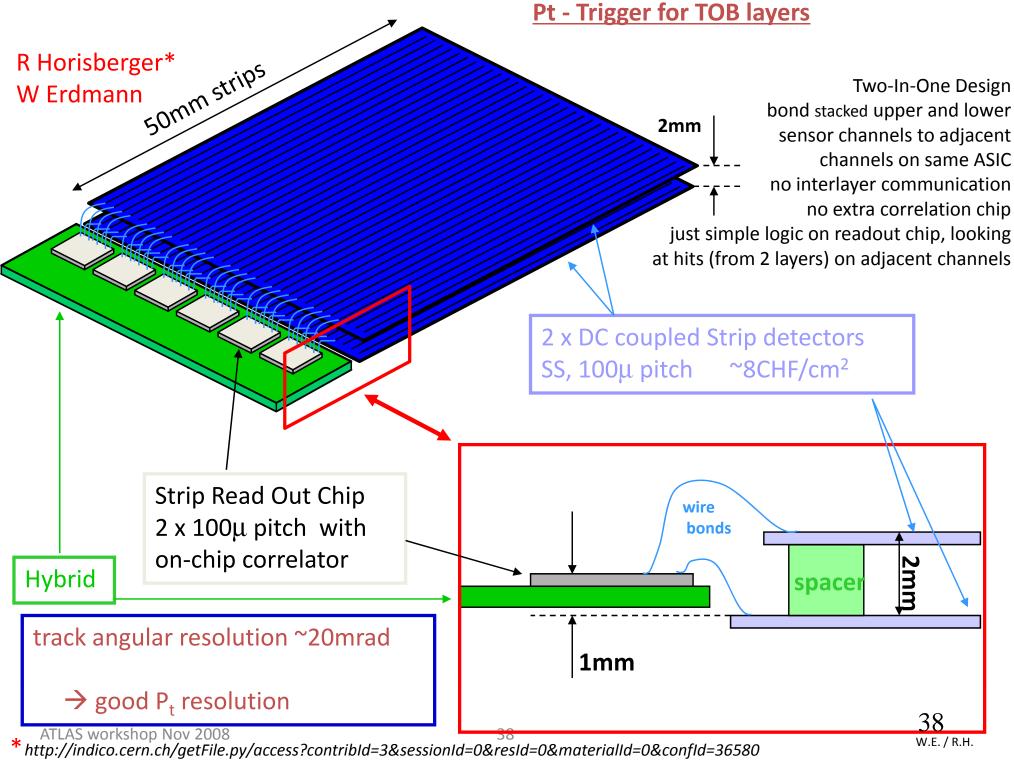

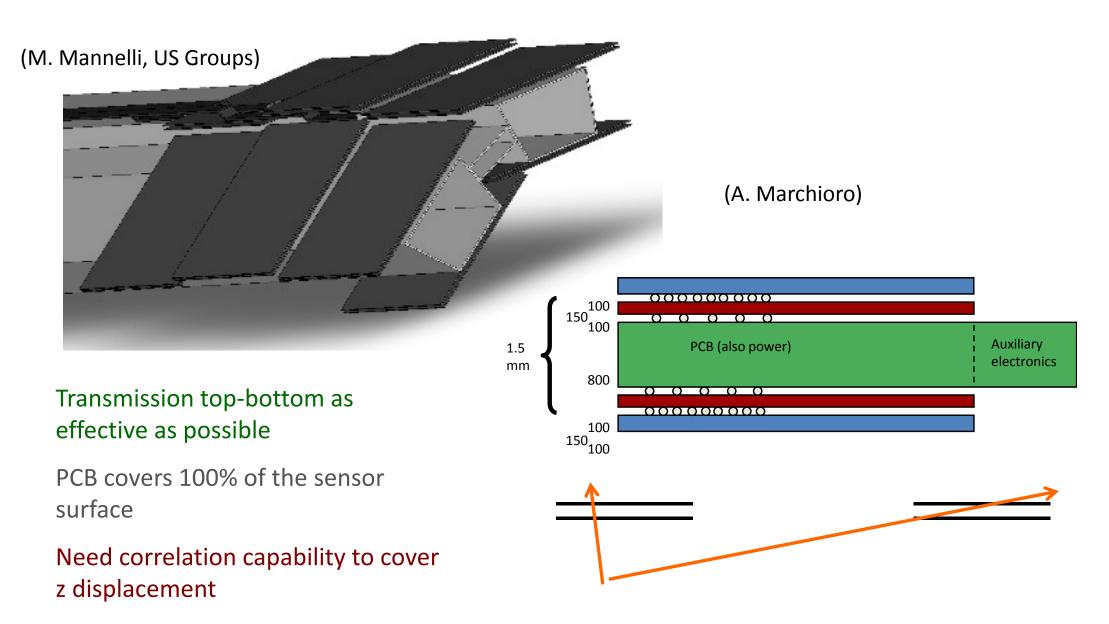

# P<sub>T</sub>-layer approaches

- Limited number of proposals so far

- try to send reduced data volume from detector for further logic

- eg factor 20 with  $p_T > few GeV/c$

- (A) Use cluster width information to eliminate low  $p_T$  tracks (F Palla et al)

- simple but thinner sensors may limit capability

- (B) Compare pattern of hits in closely spaced layers

- p<sub>T</sub> cut set hv angle of track in laver

### **Stacked Layer Algorithm Performance**

Efficiency Sensor separation is again an effective cut on p<sub>t</sub> 0.8 Again, the width of the 1mm sensor separation transition region increases with 0.6 separation. 2mm sensor separation  $\cap$ 3mm sensor separation Δ Due to: 0.4 4mm sensor separation - pixel pitch Increasing - sensor thickness separation 0.2 - charge sharing - track impact point Efficiencies decrease with sensor 25 10 20 5 15 30 p<sub>T</sub> [GeV/c] separation due to the larger  $p_{T}$  discriminating performance of a stacked layer at r=25cm for various sensor column window cuts – sensor

acceptances and fake

containment are issues

separations using 10,000 di-muon events with smearing

Cuts optimised for high efficiency: Row window = 2 pixelsColumn window = 3 pixels @ 1mm, 2mm; 4 pixels @ 3mm; 6 pixels @ 4mm

Mark Pesaresi

Imperial College London

# Architecture for Track Trigger system

- Must respond quickly to every (40MHz) bunch crossing with signal to L1 with minimal latency and dead time

- Expect to be binary, sparsified

- Correlator ASICs needed near front-end

- Position to be decided (heat removal, powering...)

- Must be programmable to cover different configuration needed for different locations in detector

- How many high speed optical links needed?

- For two barrel doublets up to  $\eta$ =2.5

- Estimated to be ~200 candidate stubs (~1% of tracks, plus fakes) to be readout each 40MHz

- How to gather gather and multiplex data into link branchs (eg GBT 80MBit/s branches)

- If >1 doublet stack used, make inter-stack correlation of track-stubs to back-end?

- Save power, keep flexibility, profit from reduced development time

- Generate signals efficiently from both isolated high  $P_T$  tracks and high  $P_T$  tracks in jets

- How to get out 'regular' tracking data from same layers

- 100kHz readout

- Maybe only need to readout one layer of a doublet

- Favouring binary, unsparsified for rest of system

- Try to match trigger layers 'standard' readout with rest of detector?

- Try to use same TTC, slow control system as rest of Tracker

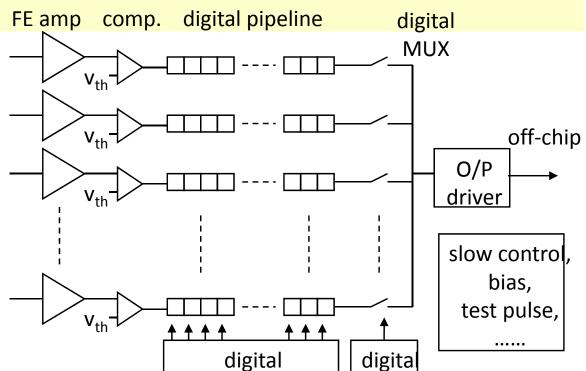

# Progress on 'standard' Outer Tracker readout architecture

### Outer readout

- Recall present architecture

- analogue, unsparsified, analogue optical links, synchronous

- external digitisation, cluster finding, zero suppression

- 0.25µm CMOS, FP edge-emitting lasers, single-mode fibres

- Pros

- works extremely well and easy to use with excellent diagnostic capability and noise robustness

- occupancy insensitive few power fluctuations

- synchronous system easy to model and understand

- cost effective, despite customisation

- Possible cons for future

- Not enough bandwidth at front-end, new optolinks TX and RX required analogue not an option

- if analogue information to be preserved, on-detector ADC

### M Raymond TWEPP 08

### binary architecture – un-sparsified

### what about binary un-sparsified?

much simpler than "digital APV" particularly for pipeline and readout side

need fast front end and comparator => more power here

but no ADC power and simpler digital functionality will consume less

### allows retention of features we like

simpler synchronous system no FE timestamping data volume known, occupancy independent (so no trigger-to-trigger variation)

**but** less diagnostics (can measure front end pulse shape on every channel in present system some loss of position resolution, common mode immunity)

### binary, un-sparsified is an option we are considering

### Readout: Operating Requirements

- Trigger rate up to 100kHz

- Latency = 6.4us (ECAL chip buffer size)

- Trigger rules and coding ?

- Bigger event size

- More bandwidth needed at backend for transmission to global DAQ (FED output)

- Run Control/Configuration

- Start-up, re-start configuration should be fast (~minute whole system)

- Synchronization (internal to Tracker then adjust global phase?)

- Straightforward scalability from small to large systems

- Ability to use substitute parts to reduce costs, e.g. electrical links on test benches rather than optical where appropriate

- Monitoring

- Want to have simple interfaces and functions to monitor state of system and correct functionality, e.g

- Slow control

- Emulator

- Spy channel

- DQM

# The role of monolithic detectors

- Can they be major contributors to new Tracker?

- Pros

- a single concept providing tracking and trigger functions would be easier to build a common effort around

- Cons

- the technology is unproven and unlikely to mature rapidly

- there are many unknowns which will require time and effort

- the R&D cost may be high, since deep sub-micron processes

- If good progress could be shown in ~2 years, it will not be too late to review the tracker design

- significant power or functional advantages would be a strong motivation to adopt a new technology, even if late

### Conclusion

- Upgrade to CMS Tracker will be again a complex, long project on a large scale

- Additional challenge of the operating environment

- New requirement for triggering functionality

- Must profit from lessons learned, feeding these back into Requirements, Specs, QA Programme, budgets, plans...

- Aim to obtain functionality with good margin whilst aiming for high yield for minimum power, material, costs (including spares)

- Requirements definition for CMS SLHC Tracker very much a work in progress

- Some requirements we have to wait for Physics

- e.g. radiation environment, occupancy, physics requirement

- Track trigger efforts gathering momentum

- iterate between simulations and layout tool

- Iterate between TK and CMS (Trigger, Physics and other subdetectors)

- Good progress on outer Tracker readout architecture

- Favouring synchronous binary, un-sparsified readout

- Simplicity here should free up resources for other work needed

### Extra slides

# **TK Connections inside CMS detector**

- Integration inside CMS detector volume (YB0)

- Tracker PP1 patch panel, 2x16

- ~ 90 power/control cables, 20 multi-ribbon fibre cables, 12 Cu pipes

- PP1 are permanent fixtures, as are cables from PP1 outwards

- To complicate matters, many ancillary systems in all PP1s

- Environmental Sensing, Heater wires, Dry air, Cable channel water

- Plus, in 'special PP1s'

- Pixels services, BCM, PLT, Laser Alignment, Thermal screen

- Also Endcap (TEC) connections at TK bulkhead to work on

- Complicated situation raises ALARA concerns for future

- 3 months to connect

- Has to be disconnected carefully (since re-using services)

- Have documented all connections and have a PP1 mockup

- How will different teams manage in ~10 years time.

- Must purchase (soon?) stock of new connectors

- MFS for fibres, custom electrical connections

### G Hall, M Pesaresi M Raymond

### possible PT module for inner layer

\*http://indico.cern.ch/getFile.py/access?contribId=15&sessionId=2&resId=1&materialId=slides&confId=36581

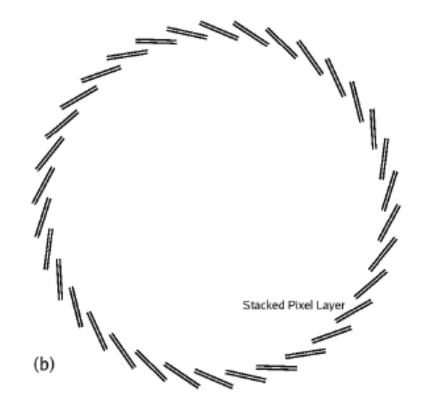

### Other approaches to stacked layers

Barrel layers only

### estimated link power contribution

| linl                                            | k # of 13     | 28 chan now                        | ver link nower/ |

|-------------------------------------------------|---------------|------------------------------------|-----------------|

| no. of chips / link depends on estimations of c | data volume – | <ul> <li>some details i</li> </ul> | n backup slides |

|                                      | speed                    | chips/link          | per link | sensor chan. |

|--------------------------------------|--------------------------|---------------------|----------|--------------|

| LHC unsparsified analog              | 0.36 Gb/s<br>(effective) | 2 / analog<br>fibre | 60 mW    | 230 μW       |

| SLHC digital APV no sparsification   | 2.5 Gb/s                 | 32 / GBT            | ~ 2W     | 490 μW       |

| SLHC digital APV with sparsification | 2.5 Gb/s                 | 256 / GBT           | ~ 2W     | 60 μW        |

| SLHC binary unsparsified             | 2.5 Gb/s                 | 128 / GBT           | ~ 2W     | 120 μW       |

### LHC unsparsified analog

230  $\mu$ W / sensor channel: ~ 10% of overall channel budget need to do better at SLHC (e.g. 10% of 0.5 mW = 50  $\mu$ W)

### **SLHC digital APV without sparsification not viable**

link power contribution too high (no. of channels will increase at SLHC)

### SLHC digital APV with sparsification appears best

**but** can only be achieved with extra buffering between FE chips and link more chips to develop, some additional power

#### SLHC binary unsparsified next best

has strong system advantages

# Layout tool output (continued)

- Stacked layer long-barrel geometry

- Strawman proposed at

FNAL workshop, 11/2008

Layers and disks

| Layer r | Ll  | Ll  | L2  | L2  | L3   | L3   | Ll  | Ll  | L2  | L2  |

|---------|-----|-----|-----|-----|------|------|-----|-----|-----|-----|

|         | 270 | 231 | 450 | 410 | 1080 | 1040 | 640 | 600 | 840 | 800 |

| Disk Z  |     |     |     |     |      |      |     |     |     |     |

| Ring r  |     |     |     |     |      |      |     |     |     |     |

| 1       |     |     |     |     |      |      |     |     |     |     |

| 2       |     |     |     |     |      |      |     |     |     |     |

| Modul   | les |     |     |     |      |      |     |     |     |     |

|                         | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | $B_4$   | B <sub>5</sub> | Total                 |

|-------------------------|----------------|----------------|----------------|---------|----------------|-----------------------|

| Tag                     | BARRELLI       | BARRELL2       | BARRELL3       | SHORTL1 | SHORTL2        |                       |

| Туре                    | pt             | pt             | pt             | pt      | pt             |                       |

| Area (mm <sup>2</sup> ) | 8580.5         | 8580.5         | 8580.5         | 8580.5  | 8580.5         | $288.7(\mathbf{m}^2)$ |

| Area (mm <sup>2</sup> ) |                |                |                |         |                | $0.0(m^2)$            |

| Occup (max/av)          | 0.7/0.3        | 0.2/0.1        | 0.0/0.0        | 0.0/0.0 | 0.0/0.0        |                       |

| Pitch (min/max)         | 90             | 90             | 90             | 90      | 90             |                       |

| Segments x Chips        | 48x8           | 48x8           | 48x8           | 48x8    | 48 <b>x</b> 8  |                       |

| Strip length            | 1.9            | 1.9            | 1.9            | 1.9     | 1.9            |                       |

| Chan/Sensor             | 49152          | 49152          | 49152          | 49152   | 49152          |                       |

| N. mod                  | 1400           | 3584           | 8512           | 1408    | 1920           | 16824                 |

| N. sens                 | 2800           | 7168           | 17024          | 2816    | 3840           | 33648                 |

| Channels (M)            |                |                |                |         |                | 0.00                  |

| Channels (M)            | 137.63         | 352.32         | 836.76         | 138.41  | 188.74         | 1653.87               |

| Power (kW)              | 13.8           | 35.2           | 83.7           | 13.8    | 18.9           | 165.4                 |

| Cost (MCHF)             | 48.1           | 123.0          | 292.1          | 48.3    | 65.9           | 577.4                 |

|                         |                |                |                |         |                |                       |

#### Cost estimates:

Pt modules: 200.0 CFH/cm2 - Strip modules: 40.0 CHF/cm2

#### Power estimates:

Pt modules: 0.10 mW/chan - Strip modules: 0.70 mW/chan