# Serial Powering System Architecture

Peter W Phillips

STFC Rutherford Appleton Laboratory

On behalf of the SP Community

Acknowledgement: many figures prepared by Richard Holt, RAL

# Outline

- SP Architecture: Modules and Staves

- System Tests

- Shunt Architectures

- Efficiency, DC-DC and 130nm

- SP and endcap geometries

- AC coupled (M)LVDS

- Serial Powering and HV

- Protection Schemes

- First Results from ABCN Integrated Shunts

- Summary and Next Steps

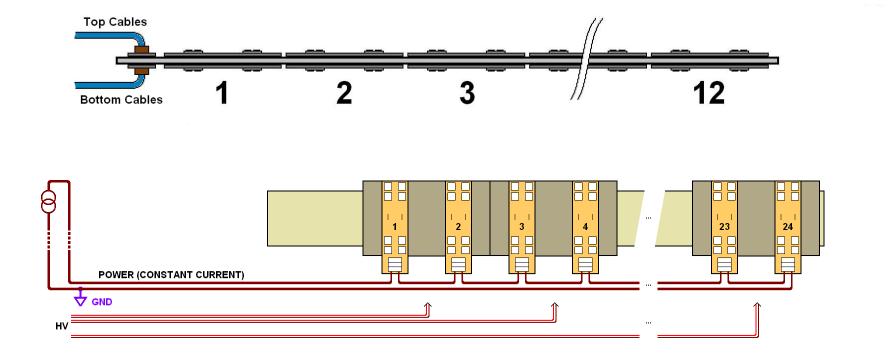

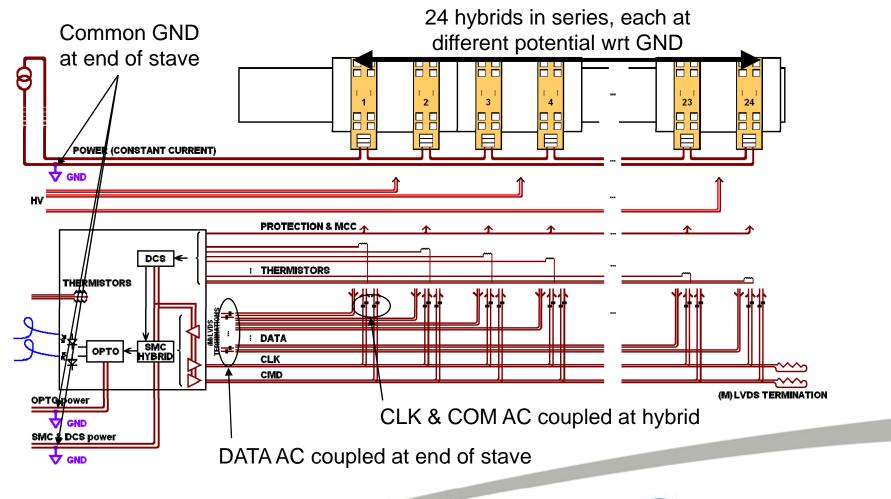

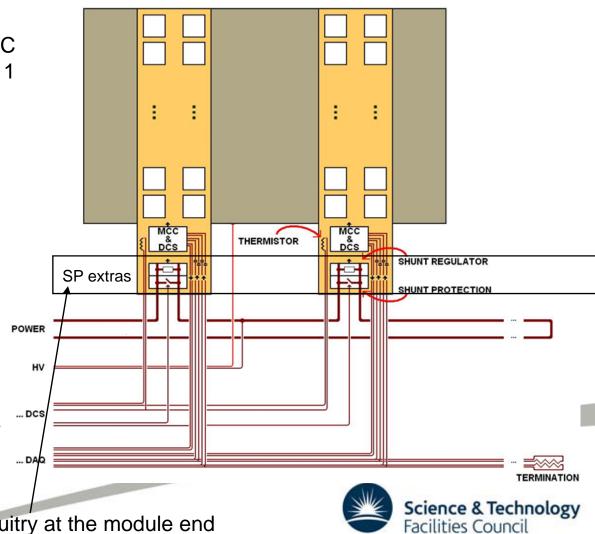

For strips, the stave comprises two separate planes:

- The top and bottom faces have separate current loops

- The grounds of the two faces are connected at the stave end

Features common with pixels:

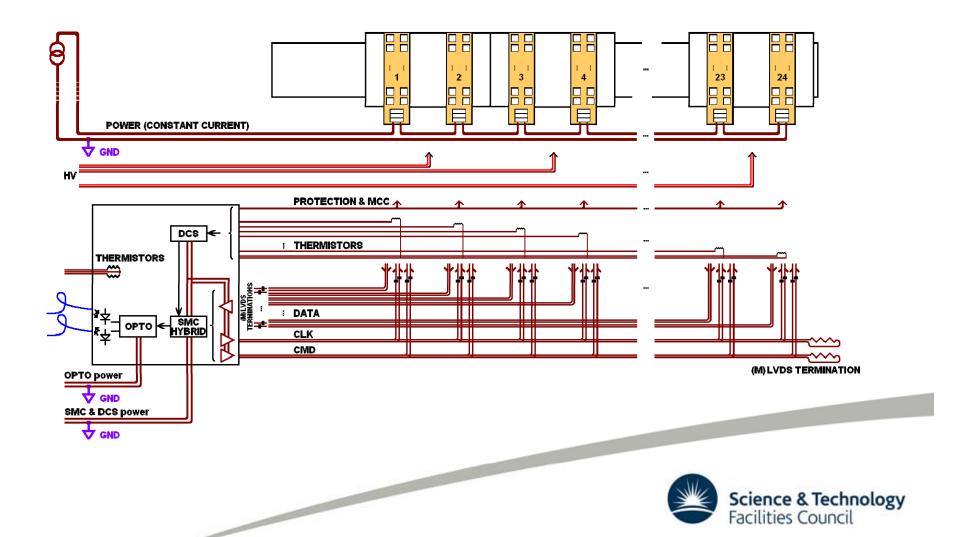

• CLK and COM are AC coupled on each hybrid

- DATA is AC coupled at the stave end

- Protection can be included such that one failed hybrid does not disturb the remainder

- DCS can monitor hybrid temperatures, the shunt current and (ideally) hybrid voltages

Depending upon design choices, the total voltage across each serial powering loop can be as low as 24 x 1V for strips, less for pixels (shorter stave)...

(DC-DC powered stave would look similar, apart from the absence of AC coupled IO)

# SP Module Architecture

#### Module Controller Chip (MCC)

- Functions common to SP & DC-DC

- multiplexes 2 data streams into 1

- voltage monitoring

- Additional for SP

- powered by SP

- AC coupling of CLK & COM

- Requires 4 capacitors

- Everything else on chip

#### Temperature

- read by (stave end) DCS

- Monitor T before power applied PO

#### Shunt protection

- under DCS control

- Turn on modules independently

7 SP requires minimal extra circuitry at the module end

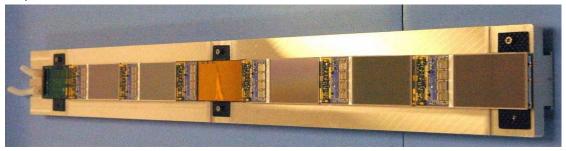

# System tests of SP staves

- 1) Pixel stave with FE-I3 (old, published)

- 2) Stave06: 6 module stave with ABCD

We have verified that:

- 1. Noise is not an issue

- 2. AC coupled (M)LVDS works

- 3. SP uses little extra real estate

- 4. Can use single HV line / strip stave

All staves working well!

30 \* 4V = 120V

(ABCD, 800nm)

(Future: 24 \* ~1V = 24V for 130nm ABCN)

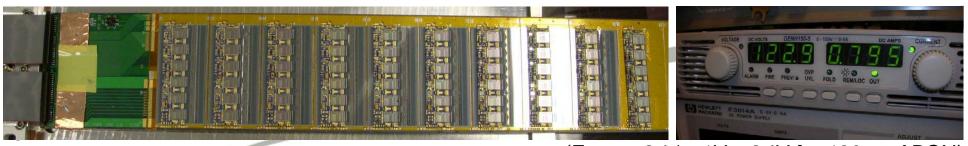

3) Stave07: 30 module stave with ABCD

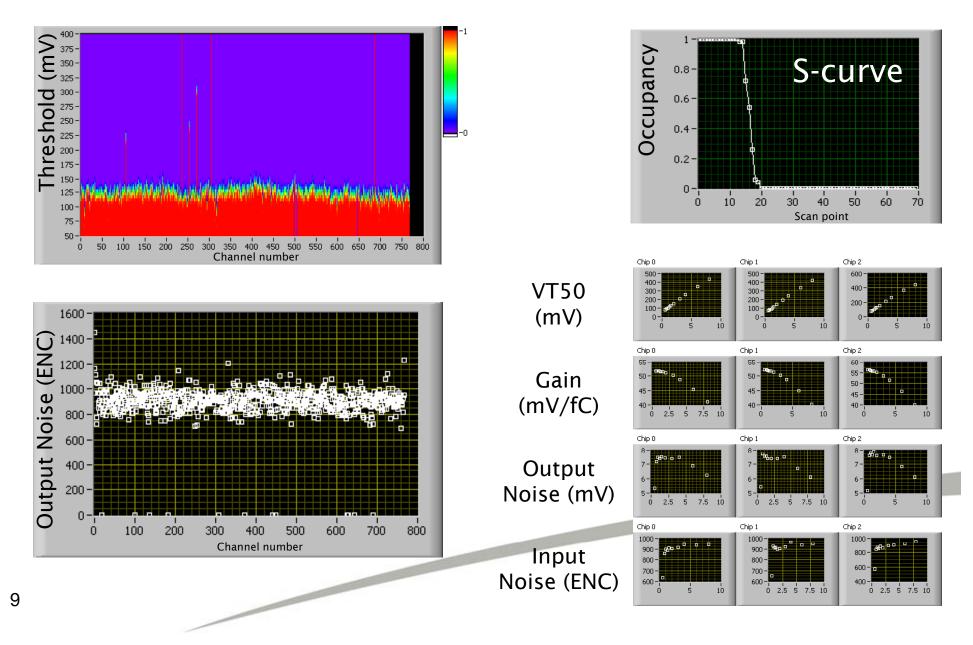

### Thirty Module Stave: Some Results

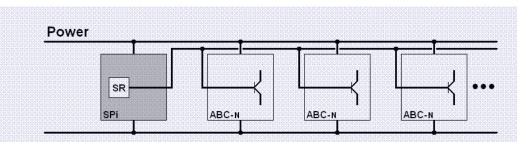

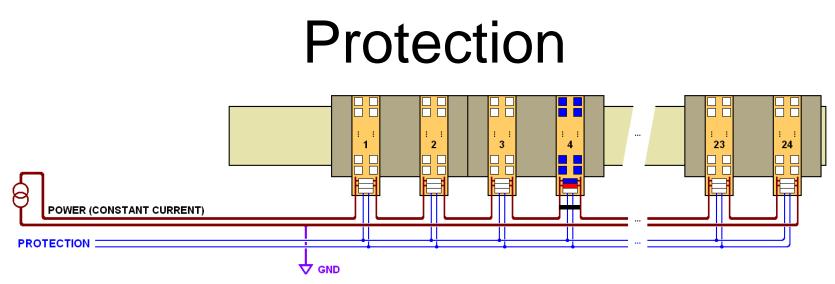

# Shunt Regulator Architectures

Power

Power

SR

SPi

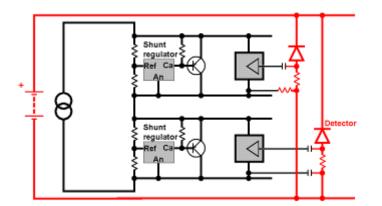

#### • Hybrid with Shunt "W"

- Use each ABCN's integrated shunt regulator

- Use each ABCN's integrated shunt transistor(s)

See "Serial power circuitry in the ABC-Next and FE-I4 chips" to be given this afternoon by W. Dabrowski

#### • Hybrid with Shunt "M"

- Use one external shunt regulator

- Use each ABCN's integrated shunt transistor(s)

- Two (redundant) shunt transistors, 140mA each

SR

ABC-N

ABC-N

SR

ABC-N

ABC-N

#### • Hybrid with SPi (or similar)

- Use one external shunt regulator

- Use one external power transistor

See "The Serial Power Interface Chip", to be given this afternoon by M. Trimpl

Each option has its merits. All now available in silicon: final choice to be based upon test results.

ABC-N

...

SR

ABC-N

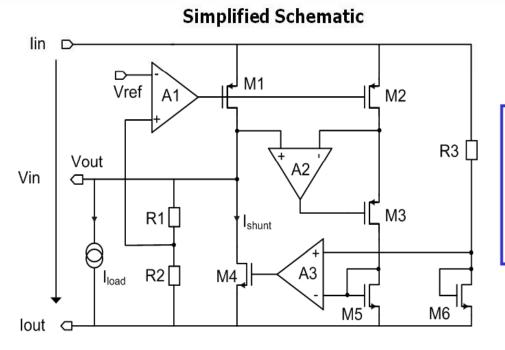

#### LDO Regulator with Shunt Transistor (ShuLDO)

- Combination of LDO and shunt transistor

- M4 shunts the current not drawn by the load

- Fraction of M1 current is mirrored & drained into M5

- Amplifier A2 & M3 improve mirroring accuracy

- Ref. current defined by resistor R3 & drained into M6

- Comparison of M5 and ref. current leads to constant current flow in M1

- Ref. current depends on voltage drop V<sub>lin</sub> which again depends on supply current Iin

- "Shunt-LDO" regulators having completely different output voltages can be placed in parallel without any problem regarding mismatch & shunt current distribution

- Resistor R3 mismatch will lead to some variation of shunt current (10-20%)

- "Shunt-LDO" can cope with an increased supply current if one FE-I4 does not contribute to shunt current e.g. disconnected wirebond → ref current goes up

- Can be used as an ordinary LDO when shunt is disabled

Slide 3

24.02.2009 Michael Karagounis – Power Distribution Working Group UNIVERSITAT

# Power Requirements with Modern Process Technologies

|                         |                                                                |                                     |                        |                                                              | Power per 128 channel chip                                         | per channel |

|-------------------------|----------------------------------------------------------------|-------------------------------------|------------------------|--------------------------------------------------------------|--------------------------------------------------------------------|-------------|

| In ATLAS SCT            | ABCD<br>(0.8μm, biCMOS)                                        | Digital:<br>Analogue:               | 4.0 volts<br>3.5 volts | 35 mA per chip (actual)<br>74 mA per chip (actual)           | => 4.0 x 35 + 3.5 x 74<br>= 399 mW                                 | 3.1 mW      |

| Present Prototype       | <b>АВСN25</b><br>(0.25µm CMOS)                                 | Digital:<br>Analogue:               | 2.5 volts<br>2.2 volts | 95 mA per chip (preliminary)<br>27 mA per chip (preliminary) | => 2.5 x 95 + 2.2 x 27<br>= 300 mW                                 | 2.3 mW      |

|                         |                                                                | Digital                             | 0.9 volts              | **51 mA per chip (estimate)                                  | => 0.9 x 51 + 1.2 x 16                                             |             |

| Proposed                | ABCN13<br>(0.13μm CMOS)                                        | Digital:<br>Analogue:               |                        | **16 mA per chip (estimate)                                  | = 65 mW                                                            | 0.5 mW      |

| Proposed<br>ABCN25: Vdi | (0.13µm CMOS)                                                  |                                     | 1.2 volts              |                                                              |                                                                    |             |

| ABCN25: Vdi             | (0.13µm CMOS)                                                  | Analogue:<br>dig >> la              | 1.2 volts              | **16 mA per chip (estimate)<br>ABCN13: Van                   |                                                                    | ana         |

| ABCN25: Vdi             | (0.13μm CMOS)<br>g > Vana I<br>e Vana from Vo                  | Analogue:<br>dig >> la<br>dig using | 1.2 volts              | **16 mA per chip (estimate)<br>ABCN13: Van<br>If we generate | ia > Vdig Idig >> I                                                | ana         |

| ABCN25: Vdig            | (0.13μm CMOS)<br>g > Vana I<br>e Vana from Vo<br>′ = 8.1mW per | Analogue:<br>dig >> la<br>dig using | 1.2 volts              | **16 mA per chip (estimate)<br>ABCN13: Van<br>If we generate | a > Vdig Idig >> I<br>e Vdig from Vana usin<br>′ = 28.5mW per chip | ana         |

http://indico.cern.ch/getFile.py/access?contrible=16&sessionId=8&resId=0&materialId=slides&confld=32084

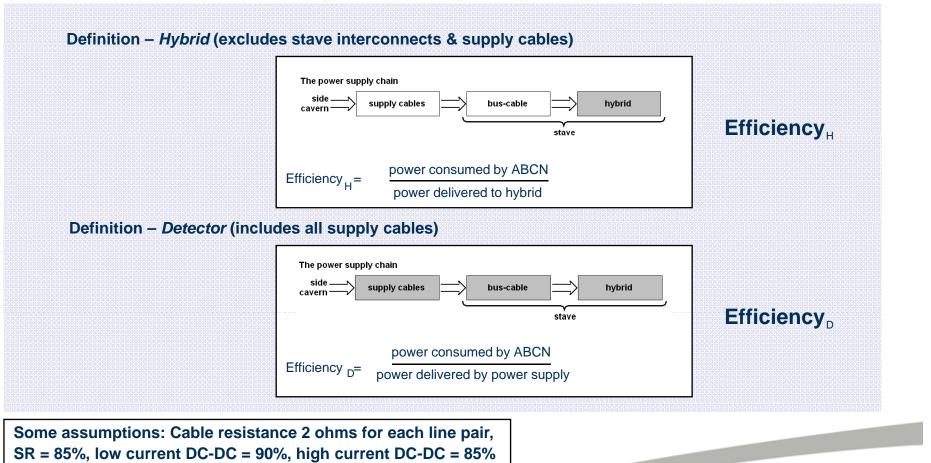

## Efficiency - definitions

ABCN demand power is dependant on task. This

will normally mean a shunt regulator will dissipate some power to maintain voltage under all conditions.

### **Favoured SP Options**

For further details, see this afternoon's presentation by W. Dabrowski: "Serial power circuitry in the ABC-Next and FE-I4 chips"

### **Favoured SP Options**

For further details, see this afternoon's presentation by W. Dabrowski: "Serial power circuitry in the ABC-Next and FE-I4 chips"

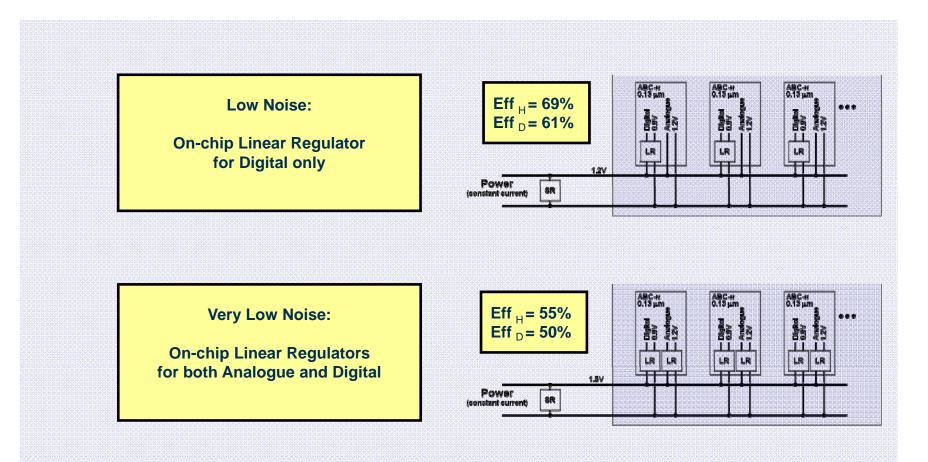

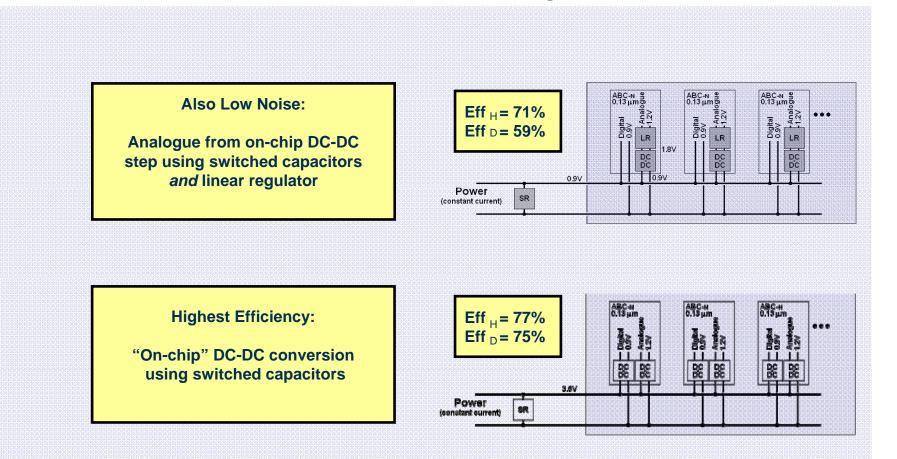

### For the sake of Comparison...

With ABCN in 130 nm technology, we shall study several options to obtain the best balance between efficiency and performance...

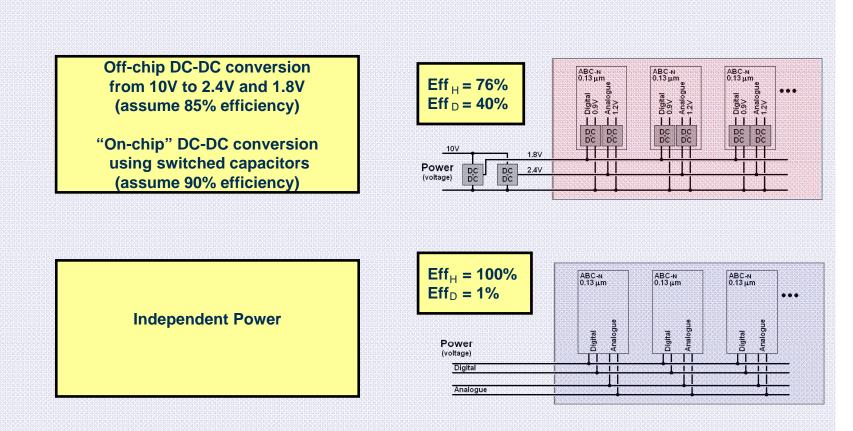

# SP and Endcap Geometries

- The baseline design for the endcap of an upgraded ATLAS strip detector is based around petals.

- Not all hybrids have the same number of chips

- Group hybrids with *similar* numbers of chips into their own power chains

- Chain 1: (3\*16) chip units

- Chain 2: (4\*12)+(2\*10) chip units

- Additional current corresponding to two chips must be dissipated by the shunt(s) on each 10 chip hybrid.

- Efficiency depends upon the values of the analogue and digital voltages and the means used to generate them:

- Example: 3 ohm cable pair, 1.5V supply, 140mA per chip and 85% shunt efficiency => 54% efficiency

- GOOD ENOUGH

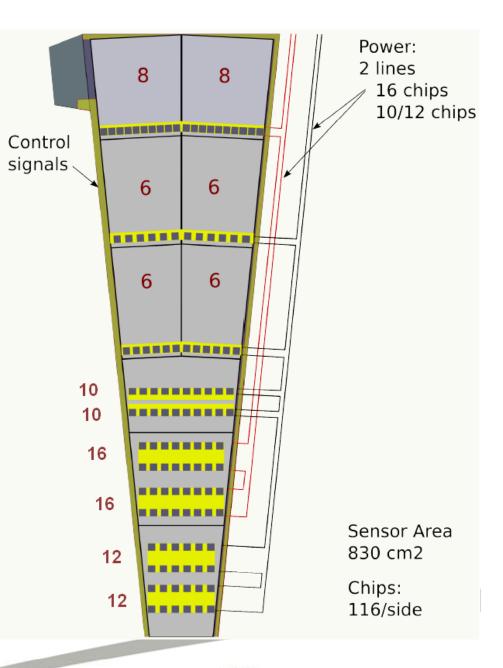

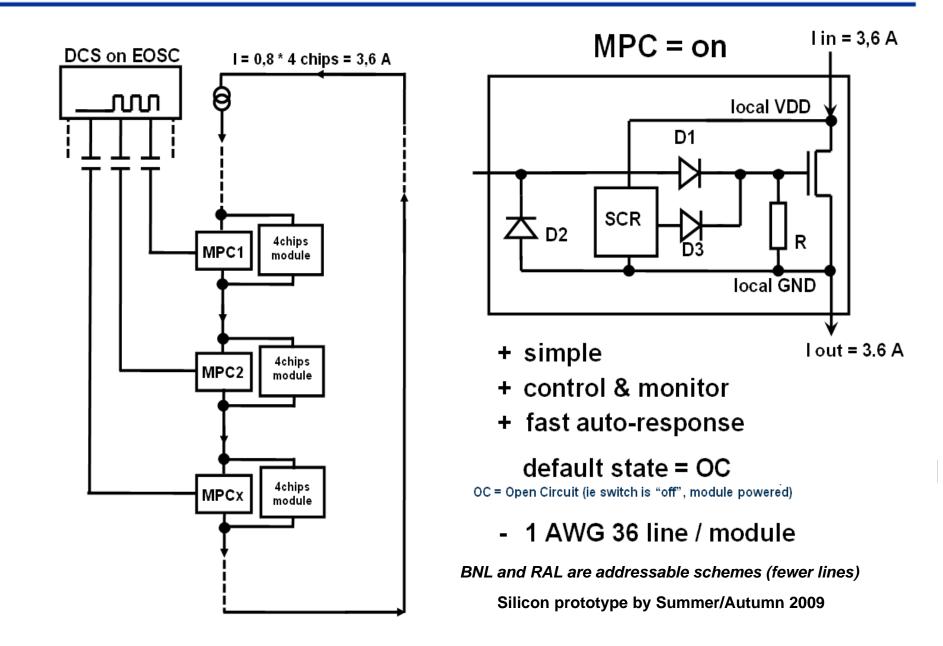

Whilst demonstration staves have generally been reliable:

- What happens if a module fails open circuit?

- What happens if a module becomes a noise generator?

We could provide a system to "short out" each module under control of DCS

- Voltage across shorted module should be small (<100mV)

- Area of components and number of control lines must be small

- Automatic over current and over voltage protection is desirable

- Protection circuit must draw no (minimal) power when module active

- Ability to put modules into "stand by" (low power state)

See poster by Richard Holt for details of proposals by Bonn, BNL and RAL

#### Bonn Scheme: Module Protection Chip

"Serial Powering Protection", Andreas Eyring, ATLAS Upgrade Week, CERN, Feb 2008 http://indico.cern.ch/materialDisplay.py?contribId=4&materialId=slides&confId=52375

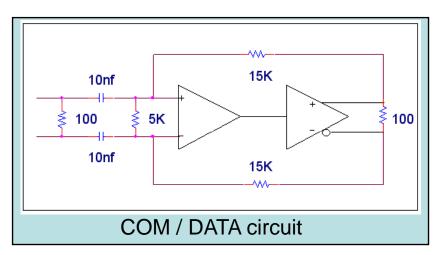

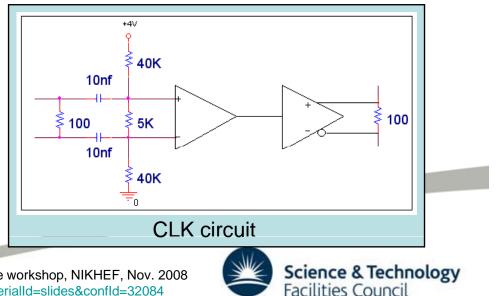

# AC Coupled (M)LVDS Receivers

#### A viable solution!

- No need for DC balanced codes

- COM/DATA circuit could be simplified if DC balanced codes were used (DC balanced remains the baseline for production staves)

- All components apart from the capacitors can be integrated into custom chips

- Capacitors need to be rated to ~30V, more for present prototypes

- MLVDS drivers offers higher currents and MLVDS receivers lower thresholds (than LVDS)

- Can help increase margins

- Working well on STAVE07

See "AC Coupled LVDS drivers", Dave Nelson, ATLAS Tracker Upgrade workshop, NIKHEF, Nov. 2008 <u>http://indico.cern.ch/materialDisplay.py?contribId=19&sessionId=8&materialId=slides&confId=32084</u>

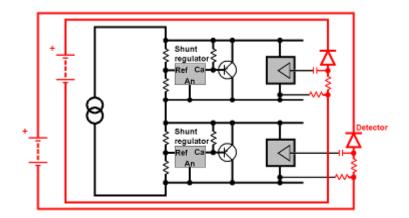

# Serial Powering and HV

Standard HV powering: one HV per module

Alternative HV powering: one HV supply per M modules

- Serial Powering is compatible with the use of a single HV supply for several modules

- Each sensor is dynamically connected to current source ground through output impedances of the chain of shunt regulators

- Low shunt output impedance is crucial to achieve good 'grounding' and reduce noise

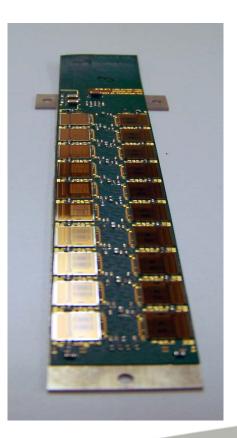

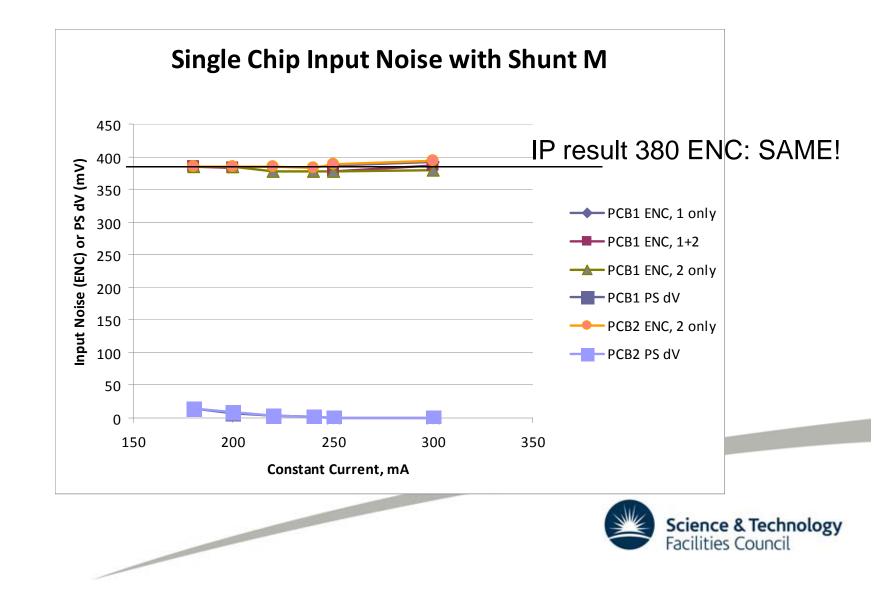

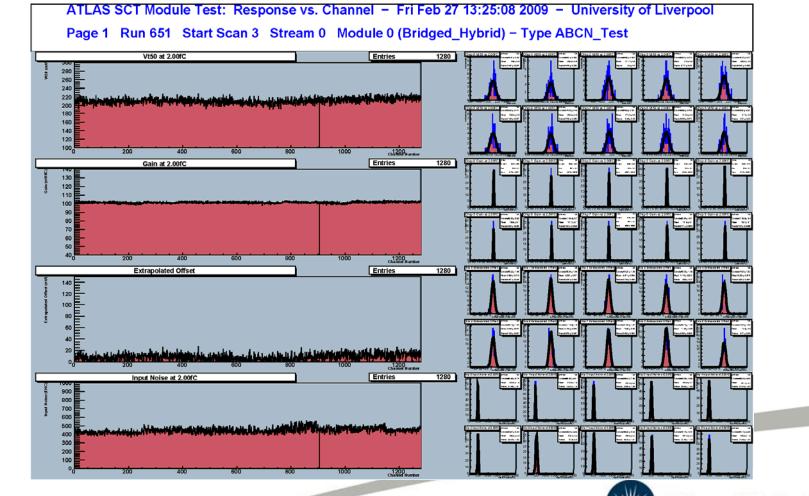

### First tests of integrated shunts in ABCN: RAL single chip PCB and Liverpool Hybrid

# Single Chip using shunt "M"

# ABCN hybrid using shunt "W"

**PRELIMINARY**

Science & Technology Facilities Council

# SP Summary and Next Steps

- We have ~2 years successful experience building and running staves with commercial SP components

- Shunt circuitry can be integrated into FE chips

- Low requirements in terms of component area

- First results from ABCN shunts very encouraging

- Protection can be part of SP architecture

- Basic scheme demonstrated

- First ABCN demonstrator stave planned for this year

- Integrated shunts + protection

- SP is an attractive option for sLHC power distribution!

# **Supplemental Material**

# Large Diameter Wire Bonds

Delvotec 64/66000 100 – 600 micron wire

Used in harsh automotive applications, e.g. ABS Shear strength for 250 micron bond 1000cN 250 micron bond => 15 A Manufacturers can do test samples

Hesse + Knipps Bondjet BJ920 125 – 500 micron wire

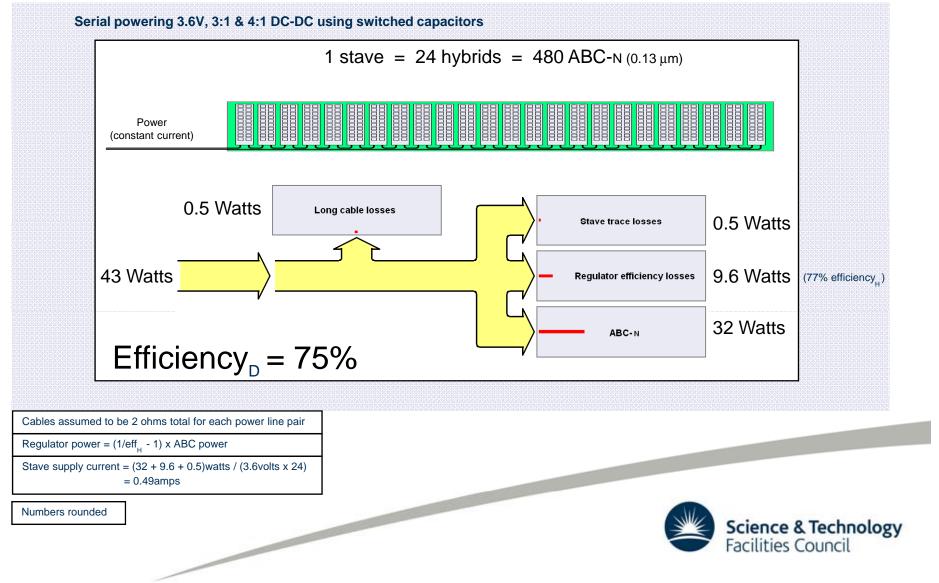

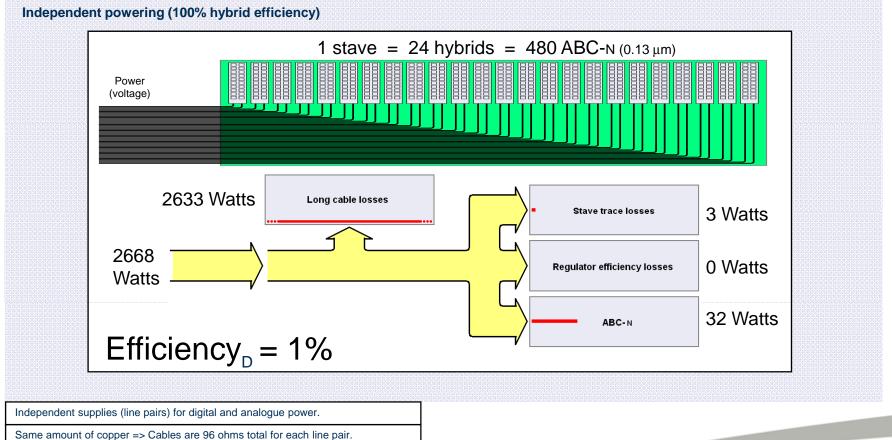

### **Detector power efficiency**

Each line pair carries 20 x 51mA (digital) and 20 x 16mA (analogue).

Numbers rounded

### Detector power efficiency