# **Serial power circuitry in the ABC-Next and FE-I4 chips**

#### W. Dabrowski

Faculty of Physics and Applied Computer Science AGH – University of Science and Technology Krakow

including material from Michael Karagounis on development at Bonn University

# How the serial powering started

#### Serial powering of pixel modules

#### Tobias Stockmanns<sup>a,\*</sup>, Peter Fischer<sup>b</sup>, Fabian Hügging<sup>a</sup>, Ivan Peric<sup>a</sup>, Ögmundur Runolfsson<sup>a</sup>, Norbert Wermes<sup>a</sup>

<sup>a</sup> Physikalisches Institut der Universität Bonn, Nussallee 12, D-53115 Bonn, Germany <sup>b</sup> Insitut für Technische Informatik, Universität Mannheim, D7, 2-4, 68131 Mannheim, Germany

Power dissipated in the shunt regulators is distributed uniformly across the hybrid.

No very high current devices required.

Single point of failure reduced compared to one regulator per hybrid.

Hybrid design fully scaleable with respect to power distribution.

but .....

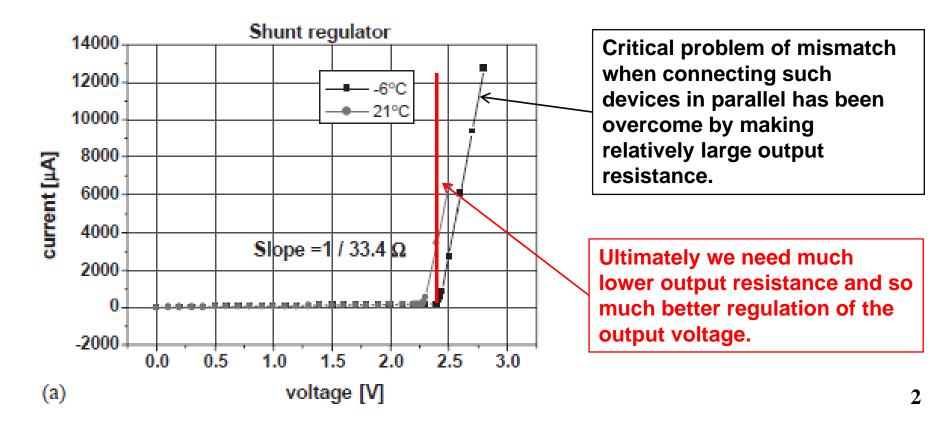

Matching becomes critical when making the shunt regulators of low output resistance.

New shunt regulator circuits suitable for integration in the readout chips have been developed independently for the strip readout and the pixel readout.

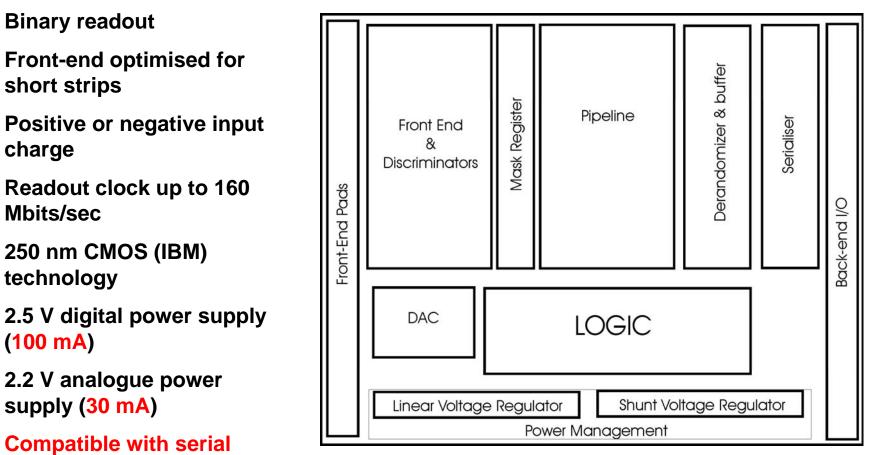

# Serial powering in strip readout

#### Prototype chip for Si strip readout in Upgrade Inner Tracker

powering scheme

#### **Two optional shunt regulators**

- A. Full shunt regulator in each ABCN chip

- B. Shunt transistor in each ABCN and regulation circuitry external common for all chips on the moule

#### Serial voltage regulator (optional)

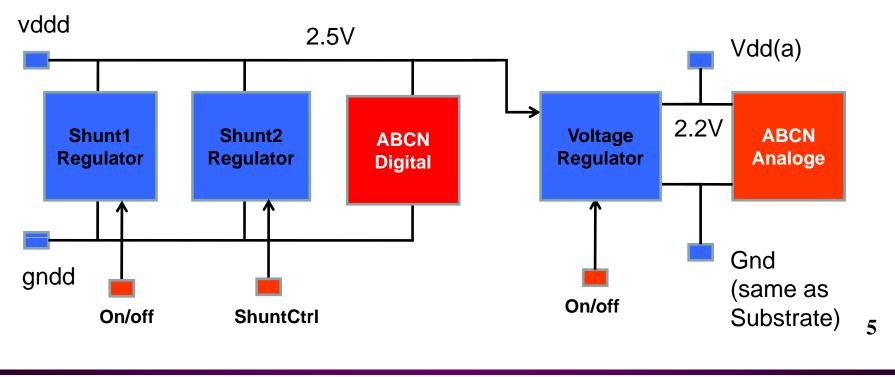

#### Nominal powering-up scenario

Supply current ramped up to the nominal required value with clock signal active in the digital part – digital switching current increase smoothly following the I-V characteristic of the digital load.

**Critical scenarios**

Clock signal is delayed with respect the power start-up – supply current forced by external current supply may temporarly go much above the ABCN current consumption.

Clock signal lost suddenly during normal operation – digital current consumption suddenly reduced.

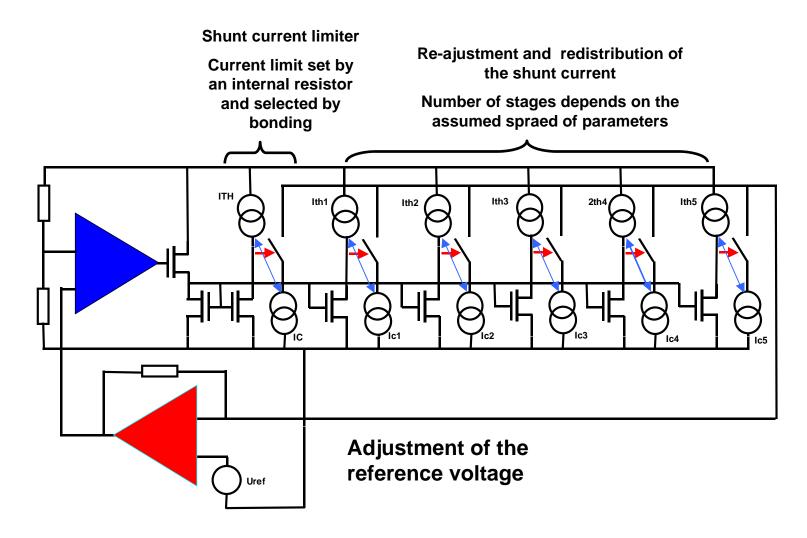

# Full shunt regulator on chip - design concept

## **Matching problem (simulation)**

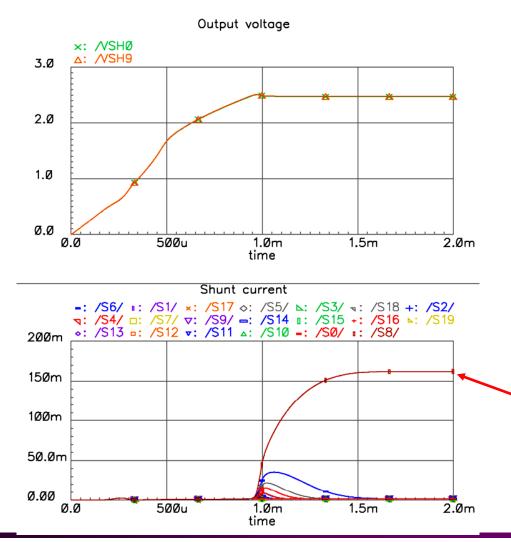

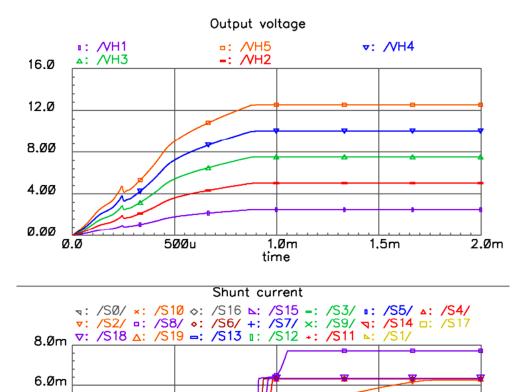

#### Clock is ON all the time

20 ABCNs with internal shunt regulators connected in parallel.

All mismatch effects represented by mismatch of reference voltages.

Flat distribution in a range -10 mV to +10 mV assumed.

Average shunt current of 8 mA per device.

#### One shunt device always wins

This would happen even if we assumed perfect matching because of the voltage drops along **8** the power busses on the hybrid.

## **Matching problem (simulation)**

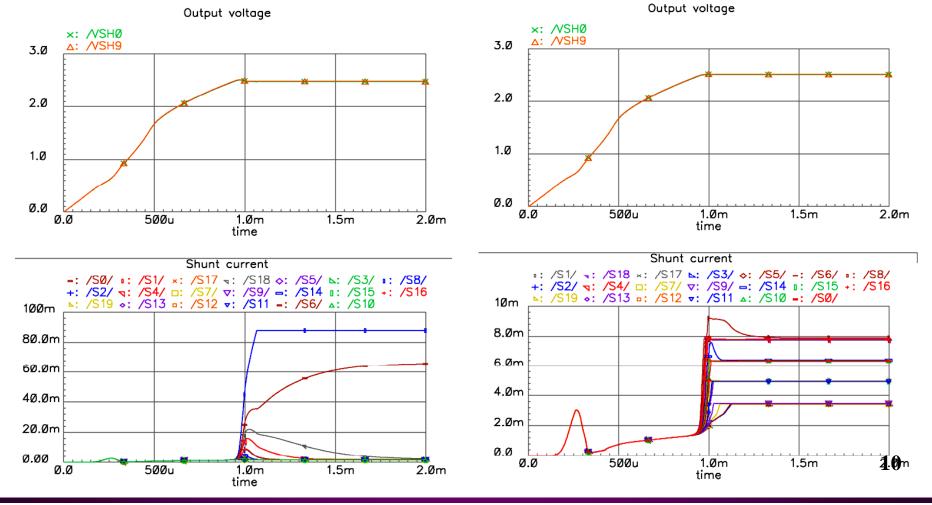

**Clock delayed Clock OFF during operation** Output voltage Outout voltage x: /VSHØ ×: /VSHØ A: /VSH9 ∆: ∕VSH9 3.Ø 3.Ø 2.Ø 2.Ø 1.Ø 1.Ø Ø.Ø Ø.Ø 500u Ø.Ø 1.Øm 1.5m 2.Øm ø.ø 1.5m 5ØØu 1.Øm 2.Øm time time Shunt current Shunt current ": /S1/ ¬: /S18 ◊: /S5/ ▷: /S3/ ×: /S17 -: /S6/ □: /S15

`: /S19 □: /S12 ◊: /S13 ⊽: /S9/ Δ: /S10 ⊽: /S11 □: /S7/ 1: /S1/ ¬: /S18 ×: /S17 ⊾: /S3/ ◊: /S5/ -: /S6/ +: /S2/ ¬: /S4/ □: /S7/ ⊽: /S9/ =: /S14 □: /S15 +: /S16 ⊾: /S19 >: /S13 □: /S12 ⊽: /S11 Δ: /S10 =: /S0/ □: /S8/ -: /SØ/ =: /S14 +: /S2/ +: /S16 v: /S4/ 1: /S8/ 1.2 6ØØm 900m **Clock ON Clock OFF** 400m 6ØØm 300m 200m Ø.Ø 500u 1.Øm Ø.Ø 1.5m 2.Øm Ø.ØØ time 5ØØu 1.Øm 1.5m 2.Øm 9 Ø.Ø time

ACES Workshop

W. Dabrowski

### **Performance of the auxiliary circuits (simulation)**

#### Clock is ON all the time

#### **Only current limiter active**

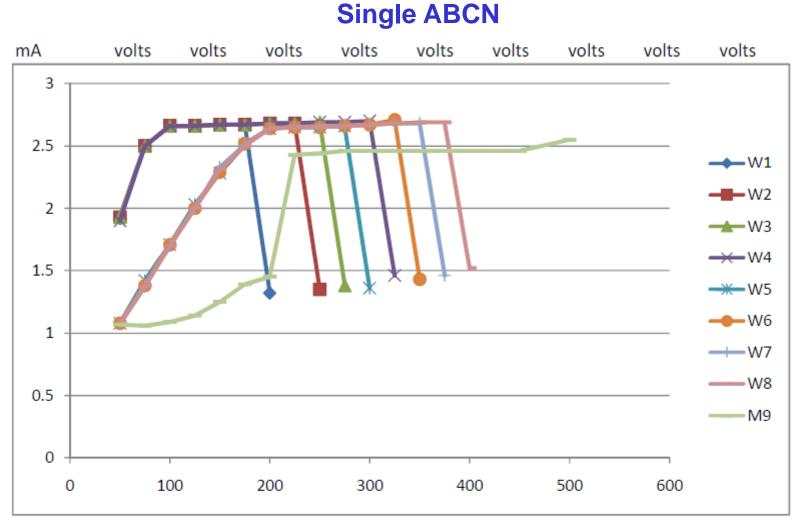

**Performance of the current limiter (measurements)**

11

AGH

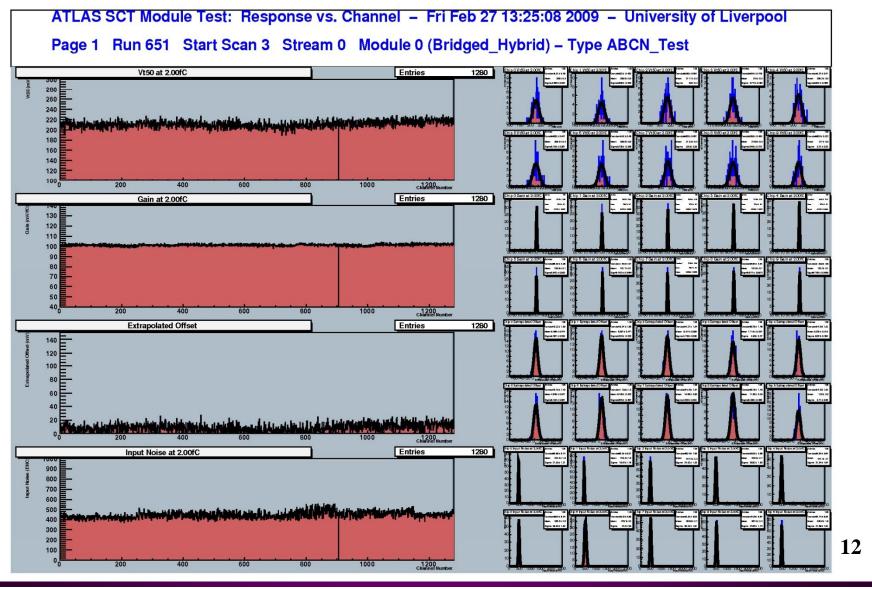

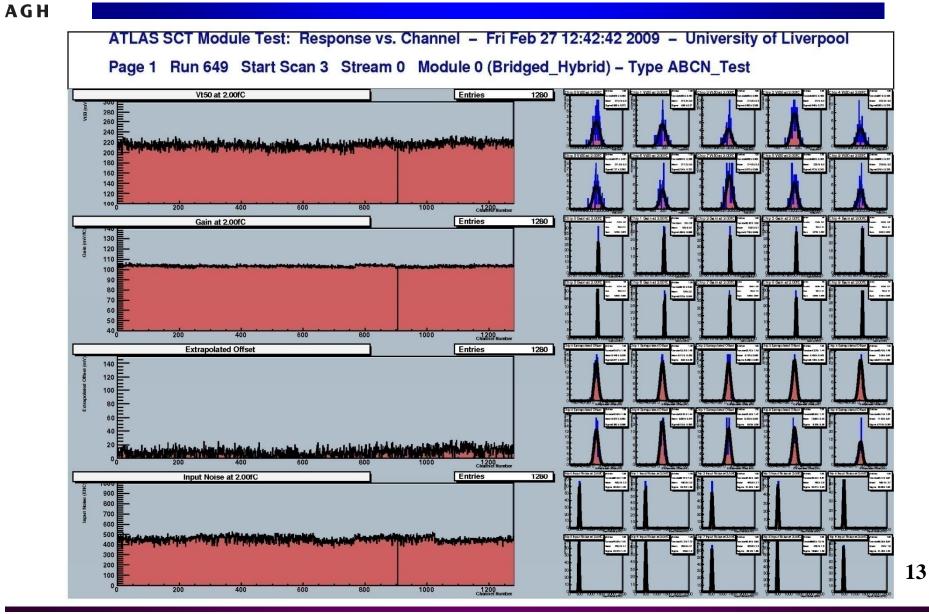

## 20 chips hybrid – powered conventionally

# **20 chips hybrid – powered through internal shunts**

#### **Design assumptions**

#### Estimate of power in ABCN130n by Mitch Newcomer

| 130 nm Estimate<br>128 Channels / chip           | Supply      | Short Strip<br>Power, Current | Long Strip<br>Power, current |

|--------------------------------------------------|-------------|-------------------------------|------------------------------|

| Analog                                           | VDDA @ 1.2V | 20 mW, 16mA                   | 39 mW, 32mA                  |

| Digital Supply                                   | VDD @ 0.9V  | 46 mW, 51mA                   | 46 mW, 51mA                  |

| Total Power <sup>*</sup> / Chip (ref ABCn 290mW) |             | 66 mW                         | 85 mW                        |

| Total Power * / 20 Chip Module                   |             | 1.3 W                         | 1.7 W                        |

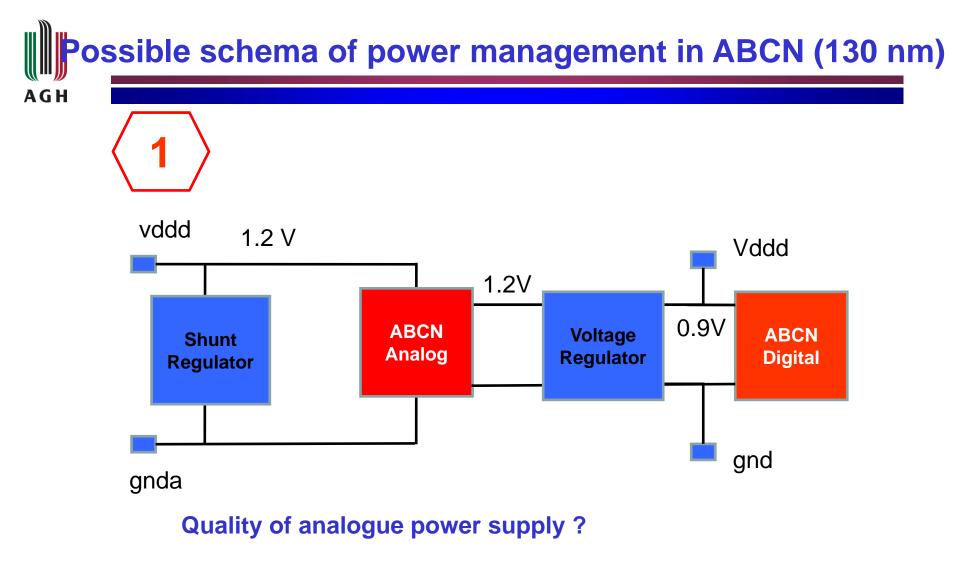

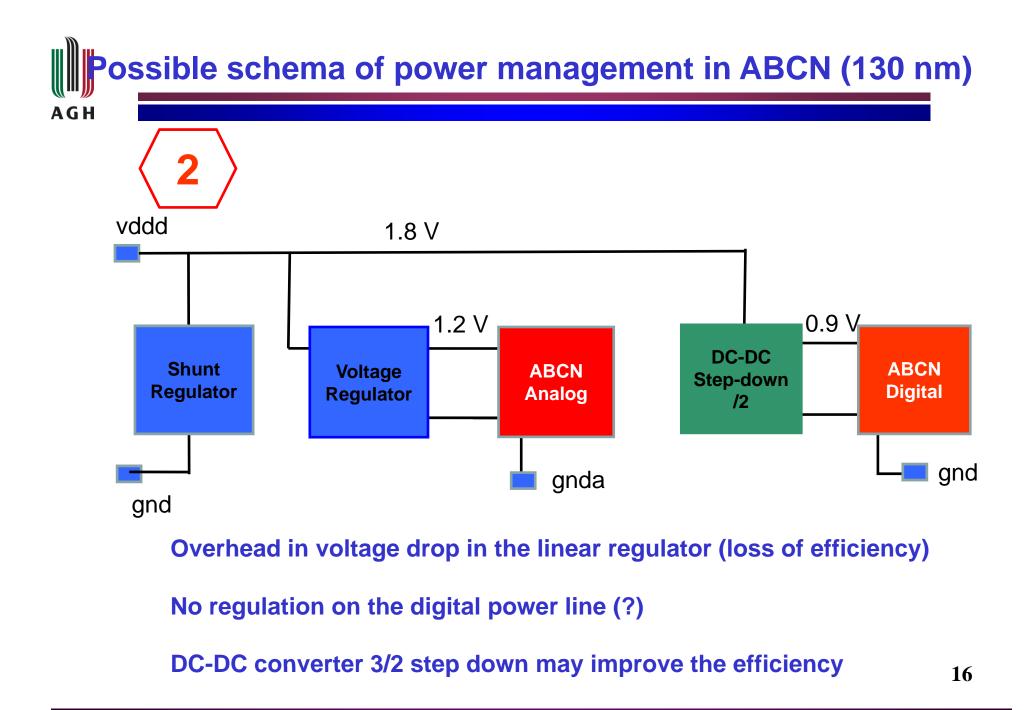

Power supply voltages are not compatible with the power management schema implemented in ABCN (250 nm) assuming serial powering.

14

Some saving of digital power due to lower voltage swing

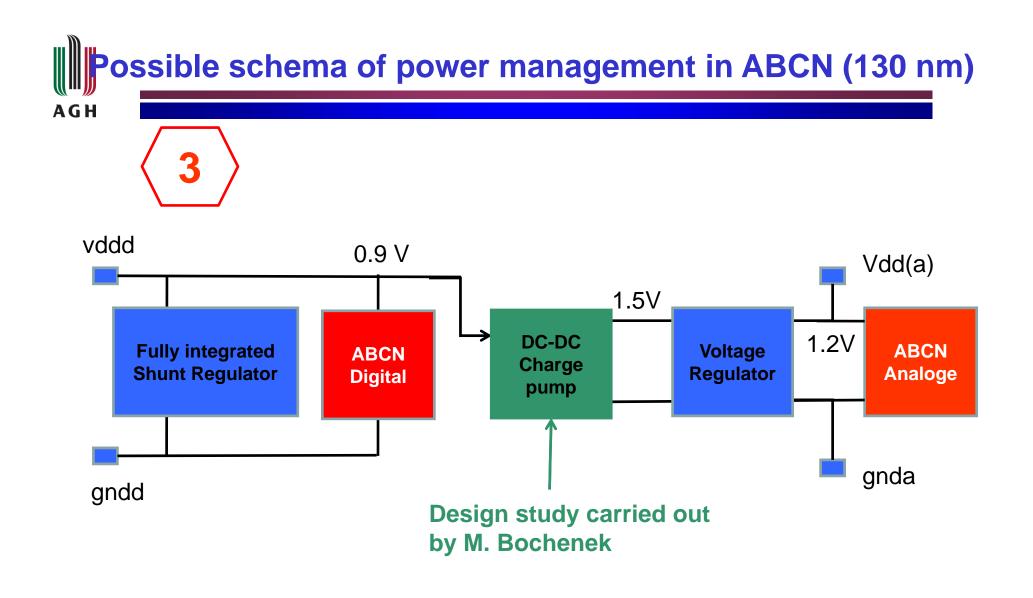

#### Possibly most efficient system compatible with serial powering

17

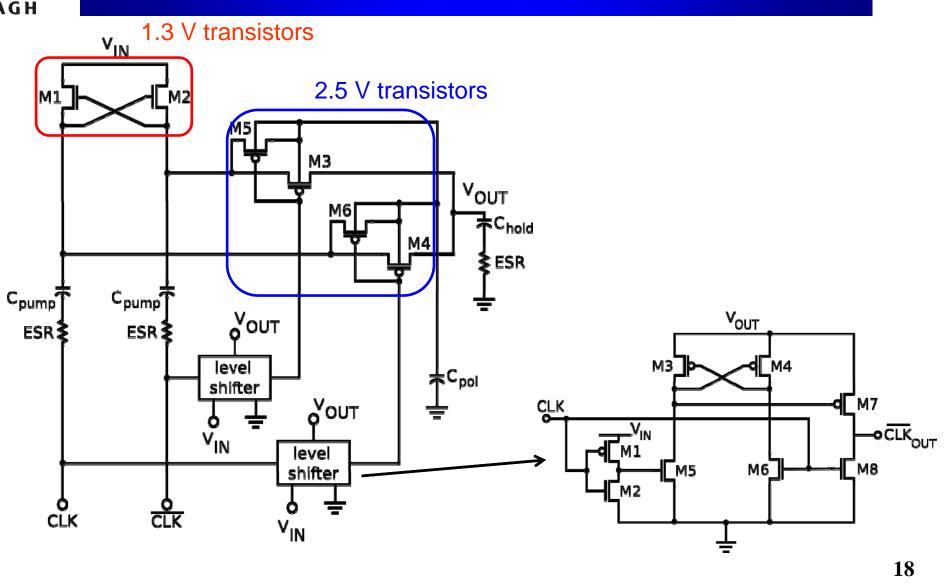

### Charge pump – design study

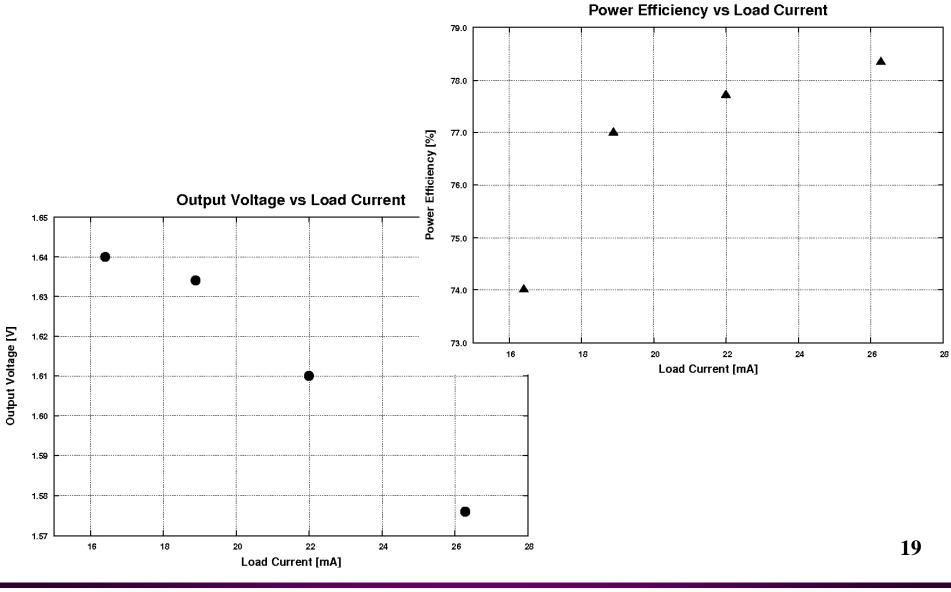

## **Charge pump – performance (preliminary)**

**ACES Workshop**

AGH

Further optimisation of the charge pump – there is a number of details to be optimised in the design (switching transistors, buffers, level shifter ....

Implementation of the fully integrated shunt design from ABCN (250nm) in the 130 nm technology.

Implementation of the serial regulator in 130 nm.

Integration of a complete power management block to be included on the front-end prototype chip.

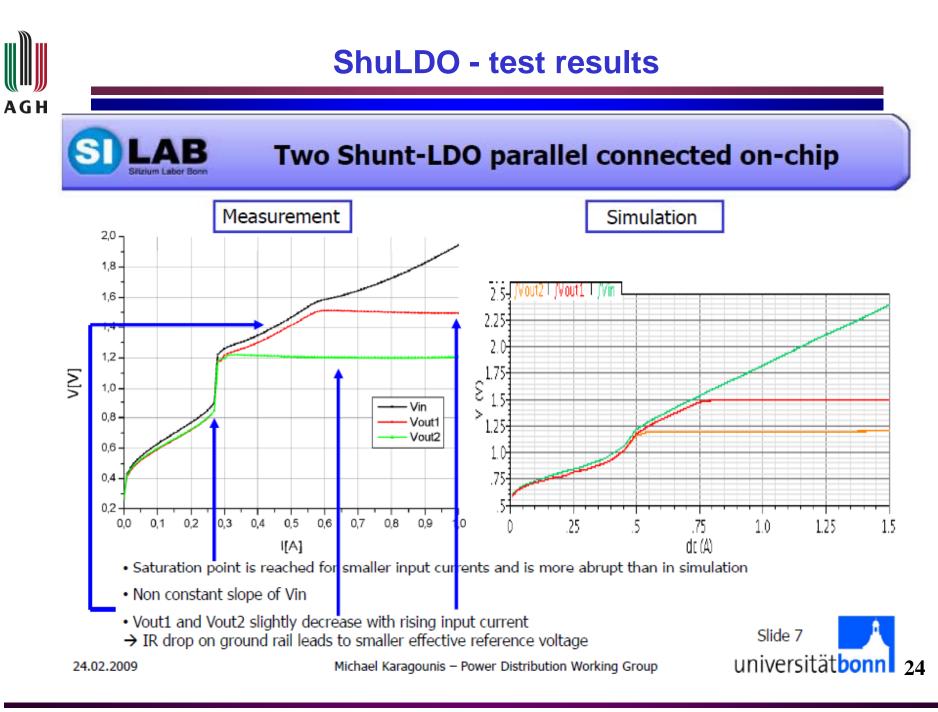

#### New shunt for pixel readout (ShuLDO) AGH New Shunt Concept Basic Ideas lin R<sub>slope</sub> Vout 7in Vref M R1 [] Vref Мı R<sub>load</sub> O Vout supply R<sub>1</sub> R<sub>2</sub> $R_2$ lout New Concept is based on two ideas: 1. The added resistor Rslope does not contribute to the regulation and burns additional power Why not replacing the added constant resistor by a regulated "resistor" of variable size 2. Very likely the shunt regulator will be used in combination with a linear regulator placed at the output of the shunt regulator Why not changing the order and placing the LDO before the shunt regulator The PMOS power transistor of the LDO becomes the variable regulated "resistor" The shunt transistor becomes part of the load of the LDO Slide 3 universitätbonn 21 Michael Karagounis - Power Distribution Working Group Meeting 01.07.2008

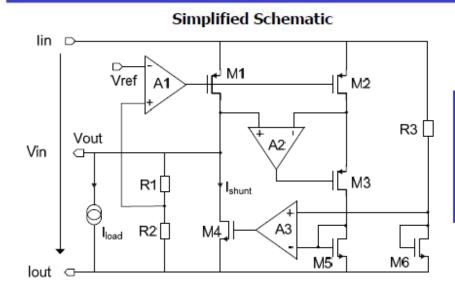

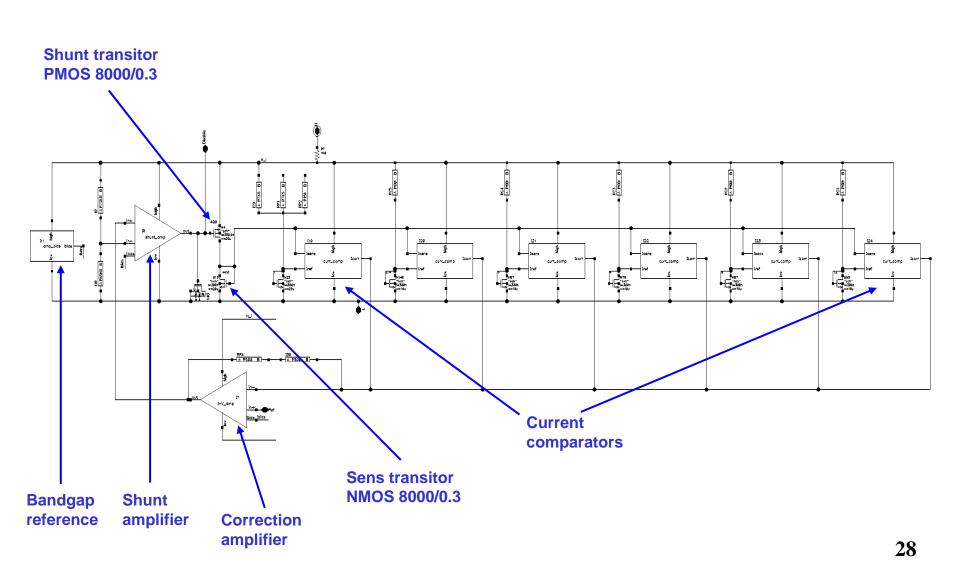

## **ShuLDO - implementation**

LDO Regulator with Shunt Transistor (ShuLDO)

- Combination of LDO and shunt transistor

- M4 shunts the current not drawn by the load

- Fraction of M1 current is mirrored & drained into M5

- Amplifier A2 & M3 improve mirroring accuracy

- Ref. current defined by resistor R3 & drained into M6

- Comparison of M5 and ref. current leads to constant current flow in M1

Ref. current depends on voltage drop V<sub>Iin</sub> which again depends on supply current Iin

- "Shunt-LDO" regulators having completely different output voltages can be placed in parallel without any

problem regarding mismatch & shunt current distribution

- Resistor R3 mismatch will lead to some variation of shunt current (10-20%)

- "Shunt-LDO" can cope with an increased supply current if one FE-I4 does not contribute to shunt current e.g. disconnected wirebond → ref current goes up

- · Can be used as an ordinary LDO when shunt is disabled

Slide 3 universitätbonn 22

24.02.2009

Michael Karagounis - Power Distribution Working Group

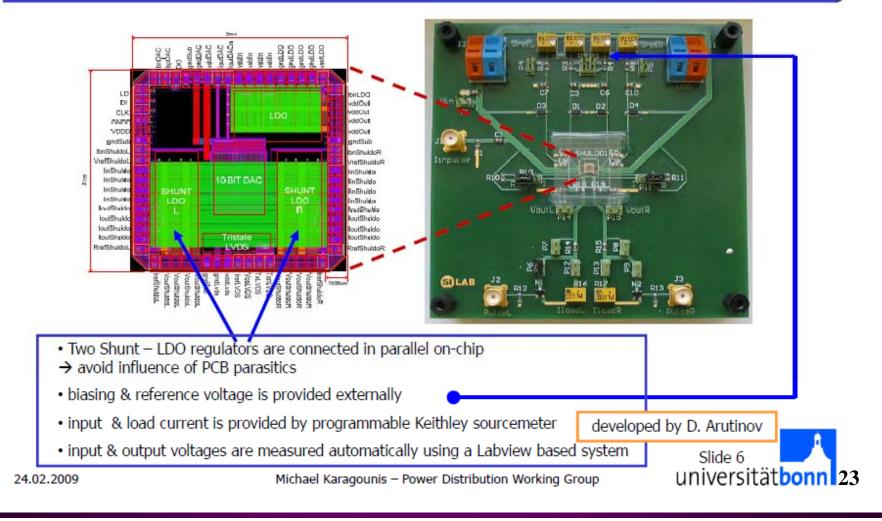

### **ShuLDO - implementation**

**Setup for Test Measurements**

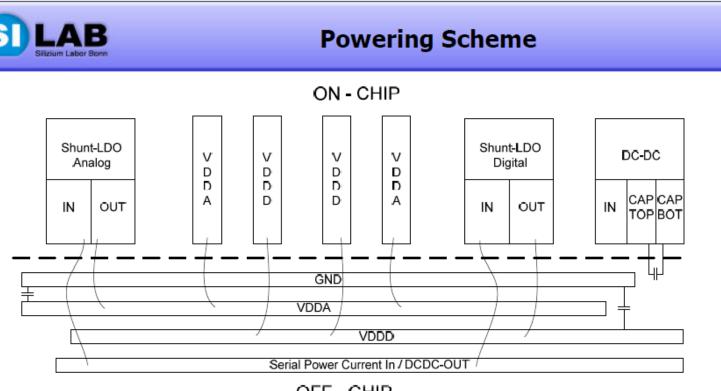

## Serial powering in pixel readout – development plan

OFF - CHIP

flexible powering scheme  $\rightarrow$  defined by bonding & external wiring

- Serial Powering: constant current fed into two ShuLDOs

- DCDC Powering: DCDC output voltage fed either directly or via LDO regulators to the core

02.03.2009

universität**bonn**

25

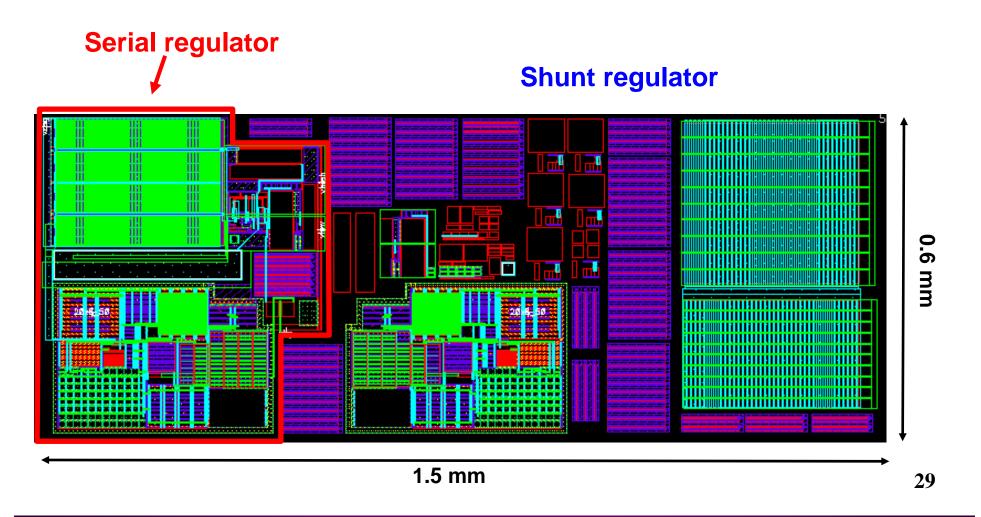

Much progress has been made on understanding and development of the serial powering for both, the strip readout and the pixel readout.

Fully integrated shunt regulator has been implemented in the ABC Next (250 nm) – it will allow building a large scale demonstrattor object with serial powering.

A new shunt regulator design has been proposed and prototype successfully for the pixel readout.

Optimising power efficiency may require combining serial powering with DC-DC on-chip conversion.

Implementation of serial powering must be readout architecture and technology specific.

26

# **Back-up slides**

#### Implementation

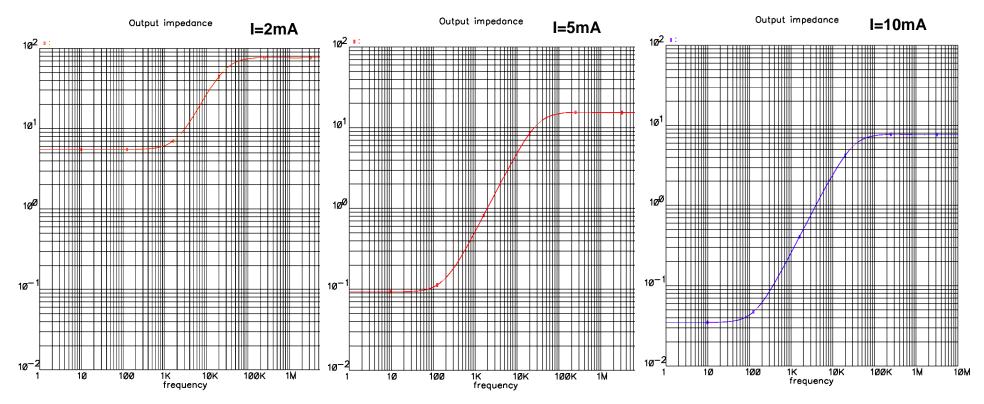

## **Ouput impedance - single shunt regulator**

#### Shunt curent of 5 to 10 mA will be required

For a hybrid with 20 ABCNs the effective output impedance will be about 20 times smaller

30

#### 5 modules (20 ABCNs each) in series

1.Øm

time

1.5m

How do we set and control the supply current?

The digital current may vary substantially with occupancy (noise scan) and process variation

An "ideal" solution: the supply current of a super module is controlled based on the voltage sensing and voltage regulation at the super module input only, e.g. for 5 modules: 5x2.5V

Implications for the overll powering system needs to be understood better

31

**ACES Workshop**

5ØØu

4.Øm

2.Øm

Ø.Ø

Ø.Ø

2.Øm