# Operational tools

Laurette Ponce BE-OP

#### Context

- After the 19<sup>th</sup> September, a re-enforcement of access control during powering tests was requested

- Access system designed to cope with radiation hazard ONLY, not electrical or cryogenic risks

- Not possible to implement a "hardware" link between access system and converters during this shutdown)

- For personnel safety, 2 powering phases have been defined, with different access restrictions AND hardware/software limitations of the current

- In addition of these measures and the procedure, a SOFTWARE interlock has been implemented

## **Outlines**

- Hardware and software limits

- Software interlock

- Principle of the interlock

- The tools used to build the logic

- Consequences for PO

- How to switch from PO phase 1 to PO phase 2

## Hardware and software limits

- To guarantee the safety of personnel during powering phase 1, current has to be limited in the main magnets as proposed to the safety Task-force (EDMS 1001985):

- RB 100A

- RQF/RQD 800A

- RQ4-RQ10 900A

- IPD 1000A

- RQX 800A

- RQTX2 600A

- RQTX1 132A

- 2 types of limitation on PC side:

- For RB, RQF and RQD: hardware limits in the power converter

- For IPQ, IPD : FGC software limits

- Another software limits in the operational database:

- Redefinition of I\_max in LSA

- This is the max current used by the sequencer

## Additional tools for OP

- A software interlock for checking access conditions versus current in the magnets

- Proposal for 2 fixed displays

- The software interlock is based on several different softwares to build the signals needed for the logic : more details in the following slides

- The main components are the LHC Software Interlock System, the LHC Access Control System and TIM (TI supervision tool)

# Principle of the interlock

- The principle is to stop <u>all the power converters of a sector</u> in case the current level in one of them is not compatible with the actual access conditions in the sector:

- to prevent powering above the defined level during powering phase 1

- to stop the powering above so called "safe current level" in case of intrusion during powering phase 2

- The Interlock is on the PCs, not on the access system:

- The access conditions (which zones are patrolled and empty) define the level of current allowed in the whole sector

- No action on the access system, just reading of the status

## The logic

```

Access OK for PO PHASE 2 = true

OR

POWERING permit = true

OR

PC in simulation mode = true

```

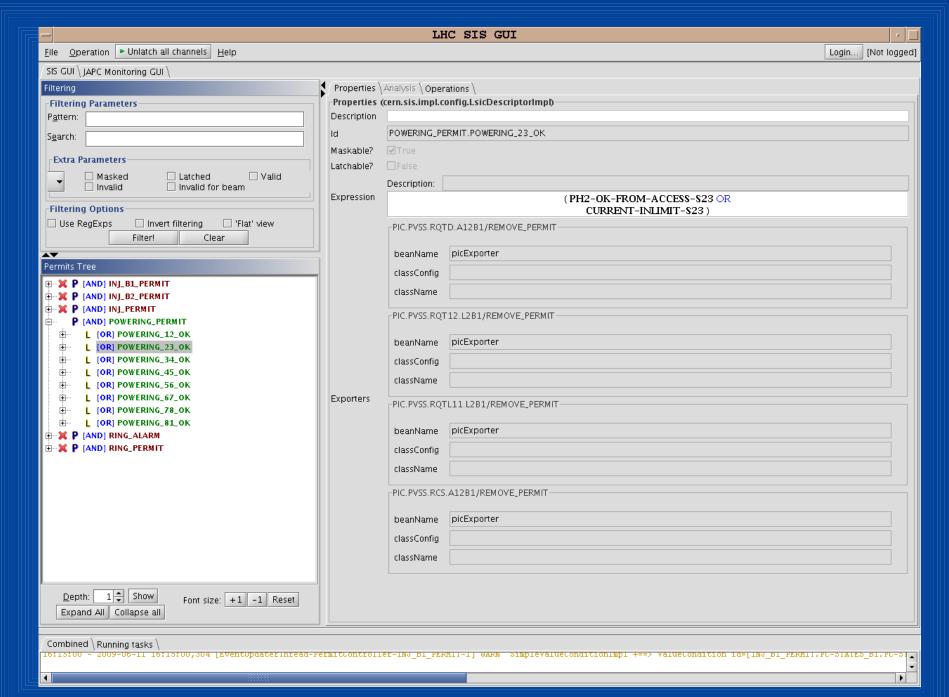

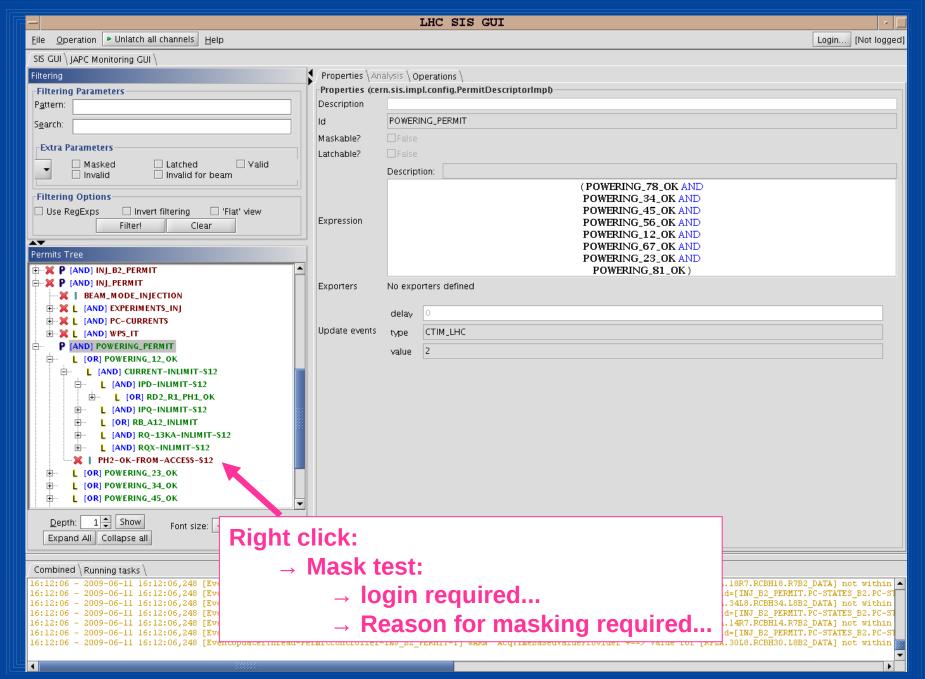

- The logic is built inside the LHC Software Interlock System.

- Origin of the signals:

- PC OP mode and I\_Meas are read and combined by the SIS

- Access OK comes from a LASER alarm (via LACS and TIM software)

- POWERING permit = false triggers on change from true to false a GLOBAL REMOVE\_PERMIT to each PIC of the powering sector

## The tools used to build the interlock

- PIC

- To remove the PC permit of the PCs

- Use the new GLOBAL REMOVE\_PERMIT command

- The SIS:

- To combine the signals and evaluate the powering permit

- To export the slow power command to the PIC

- The LASS/LACS

- To extract the patrol status

- > TIM

- To combine the individual signal form the LACS and export to LASER

- > LASER

- To publish access conditions readable from SIS

#### How it works

- There is one POWERING\_permit per sector

- The GLOBAL REMOVE\_PWRMIT is sent to all the PIC of the sector (LSS + arc)

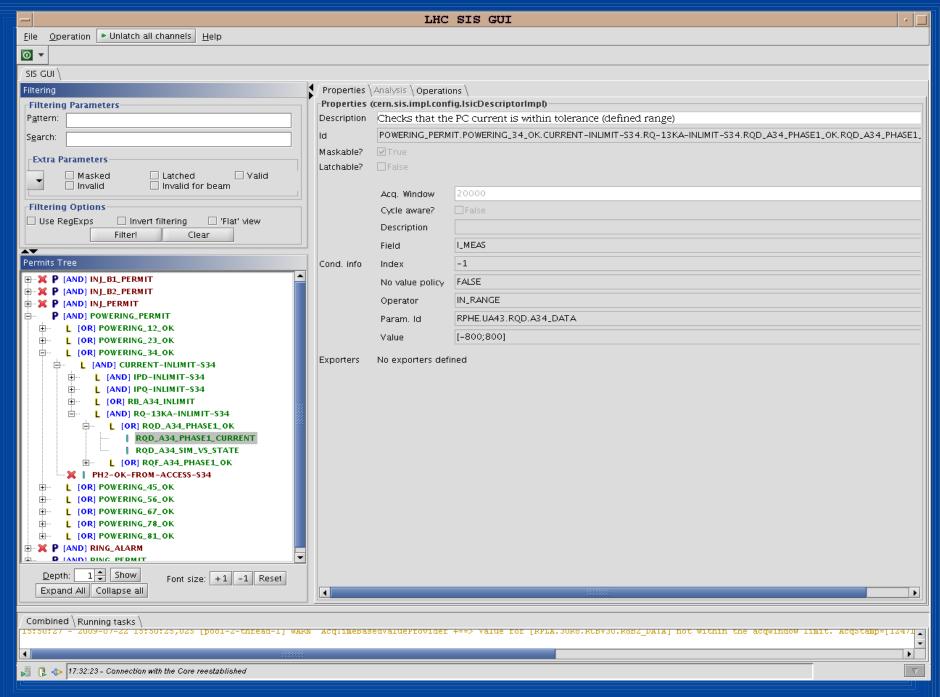

- Constant monitoring of the measured current (I\_meas) and the OP mode in the main circuits of the sector:

- RB, RQD, RQF, IPQ, IPD, RQX are monitored

- 600 A, 120A and 60A NOT monitored

- => **CURRENT-INLIMIT-Sxx** signal = true if all the I\_meas < I\_max or PC in simulation mode

- Constant monitoring of the access conditions for the concerned sector:

- Status of the patrol

- Just a concatenation of the LASS info

- => PH2-OK-FROM-ACCESS-Sxx signal = true if all the access sub-sectors defined according to the access matrix are SAFE

12<sup>th</sup> June 2009

12<sup>th</sup> June 2009

## Reliability of the parameters

- Problem: numerous software for the access conditions evaluation:

- LASS (Safety System) signals are exported to the LACS (Control System)

- LACS is publishing the signals to TIM

- TIM signals are combined in a rule to create an alarm

- This alarm is published by LASER

- SIS is reading LASER alarm

- The REMOVE\_PERMIT is sent to the PIC via CMW.

- Software has been tested during sector 23 tests:

- The load on the PIC is OK, signals received within few seconds

- Tests interrupted several times, but no unexplained triggers

- We have identified PO procedures which are not compatible with the logic

- Note: the current measure is not latched anymore

- Systematic test are needed: to be defined within the DSO tests?

## Consequences for PO

- During phase 1, access conditions are never met, so the current within limit = true is needed to have the PC permit

- If signals from the FGC are not arriving or the I\_meas values published are above the limits during phase 1, PC permit is removed to all the PCs of the sector. Some exemples:

- A restart of the FGC is stopping any ongoing tests

- Same for calibration when I\_meas is simulated

- Maybe others...?

- When FGC restart or calibration are needed, PO expert should first contact the EiC so that he masks the concerned circuit :

- Discipline is needed as soon as tests are starting in a sector

- Masking is a fast procedure

12<sup>th</sup> June 2009

# Switching from PHASE 1 to PHASE 2

- The complete procedure is described in a engineering specification under preparation LHC-MPP-ES-0003 (EDMS 1012328)

- During the whole procedure, no powering is allowed and all the PC of the sector should be LOCKED by PIC.

- The order of the actions are to be carefully followed:

- Block the circuit

- Proper information of the change (HW coordinator + LSA)

- Establish access conditions (patrols)

- Update the software limits in database

- Remove the hardware limits

- Synchronize FGC and careful check by PO expert

- Final check of all is OK by EiC, helped by SIS and LASS

- Unblock the circuits

# Switching from PHASE 2 to PHASE 1

- When sector is defined in Phase 2, no powering is allowed in the sector when access is needed, even below the phase 1 current

- If required, then we will have to switch back to phase and re-establish the hardware and software limits

- For both switching, no change are needed for the SIS interlock: can be constantly running during the procedure

- Some questions:

- The tracking of hardware/FGC limits is done by PO

- Communication between HWC/OP and PO is crucial

- Do we need more tools to ease the tracking? A kind of yellow paper for HW limits?

#### More tools

- The powering phases are now defined as a sector mode : this is published in LSA : sequence available to change it

- A fixed display will show the mode of each sector and the access conditions (still in preparation...)

|           | people in zone |           |   |

|-----------|----------------|-----------|---|

| Sector 12 | PO phase 1     | Access OK | 0 |

| Sector 23 | Cool down      | Access OK | 0 |

| Sector 34 | PO phase 2     | Access OK | 0 |

| Sector 45 | Shutdown       | Access OK | 0 |

| Sector 56 | PO phase 1     | Access OK | 2 |

| Sector 67 | Cool down      | Access OK | 3 |

| Sector 78 | PO phase 1     | Access OK | 1 |

| Sector 81 | Cool down      | Access OK | 9 |

Proposal for another fixed display, as help for volunteers giving access:

| Zone      | ITX 1R | LSS 1 R      | Arc 12    | LSS 2L          | ITX 2L |

|-----------|--------|--------------|-----------|-----------------|--------|

| People IN |        | UJ 16        |           | UJ23            |        |

| PC ON     | RQX    | IPD/IPQ/corr | RB/RQ/600 | DA IPD/IPQ/corr | RQX    |

## Summary

- The interlock is now deployed and constantly running

- We can try to improve the logic in order to allow calibration, but I would like to keep it as simple as possible

- Need to be tested with partial DSO tests before the start of the powering phase 2

- The interlock is stopping the Power Converter, not blocking the access...

- In case of doubt, the LASS gives the real status...

- Safety is guaranteed by:

- Hardware and FGC software limits

- Procedure to be apply for giving access

- SIS interlock is another independent way of checking that current is limited when people are accessing.