14–22 FEBRUARY 2018

VIENNA, AUSTRIA

# ISOTDAQ 2018 Lab Book

AUSTRIAN ACADEMY OF SCIENCES

TECHNISCHE

UNIVERSITÄT

WIEN

Vienna University of Technology

# **Tutors and their labs**

- 1. VMEbus programming Markus Joos

- 2. NIM Francesca Pastore, Andrea Negri

- 3. NIM & Scintillator Kostas Kordas, Roberto Ferrari

- 4. Muon DAQ Enrico Pasqualucci, Bransilav Ristic

- 5. FPGA Basics Dominique Gigi, Petr Zejdl

- 6. MicroTCA Hannes Sakulin, Bernhard Arnold

- 7. LabView DAQ Cristovao Barreto

- 8. ADC Basics for TDAQ Manoel Barros Marin

- 9. Network Programming Fabrice Le Goff

- 10. Microcontrollers Mauricio Feo, Barthélémy von Haller

- 11. Storage Systems Paolo Durante, Tommaso Colombo, Niko Neufeld

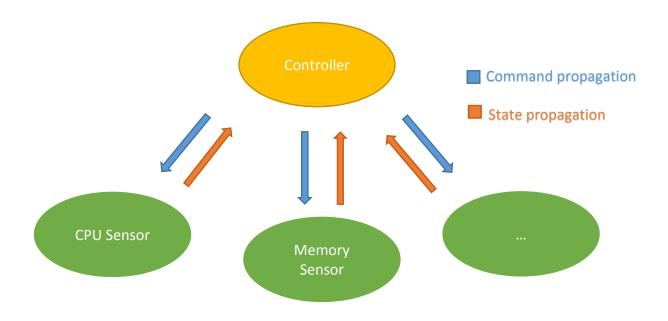

- 12. Control of DAQ Systems Enrico Gamberini

- 13. SoC FPGA Patryk Oleniuk

The main page of the 2018 ISOTDAQ School is <a href="http://isotdaq.hephy.at">http://isotdaq.hephy.at</a>

For up-to-date information on times and places, please see <a href="https://indico.cern.ch/event/643308/timetable">https://indico.cern.ch/event/643308/timetable</a>

# **Local Organizing Committee**

**Bernhard Arnold (HEPHY)**

Brigitte DeMonte (HEPHY) – emergency phone: +43 664 88476542 Markus Friedl (HEPHY) – emergency phone: +43 699 17251085

**Christian Irmler (HEPHY)**

**Richard Thalmeier (HEPHY)**

Claudia Wulz (HEPHY/CERN)

# **CERN Organizing Committee**

Paolo Durante (CERN) Markus Joos (CERN) Hannes Sakulin (CERN) Barthélémy von Haller (CERN)

# **Table of Contents**

| Exercise 1:  | VME Programming 4         |

|--------------|---------------------------|

| Exercise 2:  | NIM 6                     |

| Exercise 3:  | NIM & Scintillator        |

| Exercise 4:  | Muon DAQ                  |

| Exercise 5:  | FPGA Basics               |

| Exercise 6:  | MicroTCA 34               |

| Exercise 7:  | LabView DAQ 43            |

| Exercise 8:  | ADC Basics for TDAQ 60    |

| Exercise 9:  | Network Programming 70    |

| Exercise 10: | Microcontrollers          |

| Exercise 11: | Storage Systems83         |

| Exercise 12: | Control of DAQ Systems 87 |

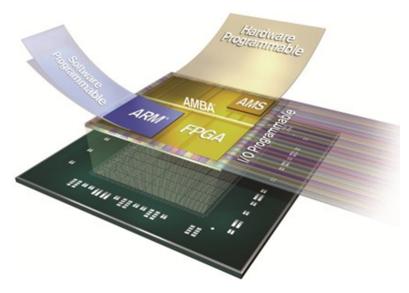

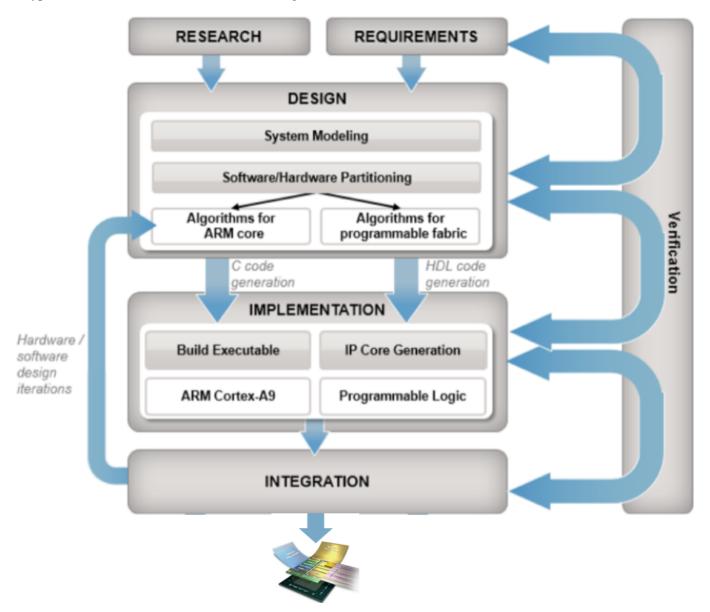

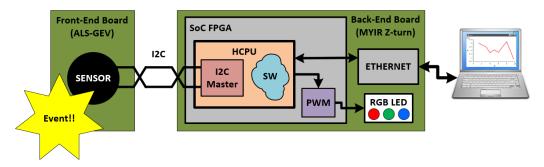

| Exercise 13: | SoC FPGA                  |

#### Student instruction sheet for Exercise 1 – VMEbus programming

#### Introduction

For the moment forget what you (hopefully) have learnt about the VMEbus protocol and the details of the H/W. For this exercise you have to look at a VMEbus slave as if it was a piece of memory in your PC. The purpose of this exercise is to demonstrate that in some respects there is little difference between internal and external memory; as far as the programming is concerned. The exercise also shows the differences between the two types of memory.

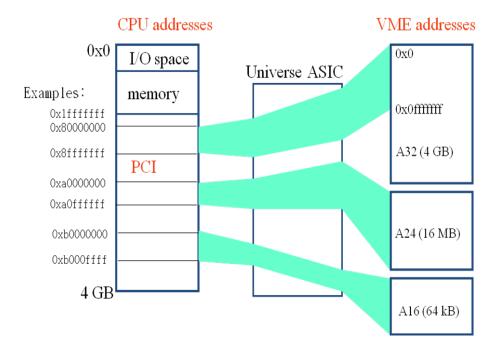

What is important to understand is that the VMEbus memory has to be mapped into the (virtual) address space of a user process before it can be accessed. This ties 3 busses together: CPU, PCI and VMEbus as shown in the picture below.

The first part of the exercise is to figure out how to create the appropriate mappings for the type of VMEbus access that you have to do. Then you actually transfer the data. This is done in single cycle mode which means that the CPU controls the data transfer.

In the second part of the exercise you will perform block transfers (DMA). This requires a different programming technique since it is not the CPU that moves the data but an external device (a DMA controller). Such DMA controllers are not VMEbus specific. You find them everywhere (e.g. in Network interfaces, disk controllers, USB devices, etc.)

Before you start you should be able to answer these questions:

- 1) What does the acronym A24D32 mean?

- 2) What is endianness and how do you deal with it?

- 3) What are the advantages of block transfers?

- 1. On the VMEbus single board computer log on with the DAQ school account (dagschool / g0ldenhorn).

- 2. Run "source setup" and then change directory to exercise1/groupX

- 3. Open the file solution.cpp with an editor of your choice (vi, nedit).

- 4. Add the missing code to "solution.cpp" to execute the VMEbus cycles listed below:

- Write 0x12345678 to address 0x08000000 in A32 / D32 mode. Use the "safe" cycles

- 2. Read the data back from address 0x08000000 and compare it

- 3. Write 0x87654321 to address 0x08000004 in A32 / D32 mode. Use the "fast" cycles

- 4. Read the data back from address 0x08000004 and compare it

- 5. Write a block of 1 KB to address 0x08001000 in A32 / D32 / BLT mode. You have to prepare the data in a cmem\_rcc buffer.

- 6. Read the data back from 0x08001000 in A32 / D64 / MBLT mode and compare it

- 5. Run "make" to compile the application

- 6. Run "solution" and catch the VMEbus transfers with the VMEtro VBT325 analyser

#### Good practice:

- Check all error codes

- Do not forget to undo all initialization steps (return memory, close libraries)

before you exit from an application

# Exercise 2: the Trigger

# Introduction

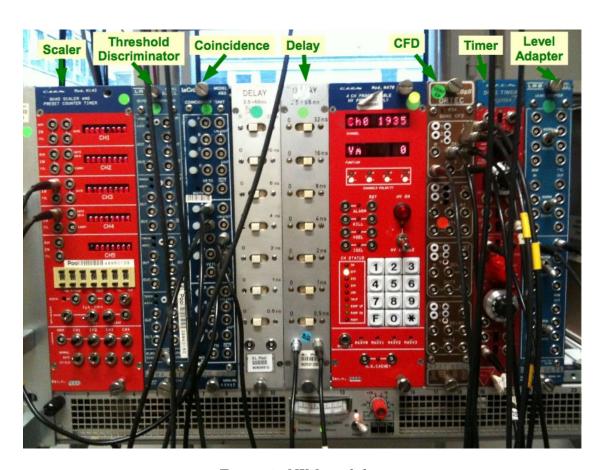

Figure 1: NIM modules.

This is a basic exercise based on the trigger lecture. It introduces all the elements and concepts needed in exercise 3 and 4. The available NIM modules are showed in Fig.1. The exercise is composed of 4 parts. At each step, look at the corresponding schema and follow the instructions.

A trigger is given by the transition of a signal from the logical 0 to 1. Before setting up any trigger system, you must have decided the levels corresponding to these logical levels and all the components of the system need to be coherently configured.

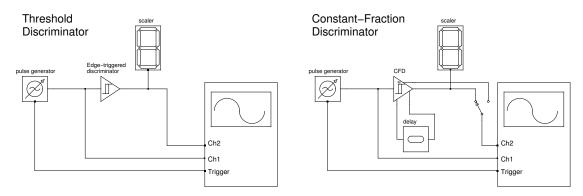

Figure 2: Scheme of threshold and constant fraction discriminators.

### Part 1a: Threshold Discriminator

The **Signal Generator** is pre-configured to provide a triangular pulse with a period of 300  $\mu$ s. Look at the signal (Channel Output) with the oscilloscope (CH1), using the Trigger Output of the generator as oscilloscope trigger (EXT). The Trigger Output is TTL signal.

How do you expect it?

Why do we use it?

Now try to characterize the signal:

| Leading edge time:  |  |

|---------------------|--|

| Trailing edge time: |  |

| Width:              |  |

Using the LEMO cables, try to implement the schema shown in the left part of Fig. 2, i.e.:

• Split the generator output signal: connect the two parts to the input of the **Threshold Discriminator** and to the oscilloscope.

• Connect one output signal of the discriminator to the scaler module and a second output to the oscilloscope (CH2).

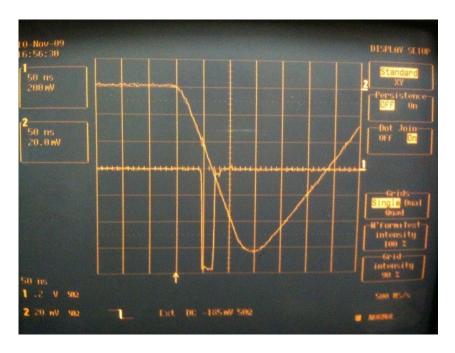

We have set-up a simple trigger system: you have a digital answer based on the amplitude of a signal. Reproduce the oscilloscope display shown in Fig. 3 and observe the amplitude of both the signal and its corresponding trigger.

Can you modify their amplitude?

Figure 3: Input signal and threshold discriminator output.

The threshold set on the discriminator can be measured with a **Voltmeter** (x10 output) and changed with a screwdriver. Change the threshold value: observe the behaviour of the discriminated signal on the scope and its rate on the scaler.

Can you relate them to the threshold values?

In real experiments, how is the best threshold value found?

# Part 1b: Threshold Discriminator, the jitter

Using the above set-up, set the discriminator threshold to 60 mV and change the amplitude of the input signal.

Which is the effect on the discriminated signal?

How does it affect a timing measurement?

Measure the discriminated signal delay with respect to the reference as a function of the amplitude of the input signal (-100, -150, -200, -250 mV) and fill up Table 1 with your numbers.

| Input signal amplitude (mV) | Threshold D (ns) | CFD (ns) |

|-----------------------------|------------------|----------|

| 100                         |                  |          |

| 150                         |                  |          |

| 200                         |                  |          |

| 250                         |                  |          |

Table 1: Measured delays on the discriminated signal with respect to reference

# Part 2: Constant Fraction Discriminator (CFD)

Now use the **Constant Fraction Discriminator** to make a trigger from the generator signal and implement the layout shown in the right diagram of Fig. 2. Using the Voltmeter and the screwdriver, set these CFD parameters:

threshold (T): 60 mV Measure with Voltmeter (x10 output) walk (Z): 2 mV Measure with Voltmeter (x10 output) delay (D): 80 ns Set with delay module + 2 x 10 ns cables

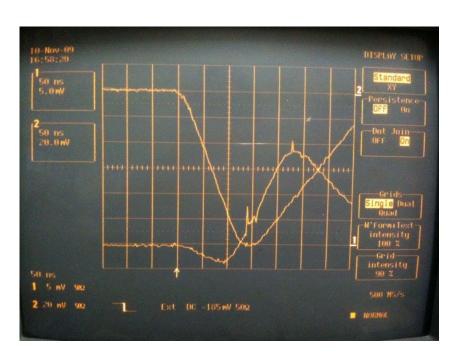

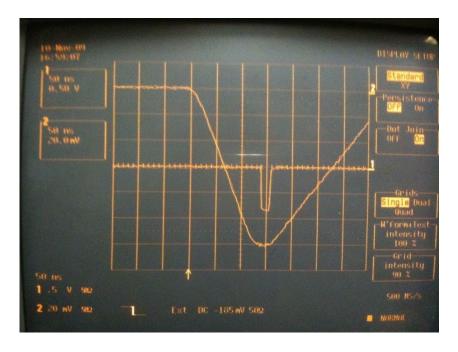

Connect the CFD monitor output (M) to the scope CH2 and reproduce Fig. 4.

Figure 4: Input signal and CFD monitor output.

Figure 5: Input signal and CFD output.

Can you recognize the CFD technique?

Which is the effect of varying the value of the delay D?

Connect now the CFD output to the scope (CH2) and change the amplitude of the input signal.

What happens to the output of the discriminator?

Measure the discriminated signal delay with respect to the reference as a function of the amplitude of the input signal (-100, -150, -200, -250 mV). Fill up Table 1 with your numbers. Compare the results with the previous measurements.

Can you see the advantage?

Can you make the CFD behave like a normal threshold discriminator?

Which configuration parameter has to be modified?

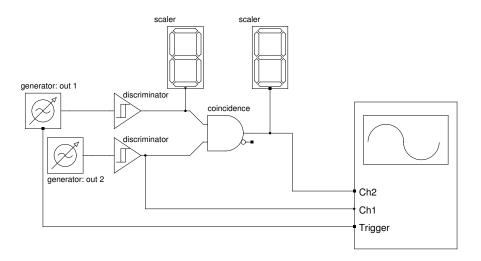

# Part 3: Making a timing coincidence

We try now to simulate the coincidence of two different trigger signals, in a simplified way. For that, use an additional output of the signal generator, which is configured to generate a triangular pulse similar to the first one. Use two threshold discriminator units to discriminate both signals, as described in Fig.6.

Figure 6: Coincidence layout

We have now two independent trigger signals with similar characteristics. Look at them in the scope.

Which parameters are important when making a coincidence?

Use one unit of the **Coincidence Module**, which is able to generate the logical AND of its input signals. The module has two outputs: OUT and LIN-OUT.

Can you guess the timing behaviour of the AND output?

When are you expecting the AND output to rise?

The **Scaler Module** is a simple and useful tool in a trigger system: it allows you to simply count the triggers and verify if your system is behaving correctly. Then use the scaler to measure the counting rate of your coincidence and try to answer these questions:

Can you count any trigger? How can you recover the coincidence rate?

After your adjustments, which is the width of the coincidence signal?

Can you explain the different behaviour of the OUT and the LIN-OUT signals?

Which is better to use in a real trigger system?

How can you save the trigger efficiency if one of the signals have large jitter?

Which is the drawback?

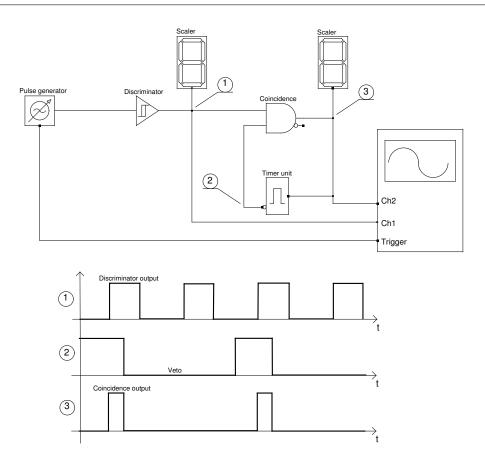

Figure 7: Top: busy logic schema with readout processing time simulated via a dual timer module. Bottom: time diagram of signals at the discriminator output (1), after the veto (2) and at the coincidence output (3).

## Part 4: Trigger veto and dead-time

A busy logic can be implemented using the coincidence module and a **Dual-Timer Module** which simulates a readout system with a fixed processing time (readout dead-time).

Configure one stage of a dual timer module to generate signals with 10 ms width. Then implement the busy logic in a second stage of the coincidence unit as shown in Fig. 7:

- one input of the coincidence unit is the trigger signal;

- to simulate the start of the readout, and so the trigger ACCEPT signal sent to the readout system, use the output of the busy coincidence to drive the timer module (START);

- use the output of the timer as the VETO of the busy coincidence: this is the BUSY signal sent back to the trigger system;

- connect the trigger signals before and after the busy logic to the scaler and check the correct logic.

You can easily make a rate measurement configuring the Scaler to work with a time gate of 1s with a GT+CLR configuration. Compare the trigger ACCEPT rate and the readout rate (after the BUSY) on the scalers.

How do they relate with the timer module setting?

Can you reproduce the numbers using the LIN-OUT of the coincidence unit?

Alternatively you can make an AND between the trigger and the output of the timer (with inverted logic) and not as a veto.

Where is the difference in the logic? Which risk are we taking?

Can you explain the behaviours observed disabling either one or the other input of the coincidence unit?

# Appendix: the Constant Fraction Discriminator

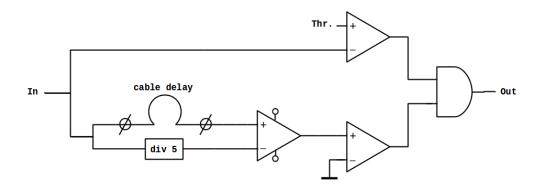

Figure 8: CFD function diagram.

The CFD functional diagram is showed in fig. 8. The input signal is treated in two different discrimination branches, whose results are then merged by the final AND gate. The top branch is a standard threshold discriminator, where the input signal is compared against a (configurable) threshold *Thr*.

The bottom branch implements instead the constant fraction technique. Technically, the input signal is split: one copy is delayed, while the other is attenuated by a factor 5. The two copies are then subtracted and the final result is compared with a threshold of (close to) zero. In fact, the zero-crossing time of the resulting signal in nearly independent from the input signal leading edge steepness (i.e. the source of time jitter in a standard threshold discriminator).

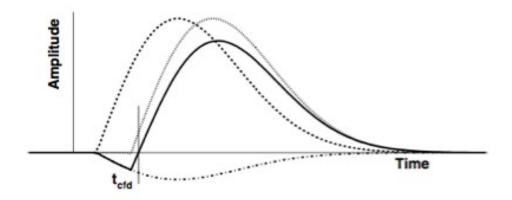

Figure 9: CFD function diagram.

Fig. 9 shows in detail the signals in the bottom branch of the CFD. The input

pulse (dashed curve) is delayed (dotted) and added to an attenuated inverted pulse (dash-dot) yielding a bipolar pulse (solid curve). The output of the bottom branch fires when the bipolar pulse changes polarity which is indicated by time  $t_{cfd}$ . From a practical point of view, a small threshold, as close as possible, is actually used in the final comparator of the bottom branch. This is needed to avoid fake signals possibly caused by the noise. Such a small threshold is normally called walk (Z).

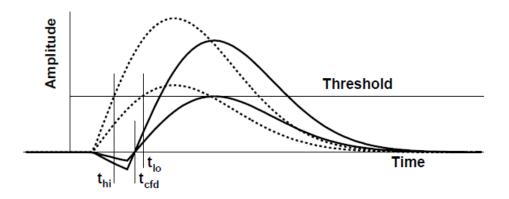

Figure 10: CFD function diagram.

In order to complete the CFD description, the merging of the top and bottom branch signals has to be considered, with the help of fig. 10. In the top branch, the threshold discriminator fires at time  $t_{hi}$ , that depends on pulse leading edge characteristics. The bottom branch instead fires at a time  $t_{cfd}$ , as discussed above, which is almost constant. Due to the delay introduce in the bottom branch, normally  $t_{cfd} > t_{hi}$ . Therefore, the overall CFD, defined as the signal generated by the final AND gate, will fires at  $t_{cfd}$ , achieving both our requirements:

- only select signal above a given amplitude *Thr*;

- provide an output trigger whose timing is independent from input signal amplitude.

As can be seen in the above figure, the CFD operating principle is not retained for all the possible combinations of configured delay, threshold and input signal amplitude. As the top branch timing depends on the signal amplitude, a small enough signal can make it fire at a time  $t_{lo} > t_{cfd}$ . In this case the CFD will behave like a normal threshold discriminator, as the output AND gate will be driven by  $t_{lo}$ .

#### Exercise 3

# Detector and Trigger: Scintillators, trigger logic, input to readout modules (ADC & TDC)

#### Introduction

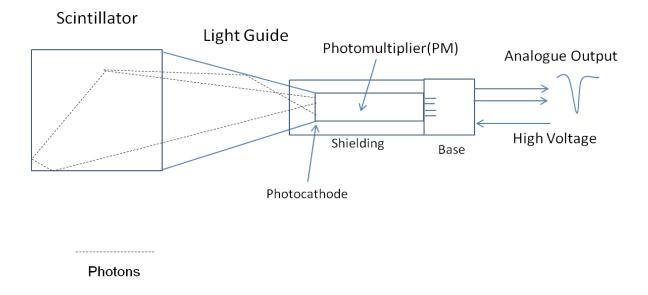

This exercise consists in building the trigger logic and the input signals to the VMEbus readout modules for a detector (exercise #4) using the experience with NIM electronics acquired in exercise #2. The detector comprises two scintillation counters detecting cosmic rays (muons). A schematic diagram of a scintillation counter is shown in

Figure 1. When a charged particle traverses the scintillator, it excites the atoms of the scintillator material and causes light (photons) to be emitted.

Through a light guide the photons are transmitted directly or indirectly via multiple reflections to the surface of a photomultiplier (PM), the photocathode, where the photons are converted to electrons. The PM multiplies the electrons resulting in a current signal that is used as an input to an electronics system. The PM is shielded by an iron and mu metal tube against magnetic fields (of the Earth). The scintillator and light guide are wrapped in black tape to avoid interference with external light. The scintillation counter setup is shown in Figure 2.

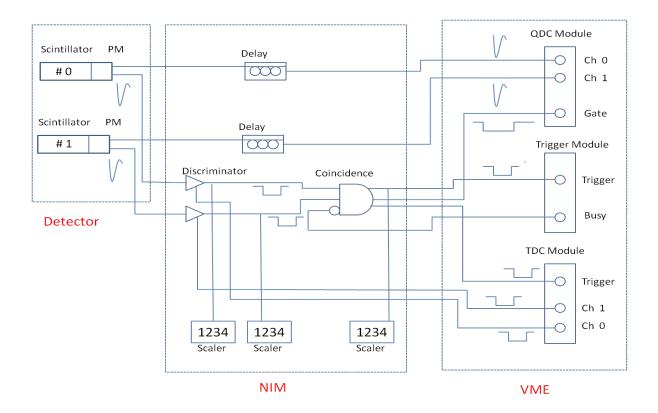

The NIM modules used to build the trigger and the input to the readout system and provide the high voltage is shown in Figure 3.

#### **Outline:**

The aim of the exercise is to get an understanding of the detector and trigger logic used in Exercise 4. The signals from two scintillation counters are analyzed using an oscilloscope and transformed into logic NIM signals that allow to build a trigger based on a coincidence between the signals. The coincidence rate i.e. the rate of cosmic muons is counted using a scaler and the charge content of the scintillator signals is measured on the oscilloscope. In addition the inputs to the readout modules (QDC and TDC) are set up.

A schematic diagram of the full trigger and readout electronics is shown in Figure 4.

Figure 1. Schematic diagram of a scintillation counter.

Figure 2. Scintillation counter setup

Figure 3. NIM trigger electronics. From left to right: scaler (counter), discriminator, coincidence unit, delay modules and high voltage power supply.

Figure 4. Diagram of the electronics for the detector, trigger and readout of the scintillator counter setup.

#### Work plan:

Note: whenever there are two parallel outputs from a (NIM) module one needs to make sure that they are both cabled, i.e. either terminated with 50 Ohm or connected to another unit. This ensures that the pulses have the correct NIM voltage levels: 0 and -0.8 Volts.

- 1. Install the scintillation counters close to each other with maximum overlap between the scintillator areas.

- 2. Check that the scintillator photomultiplier bases are connected to the N470 NIM high voltage supply.

- 3. Switch ON the NIM crate.

- 4. Connect an output from scintillator 0 (the upper one) to an oscilloscope (10ns LEMO), terminate the other output with 50 Ohm.

- 5. Set the nominal high voltage on scintillator 0 using channel 0 of the N470 HV supply. The voltage is marked on the label glued onto the base. Refer to Appendix 1 at the end of this exercise for a short guide to using the N470 HV supply.

- 6. Look at the signal on the oscilloscope (volts/div  $\sim 50$  mV, time/div  $\sim 20$ ns). What is the maximum voltage of the signal?

- 7. Connect the cable to the input of the first channel of the discriminator.

- 8. Connect an output to the oscilloscope (0.5 Volts, 50 ns) and adjust the pulse width to around 100 ns using a small screwdriver (terminate the other output with 50 Ohm), see Figure 3.

- 9. Connect the output to the first channel of the NIM scaler (N415) using a short LEMO cable (1ns).

- 10. Set the discriminator threshold to 50 mV: adjust the voltage on the test point using a DC voltmeter and a small screwdriver, see Figure 3. The voltage is 10 times the threshold value

- i.e. the voltage should be around 0.5 Volts. This step may require teamwork.

- 11. What is the scaler rate?

- 12. Vary the threshold around 50 mV and check the variations in scaler rate.

- 13. Repeat points 4 to 11 above for scintillator #1 (the lower one), connecting this scintillator in addition to the one already connected.

- 14. Given the scaler rates measured above, what is the probability of random (unphysical) coincidences between pulses from the two scintillators?

- 15. Connect an output from each of the two discriminator channels to the oscilloscope and check that they have a timing overlap i.e. are coincident.

- 16. Connect the cables from the discriminators to the first inputs of the coincidence unit (LeCroy 465) using short LEMO cables (1ns).

- 17. Connect an output from the coincidence unit to a scaler input. What is the rate? Given that the rate of cosmic muons is about 100 per second per square meter, does the rate make sense?

- 18. Connect an output of the coincidence unit to channel 1 of the oscilloscope.

- 19. Connect the (other) analogue output from scintillator 0 to a delay unit (LEMO 10ns) and the output of the delay unit to channel 2 of the oscilloscope.

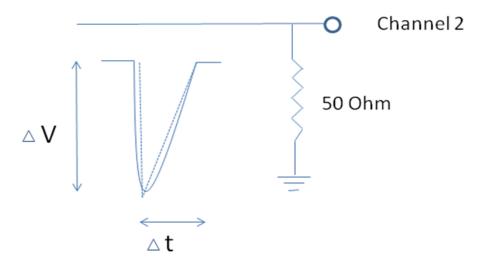

- 20. Using channel 1 as a trigger, observe the analogue signal on channel 2. Channel 2 will then show the scintillator signals for the cosmic muons. Assuming that the signal is triangular, what is the charge of the signal? See Figure 5. **Note down the charge. You will need it** again in exercise 4

- 21. Adjust the delay unit such that the analogue signal falls within the NIM pulse from the coincidence unit: inputs to the charge to digital converter (QDC) in Exercise 4 are now ready (analogue signal and gate).

- 22. Repeat point 21 for scintillator 1.

- 23. Connect a cable from the first discriminator to channel 2 of the oscilloscope and check the timing with respect to the output from the coincidence (channel 1). The signal from the discriminator should precede the coincidence. Similarly for the second discriminator. The inputs to the time to digital converter (TDC) in Exercise 4 are now prepared (trigger and timing signals).

- 24. The signals from the discriminators are sometimes about twice as long as expected. What could the reason be?

## Appendix 1. Short User's Guide to the CAEN N470 High Voltage Supply

This is a short list of the most common operations for the N470 High Voltage Supply used in Exercises 3 and 4. The manual can be found at <a href="http://www.caen.it/nuclear/product.php?mod=N470#">http://www.caen.it/nuclear/product.php?mod=N470#</a>

To select a channel: F0\*(channel number)\* e.g. F0\*0\*

To set the High Voltage on the selected channel: F1\*(type value)\* e.g. F1\*2000\*

To read the voltage on the selected channel: F6\* To read the current on the selected channel: F7\*

To turn the selected channel ON: F10\*

#### **Notes:**

The maximum voltage on the channels has been set to around 2300 Volts (on the potentiometers). These can be checked via F13\*. The current limits have been set to 2mA (via F2\*).

#### Appendix 2. Charge of scintillation counter current pulse

Figure 5. Input to the oscilloscope from a scintillatio

#### Exercise 4.

#### A small physics experiment: detector, trigger and data acquisition.

#### Introduction

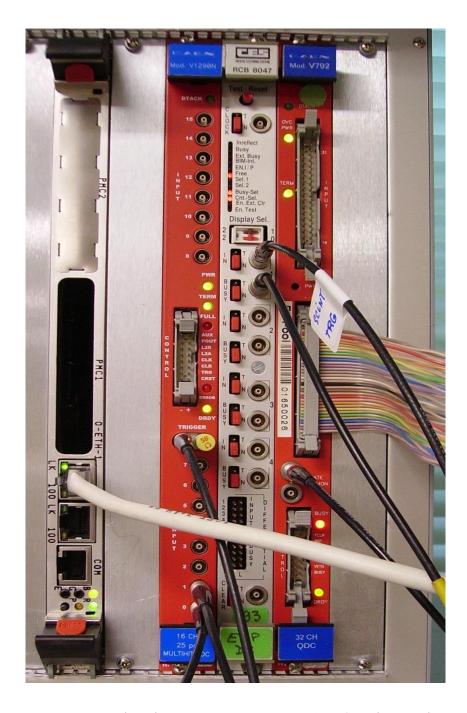

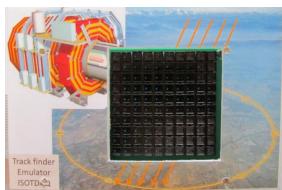

This exercise comprises all the components of a typical experiment in high energy physics: beam, detector, trigger and data acquisition. The "beam" is provided by cosmic rays (muons) and the detector consists of a pair of scintillation counters, see **Error! Reference source not found.** in Exercise #3. The trigger logic, built in NIM electronics, forms a coincidence between the signals from the scintillation counters which indicates that a muon has traversed the detector, see **Error! Reference source not found.** in exercise #3. A data acquisition system based on VMEbus is used to record the pulse heights from the scintillation counters and measure the time of flight of the muon. The VMEbus crate is shown in Figure 1 and the VMEbus modules shortly described in 0, 0 and 0. The overall run control and monitoring is provided via software running on a (Linux) single board computer (SBC).

#### Outline

This exercise is a continuation of exercise # 3. First, standalone programs are executed to give an understanding of the QDC and TDC VMEbus modules. A full DAQ system is then run on a multiprocessor configuration, with the readout, run control, GUI and infrastructure on a VMEbus SBC. Event rates and dumps are examined. An event monitoring program produces histograms of the QDC and TDC channel data which allow to compute the charges of the input signals to the QDC and the speed of the cosmic muons.

Exercise 4: Muon DAO

Figure 1. VMEbus data acquisition system: SBC (Single Board Computer), TDC (Time to Digital Converter, Trigger Module (CORBO), QDC (Charge to Digital Converter)

#### Work plan

- Verify that the detector is working i.e. the scaler counts for scintillator 0, scintillator 1 and the coincidence are counting such that the TDC and QDC receive signals (note for the tutor: if the coincidences are not counting, remove the CORBO busy from the trigger coincidence by pushing the button).

- Login to the SBC as user daqschool, password g0ldenhorn

- Start a Terminal window from the toolbar

- Go to TDAQ directory: cd ~/TDAQ and run the command source ./setup\_RCDTDAQ.sh to define the environment

- Run the program v1290scope which is a low-level test and debug program for the CAEN V1290 TDC

- 1. Run command: v1290scope (Use defaults for the command parameters).

- 2. VMEbus base address = 0x4000000

- 3. Dump the registers (option 2). Is data ready? (bit DREADY in the status register). What are the values of the match window width and the window offset? See 0.

- 4. Configure the TDC (option 3)

- 5. Read an event (option 5). The event has a format as shown in the CAEN manual pages: Output Buffer Register. How many words are read? (Check in the global trailer). What are the values of the TDC measurements (in ns). Do they make sense? See 0. Exit from the program by choosing menu entry 0.

- Run the program v792scope which is a low-level test and debug program for the CAEN V792 QDC

- 1. v792scope

- 2. VMEbus base address = 0x0

- **3.** dump the registers (option 2). Is data ready? Check also the LED on the module.

- **4.** read an event (option 5). How many words are read? Which channels have data and which are pedestal (empty) values?

- We now run the full DAQ system

- 1. Start the DAQ system: ./setup\_RCDTDAQ.sh start. This script will read the configuration database and start a number of processes on the server: run control, GUI and a number of infrastructure SW components. This is a somewhat long procedure and should result in a message 'OK!'.

- 2. Now start a GUI display: **./start\_Igui.sh**. The "folders" in the infrastructure panel should be green! You may need help from the tutor here ...

- 3. We now go through the run states in order to start a run. But first please obtain a 'Control' access by selecting the 'Control' radio button in the top menu 'Access Control'.

Exercise 4: Muon DAQ

The initialize button should become active. Now, click on INITIALIZE and then wait for the RCDApp (in RCDSegment) to reach the INITIAL state. The readout application is now loaded on the VMEbus processor.

- 4. Click the CONFIG button followed by OK on the "Remember to ..." dialog box. This configures the VMEbus modules, the CORBO, QDC and TDC.

- 5. If you don't see the DFPanel tab close to the top of the GUI, click LOAD Panels and load the first panel: DFPanel should now appear in the bar above the Run Control panel.

- 6. Click START in the control panel (on the left)

- 7. Data taking should now start. Click on the DFPanel and the L1 button to display the event rate. Is it what you would expect after exercise # 3? Check also the LEDs on the VMEbus modules (the event rate is computed by the Information Service (IS) which periodically sends a command to the Readout Application to obtain the rate which is then retrieved by the GUI).

#### • Event Monitoring

This part demonstrates event monitoring. An event monitoring program obtains a sample of events from the readout application and analyses them, in this example by producing histograms of the values from the QDC channels as well as the time difference between the two TDC values. The histograms can then be viewed via the GUI. The code for the monitoring program can be found in ~/RCDTDAQ/RCDMonitor/

- 1. Open another terminal window.

- $2 \cdot cd \sim /TDAQ$

- 3. source ./setup RCDTDAQ.sh to define the environment.

- 4. Run the event monitoring task: ./event\_dump.sh -e -1

(-1 means to run forever. I you want only one event, please change it to 1.). Once you have seen the raw data output of the even\_dump you can terminate this application with ctrl+c.

- 5. The first nine words of the data constitute an Event (ROD) header. The following words are the data from the QDC and the TDC. Do you recognize the data?

- 6. On the terminal start the monitoring program by executing monitor. This program monitors data, like the event\_dump program, publishing measurements to the histogramming service.

- 7. In the GUI click on the OH button (Online Histogram). Click on Histogram Repository, part RCDTDAQ, RCDMonitor. Double click on the histograms to view them.

Alternatively, using a new terminal execute **source** ./setup\_RCDTDAQ.sh followed by ./start\_ohp.sh. This is the online histogramming presenter. In the panel Histograms (on the left) select SCMonitor to view TDC histograms or RCDMonitor to view also the QDC histograms that we are producing.

8. Record the mean values of the QDC histograms and the mean value of the time difference histogram. The time histogram is not centered around zero. Why?

- 9. The charge that you find in the histogram is not the charge delivered from the PMT to the QDC. What is the reason for that and how can we measure the proper charge?

- 10. The monitoring of the statistics can be reset by stopping and starting the monitoring program (Ctrl+C to terminate). This restarts the monitoring program described in point 6.

- 11. Display the histograms of the QDC channels. Record the pedestal values.

- 12. Using the formula shown in 0, compute the mean charges of the signals from the scintillators. Do they agree with the results obtained in exercise #3?

- We now want to measure the time of flight of the muons between the two scintillators.

- 1. In the histogram for the data from the TDC we already get a  $\Delta$ -t. This value, however, is not the time of flight of the muon. Why? How can we modify the set-up in such a way that we can correct the  $\Delta$ -t for errors and measure the actual time of flight?

- 2. Restart the monitor program from the IGUI per point 10 above. Record the new mean value of the  $\Delta$ -t histogram.

- 3. What is the difference with respect to the value measured before? Compute the speed of the cosmic muons.

#### . TDC CAEN V1290 VMEbus module

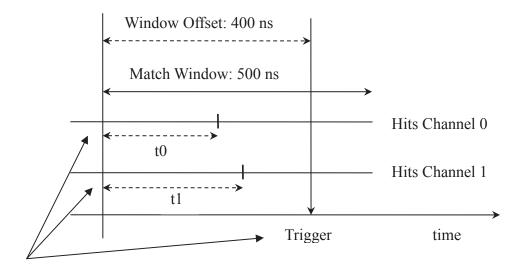

The TDC is operated in *trigger matching* mode. This means that the TDC measures the time of arrival of the hits on a channel within a *match window*. The TDC receives a trigger and the channel signals as shown in the diagram of the complete setup, **Error! Reference source not found.** of exercise #3 and seen in the picture of the VMEbus crate, Figure 1. A trigger match window is then defined by a window offset with respect to the trigger and a match window size as shown in the figure below. The hits occurring on channel 0 and channel 1 within the match window are recorded by the TDC and the values in units of 25ps stored in the memory of the module.

The module is shown in the photo of the VMEbus crate and the manual for the module can be found at <a href="http://www.caen.it/csite/CaenProd.jsp?parent=11&idmod=796">http://www.caen.it/csite/CaenProd.jsp?parent=11&idmod=796</a>

26 Exercise 4: Muon DAO

Input signals to the TDC

#### . QDC CAEN V792 VMEbus module

This page explains briefly how to calculate the charge of the input signal to the QDC from the data readout from the module over VMEbus. The module is shown in Figure 1.

The manual for the module can be found at <a href="http://www.caen.it/csite/CaenProd.jsp?idmod=41&parent=11">http://www.caen.it/csite/CaenProd.jsp?idmod=41&parent=11</a>

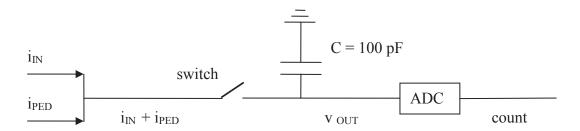

The circuitry of a channel is shown schematically, below.

The switch is closed as long as the gate input signal is present. The input current is the sum of i  $_{IN}$ , the current input to the module via the front panel (from the scintillator), and i $_{PED}$ , a bias (or pedestal) current which is generated internally. The bias current allows to handle input signals with small positive voltage components. When the switch is closed during the time of the gate signal, the input current charges the capacitor C. When the switch is opened again, the voltage across C, v  $_{OUT}$ , is converted by an ADC and stored in the memory of the module. The ADC has the property that one count = 1 mV.

We now have for the charge of the capacitor:

$$Q = C * v_{OUT} = 100 (pF) * count (mV) = 0.1 * count (pC)$$

To compute the charge in the signal input to the channel, corresponding to  $i_{IN}$ , we have to correct for the pedestal value:

## $Q_{IN} = 0.1 * (count - count_{PED}) (pC)$

count = channel data with input signal present

count  $_{PED}$  = channel data with input signal removed ( i  $_{IN}$  = 0)

#### . CES RCB 8047 CORBO VMEbus trigger module

When a NIM signal is sent to a channel on the CORBO, a bit is set in a status register and an interrupt on VMEbus is generated, optionally.

The DAQ process on the VMEbus processor can then execute the code to readout the data from the QDC and TDC modules. In addition, the CORBO generates a busy signal which allows to block further triggers until the readout code is terminated.

The CORBO module is shown in Figure 1.

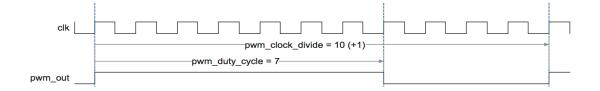

# **FPGA programming**

(Ver2014\_v01)

#### **INTRODUCTION:**

In a lot of digital designs (DAQ, Trigger, ... ) the FPGAs are used. The aim of this exercise is to show you a way to logic design in a FPGA. You will learn all the steps from the idea to the test of the design.

In this exercise you will:

- -discover how we can do parallel applications

- -program a FPGA from the design up to the implementation and the test

The boards used are ALTERA development kit (Figure 1) based on a small FPGA (CYCLONE) with multiple additional interface components like audio CODEC, switches, button, seven-segments display, LEDs, .... and a home-made board (named detector in the following pages) connected to the development kit with a flat cable (figure 2)

The initial design is loaded into the board.

You will follow the example to understand the design flow. Four exercises are proposed to modify the original design functionality.

Figure 1: development kit

Figure 2: detector

#### **QUICK START:**

- 1) Programs used are: QUARTUS (FPGA tool), ModelSim (simulator), LabView

- 2) Ask the tutor if you have question(s) or problem(s)

# **EXERCISE** (example)

When you switch on the kit, the initial design is loaded into the FPGA.

On the LabView window, you can see the progression of the marker on the detector.

At the same time, you can see on the two 7-segments LED (the right ones on ALTERA kit) the column and the line number over which the maker is positioned.

#### **DESIGN ENTRY**

The design file is named "CII\_Starter\_Default.bdf" (for all exercises you should work with the same design file). The design is divided in three parts:

Exercise 5: FPGA Basics 29

- a) A green rectangle which is used to transmit the information to the computer via the RS232 connection to display the trace on LabView.

- b) A blue rectangle in which the design generates the clock and the logic to control the detector (see Appendix A for detailed functionality).

- c) A red rectangle, which contains the logic to detect the trace. You will change the logic in this rectangle in the following exercises.

The idea of all exercises is to detect a trace. As soon as the trace is detected one 7-segment LED blinks (the third for the right side).

Click on key0 (Altera kit) to stop the blinking. Now generate another trace.

Spend some time to understand how this design works.

Do you understand it?

#### **COMPILATION**

This design is the entry of your logic, it should be compiled now; go to QUARTUS *Processing->Start Compilation*.

The design is compiled for the chosen component (Cyclone II).

The compiler executes multiple tasks:

- √ logic optimization

- ✓ generates a binary file used to program the FPGA (memory array),

- ✓ extracts the timing between each logic elements used for the timing analyses

- ✓ generate an output VHDL file used for the simulation

#### **SIMULATION**

When the compilation is finished, you can check the design with a simulator. To do this you will use ModelSim.

Check in the "Project" TAB if there is a file marked with a bleu "?", if YES, compile it (right-clic on it, Compile-> compile selected)

In the "Transcript" tab, type 'source sim.tcl', ENTER. The simulator opens the waveform, loads the signals, and starts the simulation.

At the end, stimuli and results are displayed in the wave window.

This simulation emulates a trace starting from the top left and finishing at bottom right describing a straight line on the detector.

(The tutor will give you some explanations on the results and the signals shown in the waveform)

Remember where the signal OK goes to "TRUE".

Figure 3: straight line

When you finished with the simulator type 'quit –sim ' ENTER in the "Transcript" tab.

#### **PROGRAM THE KIT**

30 Exercise 5: FPGA Basics

To download the design on the board, (QUARTUS program) go to on *Tools->Programmer* (Check that the Hardware is USB-Blaster, if not ask the tutor).

One file is shown in the window: it is your design. Click on Start .The programmer takes few seconds. At the end, a message appears to inform you that the programming is completed (or not successful: in this case usually the board is switched OFF, or the cable is not well connected).

#### **TEST**

Draw a straight line from top left to bottom right to see if the design works well!

Now, you are ready to do the other exercises by yourself.

Good Luck!

# **EXERCISE I**

The exercise above uses the graphic to describe the design. In this exercise, we want to do the same with a text design entry (VHDL).

In the QUARTUS design entry (file "CII\_Starter\_Default.bdf"), delete the line between inst\_graph and JKFF inst\_result and connect the output 'result' of "track1"box to the JKFF inst\_result with a line.

- -Compile the design

- -Simulate the design

Go to ModelSim:

- ✓ Compile the file marked with a ? in the "Project" tab (select the file to be compiled Menu Compile-> Compile selected)

- ✓ Type "quit –sim" in the "Transcript" tab.

- ✓ Type "source sim.tcl " in the "Transcript" tab.

Find out the difference with the previous result (check where the signal OK goes to "TRUE").

Can you explain the difference? Can you modify the file "track1.vhd" to have the same result as in the previous exercise?

- -Download the design

- -Test the design

# **EXERCISE II**

In this exercise we want to detect a curved trace.

Figure 4

Figure 5: example of trace expected.

31

Exercise 5: FPGA Basics

In the QUARTUS design entry (file "CII\_Starter\_Default.bdf"), delete the line between output 'result' of "track1" box to the JKFF inst\_result, and connect the output of the "trck\_fnd01" box to JKFF inst\_result.

The "trck fnd01" box logic detects only a straight trace. Compile the design and do a simulation:

- -Compile the design (QUARTUS)

- -Simulate the design

Go to ModelSim, compile the file marked with a ? in the "Project" tab (click on the file to compile – Menu Compile-> Compile selected)

To simulate:

- ✓ Type "quit –sim" ENTER in "Transcript" tab to exist any running simulation.

- ✓ Type "source sim2.tcl" ENTER in "Transcript" tab to start the simulator.

A signal OK becomes true if the logic detects the expected trace (here a straight trace).

In this exercise, you will examine the implementation of the design in the FPGA and see how we can change the results (max. frequency ...)

1. In QUARTUS open TimeQuest (Tools -> TimeQuest timing Analyser)

-double click on Report Fmax Summary ("Tasks" window)

You can see the maximum frequency of each clocks implemented in the design (Note the max frequency that "scan clk" can reach)

2. Go back to QUARTUS,

Open the partition window (Assignments -> Design partitions window)

Right-click on the partition named "trck\_fnd01:instzigzag" (Locate-> Locate in Chip Planner )

Now, you will specify the place where your logic will be implemented:

There is a blue rectangle in the Chip planner (named "trck\_fnd01:instzigzag").

Place it where you want (not at the place where the logic is actually implemented) to implement the logic at the next compilation.

Compile the design (Quartus), and execute the TimeQuest (see point 1). Normally the maximum frequency will change.

This give you an idea of the importance of the place of you logic or how to reserve a place if you work in a team (each person will have a reserved place to implement his logic).

NB: For your information, for each clock of the design, the frequency to reach <u>has to be specified</u> in a <u>constraint</u> file.

# **EXERCISE III**

The exercise consists to modify the "trck fnd01" box logic to detect any curve trace as in figure 4.

The trace should start at any pixel in the first line and goes to next line going to a pixel adjacent to the pixel of the first line and so forth (figure 5).

To help you, you have to change code in the "mask\_build" entity (beginning of the "trck\_fnd01.vhd").

- -Compile the design

- -Simulate the design

Go to ModelSim, compile the file marked with a ? in the "Project" tab (click on the file to compile – Menu Compile-> Compile selected)

To simulate:

✓ type "quit –sim' ENTER in "Transcript" tab to exist any running simulation.

✓ type 'source sim2.tcl' ENTER in "Transcript" tab to simulate in this exercise.

A signal OK becomes true if the logic detects the expected trace.

- -Download the design

- -Test the design

# **EXERCISE IV**

If you have time, you can modify the previous file to detect only the curve trace on right or left (not in zigzag like the red trace in figure 4).

# **APPENDIX A**

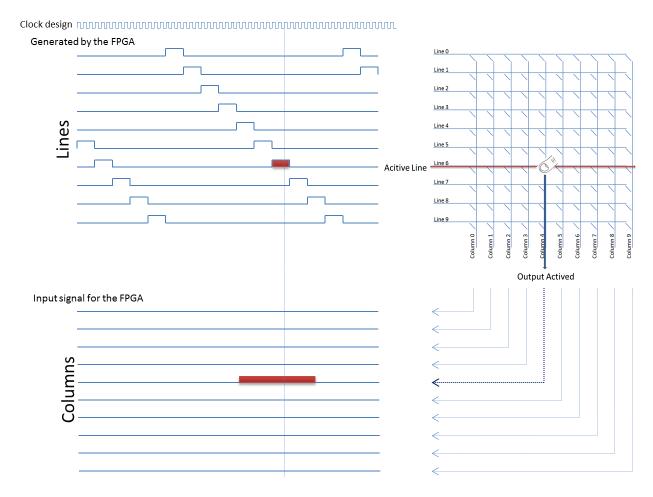

The detector is a matrix of 10 lines and 10 columns (100 pixels). Only one line is activated at a time.

When a line is activated the result of each column indicates if the marker is over a pixel. Each line is activated one after the other (0, 1, 2... 8, 9, 0, 1, ...). Each line is activated during 4 clocks cycles. The detection logic checks the result (if pixel is masked by the marker) only during the third clock cycle (signal "check" in the design).

#### Exercise 6: Micro TCA

#### **Overview**

In this exercise you will ...

- explore the Micro-TCA technology

- learn about the PCI (express) bus

- write data acquisition software to sample music and display the wave forms

#### Introduction

In this exercise you will work with modular electronics based on the rather new Micro-TCA standard. TCA stands for Telecommunications Computing Architecture, an architecture that is used in Telco industry to provide highbandwidth, high-availability solutions. Both Micro-TCA and its bigger brother Advanced TCA (ATCA) will be used in the upgrades of the LHC experiments. Like VME or Compact PCI, Micro-TCA defines a rack—called *shelf* in TCA speak—and boards, called Advanced Mezzanine Cards or AMCs. Typical shelves have space for 12 AMCs but we will work with a slightly smaller version. A Micro-TCA Carrier Hub (MCH) performs management functions, such as monitoring temperatures and regulating fan speed to provide the necessary cooling. A Micro-TCA shelf may contain a second MCH for redundancy (but we will work with only one). The backplane contains high-speed serial links that are suitable for transferring data at rates of 10 Gb/s or more using various protocols. Typically the backplanes have a single or dual-star layout with all high speedlinks going from each AMC to the MCH slot(s). The MCH then contains a switch for the desired protocol—in our case PCI Express (PCIe). Other backplane layouts exist with high-bandwidth links between neighboring AMC slots.

#### The test setup

We are using a small ELMA Micro-TCA shelf containing:

- a built-in power module and a built-in fan

- a backplane with star and mesh connections

- an MCH by Samway (IP 137.138.63.22)

- an AMC containing a Processor running Linux (IP 137.138.63.15)

- an I/O AMC (AMC-ADIO24) providing digital and analog IO

- optionally, an AMC that can generate a programmable load on the crate

**Figure 1.** The exercise setup

34 Exercise 6: MicroTCA

We will be working directly on the processor AMC. Keyboard, mouse and screen are directly connected to this card which runs a standard Scientific Linux CERN (SLC) distribution. We will use the network port of this card to communicate with management port of the MCH.

#### Get to know the setup

Log into the processor AMC:

User: student (ask your tutor for the pwd)

#### **Explore the system using the Webserver**

- open Firefox

- Connect to the Samway MCH webserver at IP 137.138.63.22

You can use the webserver to browse the different Field Replaceable Units (FRUs) in the system. You can get information about the units, their voltages and temperatures as well as the valid operating ranges for all these quantities.

Turn on all load groups of the load AMC as shown in the next section. See how the MCH reacts.

#### Connect to the MCH by telnet

You can see details of the processes in the MCH by connecting to it with telnet (*telnet 137.138.63.22*). Login: user

Try it. (use command *help* to display help).

**Note** that the backspace may not work. In this case you can use ctrl+h.

To see the fan-speed and fan-levels:

```

sensor cu 1

```

As an alternative way to looking at the webserver, you can check the operating ranges and current readings of all sensors via the telnet connection:

```

sensor amc <slot>

```

#### **IPMI**

The webserver communicates with the MCH through IPMI (Intelligent Platform Management Interface) commands. The MCH either answers to the IPMI commands itself or it forwards the request to a FRU using a dedicated I2C (Inter-Integrated Circuit, often pronounced I-squared-C) link.

Exercise 6: MicroTCA 35

You can also directly use the IPMI protocol to talk to a card in the sytem. For example, we can program the load of the load board (produced at CERN) through IPMI. For this we use the program *ipmitool* with the following syntax:

```

ipmitool -I lan -H <ip_address> -U admin -P ADMIN -T 0x82 -t <AMC_address> -b 7 -B 0 raw 44 7 0 0 <group_number> <action> 0 15

Where:

<ip_address> is your MCH address

<AMC_address> is the target AMC address (Slot1 = 0x72, Slot2 = 0x74, Slot 3 = 0x76 ....)

<group_number> is the LED/Load group number from 4 to 11

<action> if 0xff group ON, if 0x00 group OFF

```

- Try switching on all the load-groups of the AMC

- See the reaction on the temperature of the AMC by repeatedly running the sensor command (see above)

- When a non-critical threshold is reached the MCH should increase the fan-speed of the crate

- Check this by running the cu command

- Now you should turn off the load groups quickly to avoid that the system overheats (the fan is not powerful enough in this crate)

#### **Explore the Backplane**

The telnet prompt has commands that allow to display the links of all FRUs.

bpppc # backplane connectivitypcie # PCIe status

Try them. The backplane connectivity information needs some decoding. There is some information given at the top of the output. Some further information may be found in the Samway MCH user manual (ask your tutor for a printed copy or find it in /ISOTDAQ/doc/).

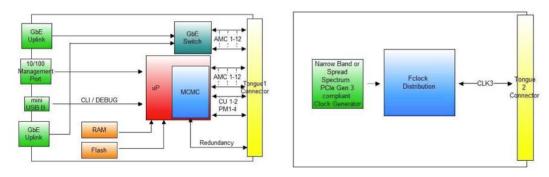

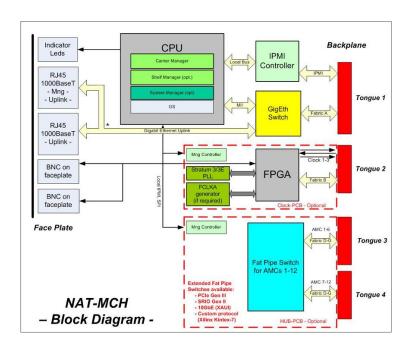

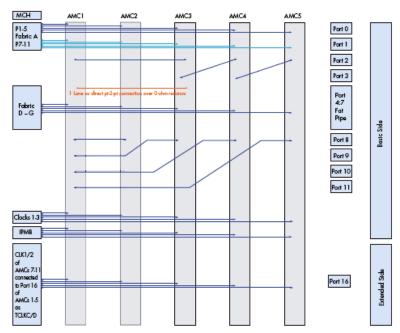

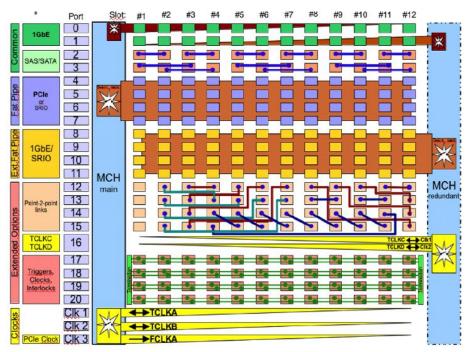

AMCs usually have 21 ports, MCHs up to 84 ports. An MCH connects to multiple connectors and is composed of a number of printed circuit boards stacked on top of each other. The boards are called the *tongues* of an MCH. Figures 2 and 3 show the block-diagrammes of the two tongues of the Samway MCH. Figure 4 shows another block-diagram of a MCH with more functionality compared to the one used in the test setup.

Ports are grouped into fabrics. MCHs usually provide *switches* for a certain fabric.

In our test setup, the MCH contains

- a Gigabit Ethernet Switch on Fabric A going to ports 0 and 1 of each AMC.

- a PCI-express Gen3 Switch on fabrics D-G supporting up to 4 lanes, going to ports 4-7 of each AMC.

36 Exercise 6: MicroTCA

Figure 2. Block diagram of the Samway MCH.

Figure 4 shows the backplane of our test shelf, figure 5 shows a typical backplane of a larger shelf with 12 AMCs and redundant MCHs.

Take a look at the backplane with the bpppc command, which AMC has which connectivity? You can also have a look with the pcie.

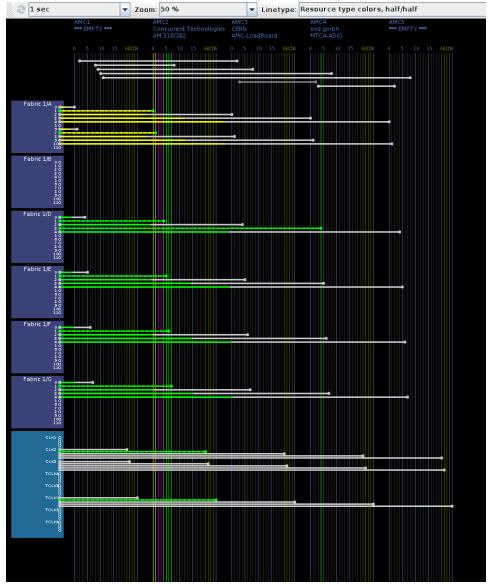

For some MCH dedicated tools are available to illustrate the backplane connectivity, figure 6 shows one such example, the NATView Backplane viewer.

Figure 3. Block Diagram of the NAT MCH.

**Figure 4.** Backplane of the ELMA blue eco shelf used in the exercise.

**Figure 5.** Backplane of a typical larger Micro-TCA crate with 12 AMCs. (not used in the exercise)

Figure 6. NAT Backplane viewer

#### **PCI Express**

The MCH in our test system provides a PCIe switch. Cards in the shelf may use it to communicate with each other. In our system, the Processor AMC communicates with the IO AMC via PCIe. Unlike its predecessor, PCI, PCI express is a serial link. Up to 32 serial links may be combined to form a link. Table 1 shows the speeds in Giga-transfers (GT) per second per lane. Physically, PCIe links are point-to-point, as opposed to a bus topology used in PCI. Data are transferred in packets (like in Ethernet) with data integrity checks, retransmissions and flow control. PCIe switches are used to connect multiple devices to a single controller (called *root complex* in PCIe). Despite all these differences in the lower link layers, PCI-express is software compatible to PCI.

Table 1. Speed of PCI-express

|       | per lane | per lane  |

|-------|----------|-----------|

| Gen-1 | 2.5 GT/s | 250 MB/s  |

| Gen-2 | 5 GT/s   | 500 MB/s  |

| Gen-3 | 8 GT/s   | 985 MB/s  |

| Gen-4 | 16 GT/s  | 1970 MB/s |

To discover the bus structure and devices, you can use the *lspci* tool.

For example, try: *lspci-tv* to display the bus in a tree structure or try options –*v* and -*vv* to display detailed information about the devices.

Try to locate the IO AMC. Find its bus address and its base address.

#### Hot Plugging (demo by your tutor)

In a Micro-TCA system, AMCs may be hot-plugged (i.e. exchanged without switching the shelf off). We will try hot-plugging the IO AMC card. Since the IO AMC is a PCI device connected to the Processor AMC, we have to let the Processor AMC know.

Together with the tutor, try these steps (you need to be *root* on the machine):

- show the PCI devices with *lspci*

- Pull gently on the black lever

- wait till the blue light is on

- pull the card out by its lever

- repeat *lspci* (did anything change?)

- push the card back in

- wait till the blue light is on

- push the black lever in

\_

- echo 1 > /sys/bus/pci/devices/[address]/remove

- (address is the address of this device: PCI bridge: PLX Technology, Inc. PEX 8111 PCI Express-to-PCI Bridge)

- repeat *lspci* (did anything change?)

- echo 1 > /sys/bus/pci/rescan

- repeat *lspci* (did anything change ?)

#### Build your own digital scope

Now let's get our hands dirty and do some programming. You will use the Analog-to-Digital converter on the IO/AMC to repeatedly sample an analog input channel and to display the waveform of the sampled signal. The A/D converter continuously samples its input at a programmable frequency. The acquired data may either be polled or transferred to host memory by Direst Memory Access (DMA).

- First have a look at the provided example program <code>adio\_scope.cpp</code> (in <code>/home/student/amc\_adio/src</code>). See how the program maps the address space of the IO AMC into the Processor AMC's memory space and how it then addresses the IO AMC's registers by simple read and write operations to a data structure. Run the program (from <code>/home/student/amc\_adio/bin</code>) and play with it. You can recompile it by running <code>make</code> in <code>/home/student/amc\_adio</code>.

- The scope should sample Analog Input 0 at 44.1 kHz. Have a look at the documentation (Hardware Manual) of the IO AMC and find out how to set up the ADC to sample at this frequency.

- First set up the timestamp counter to provide timestamps in microseconds (register DIVMODE)

- Then find out how fast you can poll a register of the IO AMC. Is polling fast enough to do a scope working at 44.1 kHz?

- Now set up the IO AMC to sample Analog input 1 at 44.1 kHz You will need to set up registers FGENAB and ADCMODE.

- After setting up the card, your program should acquire a few hundred samples from the ADC.

- Your program should produce a file with lines of two columns, containing a timestamp in microseconds and the voltage in volts (separated by a space). You can start from the routine *acquire\_shot()* which already provides parts of the solution.

- A ROOT program to plot you file is available. So you don't need to worry about producing the graphics. The program will let you choose the file name to plot.

```

root -l

root [0] .x /home/student/gui_cint.cpp

```

- As an input signal, you can connect the provided head-phone jack to your smart phone and play some music (you'll have to turn up the volume). Or you download a function generator onto your phone – for example

RADONSOFT Signal Generator. (No smart phone in your group? Ask you tutor.)

#### References (.pdf files available in /ISOTDAQ/doc)

- Short intro to uTCA. *MicroTCA\_ShortOverview.pdf*

- <a href="http://en.wikipedia.org/wiki/PCI">http://en.wikipedia.org/wiki/PCI</a> Express PCIExpressWikipedia.pdf

- More info about PCIe: <a href="http://xillybus.com/tutorials/pci-express-tlp-pcie-primer-tutorial-guide-1">http://xillybus.com/tutorials/pci-express-tlp-pcie-primer-tutorial-guide-1</a> PCIExpress\_Xillybus[1-3].pdf

- Info about the shelf: *ELMA\_BlueEco\_Shelf.pdf*

- MCH doc: Samway\_MCH\_Usermanual\_Rev\_1.6

- Manual for the IO AMC: HardwareManual\_IO\_AMC.pdf

#### **LabView Programming**

#### Exercise 7

# Introduction

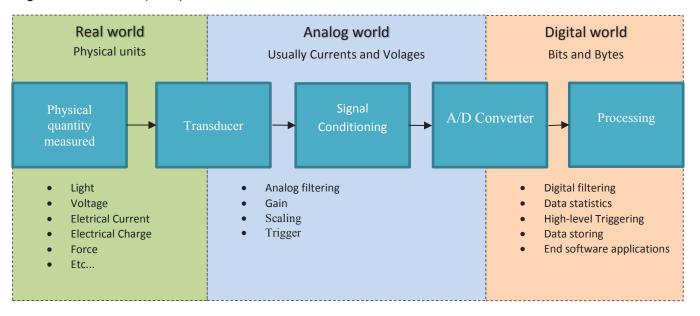

The following block diagram shows the main components of an electronic measurement system:

Sensor

Analog signal conditioning

ADC

Digital signal Conditioning, preprocessing

**DSP**

Analog world

In most cases the function of the components are the same. The sensor converts the physical value (temperature, pressure, acceleration...) to an electrical signal. After the conditioning of the signal and converting it to the digital space the system process and store the digital values. The numbers and the physical types of the measured signals can be different and processing algorithm as well. If we could handle all types of signals we would be able to solve any measuring problem. Additionally if it was also true for the actuators, we would be able to handle all controlling problems. This is the goal of the modular electronic instrumentation.

National Instruments has been developing measurement equipment since the '80s. They provide general, programmable interface modules: for analog/digital inputs/outputs (programmable ADC/DAC modules with programmable signal conditioning), for standard communication interfaces (Ethernet, CAN/LIN, PROFIBUS, PCI...). They provide a development environment to communicate with these modules with a PC. The software environment uses a graphical programming language.

During this laboratory we are using the following equipment. The modules place in the NI Compact DAQ chassis (cDAQ-9178). This chassis can communicate with the PC (LAN or USB) and control the placed-in modules. The analog input module (NI 9211) contains 24 bit delta-sigma ADCs and 4 differential channels. This module can handle the thermo-couple sensors. We are using an analog input and a digital output module as well.

The chassis contains the following, programmable component: four 32 bit general purpose counters, clock generators, FIFO for analog/digital inputs (with 127 depth per slot), FIFO for digital outputs (2047 samples), clock generators (base clock: 20 MHz, 10 MHz, 100 kHz, divisors: 1 to 16), digital trigger circuit.

By the graphical programming environment we can program and control the modules. We can visualize our acquired data and do calculations. The data processing with this cDAQ chassis runs on the processor of our desktop PC.

Try to answer the following questions:

- If this chassis contains only some counters and FIFOs why does it cost approx 1000 €?

- What is the advantage of this modularity, developing a measurement system?

- What would be the problem is we would like to use this system as a control system or as a real-time signal processing application? How would you solve this problem?

- For which application would you choose this configuration? Why?

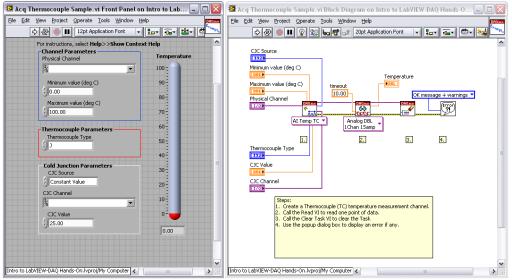

# Exercise 1: Take a Basic Measurement with CompactDAQ

The purpose of this exercise is to use LabVIEW and NI CompactDAQ to quickly set up a program to acquire temperature data.

#### Set up the Hardware

- 1. Make sure that the NI CompactDAQ chassis (cDAQ-9178) is powered on.

- 2. Connect the chassis to the PC using the USB cable.

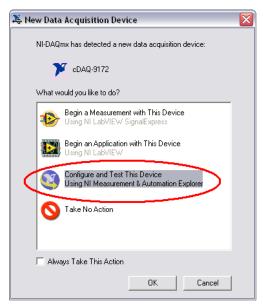

- 3. The NI-DAQmx driver installed on the PC automatically detects the chassis and brings up the following window.

4. Click on Configure and Test This Device Using NI Measurement & Automation Explorer. Note: NI Measurement & Automation Explorer is a configuration utility for all National Instruments hardware.

- 5. The Devices and Interfaces section under My System shows all the National Instruments devices installed and configured on your PC. The NI-DAQmx Devices folder shows all the NI-DAQmx compatible devices. By default, the NI CompactDAQ chassis NI cDAQ-9178 shows up with the name "cDAQ1".

- 6. This section of MAX also shows the installed modules as well as empty slots in the CompactDAQ chassis.

- 7. Right-click on NI cDAQ-9178 and click on Self-Test.

8. The device passes the self-test, which means it has initialized properly and is ready to be used in your LabVIEW application.

#### **Program LabVIEW Application**

- 9. Create a new VI from the Project Explorer. Right click on the Exercises folder and select New»

- VI. Once opened, Save the VI in the Exercise folder under the name "1-Basic Measurement.vi."

- 10. Press <Ctrl +T> to tile front panel and block diagram windows.

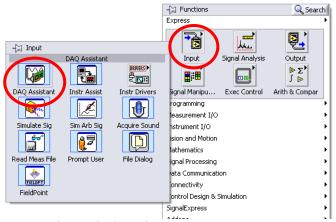

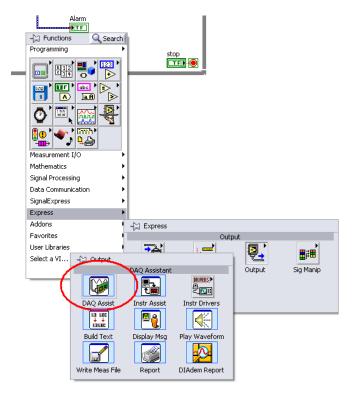

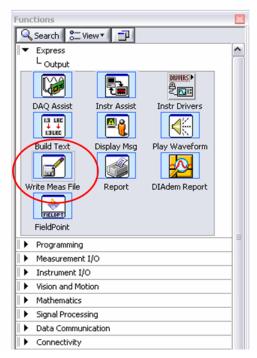

- 11. Pull up the Functions Palette by right-clicking on the white space on the LabVIEW block diagram window.

- 12. Move your mouse over the **Express» Input** palette, and click the DAQ Assistant Express VI. Left-click on the empty space to place it on the block diagram.

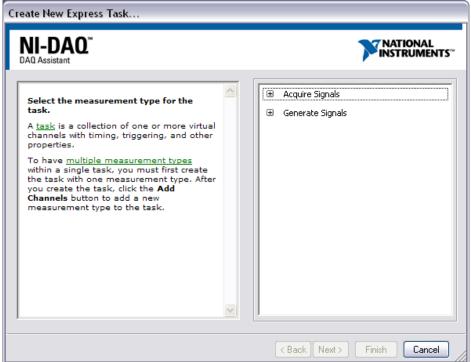

13. The Create New Express Task... window then appears:

- 14. To configure a temperature measurement application with a thermocouple, click on **Acquire Signals» Analog Input» Temperature» Thermocouple**. Click the + sign next to the cDAQ1Mod1 (NI 9211), highlight channel ai0, and click Finish. This adds a physical channel to your measurement task.

- 15. Change the CJC Source to Built In and Acquisition Mode to Continuous Samples. Click the Run button. You will see the temperature readings from the thermocouple in test panel window.

- 16. Click Stop and then click OK to close the Express block configuration window to return to the LabVIEW block diagram.

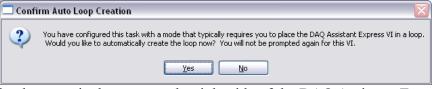

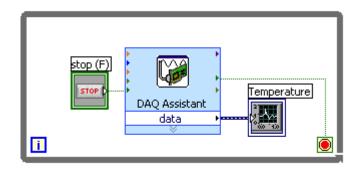

- 17. LabVIEW automatically creates the code for this measurement task. Click Yes to automatically create a While Loop.

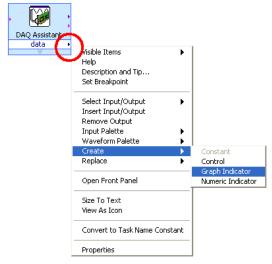

18. Right-click the data terminal output on the right side of the DAQ Assistant Express VI and select **Create» Graph** Indicator. Rename "Waveform Graph" to Temperature.

19. Notice that a graph indicator is placed on the front panel.

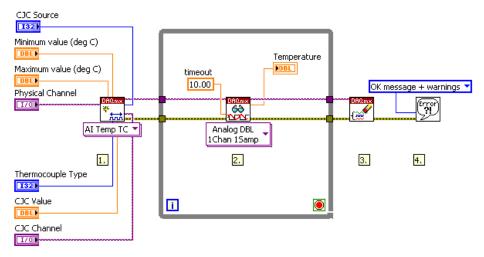

20. Your block diagram should now look like the figure below. The while loop automatically adds a stop button to your front panel that allows you to stop the execution of the loop.

**Additional Steps** Express VIs make creating basic applications very easy. Their configuration dialogs allow you to set parameter and customize inputs and outputs based on your application requirements. However, to optimize your DAQ application's performance and allow for greater control you should use standard DAQmx driver VIs. Right Click on block diagram Functions» Measurement I/O Palette» NI-DAQmx.

- 20. Before you generate DAQmx code you need to remove all the code that was automatically created by the Express VI. Right click on the while loop and select "Remove While Loop." Then click on the Stop button control, and press the Delete key to remove the Stop button. Repeat actions for Temperature Graph as well as any additional wires that may remain. You can press <Control + B> to remove all unconnected wires from a block diagram.

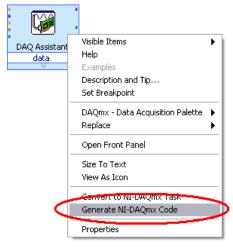

- 21. Convert Express VI code to standard VIs. While not all Express VIs can be automatically converted to standard VIs, the DAQ Assistant can. This will allow for greater application control and customization. Right-click on the DAQ Assistant Express VI you created in this exercise and select "Generate NI-DAQmx Code."

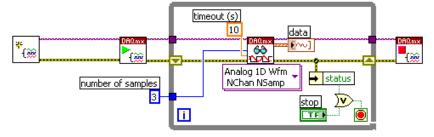

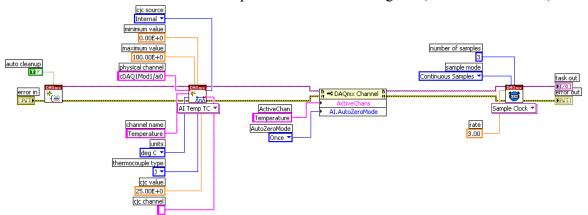

Your block diagram should now appear something like this:

The Express VI has been replaced by two VIs. We'll examine their functionality in the following

steps.

- 22. Open Context Help by clicking on the Context Help icon on the upper right corner of the block diagram. Hover your cursor over each VI and examine their descriptions and wiring diagram.

- 23. DAQmx Read.vi reads data based on the parameters it receives from the currently untitled VI on the far left.

- 24. Double-click on the untitled VI and open that VI's block diagram (code shown below).

All the parameters that are wired as inputs to the different DAQmx setup VIs reflect the setting you originally configured in the DAQ Assistant Express VI.

Note: By moving these parameter and setup VIs onto the block diagram, you can now programmatically change their values without having to stop your application and open the Express VI configuration dialog, saving development time and possibly optimizing performance by eliminating unnecessary settings depending on your application. Using the LabVIEW Example Finder

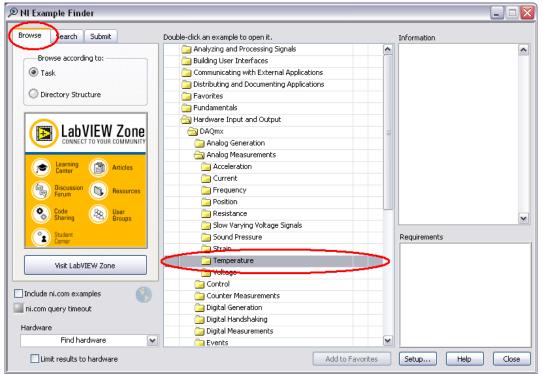

The LabVIEW Example Finder provides hundreds of example application to use as reference or as the starting point for your application.

- 25. Open the LabVIEW Example Finder to find DAQ examples that use DAQmx standard VIs. Go to **Help» Find Examples...** to launch the LabVIEW Example Finder.

- 26. Browse to the DAQmx Analog Measurements folder from the Browse tab at **Hardware Input** and Output» DAQmx» Analog Measurements.

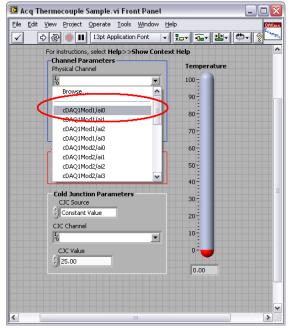

27. The following VI will then appear:

28. Set the Physical Channel to match the CompactDAQ chassis channel and run the application. Expand the physical channel control from the Front Panel and select cDAQ1Mod1/ai0.

Press the Run button several times while holding and releasing the thermocouple on the CompactDAQ chassis and observe the value change on the front panel.

- 29. Open the block diagram and examine the code. This VI only uses standard VIs instead of Express VIs, which allows much more customization of inputs and run-time configuration. Acq Thermocouple Sample.vi has no while loop to allow for continuous execution, and the remaining steps of this exercise will focus on adding that functionality.

- 30. Add a while loop and Stop button to Acq Thermocouple Sample.vi. Right-click on the block diagram to bring up the Functions palette. Find the While Loop on the Programming» Structures palette and drag a while loop over the DAQmx Read.vi. You may need to spread the VIs across the block diagram so that there is room. You can create additional space by holding the Control key and dragging a box on the block diagram or front panel.

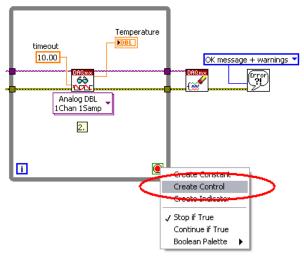

Right click on the While Loop's Conditional terminal and select "Create Control." This automatically wires a Stop button to the terminal.

Notice that the Stop button has appeared on the front panel.

- 31. Run the VI. Acq Thermocouple Sample.vi now runs continuously.

- 32. Save the customized example VI to the Project. Go to File» Save As..., select Copy» Substitute Copy for Original and name the VI "Thermocouple Customized Example.vi." Save this VI. This allows for further development without overwriting the LabVIEW example. End of Exercise 1

# Exercise 2: Add Analysis and Digital Output to the DAQ Application

#### Set up Hardware

1. Confirm that the CompactDAQ chassis is powered on and connected to the PC via the USB cable. If not, or if it is not behaving as expected, repeat steps #1-8 from Exercise #1

#### LabVIEW Application - Compare signal to user-defined alarm

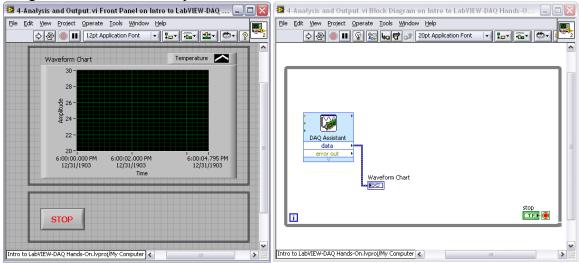

2. Exercise 2 is functionally the same as the end result of Exercise 1. You can open Exercise 1 to synchronize with the illustrations in this section. Open 1-Analysis and Output.vi from the Exercises folder in the Project explorer. The VI will appear like the image below, with additional space on the block diagram to add functionality:

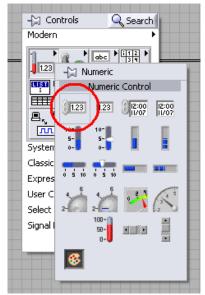

3. Create an alarm that signals if acquired temperature goes above a user-defined level. On the front panel, right-click to open the Controls palette Programming» Numeric and place a numeric control on the front panel.

- 4. Change the numeric control's name to "Alarm Level." Double-click on the control's label and replace the generic text with "Alarm Level"

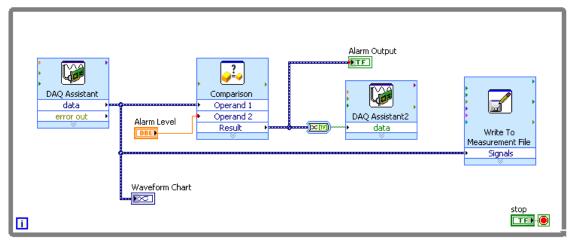

- 6. Use the Comparison Express VI to compare the acquired temperature signal with the Alarm Level control. Switch to the block diagram, right-click on an empty space and open the Functions palette. Place the Comparison Express VI on the block diagram from Functions» Express» Arithmetic & Comparison» Comparison.

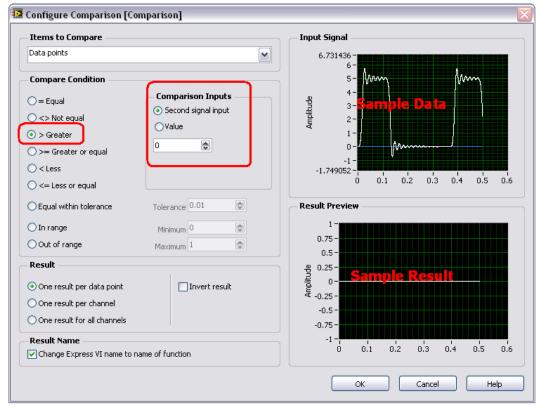

7. Once placed on the block diagram, the Comparison Express VI's configuration dialog will appear.

Select "> Greater" in the Compare Condition section and "Second signal input" from the Comparison Inputs section then click OK.

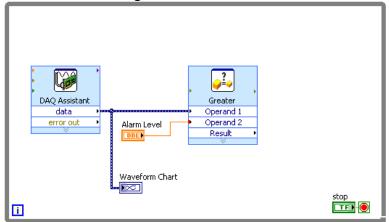

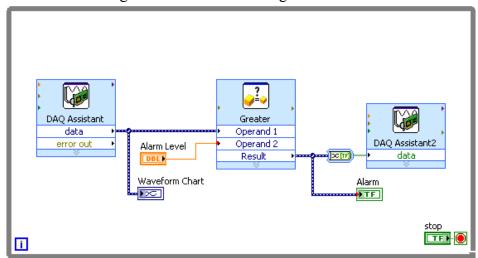

8. Connect the acquired temperature data and Alarm Level inputs to the Comparison Express VI. Hover over the output of the DAQ Assistant until the spool icon appears on your cursor, then left-click and drag you mouse to the Operand 1 input on the Comparison Express VI. Perform the same hover, drag and connect to wire the Alarm Level control and the Operand 2 input on the Comparison Express VI. Your block diagram should now look like this:

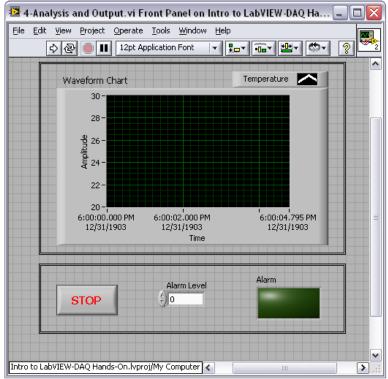

9. Display the result of the Comparison Express VI on the front panel. On the front panel, right click, open the Controls palette and add a Square LED indicator. The square LED is found at **Controls» Modern» Boolean**. Resize the Square LED so that it is easier to see and rename it "Alarm." Your front panel should look like this:

On the block diagram, wire the output of the Comparison Express VI to the input of the Alarm indicator's terminal.

10. Run the application. Press the Run button and then change the Alarm Level control to some level above the current acquired temperature signal. Hold the thermocouple until the temperature exceeds the Alarm Level value. The Alarm LED turns on when the acquired temperature signal goes above the level set on the front panel.

#### **Output Alarm to CompactDAQ Chassis**

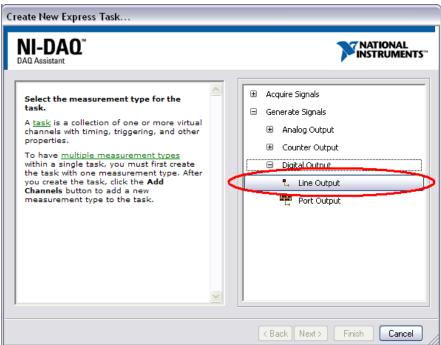

11. Use another DAQ Assistant Express VI to output Alarm's status to the CompactDAQ's 9474 module. Open the Functions palette on the block diagram and find the DAQ Assistant Express VI at Functions» Express» Output.

<picture of palette w/ DA circled>

12. Select Generate Signals» Digital Output» Line Output from the Create New Express Task... window.

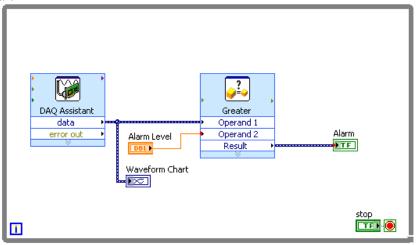

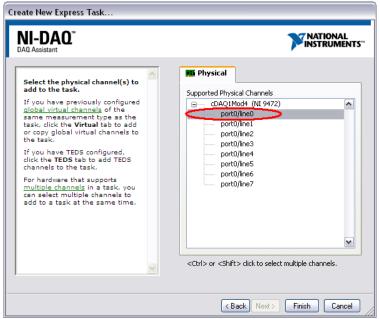

13. Select the physical channel you want to use as output. Expand the + sign next to cDAQ1Mod4 in the following window and select port0/line0.

- 14. Press OK in the DAQ Assistant window that appears, since all of its settings are correct for the application.

- 15. Create an additional wire that connects the Comparison Express VI's Result output to the **data** input on the new DAQ Assistant Express VI. A Convert from Dynamic Data function appears automatically. LabVIEW will always try to coerce unlike data types when two nodes are wired together. In this case, the output of the Compare Express VI is a Dynamic Data type, and the input of the DAQ Assistant is Boolean. LabVIEW placed the Convert from Dynamic Data node in between the two nodes so they could be connected. You can double-click the Convert from Dynamic Data to view its configuration. Your block diagram should now look like this:

- 16. Run the VI. Press the Run button. Notice that the LED bank on the CompactDAQ 9474 module turns on and off to match Alarm's value on the front panel.

- 17. Save and close the VI.

#### **End of Exercise 2**

# **Exercise 3: Writing Data to File with LabVIEW**

- 1. In the Exercise folder in the Project Explorer, open 2-Analysis and Output.vi. We will use the final program from the last exercise as the beginning of this exercise.

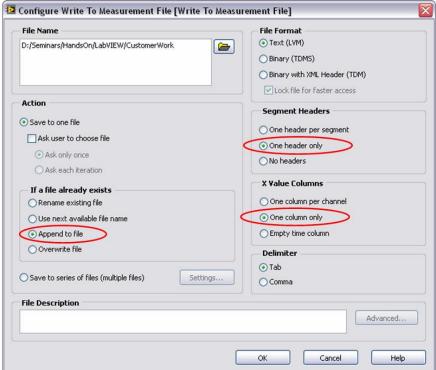

- 2. Right-click on the block diagram and select Functions» Express» Output» Write to Measurement File and place it inside the While Loop on the block diagram.

3. A configuration window will appear. Configure the window as shown below and click OK.

- 4. Wire the output of the DAQ Assistant Express VI to the input of the Write to Measurement File Express VI.

- 5. Your block diagram should now resemble the following figure.

- 6. Save the VI by using the **File» Save As...** menu, select the **Copy» Open Additional Copy** and name it 3-Write to File.vi.

- 7. Run the VI momentarily and press STOP to stop the VI.

- 8. Your file will be created in the folder specified.

- 9. Open the file using Microsoft Office Excel or Notepad. Review the header and temperature data saved in the file.

- 10. Close the data file and the LabVIEW VI.

#### **End of Exercise**

# Exercise 4: Generate, Acquire, Analyze and Display

Generate a sine waveform using the analog output module. Try to check the signal with an oscilloscope. Acquire the sine waveform using the analog input module. Perform the appropriate analysis on the acquired waveform to figure out the frequency of the acquired waveform. Finally display the acquired waveform and its frequency. Try to play with the Nyquist-Shannon sampling theorem.

This is a challenge exercise and step-by-step instructions are not provided, but rather the end goal is given. It is up to you to figure out how to come up with the program to achieve the given task.

#### ADC basics for TDAQ (Lab 8)

Manoel Barros Marin (manoel.barros.marin@cern.ch, tutor)

## Concepts of this lab

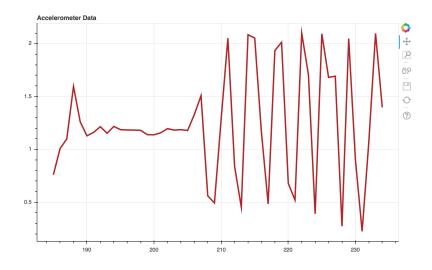

Figure 1 below shows the generic signal flow of a Data AcQusition (DAQ) system to perform Analog to Digital Conversions (ADC).

Figure 1- Basic ADC DAQ chain

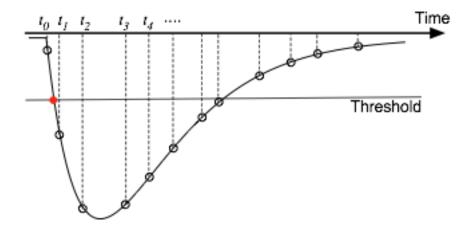

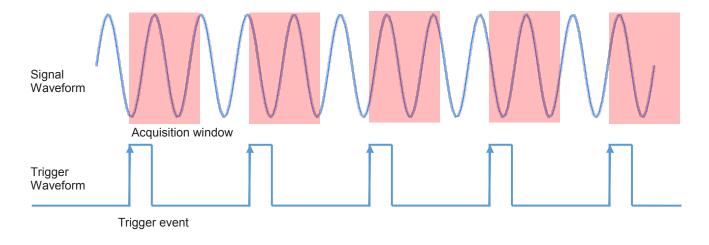

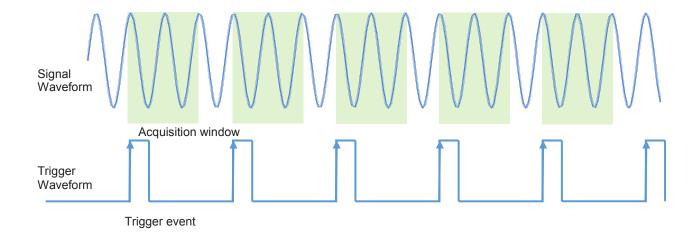

The scope of this laboratory experience is to understand and experiment with the following components of a Data AcQuisition system:

- 1. Triggers:

- 1.1. External triggers: accelerator like type of triggers

- 1.2. Triggering on the signal: astroparticle like type of triggers

- 2. Analog to Digital Converter (ADC): we will try to understand fundamental parameters that come into play when measuring with ADC; as for example its resolution, speed, bandwidth, acquisition window, etc.

## Lab setup

Figure 2 below depicts the setup for Lab8.

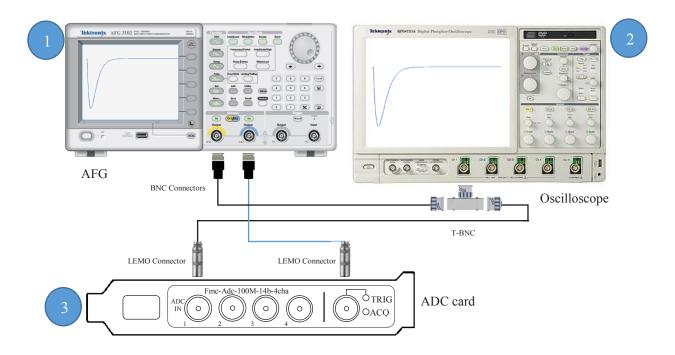

Figure 2 - Equipment setup

- 1. Tektronix AFG3252: Arbitrary Function Generator, is the **input** of our system

- 2. Tektronix DPO70404C: Oscilloscope, it the **monitor** of our system (to cross-check that the signals fed to the system are truly what intended)

- 3. SPEC+FMC ADC card plus host PC: this is the core ADC DAQ

- 3.1. FPGA Mezzanine Card (FMC) ADC: <a href="http://www.ohwr.org/projects/fmc-adc-100m14b4cha">http://www.ohwr.org/projects/fmc-adc-100m14b4cha</a>

- 3.2. Simple PCI Express Carrier (SPEC) card: http://www.ohwr.org/projects/spec/wiki

- 3.3. Linux based host PC

## Introduction to Analog to Digital Conversion (ADC)

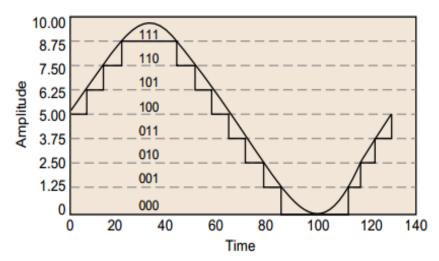

An Analog to Digital Converter (also known as "digitizer") is a device which converts the level of an analogue signal into an integer number which is closest to the real value of the signal in terms of ratio. There is a limit for the number of choices of this integer which is determined by the number of bits used for the digitization.

Example: We have a voltage signal whose range is [0 - 10] Volt, and we have a digitizer which has just 3 bits. We can have 8 different integer numbers with 3 bits. Each of these numbers will correspond to a voltage. See table below.

| Voltage     | Digitizer bits | Integer |

|-------------|----------------|---------|

| 0.00 - 1.25 | 000            | 0       |

| 1.25 – 2.50 | 001            | 1       |

| 2.50 - 3.75 | 010            | 2       |

| 3.75 – 5.00 | 011            | 3       |

| 5.00 - 6.25  | 100 | 4 |

|--------------|-----|---|

| 6.25 – 7.50  | 101 | 5 |

| 7.50 – 8.75  | 110 | 6 |

| 8.75 – 10.00 | 111 | 7 |

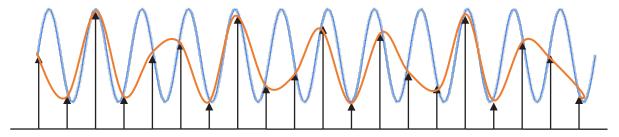

This kind of conversion is performed at regular intervals (**samples**), and the repetition (frequency, Hz) is called **sampling frequency** (normally expressed in samples per seconds). Thus, digitization is not only performed in the signal domain, but also in the time domain.

Also note that to improve the precision of the measurement one should:

- Increase the number of bits, so each corresponding range is small with respect to the signal to be sampled

- Sampling should be done at the proper frequency (see Nyquist frequency); and even more

importantly, a precise sampling clock should be used, such that the deviation between consecutive

samples is kept as constant as possible.

If you are interested in more details about ADC parameters, please check: <a href="http://www.analog.com/en/analog-to-digital-converters/products/index.html">http://www.analog.com/en/analog-to-digital-converters/products/index.html</a>

If are interested in understanding more in detail the importance of clock stability (jitter), please check: <a href="http://anlage.umd.edu/Microwave%20Measurements%20for%20Personal%20Web%20Site/Tek%20Intro%20to%20Jitter%2061W">http://anlage.umd.edu/Microwave%20Measurements%20for%20Personal%20Web%20Site/Tek%20Intro%20to%20Jitter%2061W</a> 18897 1.pdf

The ADC card we will be using has 14 bit voltage resolution and a typical conversion time of 10 ns (100 MS/s). In this exercise, we will operate the ADC in order to understand and push its limits.

#### The Measurement

Qualify in the best possible way a set of signals mimicking real experimental equipment. The tutors will provide some pre-cooked ones (sine waves, positive pulses, scintillator like pulses) but you can try to think of your real world input.

In general terms, a digitization process is characterized by the following:

- Signal range: how much the signal can vary to be correctly interpreted by the device (voltage)

- Sampling frequency: the rate at which it can convert an analogue value to a discrete signal (bits)

- Latency: How long does the device takes to finalize the acquisition process in the chain (time)

- Noises: physical quantities responsible for the signal deterioration (e.g. added noise, intrinsic noise, quantization errors, etc.)

The best measurement is achieved by understanding and controlling those parameters. **The designers (so YOU) have to decide how to setup your TDAQ:** choose a trigger type, define the acquisition windows, find the signal in the window, maximize the scaling for increasing the accuracy of the measurement, etc.

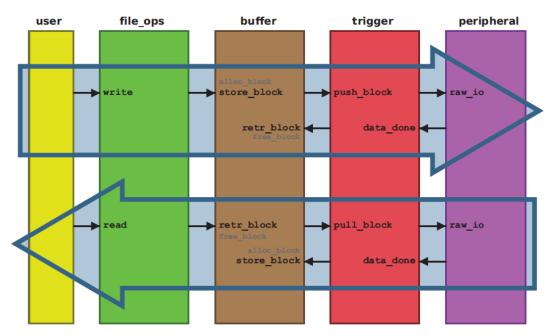

#### Architecture of a Linux Device Driver for the PCIe Card

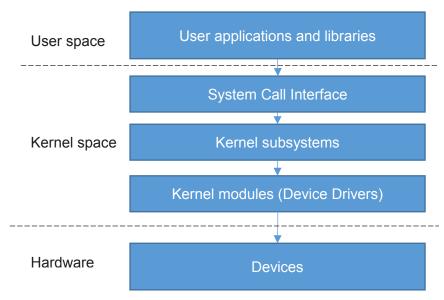

Before running the DAQ system, an **overview on the communication between the software and the hardware layers and an introduction to the role of device drivers**, is fundamental to understand. *Figure 3* shows a simplified diagram of the Layers of a Linux Operating System (OS).

Figure 3- Layers of a Linux OS

The basic control is on the hardware peripheral itself. The lowest level software for this system resides in the kernel of the OS as a "device driver." There are certain control/status registers on the ADC card. These registers can be accessed just like a regular memory access in a C program.

As seen earlier in this document, in our context, the ADC DAQ hardware used is composed of two electronic boards: the SPEC carrier board and the FMC ADC module. The first board is attached directly to a PCIe slot connector on the PC, and is the host for the ADC module. The SPEC card acts as a bridge for the electrical signals of the ADC FMC to be interfaced and converted to PCIe. For the scope of this lab, the "bridging" is done by some "black box" electronics. Thus from a software perspective, one kernel module is instantiated to use the SPEC card, another one for the FMC ADC module.