# Charge Collection Efficiency on Irradiated Pixels

Natalie Krzyzanowski 09.18.09

### Purpose

- The purpose of this study is to determine how efficiently chips can collect charge after being exposed to fluences ranging from 3.2E14 – 5.1E15.

- We wanted to see at what point the chips yielded inadequate results, and how long this took.

- The control was the unirradiated chip, from which charge was also collected. The source used was Sr-90.

## Taking Data

- Chips are cooled down to -25°C with better cold box (before, at -15°C)

- Each chip is calibrated with PreTest and other calibration test.

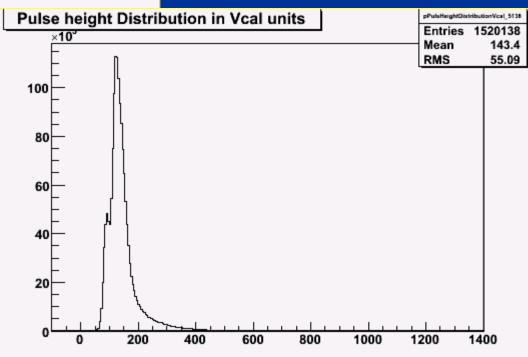

- A value of Vcal trim is set. Normally this is 45 V, but for higher fluences 55 V works best as shown from improved results.

- Depending on the leakage current, data and S-curves are taken for bias voltages ranging between 200-800 V.

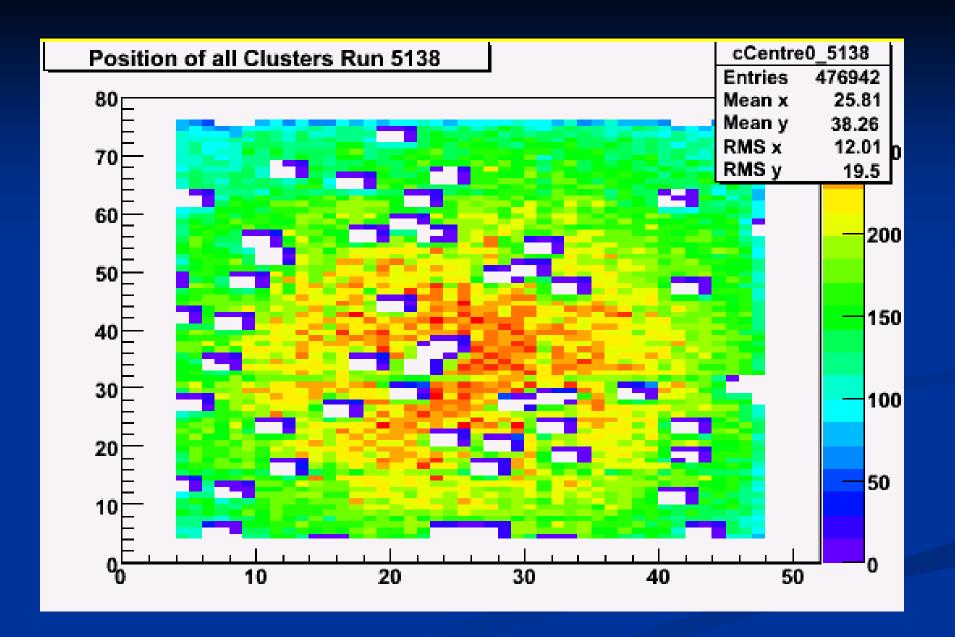

- Data is analyzed using analysis code.

### **Progress**

- Ran complete tests on several chips of varying fluences: mainly 5.1E15

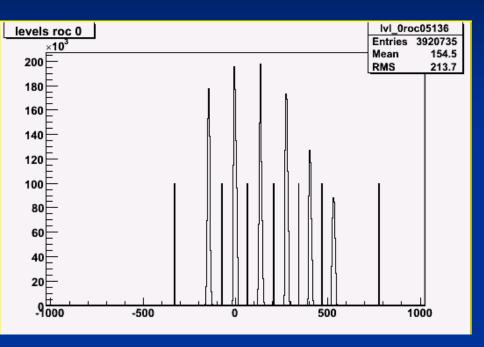

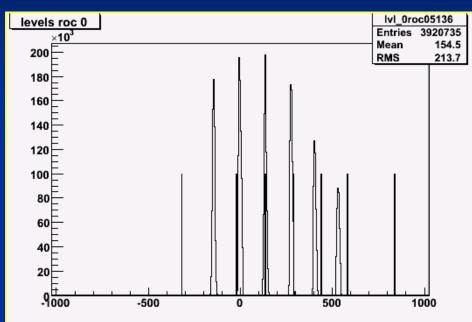

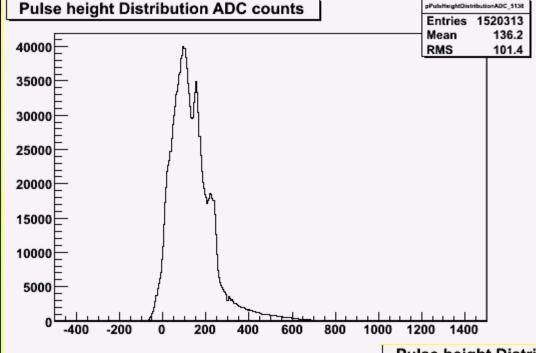

- Analysis consisted of determining whether fits looked like certain distributions; if not, something needed to be fixed

- We figured out how to fix bad address levels and recorded this in the Twiki

Before After

LandauDistribution for ADC graph

# Hikes