### **Enhancement Presentation**

Carlos Abellan Orsay December 17th, 2009

### **Enhancement Presentation**

- Summary

- The analogical mezzanine prototype

- Ideas

- Schematics

- Physical dimensions

- Connectors

- Discrete OP Amp simulations

- Previous problems

- Calculations

- Results

- Ideas to discuss

- About noise and grounding

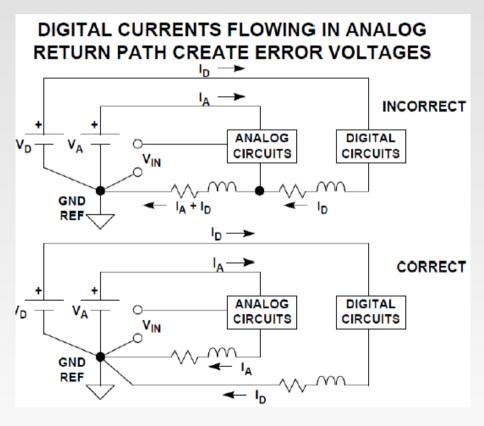

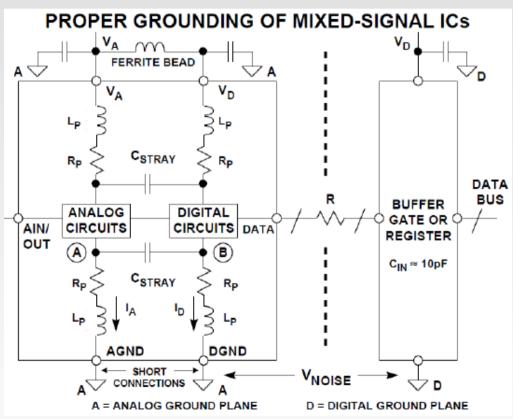

- Different strategies with grounding

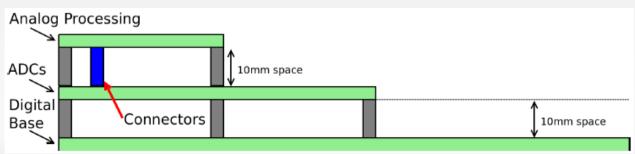

- About connectivity

- Flexibility to test any analog architecture

- About delay evaluation

- Flexibility to evaluate all possible delay scenarios

#### Noise and grounding

- Connectivity

- Flexibility to test any analogical architecture

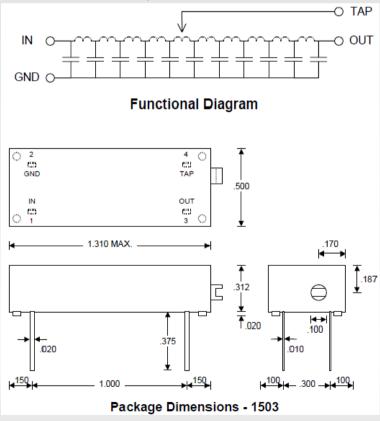

Tyco 619134-1

Char. Imp. 50 Ohms

Freq. Range Up to 6 GHz

Return Loss –20dB min.

Shield Effect. –60 dB min.

Resistance < 70 mOhm

#### Ratings

Voltage: 125 volts AC

• DC Current: 4.8 A max.

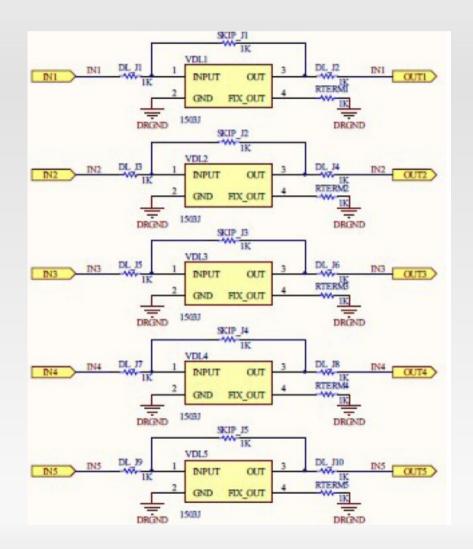

- Delay evaluation

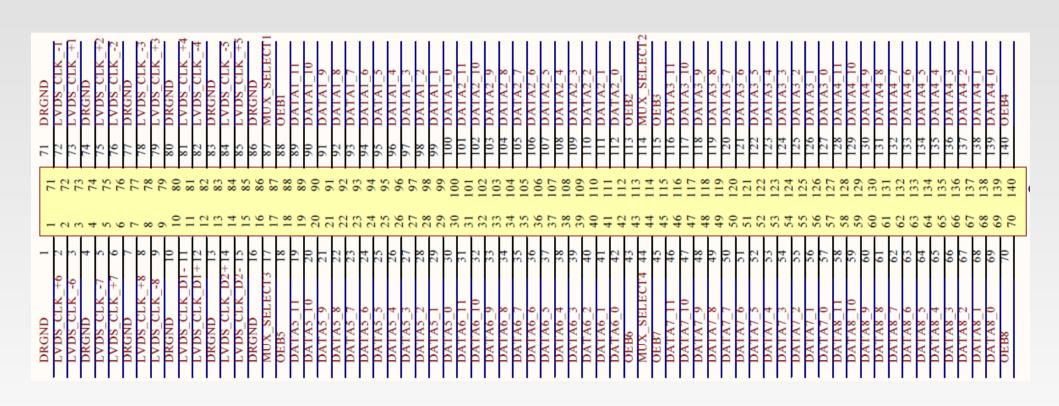

- 2xClock, 2x Output Enable, Mux Select

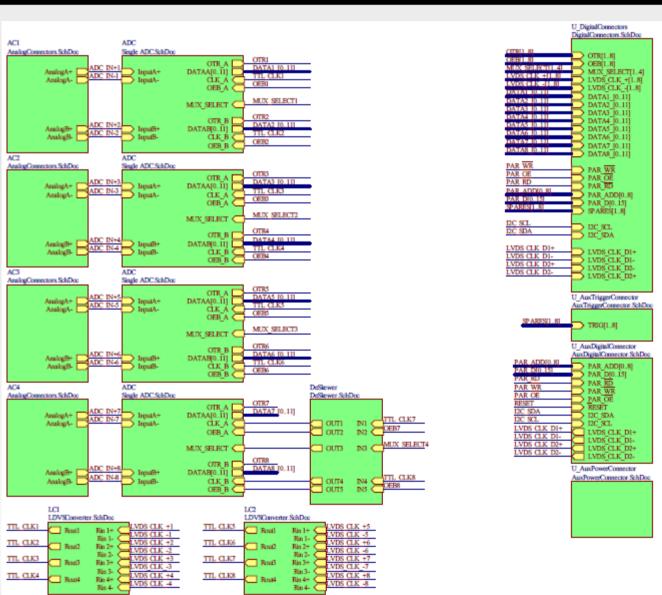

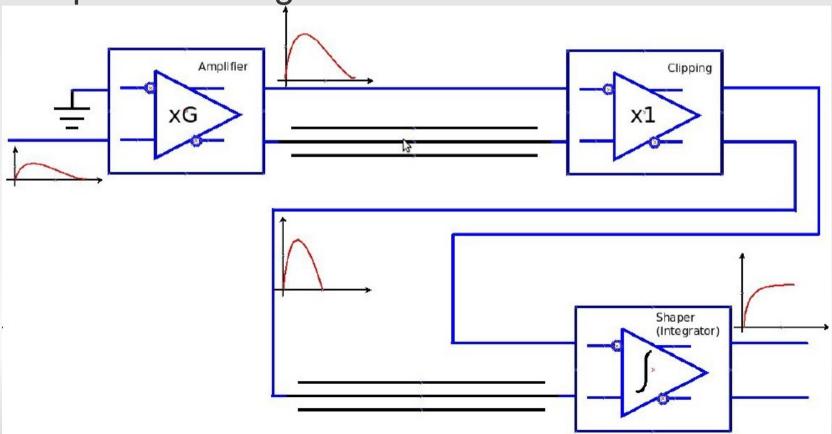

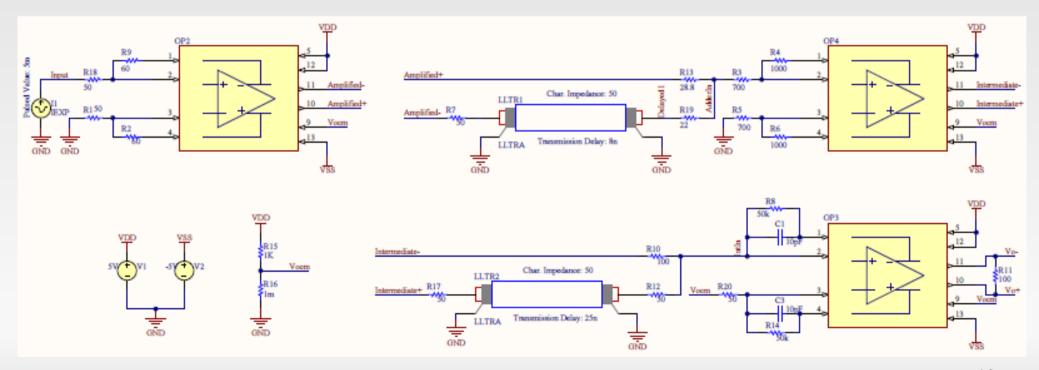

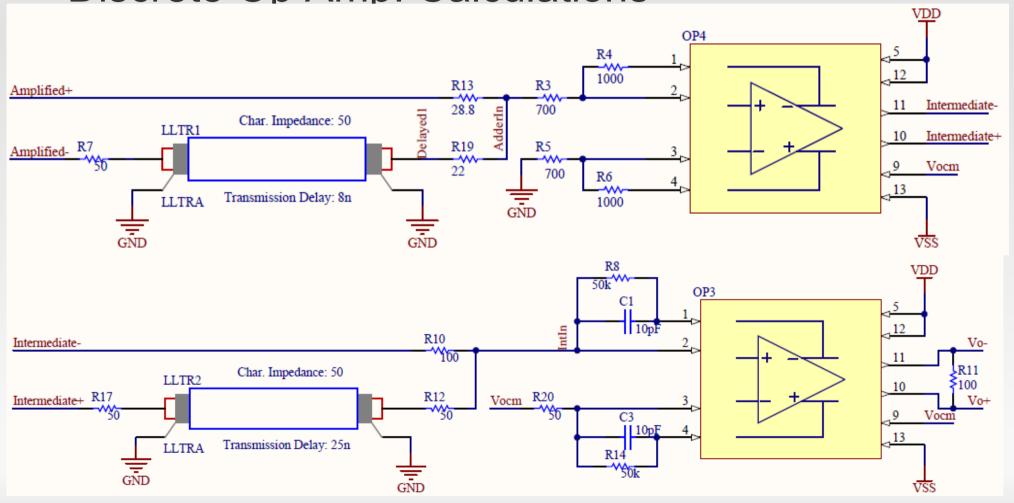

#### Schematics

- 4 Instances of 2 channels each

- 1 With Delay Control

- Clock Conversion to single ended

- Digital Connector

- Analogical Connector

- Auxiliary Connectors

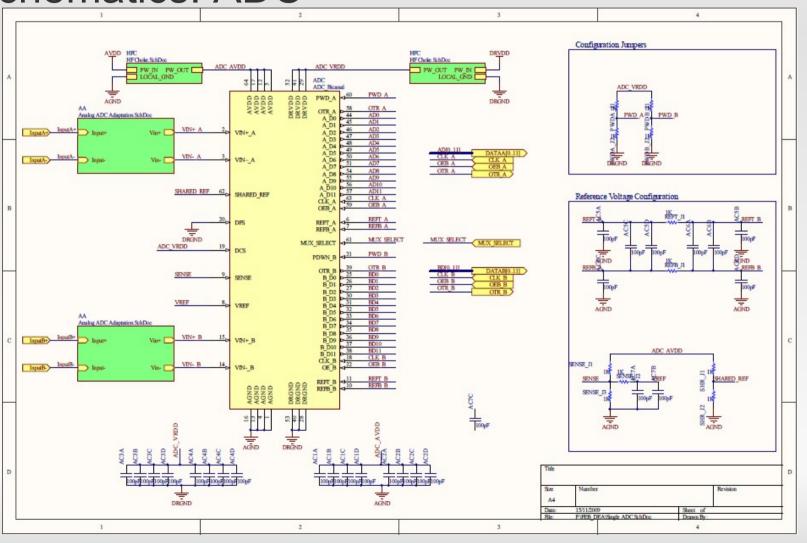

Schematics: ADC

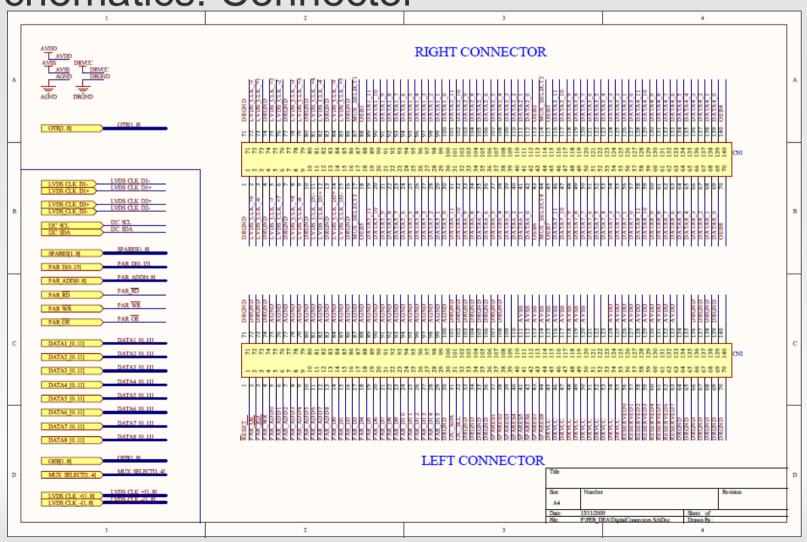

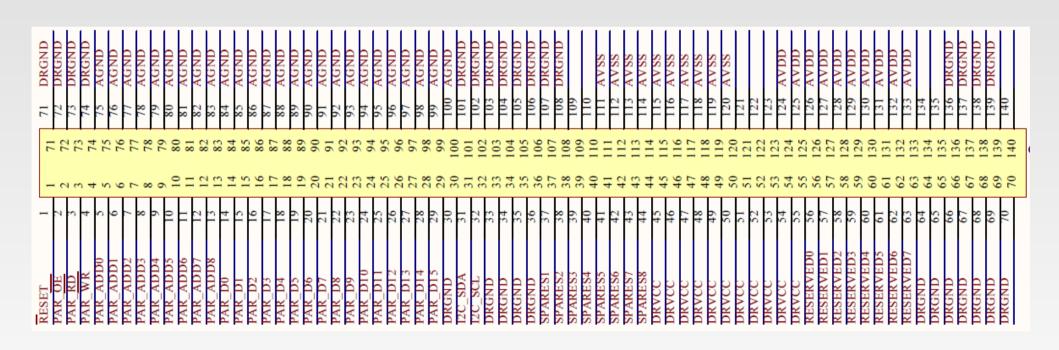

Schematics: Connector

Schematics: Right Connector

Schematics: Left Connector

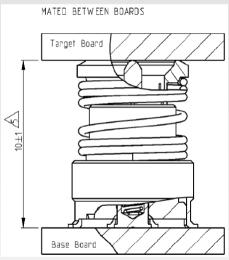

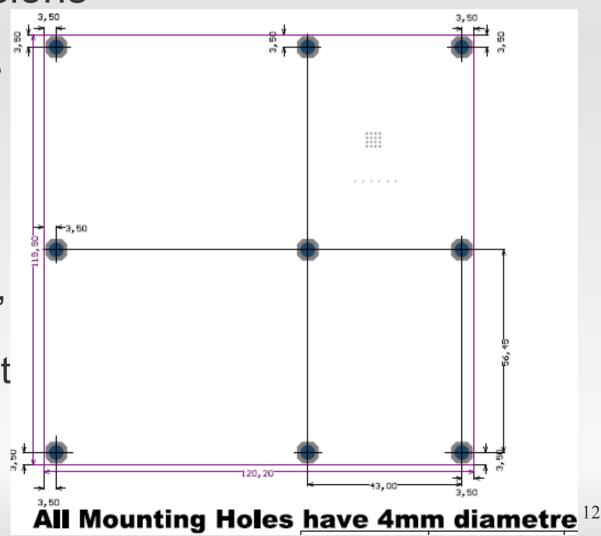

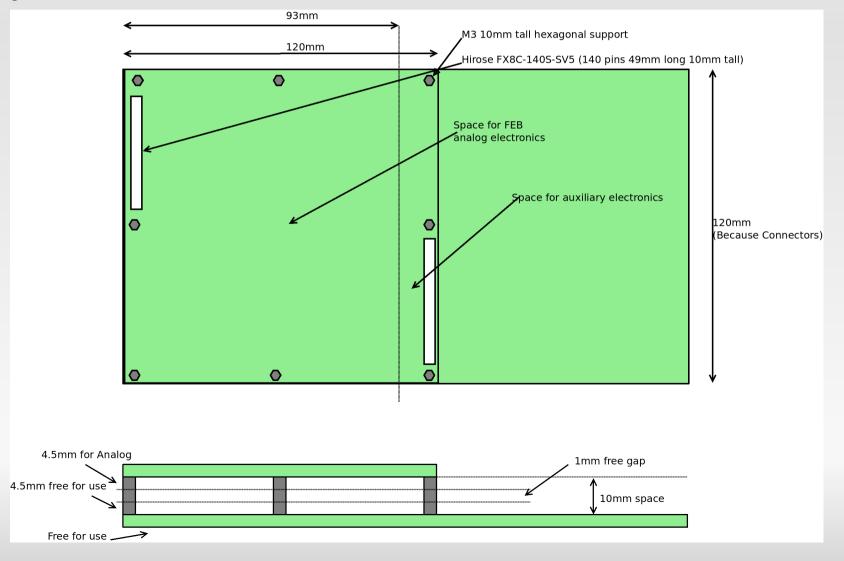

Physical Dimensions

- Mounting Holes for their use if needed.

- Digital connectors must be placed, not already agreed on exact position and direction.

Physical Dimensions

- Connectors

- Hirose FX8C-140S-SV5

- 10 mm tall

- 49 mm long

- 140 pins

- Male and female, not yet agreed on which to use on the digital motherboard and which on the analogical mezzanine.

#### **Enhancement Presentation**

- Summary

- The analogical mezzanine prototype

- Ideas

- Schematics

- Physical dimensions

- Connectors

- Discrete OP Amp simulations

- Previous problems

- Calculations

- Results

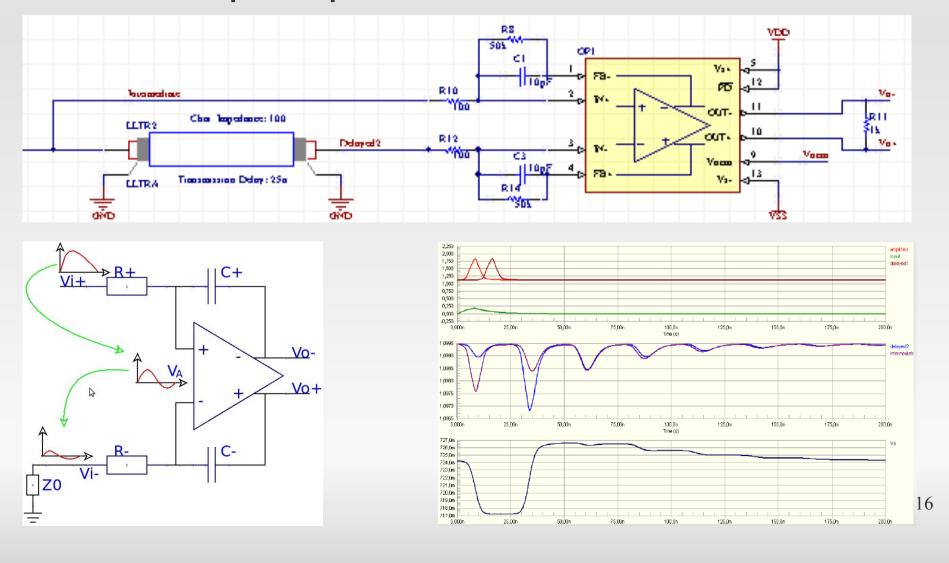

Discrete Op Amp: Previous Problems

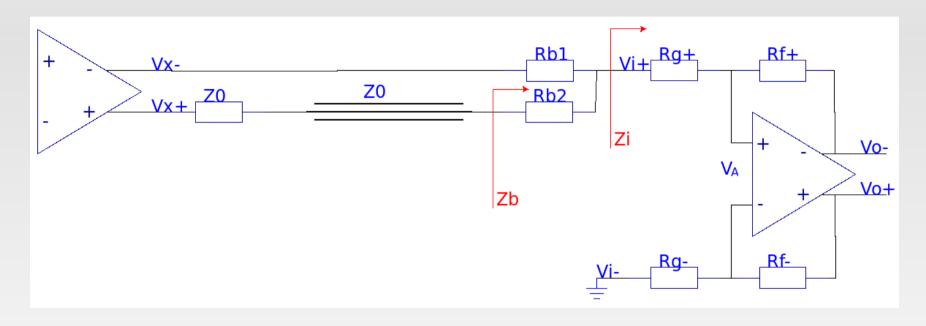

- Discrete Op Amp: Previous Problems

- The previous OP Amp must also be differential in order to cut the feedback. The same happends to the previous stage.

Discrete Op Amp: Calculations

Zb=Z0; Same contribution of both outputs;

$$\begin{aligned} \text{Vi} &== \text{V1} \star \frac{\text{Par}[\,(\text{R2} + \text{Z0})\,\,,\,\,\,\text{Zi}\,]}{\text{Par}[\,(\text{R2} + \text{Z0})\,\,,\,\,\,\text{Zi}\,] + \text{R1}} + \text{V2} \star \frac{\text{Par}[\,\text{R1}\,\,,\,\,\,\text{Zi}\,]}{2 \star \text{Z0}} \,; \\ \\ &\frac{\frac{\text{Par}[\,\text{R1}\,\,,\,\,\,\text{Zi}\,]}{2 \star \text{Z0}}}{\frac{\text{Par}[\,(\text{R2} + \text{Z0})\,\,,\,\,\,\text{Zi}\,]}{\text{Par}[\,(\text{R2} + \text{Z0})\,\,,\,\,\,\text{Zi}\,] + \text{R1}}} == \text{G} \,; \\ &\frac{1}{2} \left( 2 \,\text{G} \,\text{Z0} - \text{Zi} - \text{G} \,\text{Zi} + \sqrt{8 \,\text{G} \,\text{Z0} \,\text{Zi} + \left(\text{Zi} + \text{G} \,(-2 \,\text{Z0} + \text{Zi})\,\right)^2}} \right) \end{aligned}$$

- Discrete Op Amp: Calculations

- Also calculations for the integrator:

- Same ideas. Adaptation & Same Contribution.

Discrete Op Amp: Calculations

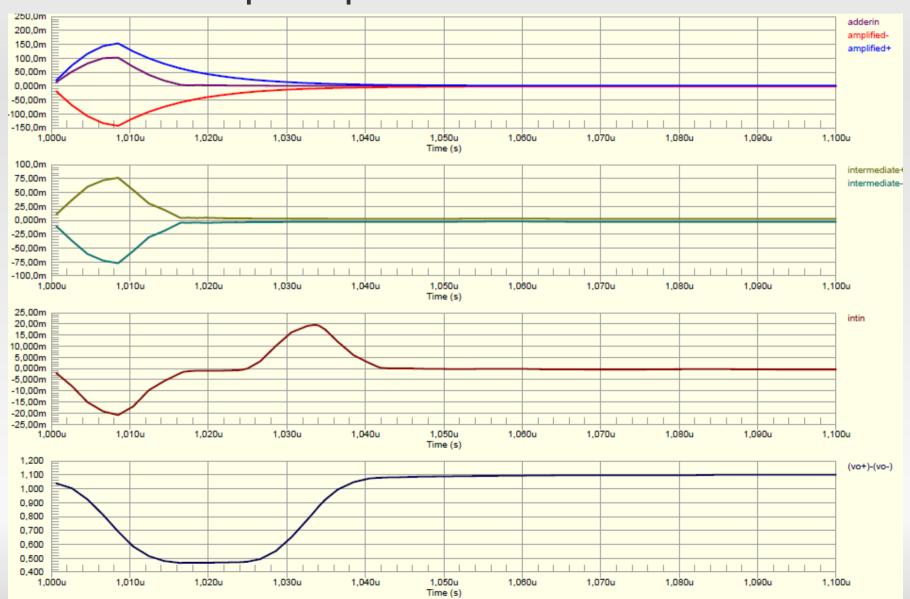

#### **Simulation Results**

#### Discrete Op Amp: Results

#### Conclusion

- A differential output was needed because of the interface with the ADC

- NOT a differential scheme, only uses differential OP Amps

- Studying the possibility of decreasing power

- Relatively low resistances → low noise, possible to decrease them even more, under study

- Needs noise and linearity studies