# Data processing in the wake of massive multicore processors

How our software infrastructure is evolving to meet changes in the large-scale computing environment

Jim Kowalkowski

Fermi National Accelerator

Laboratory

CHEP2013 - jbk 10/15/2013

# Moving away from the simple commodity cluster

The computing environments that run our major event-processing framework software are changing. These frameworks have been evolving to accommodate this change. The changes need to go quite a bit further, to better handle coprocessors with alternative architectures.

Are we going far enough with our software framework and related infrastructure?

By the way: Heterogeneous computing is back

#### Overview

- O Reminders

- A few reminders concerning the changes

- O Changes in computing architecture

- O Software

- O Software development in this future context

- O Software frameworks on modern architectures

- O Programming

- Aspects of programming many-core

- Already visible software issues

- O Putting it all together

### A few reminders

CHEP2013 - jbk 10/15/2013

## The changes are real

- What specially am I talking about?

- O The many-core processor, not the multicore processor.

- O The accelerator or coprocessor

- O The Nvidia GPGPU and the Intel Xeon Phi are the best examples out there

The computing challenge has been recognized nearly everywhere, as evident from the R&D groups that have popped up over the past couple of years.

From the frameworks perspective, the focus has been on multicore, which of course is an excellent start – but does it go far enough?

Concurrency Forum at <a href="http://concurrency.web.cern.ch/">http://concurrency.web.cern.ch/</a>

Software Engineering, Parallelism & Multi-Core - Track 5 Event Processing, Simulation and Analysis - Track 2

## The changes are fundamental

- O The many-core computing change

- Large core counts is primary focus

- O Slower cores with reduced memories, reduced operations, and much greater vector processing.

- The larger leadership class machines have been headed in this direction, but also include multiple high speed interconnects.

- Even the simpler commodity-computing environment is changing.

- ARM based server announcements.

- O PDAs replacing laptops and laptops have been replacing desktops.

- O Integrated CPU-GPU systems.

## Changes in architecture

CHEP2013 - jbk 10/15/2013

## Mainstream Computing in HEP

- O Heavyweight cores made life easy

- O Endless memory

- High-level languages

- Single architecture

- O Single OS (mostly)

- Are we spoiled?

- Must all good things come to an end?

#### On the horizon

- O Top 10 supercomputers

- Where is money being spent?

- Who is driving change and innovation?

- Looks like they are moving towards a more useful measures of effectiveness: cycles of computing accomplished for the energy used.

- Note that the core counts are not all that exciting, as perhaps we expected a few years back.

| Total |              |          |                                        |             |                      |  |  |

|-------|--------------|----------|----------------------------------------|-------------|----------------------|--|--|

| Rank  | Name         | Cores    | Processor                              | Mflops/Watt | Coprocessor          |  |  |

|       | Tianhe-2     |          |                                        |             |                      |  |  |

| 1     | (MilkyWay-2) | 3120000  | Intel Xeon E5-2692 12C 2.2GHz          | 1901.54     | Intel Xeon Phi 31S1P |  |  |

| 2     | Titan        | 560640   | Opteron 6274 <mark>16C</mark> 2.200GHz | 2142.77     | NVIDIA K20x          |  |  |

| 3     | Sequoia      | 1572864  | Power BQC 16C 1.600GHz                 | 2176.58     | None                 |  |  |

| 4     | K computer   | 705024   | SPARC64 VIIIfx 8C 2.000GHz             | 830.18      | None                 |  |  |

| 5     | Mira         | 786432   | Power BQC 16C 1.600GHz                 | 2176.58     | None                 |  |  |

| 6     | Stampede     | 462462   | Xeon E5-2680 8C 2.700GHz               | 1145.92     | Intel Xeon Phi SE10P |  |  |

| 7     | JUQUEEN      | 458752   | Power BQC 16C 1.600GHz                 | 2176.82     | None                 |  |  |

| 8     | Vulcan       | 393216   | Power BQC 16C 1.600GHz                 | 2177.13     | None                 |  |  |

| 9     | SuperMUC     | 147456   | Xeon E5-2680 8C 2.700GHz               | 846.42      | None                 |  |  |

| 10    | Tianhe-1A    |          | Xeon X5670 6C 2.930GHz                 | 635.15      | NVIDIA 2050          |  |  |

| CHI   | EP2013 - jbk | 10/15/20 |                                        |             |                      |  |  |

## An quick aside ...

- O Note that our old friend the heavyweight multicore cluster node has not changed much regarding core counts.

- Nothing greater than 16 cores per nodes on the top ten!

- Note that high-speed networking is important on the top ten. This is now affordable, even at speeds of 40Gb/s.

- O Does this mean anything for computing.

- At this speed, is it cheaper to move things around the network than to store and move files?

- Are there advantages to protocols outside TCP/IP over ethernet?

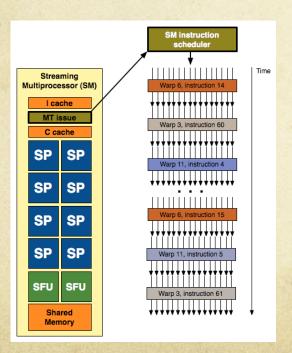

## Many-core: Available now

- Key features that impact software frameworks

- Lots of cores and support for many threads

- Low power given the computing resources

- Low memory per thread

- Other key aspects

- NVIDIA K20: unusual synchronized thread operation

- Xeon Phi: Big 512 bit VPU registers

|                 | Phi          | K20                   |  |

|-----------------|--------------|-----------------------|--|

| Power           | ~300W        | ~235W                 |  |

| Cores           | 60           | ~2500                 |  |

| Threads         | 60*4=240     | 2048*13=26624         |  |

| Memory / thread | 8GB/240=33MB | 32 regs + 24KB shared |  |

Most interesting is how many-core affects event processing applications

## Past: Remembering days gone by

- O Does anyone remember the era on the left?

- O What was unique about it?

Are the good times over or have they returned?

# Software development in this future context

CHEP2013 - jbk 10/15/2013 13

#### Modern software on current cores

- O What has the large-core processors brought us?

- O Languages

- O Java, Javascript, PHP very popular

- O C++

- o still an interesting choice

- o what do many people outside of HEP say about it?

- O How well do people know it?

- O Complexity

- Performance is difficult to quantify, even with the extremely advanced tools of today.

- O Still difficult to estimate performance changes from measurements

- Many interacting parts contribute to this

#### Living within the future context

- What has our software infrastructure team been doing to accommodate these hardware changes?

- A clash of thinking

- O Have you worked with people that have been using complex parallel-capable machine for years?

- What about optimizing the computational kernel after locating it?

- O Still a mismatch for many-core

- O Irregular problems and workloads

- Reduced flexibility changes programming patterns

- O Slow progress in showing reasonably good value

Is more code design actually going to be necessary?

## Why all the excitement?

- Are massively parallel platforms really all that interesting?

- Software frameworks are used to define our applications

- Organization and programming of these will be the my focus

- O Key changes to software requirements to watch for

- The Goldilocks effect: choosing just the right unit of work

- Extra steps likely needed: ordering and summarizing partial results

# Software frameworks on modern architectures

CHEP2013 - jbk 10/15/2013 17

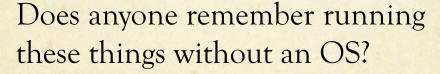

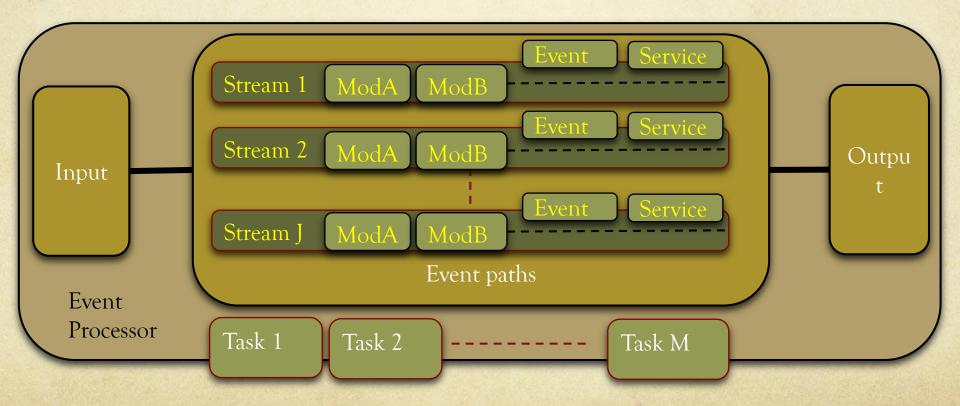

# An essential organ: The standard framework

**Event Processing Framework**: Software that coordinates the processing of *collision events* by pluggable *reconstruction, filtering,* and *analysis* modules. Events and modules are independent. Modules add data to and retrieve data from one event at a time.

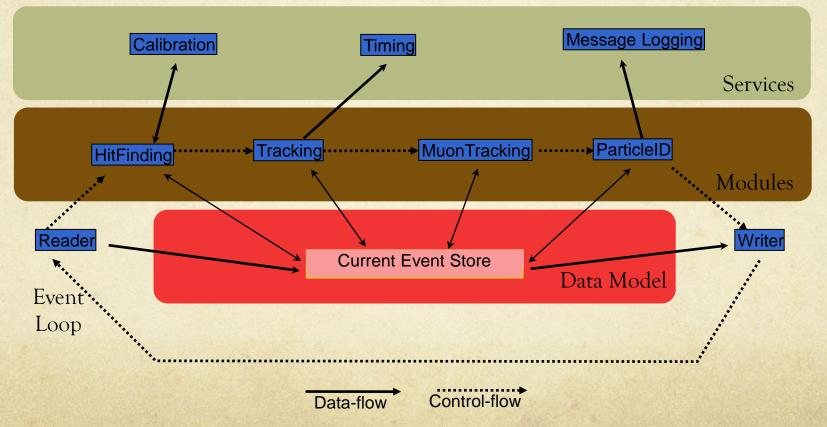

#### Assumptions for this discussion

- O Event time and size estimates from CMS

- 10-30 seconds for reconstruction

- 1-20Hz processing rate for skim jobs

- 1MB event size during reconstruction

- O 150KB size for AOD

- Assuming that the processing times will be 10x bigger in next run

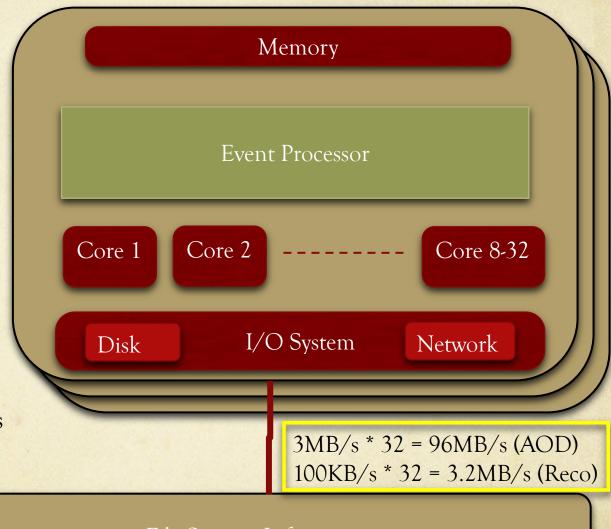

- O Bandwidth estimates based on these numbers and only on input data rates.

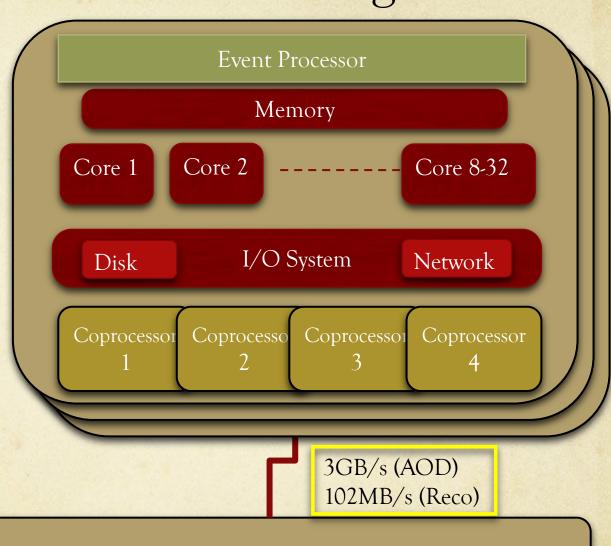

## Let's start from where we are now

- Same old organization

- Serial processing of events

- One processor per core

- O New

- Rules for making thread-safe module code

- Removal of global variables

- Addressing global service issues

Console File Serving Infrastructure

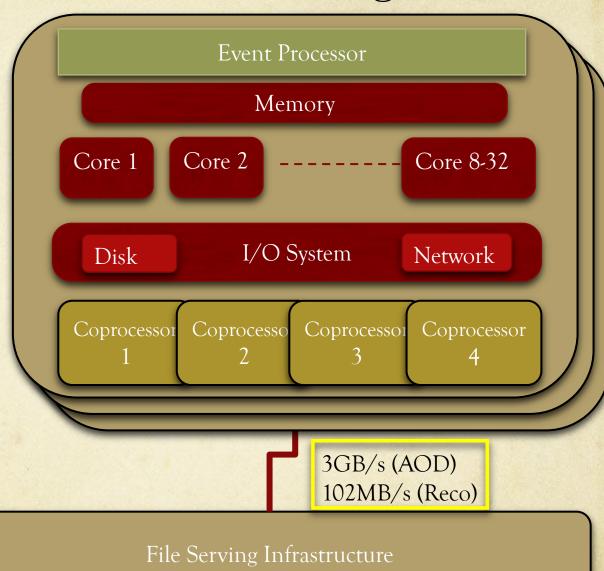

# Framework reorganization

- Key principle: Work is assigned to tasks, and tasks are scheduled to run on cores.

- O Intel Threading Building Blocks (TBB) operates like this and is commonly used

- O Parallelism at the event, module, and algorithm level all available

- Framework schedules streams and modules, algorithms can generate more work

#### Near future framework

- Focus on multi-core heavy-weight "serial cores"

- O Some goals

- Reduce memory use

- Maintain processing efficiency

- Reduce run latencies

- Allow multi-threaded algorithms

- Multiple active events

10/15/201

Console

File Serving Infrastructure

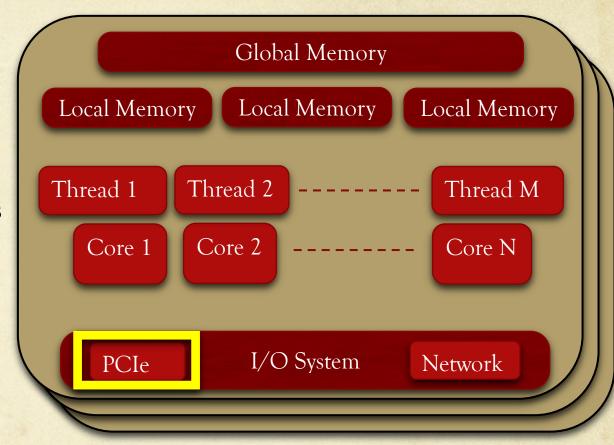

## The many-core coprocessor

- Small memories

- Simple cores

- O Data transfer costs

- Lock step operations

- Specialized languages

|                 | Phi   | K20                 |

|-----------------|-------|---------------------|

| Cores           | 60    | ~2500               |

| Threads         | 240   | ~26624              |

| Memory / thread | ~33MB | 32 regs+24KB shared |

## Where are we heading?

- O 10x compute capacity?

- Low overhead scheduling and coordination essential

- O Is the bandwidth increase an issue?

Console File Serving Infrastructure

## Where are we heading?

- Now a distributed framework?

- Coordination of separate memories

- EDM and data sharing affected

- Load balancing difficulties

- Must not overload serial cores

- O Is this an intermediate step?

Console

10/15/201

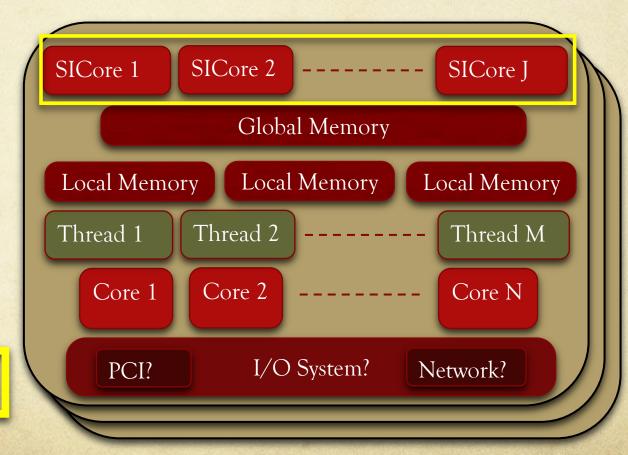

## Is this still a coprocessor?

- SICore = serial, integrated core

- O ARM?

- O PowerPC?

- Shared memory

- Low overhead communications

- Single address space possible

- Usual coordinated access needed

- A Hybrid Processor

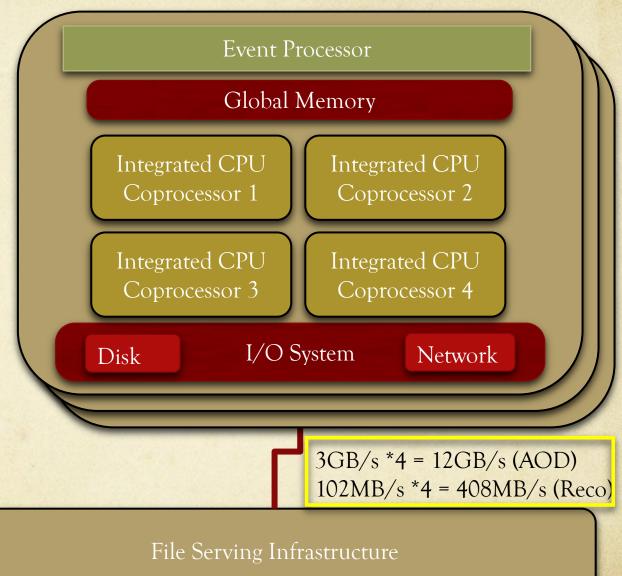

## Not that far away

- What can we do this something like this?

- Are files still useful?

- Many options for event processor application

- O Is 20x 40x increase plausible?

Console

# These things already exist

- O NVIDIA Tegra 4 (hand-helds)

- o 72 GPU Cores

- O Quad-core ARM

- O Dell Copper

- 4 quad-core ARMs per sled

- 12 sleds per chassis

- O Cray XC30 blade

- High density

- o multicore, GPGPU, MIC

- Pick and choose

- High-speed interconnect

## Programming many-core

CHEP2013 - jbk 10/15/2013 29

## Programming aspects

- O Language extensions and special directives are needed

- O Chose CUDA

- Will use the Intel tools: Cilk Plus, intrinsics, pragmas

- Our development tools have evolved to incorporate many-core

- O CUDA compilation is in our build suite.

- O Integrated TBB into our tool chain

- Xeon Phi not far behind

- Multiple architecture builds (again)

- Cross compiling necessary

- More than one algorithm implementation likely

- O Complicates testing and validation

- Two or more kinds of compiled code available at run-time

- Moving to new externals requires more synchronization

## More programming aspects

- O Programming the many-core machines is getting better

- O Dynamic parallelism and Hyper-Q

- Hyper-Q = many processing streams active at the same time

- O Dynamic parallelism = GPU functions can start more GPU functions without returning control to host

- Allows for more than one independent activity on the GPU

- Overlap of transfers and computation boosts performance

- Hides the transfer latencies present in the current series of processors

#### Affected framework areas

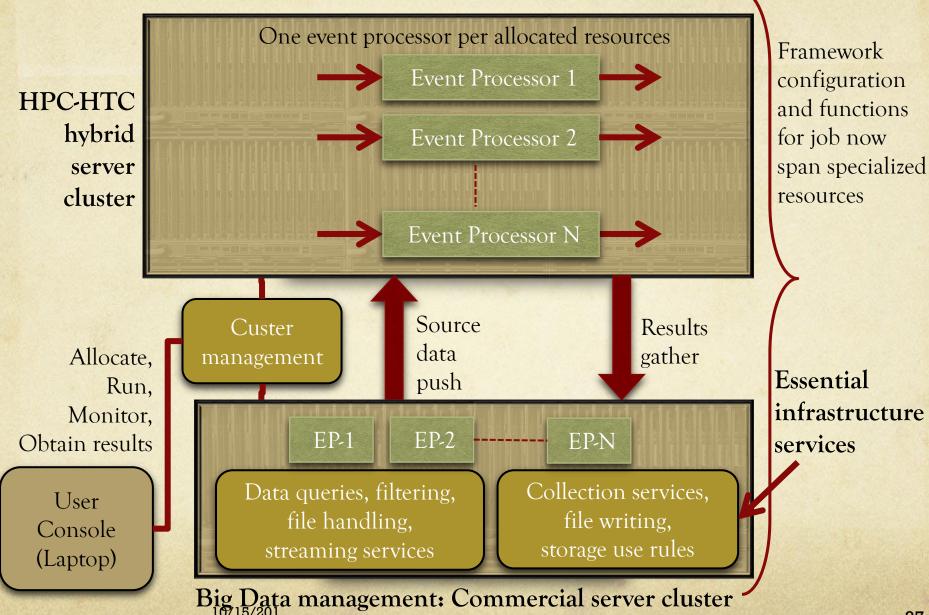

- Current HEP cluster defined as High Throughput (HTC), not High Performance (HPC)

- O Increase in node capabilities will stress the I/O systems

- O A more distributed framework will affect the

- O Scheduling of work (TBB will help, data dependencies more visible)

- Event data model (EDM delayed reading or loading is troublesome)

- O Configuration (boundaries and constraints more important)

- O Services (global will need to be eliminated)

- C Larger scale distributed reductions (sums and aggregations) will be necessary

- O Handling synchronization points such as runs and other event groupings become more complex

|              | 1 core  | 32 cores  | 256 cores | 512 cores | >1024 cores |

|--------------|---------|-----------|-----------|-----------|-------------|

| 150KB @ 20Hz | 3MB/s   | 96MB/s    | 768MB/s   | 1.5GB/s   | 3GB/s       |

|              | 100KB/  |           |           |           |             |

| 1MB @ .1Hz   | s Summa | 3v2MBaird | 25MBgues  | 54MB/s    | 102MB/s     |

# Already visible software issues

CHEP2013 - jbk 10/15/2013 33

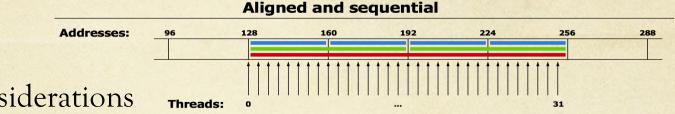

## Issues that are already visible

- Memory considerations

- O Bank access patterns visible in code (must understand)

- O Calculating values better than caching results

- O Can quickly become the bottleneck and source of bad performance

- O Small tweaks in access pattern can yield wildly difference results

- O Task model for parallelism has been good

- O Common direction (layers easily cooperate)

- Can avoids locking

- O Design decisions on data structures and algorithm decomposition become more critical than ever

## Issues that are already visible

- Mixed execution locations needed

- For algorithm phases

- For modules

- O Heterogeneity is back and will be a big issue

- O Unclear how much visibility and control the framework will have here

- O Unclear how to keep a balanced load: many run-time parameters

- New methods of collecting summary data and diagnostic information from algorithm phases will likely be needed

- O Conditional logic troubles

- O Deviations in work load problems

- O Temporary storage of extra data issues

- Making it widely available concerns

- O What is good for the lighter weight processors has also been good for the heavier weight processors

# Pulling it all together

CHEP2013 - jbk 10/15/2013 36

# A possible overcome

CHEP2013 - jbk

37

## Summary

- A mixed computing environment is inevitable

- Heterogeneous within and among resource types

- Job specification / configuration split across resource types

- O Changes will affect our I/O subsystem

- Focus on simpler streaming methods

- O Leave file and catalog handling to special-purpose nodes

- Newer network protocols and hardware may help

- O Changes in algorithm development strategy

- O Began a while back

- Accommodate all types of many-core and multi-core

10/15/201

#### Conclusion

- Movement in industry and research towards

- Increasing performance through specialization

- Keeping operational cost constant (or lower)

- O All of this means more independent parts within our software infrastructure

- O To keep up, we need continued and increased cooperation

- O Between physics laboratories

- O Between HPC communities