#### A High-speed Adaptively-biased Currentto-current Front-end for SSPM Arrays

Bob Zheng, Jean-Pierre Walder, Henrik von der Lippe, William Moses, Martin Janecek

June 9, 2011

#### **Outline of Presentation**

- Motivation for Solid State Photomultipliers (SSPM)

- SSPM Background

- ASIC Design Challenges and Avalanche Photodiode (APD) Background

- ASIC Design

- Results

- Future work

#### Motivation for using SSPM's

| SSPM                           |

|--------------------------------|

| High gain                      |

| Sub-ns timing resolution       |

| Silicon                        |

| Integrated                     |

| Low Power (bias voltages ~35V) |

|                                |

Large, expensive

#### **Motivation (continued)**

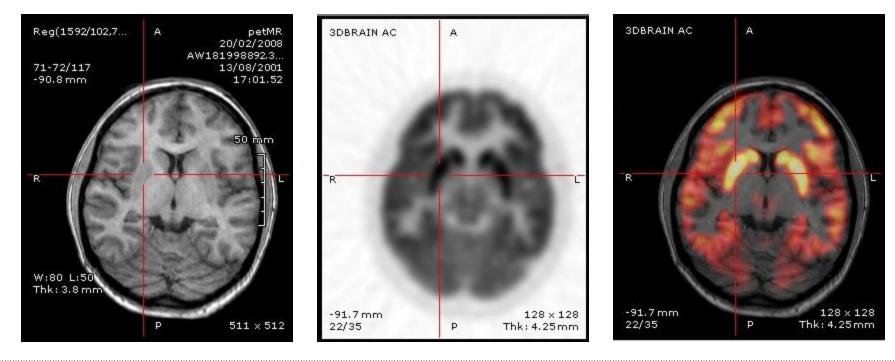

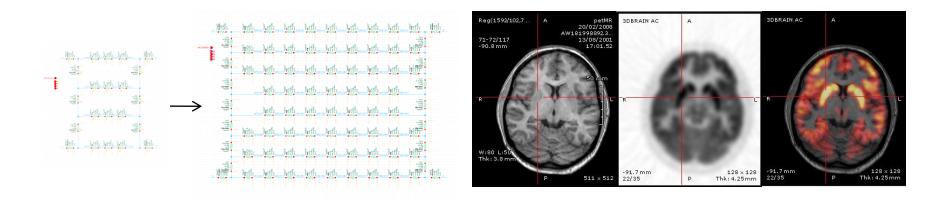

- Insensitive to magnetic fields, which allows for hybrid PET/MRI imaging

- Complementary imaging techniques reveals structure and function simultaneously

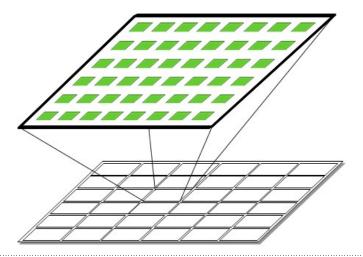

#### **Background: SSPM Arrays**

- Large variety of SSPM detectors

- Capacitance ranges from 20pF to 900pF

- Output currents ranges from 20µA to 20mA

- For example: numerous arrays made by **RMD**, **Inc.** based in Watertown, MA.

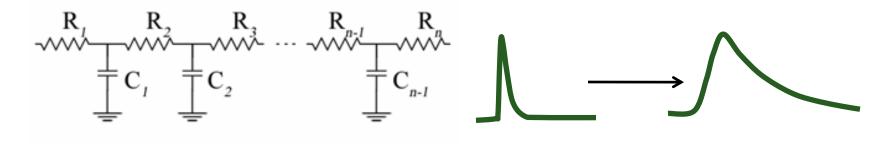

#### **Background: ASIC Design Challenges**

- Large capacitance range and output current range

- To reduce number of outputs, our group uses resistive charge division network but directly connecting SSPM to network degrades timing resolution

$$\tau = RC = (100\Omega)(900pF) = 90ns$$

### •ASIC must handle large dynamic range without degrading performance of SSPM

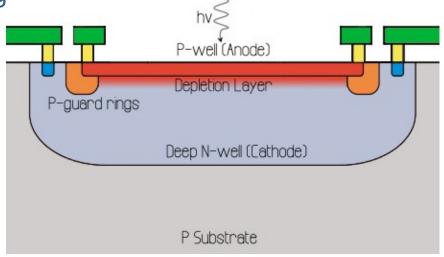

#### Single Photon Avalanche Diode Background (SPAD)

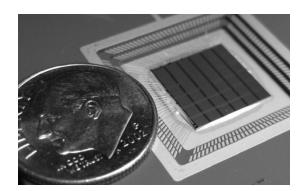

- Produced by RMD, Inc. in AMS high-voltage 0.35µm technology

- Independent digital micropixel signals within macropixel sum together to produce analog signal

- Can be used for photon counting

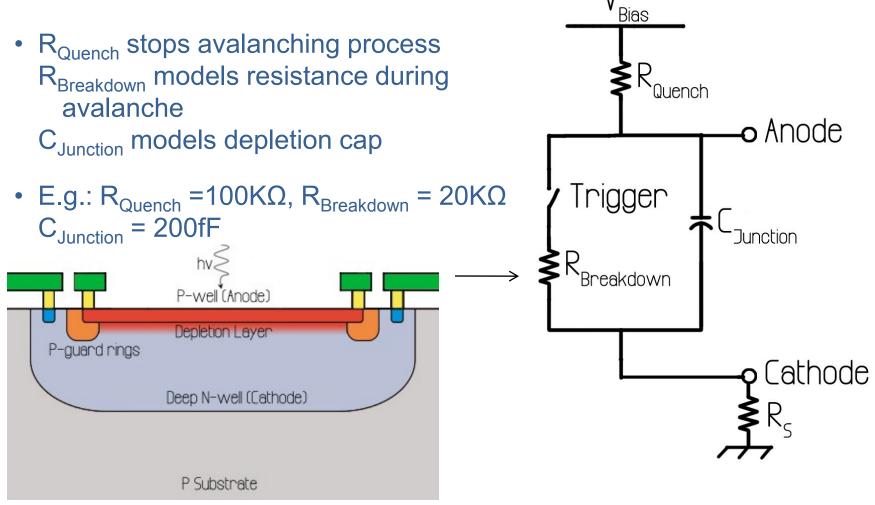

#### **SPAD Model**

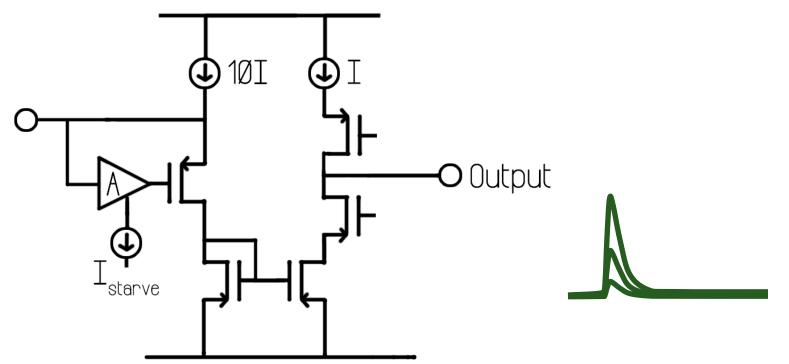

#### **Proposed Solution**

Isolate macropixel cathode by using a current conveyor

•

$$\tau_{new} = RC_{parasitic} << RC_{pixel}$$

. Minimal timing resolution loss

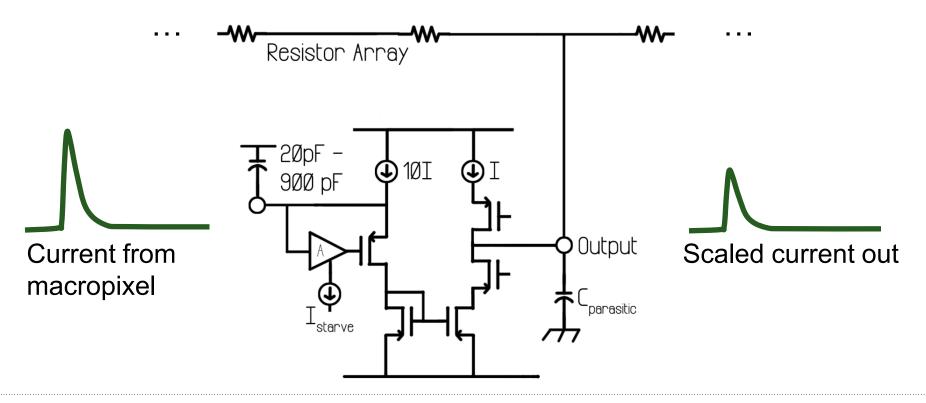

#### **Front-End Circuit**

•Feedback amplifier gain controlled by starving current which ensures stability with pixel capacitances from 20pF up to 900pF and currents from 20uA up to 20mA

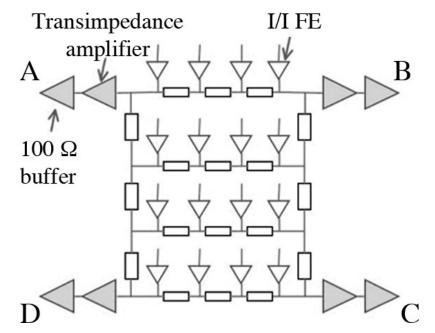

#### **Complete ASIC**

•Comprised of:

- -16 Current-to-current front-ends

- -Resistive charge division network

- -4 Transimpedance amplifiers

- -4 100 $\Omega$  Output buffers

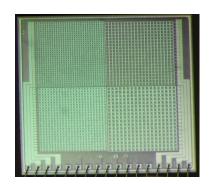

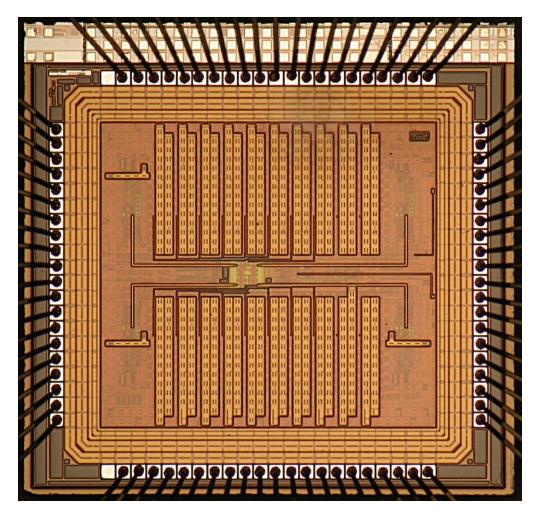

#### **Results – Micrograph**

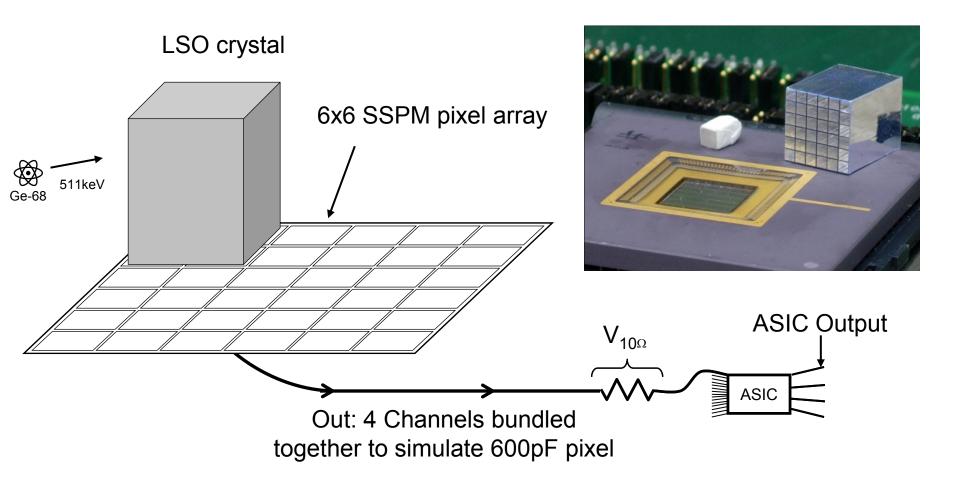

#### **Results – Measurement Setup**

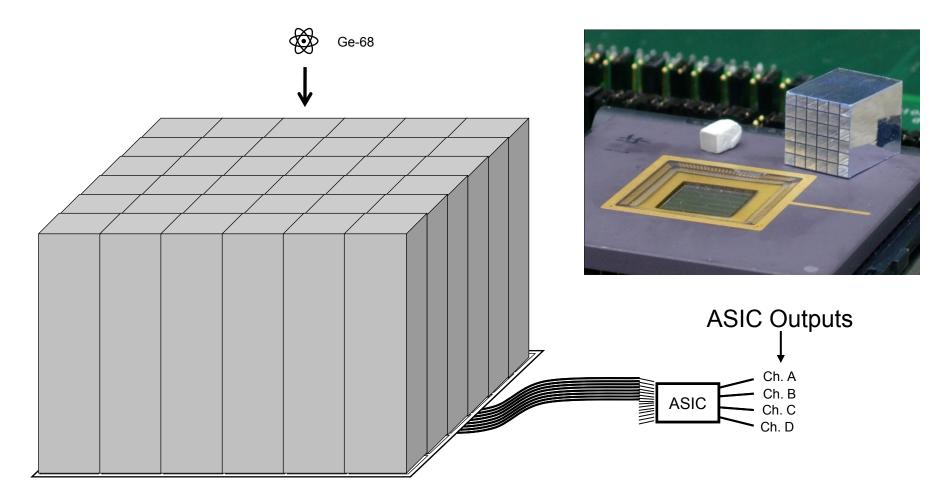

#### **Results – Measurement Setup**

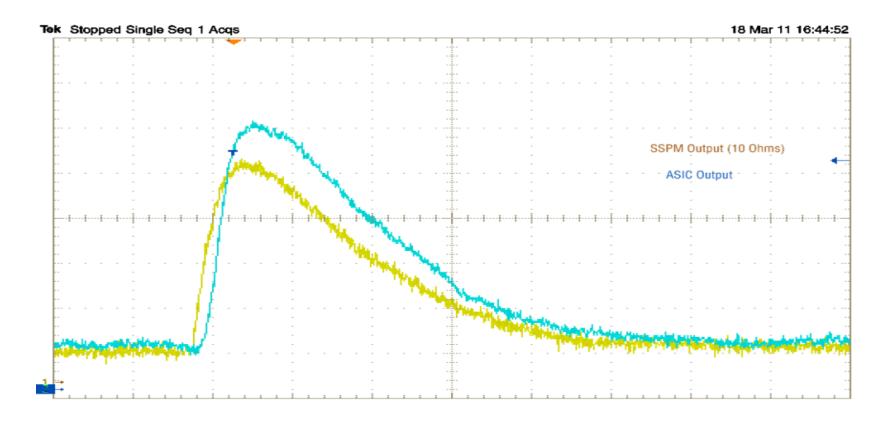

#### **Results – Transient Plots**

Risetime for this pulse: ~12ns

Degradation <2ns

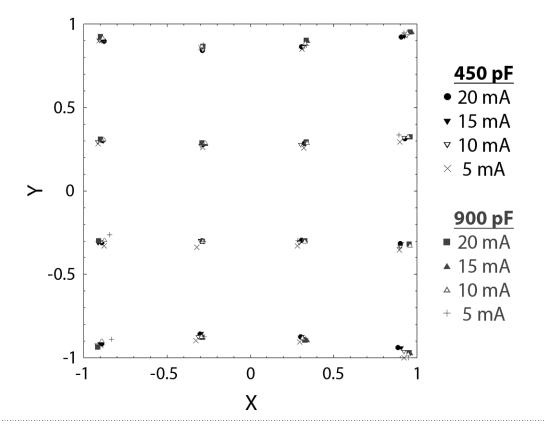

#### **Results – Position Plot**

•Measured output of ASIC shows good separation. Input from emulator board.

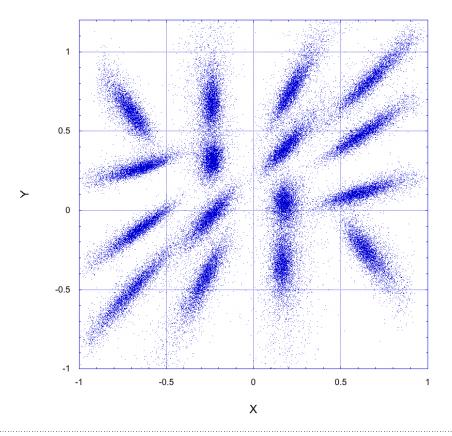

#### **Results – Crystal Decoding**

•Distortion comes from test measurement setup. The multi-purpose PCB used, which is not optimized for our experimental setup.

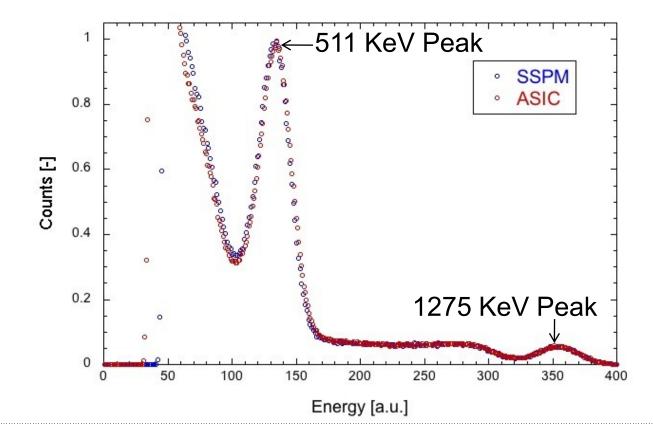

#### **Results – Energy Spectra**

•For Na-22 source, energy resolution (FWHM) at 511keV peak is 20.4% for detector and 20.6% for detector and ASIC

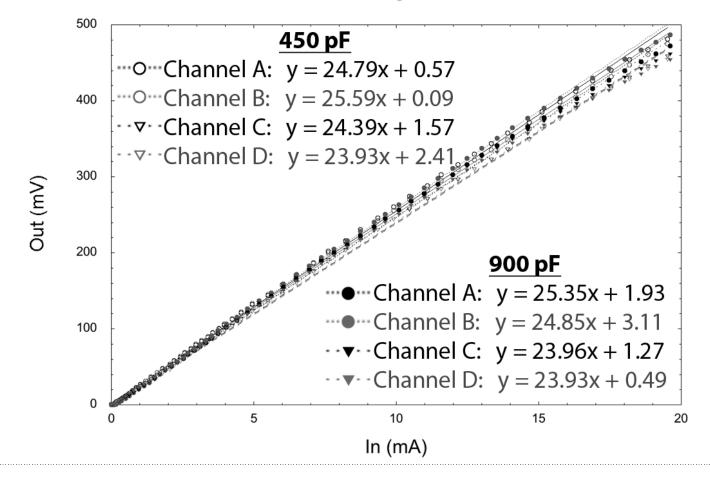

#### **Results – Linearity**

#### •Less than 4% deviation with large and small loads

#### **Results - Summary**

| Rise time degradation   | <2ns                                   |

|-------------------------|----------------------------------------|

| Input capacitance range | 20pF to 900pF                          |

| Total # of Inputs       | 16                                     |

| Total # of Outputs      | 4                                      |

| Power                   | ~12 mW/ channel, ~300mW full chip      |

| Noise (rms)             | < 1 mV <sub>rms</sub>                  |

| Noise (FWHM)            | <1% added in quadrature to LSO crystal |

| Linearity               | <4% deviation                          |

#### **Future Work**

- Improve measurement setup

- Integrate SSPM and ASIC monolithically

- •Increase the number of read-out channels from 16 to 64

- •Add temperature stabilization and correction circuits for SSPM

- •Use inside of MRI for hybrid PET/MRI imaging

#### Acknowledgements

#### Financial support by

#### Detectors made by

## RMD

# Thank you for your attention