# Cold CMOS Electronics for the readout of very large LAr TPCs

#### Craig Thorn On behalf of the LBNE LAr Working Group

TIPP 2011 June 11, 2011

Gianluigi De Geronimo, Alessio D'Anadragora\*, Shaorui Li, Neena Nambiar, Sergio Rescia, Emerson Vernon Hucheng Chen, Francesco Lanni, Don Makowiecki, Veljko Radeka, Craig Thorn, and Bo Yu

> Brookhaven National Laboratory, NY, USA \* University of L'Aquila, L'Aquila, Italy

# Outline

- LAr40 overview

- The Cold Electronics System

- Analog Front End

- ADC

- Summary

Other presentations at TIPP 2011 describing LBNE LAr40:

- [412] Membrane cryostat technology and prototyping program towards kton scale Neutrino detectors, **Rucinski**

- [422] Designs of Large Liquid Argon TPCs from MicroBooNE to LBNE LAr40, Yu

- [223] Front End Readout Electronics of the MicroBooNE Experiment, Chen

#### LBNE LArTPC inside Cryostats in Cavern

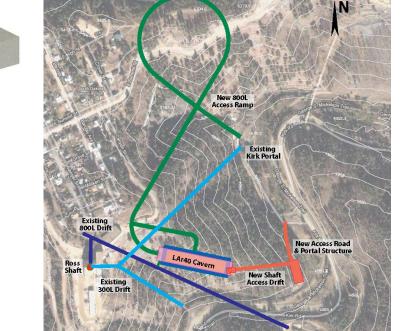

Deep Underground Science & Engineering Lab (DUSEL) in Homestake, South Dakota, USA

LAr40 TPC 2x20 killotonnes

High Bay Access

Truss Lid for

Cryostat

3

BROOKHAVEN

Membrane

Cryostat

TPC

Arrays

Isolated Personnel Access

June 11, 2011

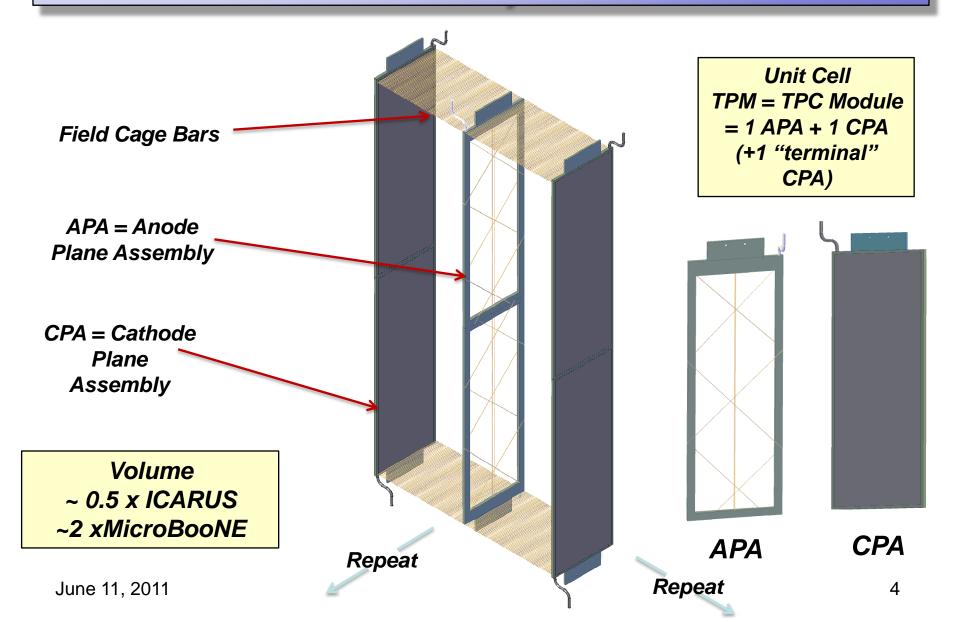

#### APA + CPA Assemblies form TPC modules in the Cryostat

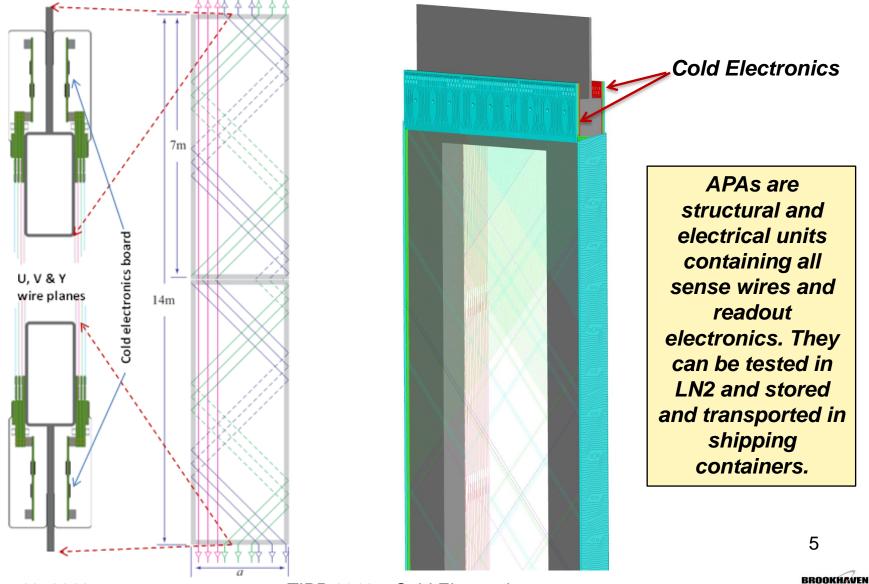

#### Anode Plane Assembly (APA): the core element of a TPC unit

June 11, 2011

TIPP 2011 – Cold Electronics

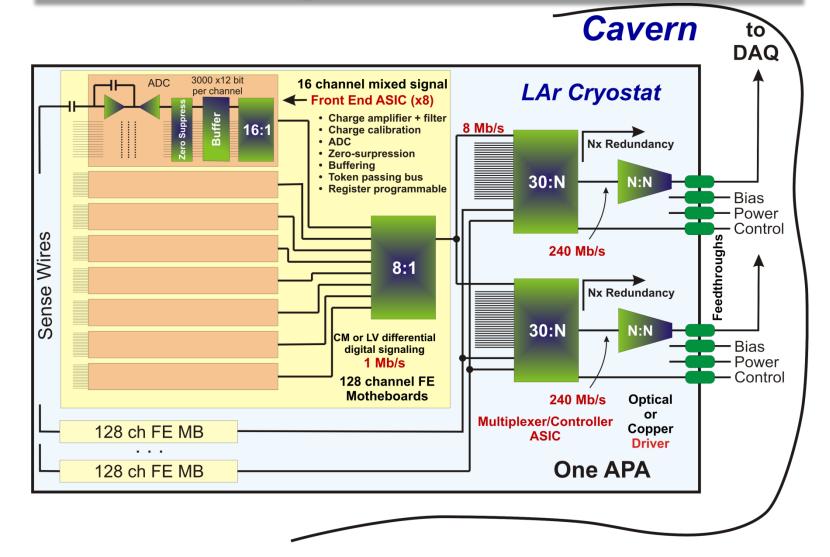

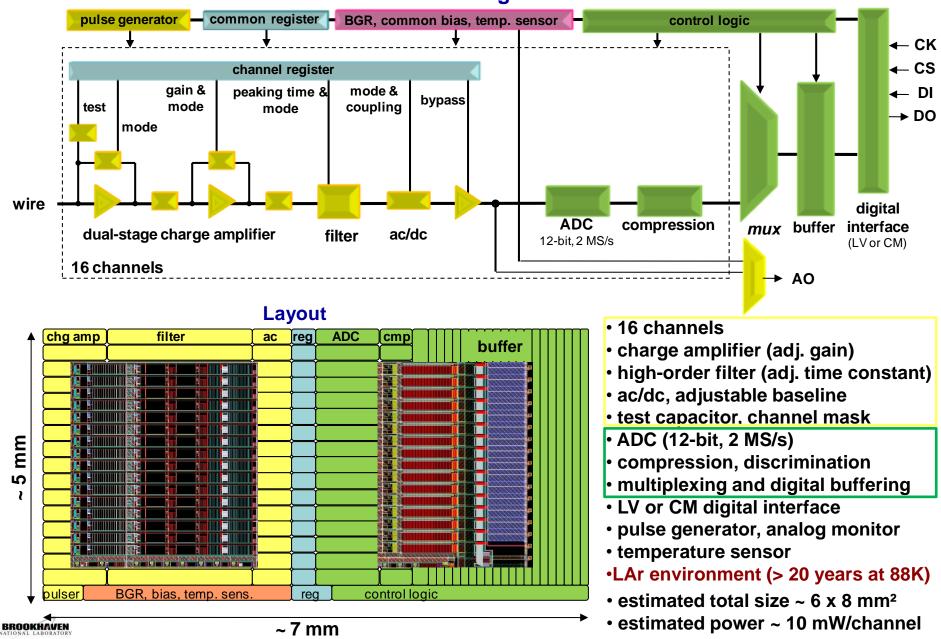

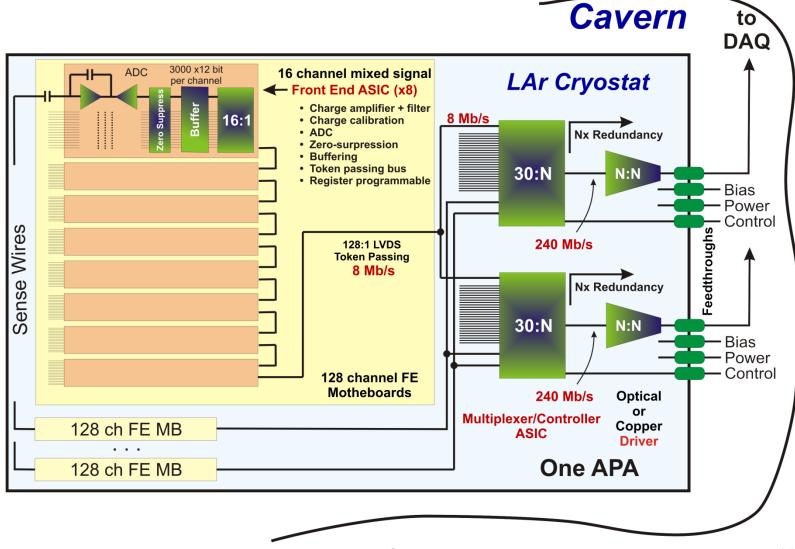

#### LAr TPC - Cold CMOS Electronics Block Diagram – Reference Design

#### LAr TPC Front-End ASIC

#### **Block Diagram**

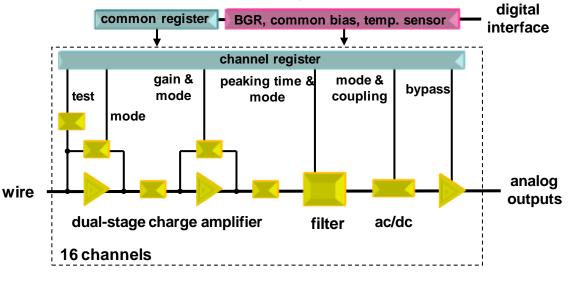

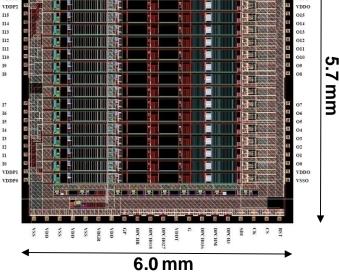

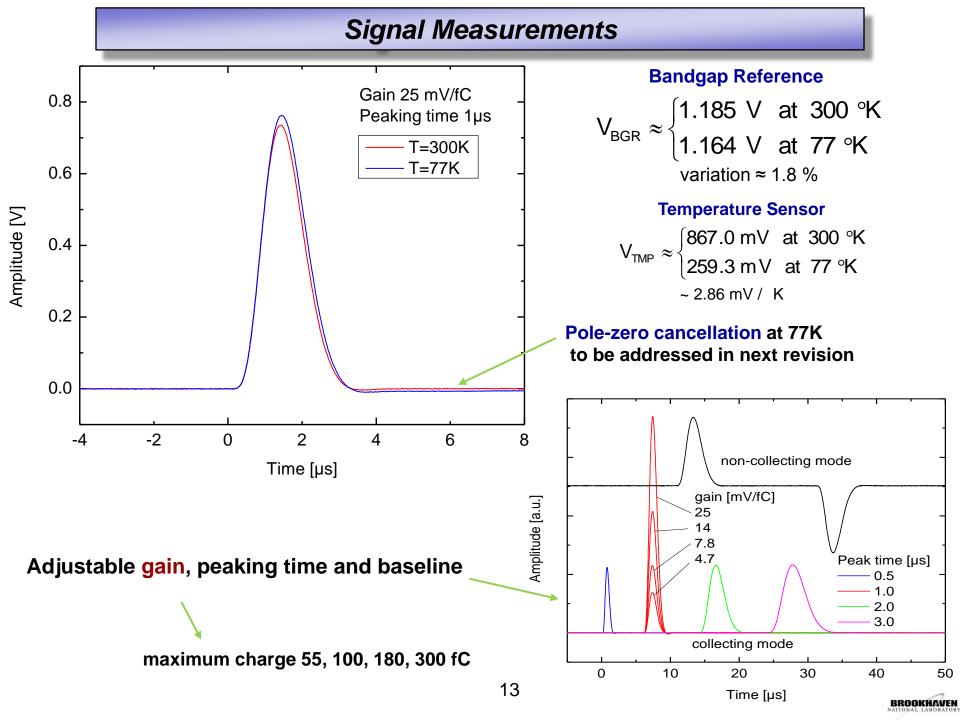

#### Analog ASIC

#### **Block Diagram**

- 16 channels

- charge amplifier, high-order filter

- adjustable gain: 4.7, 7.8, 14, 25 mV/fC (charge 55, 100, 180, 300 fC)

- adjustable filter time constant (peaking time 0.5, 1, 2, 3 μs)

- selectable collection/non-collection mode (baseline 200, 800 mV)

- selectable dc/ac coupling (100µs)

- rail-to-rail analog signal processing

- band-gap referenced biasing

- temperature sensor (~ 3mV/ C)

- 136 registers with digital interface

- 5.5 mW/channel (input MOSFET 3.9 mW)

- single MOSFET test structures

- ~ 15,000 MOSFETs

- designed for room (300K) and cryogenic (77K) operation

- technology CMOS 0.18 μm, 1.8 V

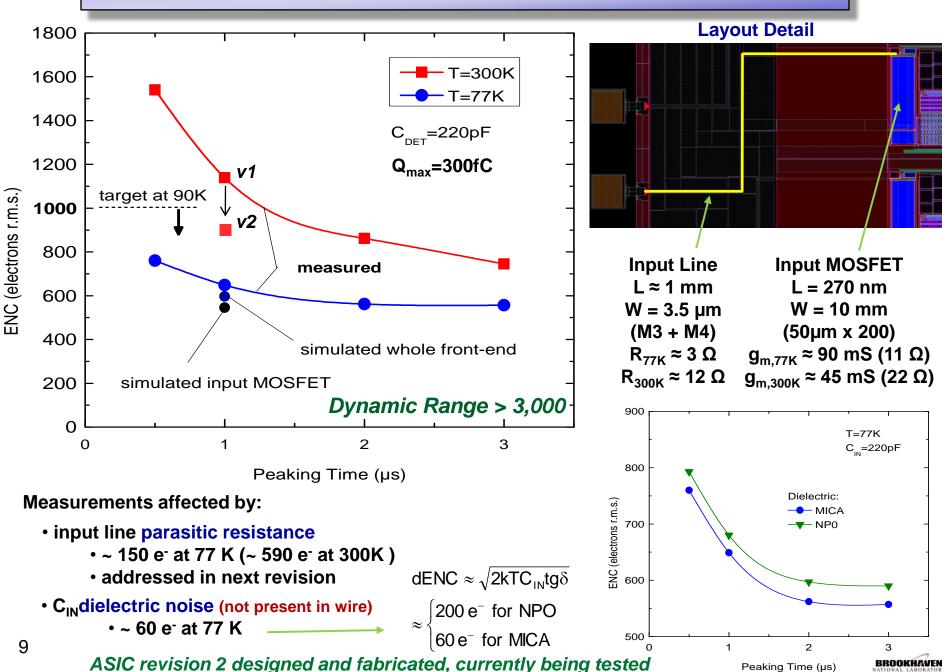

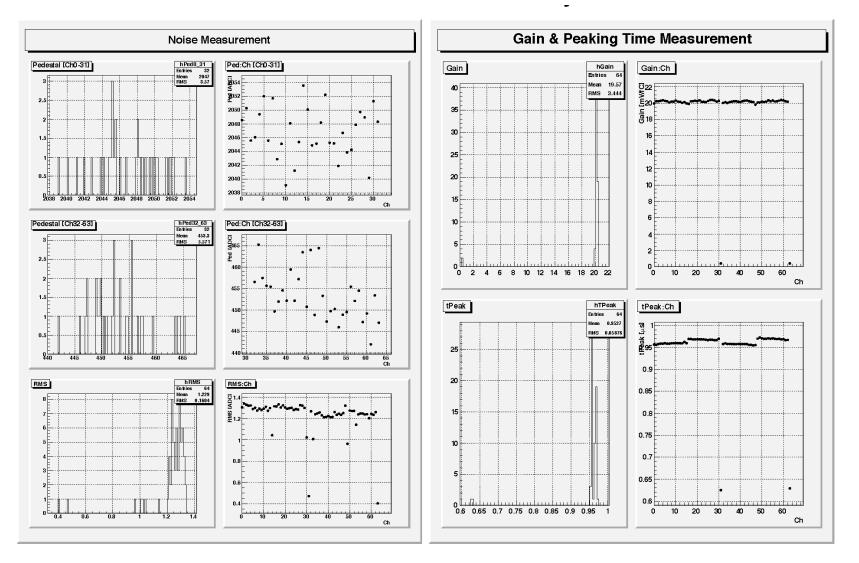

#### Noise Measurements

#### FEE ASIC Evaluation

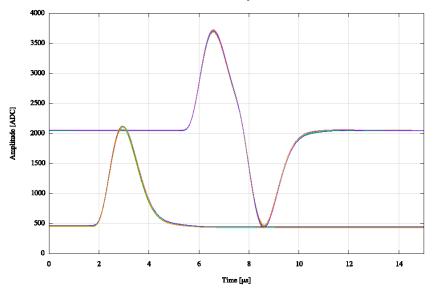

MicroBooNE FEE Test Stand Signal Readout Waveforms

#### **Crosstalk Measurement** Xtalk Xtalk 0.4 0.3 0.2-0.1 0 Chnessur 40 30 20 50 Chinject **4**0 <u>з</u>о 20 10 10 ົດ 0

#### FEE Test Stand for MicroBooNE is operational

- Full front end electronics chain, from CMOS ASIC to Receiver/ADC board, data is acquired to PC through FPGA board and Gigabit Ethernet

- One temporary 32 channel cold cable is available which has one broken channel

- Without detector capacitance, noise is ~200e<sup>-</sup> with 1us peaking time

- Nonlinearity and crosstalk are less than 0.5%

- FEE test stand will be upgraded with the second version of ASICs and two prototype cold cables, more tests to follow

10

BROOKHAVEN

June 11, 2011

TIPP 2011 – Cold Electronics

#### FEE Analog ASIC Evaluation Noise, Gain & Shaping Time

June 11, 2011

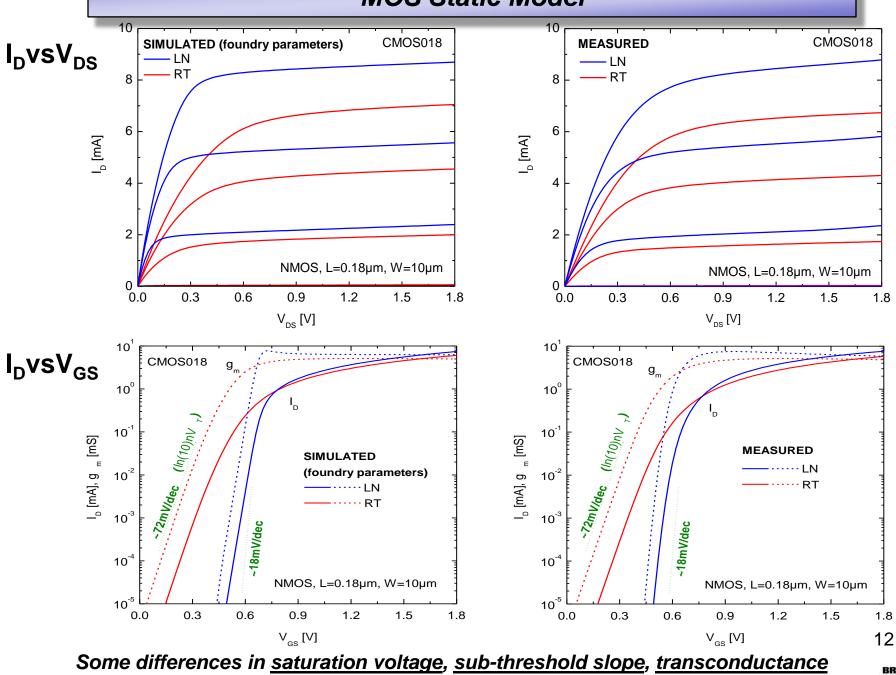

#### **MOS Static Model**

BROOKHAVEN

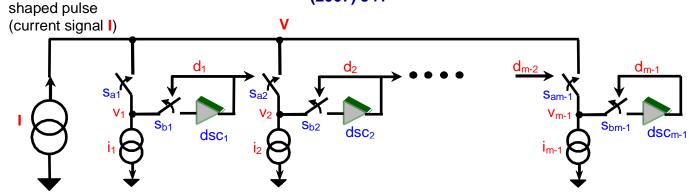

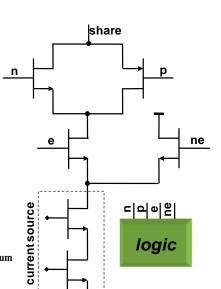

#### **ADC - Architecture**

#### **Clockless low power ADC stage**

Demonstrated in ASIC for SNS, see De Geronimo, *et al.*, IEEE Trans NSS, 54 (2007) 541

#### **Current mode ADC**

•dual stage6-MSBs in 150ns, 6-LSBs in 250ns

single trigger conversion per stage

#### 12-bit resolution

- •2 MS/s conversion rate

- power dissipation 3.6 mW at 2 MS/s

- power-down option for low rate applications

- wake up in few tens of ns

- layout size: 0.23 mm x 1.25 mm

233 um

**ADC cell**

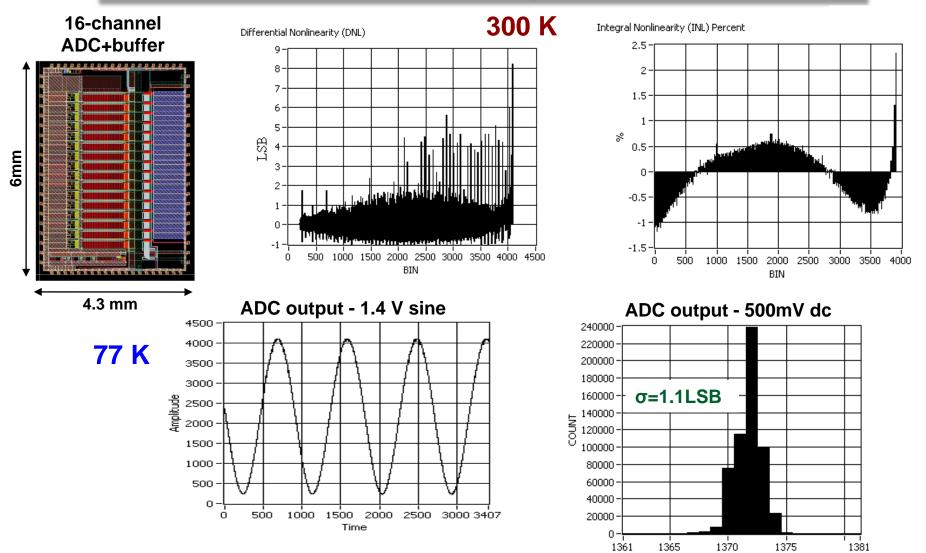

#### **ADC - Preliminary Results**

operation verified at room and cryogenic temperatures

differential non-linearity limited by timing design error in control circuit

integral non-linearity limited by mismatch (linear → common centroid)

ASIC revision being designed, to be fabricated in July

15

BIN

### **Conclusions and Future Work**

- CMOS performs better at cryogenic temperatures

- **Defined and predictable** design for cryogenic T is possible

- Low-noise at cryogenic T demonstrated

- ENC < 1,000 e<sup>-</sup> at 200pF ~5mW/ch.

- characterization and modeling of CMOS 180nm

- Long lifetime at cryogenic T possible with guidelines

- Critical building blocks front-end & ADC developed

- Future work

- Improve cryogenic static models

- Optimize ADC

- Merge, add zero-suppression & buffering, and finalize

# Backup Slides

#### LAr TPC - Cold CMOS Electronics Block Diagram – Alernate Design

June 11, 2011

TIPP 2011 – Cold Electronics

18

BROOKHAVEN

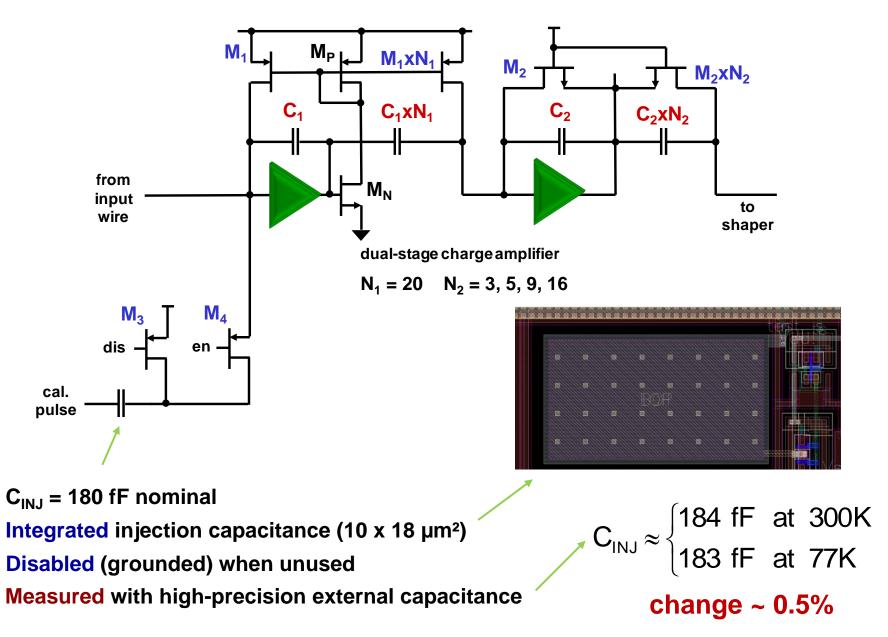

#### **Calibration Scheme**

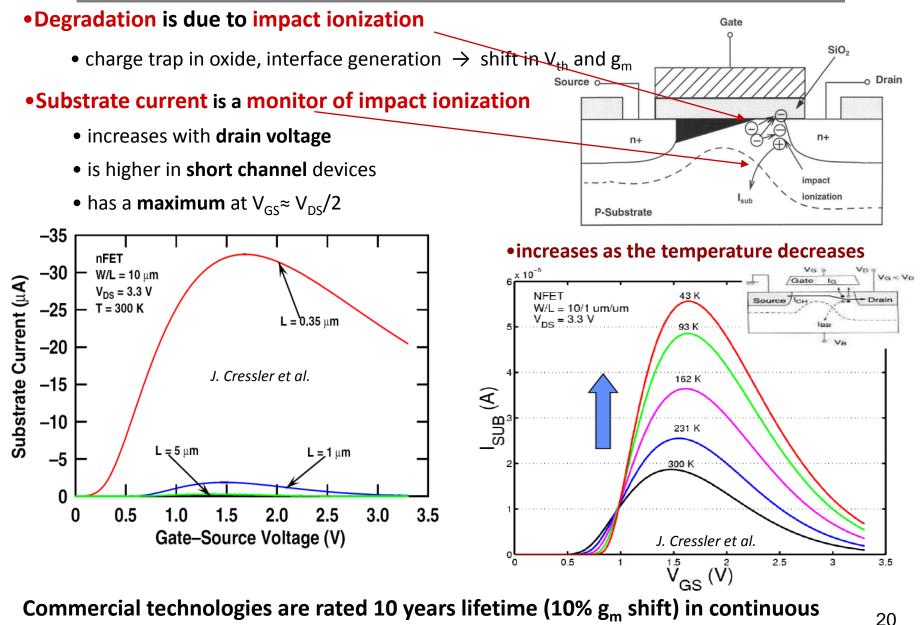

#### **Lifetime - Basic Mechanism**

ring oscillator operation: T = 300 K, L =  $L_{min}$ ,  $V_{ds}$  = nominal  $V_{DD}$ +5%,  $V_{GS} \approx V_{DS}/2$ )

BROOKHAVEN

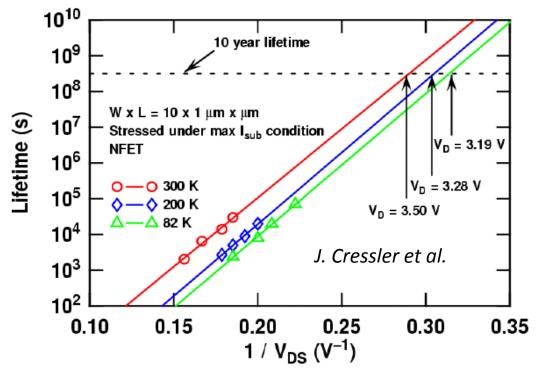

#### **Lifetime - Design Guidelines**

## Desired lifetimeat low temperature can be achieved by:

- decreasing V<sub>DS</sub> (e.g. decreasing the supply voltage)

- decreasing J<sub>D</sub>(i.e. decreasing the drain current density)

- **3.** increasing L (i.e. non-minimum channel length devices)

#### Design guidelines can be obtained for:

#### analog circuits

- operate devices at low current density

- use non-minimum channel length L

#### digital circuits

- operate devices at -10% of nom. V<sub>DD</sub>

- use non-minimum channel length L

- operate at low clock frequency

Accelerated tests at cryogenic temperature are being performed to verify guidelines