# The LHCb Velo Upgrade

Daniel Hynds On behalf of the LHCb Velo Group

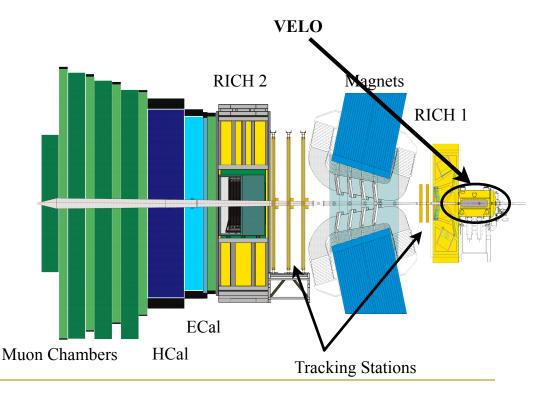

### LHCb at a glance....

- Heavy flavour physics experiment at the LHC

- Studies of b- and c-quark decays, New physics via CP violation, rare decays....

- High correlation of b-quarks in rapidity => forward arm spectrometer design

- b-quark mesons typical decay length ~ 1cm => vertexing critical to identify PV

- Main requirements/features:

- Excellent vertex resolution

- Excellent PID

- Efficient triggering and tracking

#### June 2011

# The VErtex LOcator

Silicon strip detector with back to back modules - strips in radial and angular directions

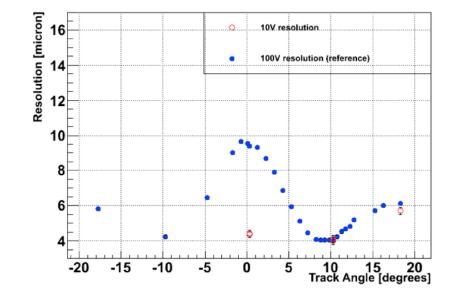

Projected angle 0-4 degrees

Projected angle 7-11 degree **Binary Resolution**

Strip Pitch [um]

- Highest resolution vertexing at LHC!

- Demanding requirements

- Proximity to proton beams (7mm)

Resolution [µµ] 30 30

20

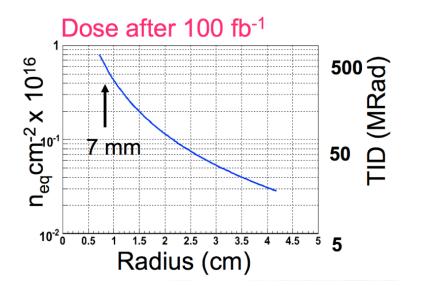

- High radiation environment

- Detector sits in vacuum

- The whole thing **moves....**

- n<sup>+</sup>- implanted n-type sensors (1 n-in-p sensor!)

- Proper time resolution  $\sim 40$  fs

- IP resolution  $\sim 13 + 25/p_T \mu m$

#### See talk by T.Latham

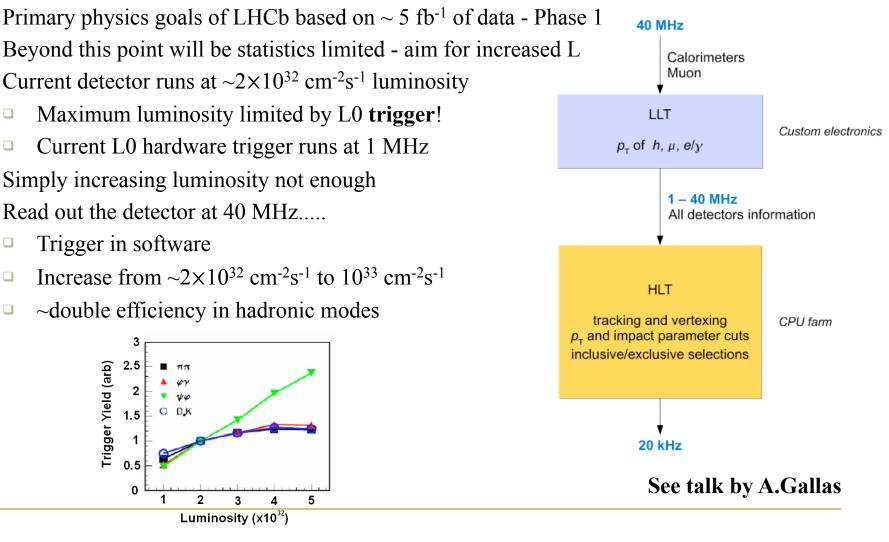

# Beyond the current detector...

# Moving Velo into the future

- Current Velo not suited to upgrade scenario

- 40 MHz readout

- Radiation tolerance (thermal runaway)

- Large parts of the current Velo can be kept:

- CO<sub>2</sub> cooling plant

- Mechanics

- HV and LV systems

- However.....

- Silicon modules must be replaced rad. hard to  $> 5 \times 10^{15}$  1 MeV n<sub>eq</sub>cm<sup>-2</sup>

- FE electronics upgraded to 40 MHz readout

- New module geometry => new RF foil design

- Aim for low occupancy

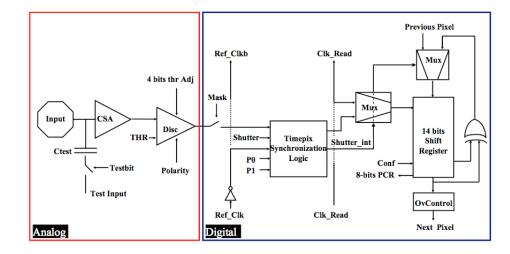

# ASIC baseline - Timepix

- Development from Medipix collaboration

- Return to HEP from medical physics

- Velopix, Clicpix, Time projection chips.....

- Pixel ASIC with shutter-based readout

- $256 \times 256$  pixel matrix with 55µm pitch

- Several operating modes:

- Particle Counting (Medipix)

- Time of Arrival (TOA)

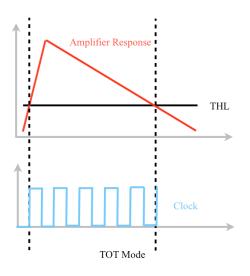

- Time over Threshold (TOT)

# From Timepix to Velopix

- Much more stringent requirements on Velopix

- Replace shutter based readout with data-driven (ZS) readout

- Reduce timewalk < 25ns (1000e<sup>-</sup>)

- Include TOA and TOT

- Lower (~500e<sup>-</sup>) threshold

- Reduced non-linearity near threshold

- Cope with anticipated particle flux in the upgraded LHCb

- Keep data loss < 0.5%

- Data rate critical!!

- An ambitious project! Still much to do....

- Main constraints will be power and data flow

#### Data rates

- Particle rate for chips closest to beam ~ 6 particles / bunch crossing

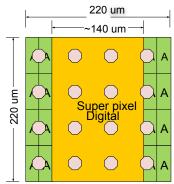

- Average 2 pixels per hit, 32 bits per pixel read out (16-bit ID, 12-bit BCID, 4-bit TOT)

- $6 \times 32 \times 2 \times 40$  MHz gives data rates of almost 15 Gbit s<sup>-1</sup>!!

- Biggest challenge to Velopix manageable data flow!

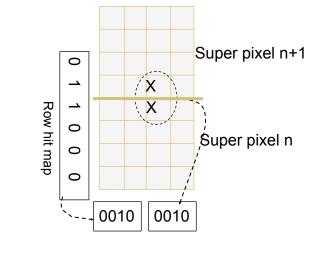

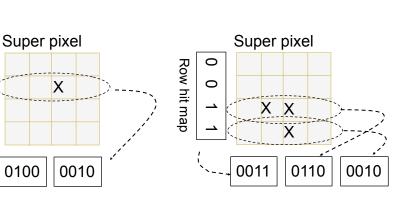

- Super Pixel Packet format proposed group together clusters of 4×4 pixels to create Super Pixels

- Share time-stamping information (crossover of digital regions)

- Save ~ 30% bandwidth

- Still requires several multi-gigabit readout links

- Challenge to divide work between FPGA readout and ASIC logic

- Current questions:

- Can we specify stream sizes to reduce workload on DAQ system?

- How much information should we decode for trigger pattern recognition stage?

- Is it worth making life difficult on-chip? Yes, power needs to stay < 1 W/chip

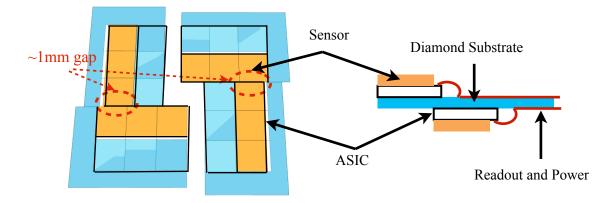

# Proposed module design

- Each Velo half to consist of 12 ASICs in 2 staves

- Each stave consists of:

- CVD diamond support structure (essential high thermal conductivity)

- Front- and back-mounted tiles of 3 ASICs with sensors bump-bonded on top

- Readout and power traces on the substrate

- Minimise radiation length

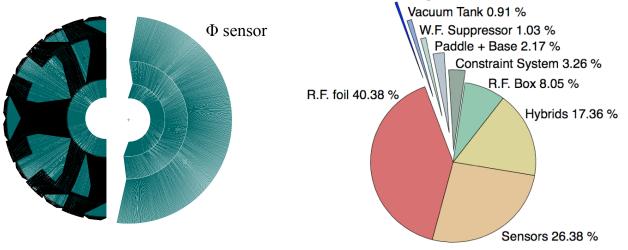

# Strip sensor option

- Background development of strip sensor option

- Should pixels exceed power/material restrictions

- Still challenging work to

- Keep strip capacitance low

- Increase number of strips aim for occupancies < 0.5%</p>

- Radiation hardness and performance n-on-p sensor baseline

- 40 MHz readout chip still to be developed, overlap with LHCb Silicon Tracker upgrade program

Cooling Block 0.46 %

- Reduce X<sub>0</sub>

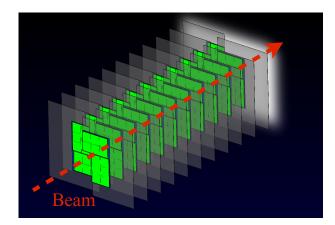

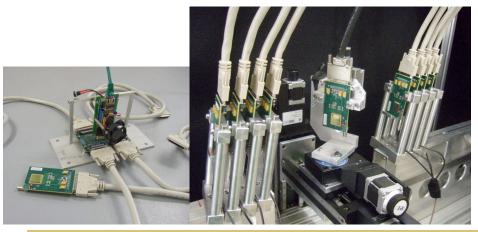

# Timepix telescope

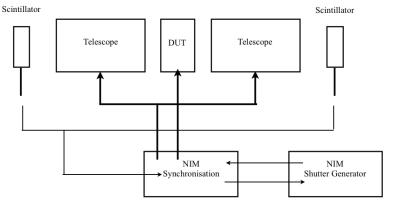

- 8 telescope planes, 7 in TOT mode and the other in TOA

- NIM crates providing shutter logic (coincident scintillator hits)

- 40MHz-synchronised triggers

- FPGA based readout RELAXd

- From "what if....?" to world class telescope in less than a year!

- $\sim 1 \mu m$  resolution at device under test

- ~1ns timestamp

- > 5 kHz track rate

2009 + 2010 data already published (more to come!) http://arxiv.org/abs/1103.2739

The LHCb Velo Upgrade - TIPP 2011

## Timepix for tracking

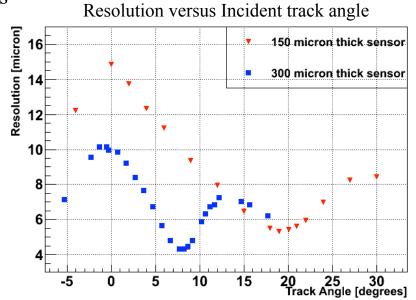

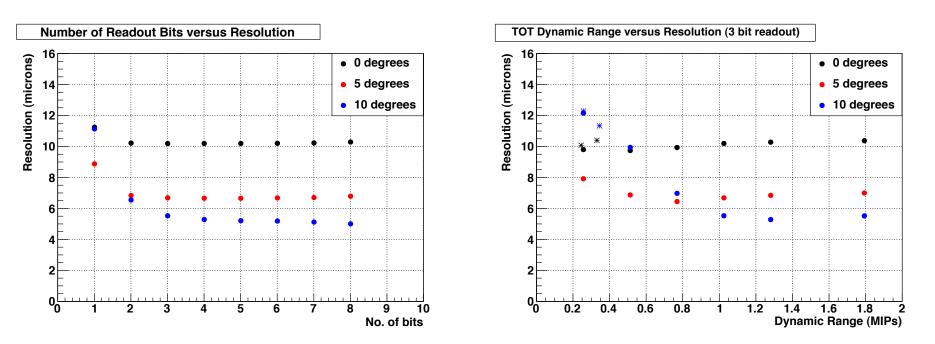

- Timepix performance comparable to current Velo sensors

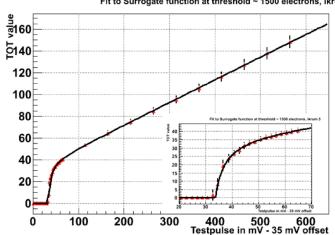

- Resolution with TOT better than binary resolution (aim for min. 4 bit TOT)

- Extensive studies on charge sharing

- Angular dependance of resolution

- HV dependence

- Sensor thickness

# Looking to the future...

- Latest chip from Medipix collaboration Medipix3

- Similar to Medipix2 no TOT, TOA

- 2 threshold counters per pixel, *limited* charge discrimination

- Group 4 pixels together to gain 3 bit TOT!

- Radiation hard, 130nm process => sensor irradiation studies!

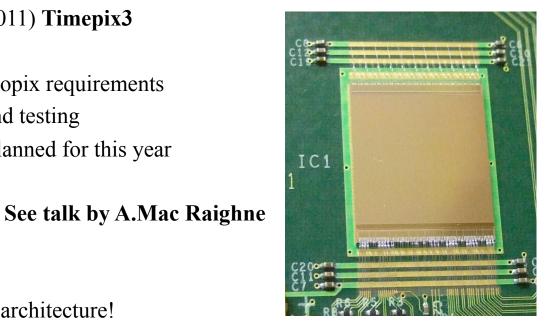

- Next step (submission ~end of 2011) Timepix3

- Simultaneous TOT and TOA

- Analogue FE identical to Velopix requirements

- Real prototype production and testing

- Many irradiated sensor studies planned for this year

- n-on-p

- Double sided 3D

- Diamond sensors

- Guard ring designs

- Finalise decisions about Velopix architecture!

### Summary

- Velo upgrade program well advanced and ambitious

- Velopix baseline pixel ASIC, strip option still realistic alternative

- Challenges "manageable" (ask us in 2 years!!)

- Radiation hardness comparable to requirements on other LHC experiments

- Power consumption must be kept low

- Data rates must be fine tuned and workload sensibly distributed

- Project independent of LHC upgrades!

# Backup

# Data reduction schemes

- Unformatted:

- 16 bit pixel address

- 12 bit bunch ID

- 4 bit TOT

- 32 bits per pixel!

- Using SPP format:

- Fixed 30 bit header (BCID, super pixel ID, row hit map)

Row hit map

0

~

0

0

0100

- Variable length column hitmap with TOT

- Share information across row boundaries of super pixels

- Bandwidth reduction  $\sim 30\%$

# Design lessons for Velopix

- For single hit clusters no need for TOT

- On multi-pixel clusters TOT essential for accurate reconstruction

- Study into TOT requirements for Velopix front end

- Necessary to tune preamplifier response, etc.

### Bias voltage