# SiPMs with bulk integrated resistors – Future perspectives –

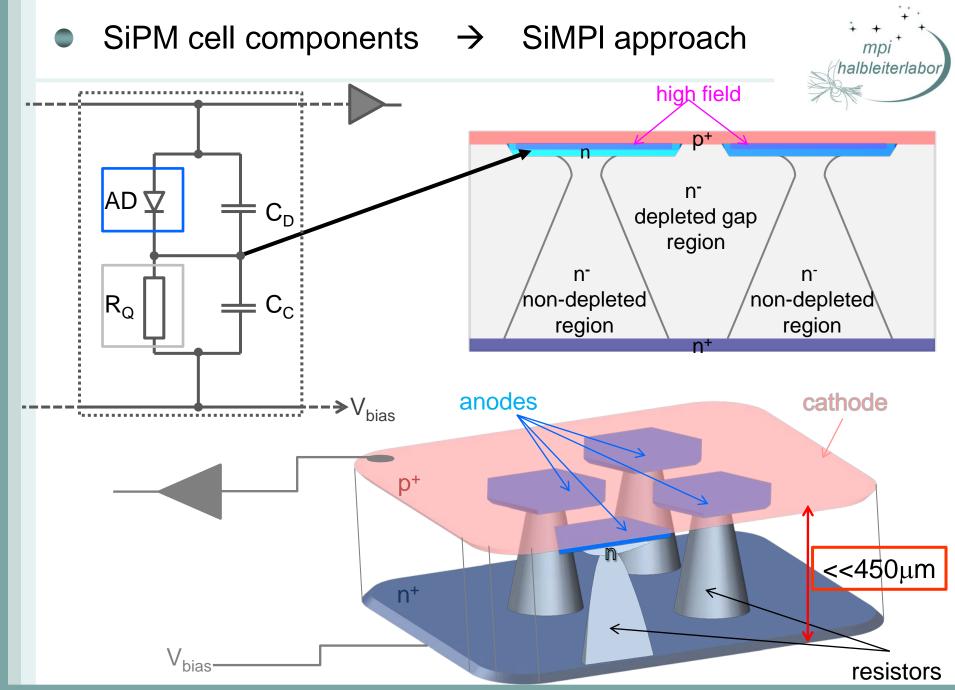

- •Concept of SiPMs with Bulk Integrated Quench Resistors SiPMI concept

- •First results from the prototype production

- •Future perspectives

J. Ninkovic<sup>1</sup>, L. Andricek<sup>1</sup>, C. Jendrysik<sup>1</sup>, G. Liemann<sup>1</sup>, G. Lutz<sup>2</sup>, H. G. Moser<sup>1</sup>, R. H. Richter<sup>1</sup>

<sup>1</sup>Max Planck Institute for Physics, Semiconductor Laboratory, Munich, Germany <sup>2</sup>PN Sensor GmbH, Munich, Germany

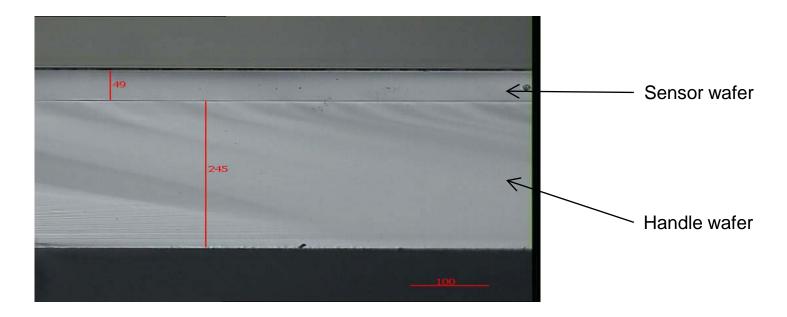

## SOI wafers

## Advantages and Disadvantages

## Advantages:

- no need of polysilicon

- free entrance window for light, no metal necessary within the array

- coarse lithographic level

- simple technology

- inherent diffusion barrier against minorities in the bulk -> less optical cross talk

#### **Drawbacks:**

- required depth for vertical resistors does not match wafer thickness

- wafer bonding is necessary for big pixel sizes

- significant changes of cell size requires change of the material

- vertical 'resistor' is a JFET -> parabolic IV -> longer recovery times

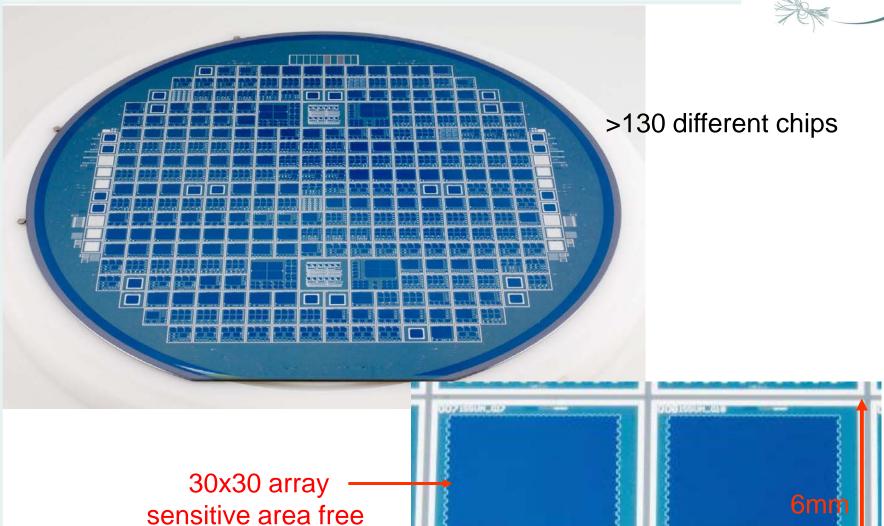

## Prototype production

Jelena Ninkovic

TIPP 2011, Chicago, IL

€ 6mm\*\*\*

>===0=O=

### Results

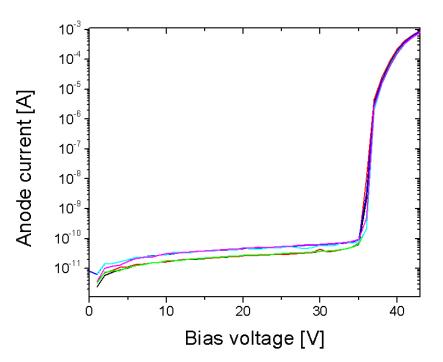

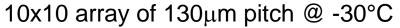

#### Static measurements

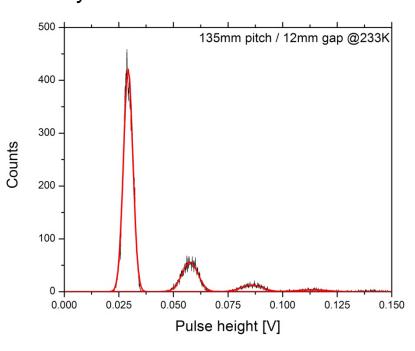

### Dynamic measurements

High homogeneity over big distances!

6 (10x10) arrays placed over

6mm distance

High homogeneity within the array!

## Gain linearity

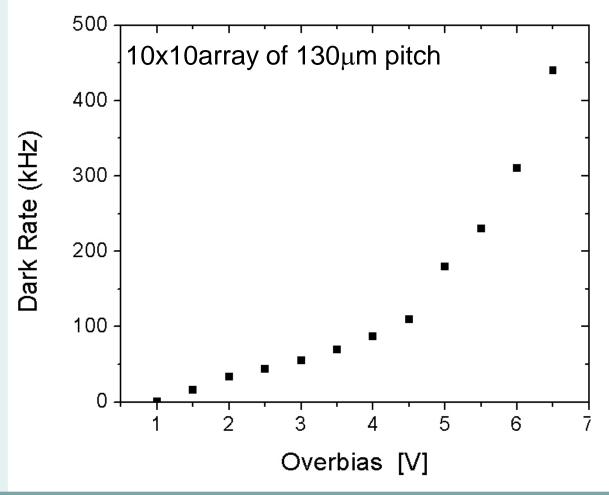

### Dark rate

Due to the non optimal process sequence of the high field processing ~10MHz @300K for 4V overbias

Normal operation up to 4.5V overbias @227K

# Fill factor & Cross Talk & Photon Detection Efficiency halbleiterlabor

#### Produced SiMPI devices have the world record in the fill factors!

| Pitch / Gap  | Fill factor | Cross talk<br>meas.<br>(∆V=2V) | PDE calc.<br>(∆V=2V) | PDE calc.<br>(∆V=5V) |

|--------------|-------------|--------------------------------|----------------------|----------------------|

| 130μm / 10μm | 85.2%       | 29%                            | 39%                  | 61%                  |

| 130μm / 11μm | 83.8%       | 27%                            | 38%                  | 60%                  |

| 130μm / 12μm | 82.4%       | 25%                            | 37%                  | 59%                  |

| 130μm / 20μm | 71.6%       | 15%                            | 32%                  | 52%                  |

#### PDE estimate:

•Optical entrance window: 90% @400nm

•Geiger efficiency: 50% @ 2V overbias 80% @5V overbias

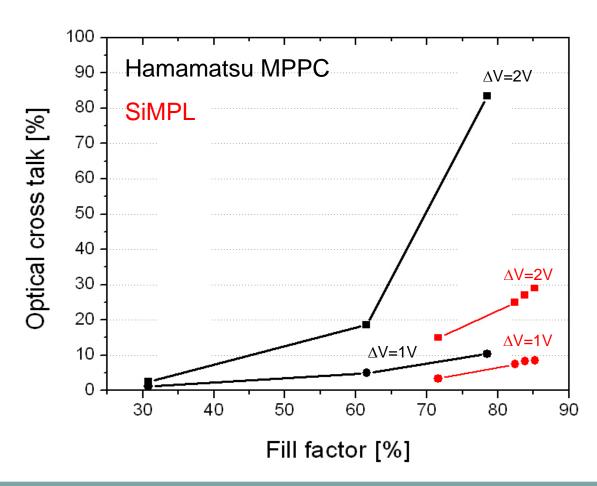

## Fill factor & Cross Talk

## Produced SiMPI devices have the world record in the fill factors and still lower cross talk!

No special cross talk suppression technology applied just intrinsic property of SiMPI devices

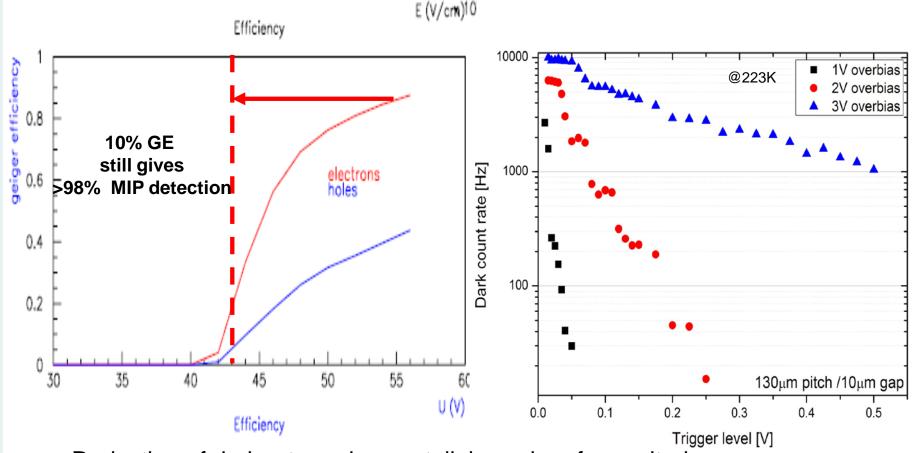

## Detection of particles

Excellent time stamping due to the fast avalanche process (<1ns)

MIP gives about 80pairs/ $\mu$ m  $\rightarrow$  huge signal in SiPM $\rightarrow$  allows operation at small  $\Delta V$

Reduction of dark rate and cross talk by order of magnitude

## Detection of particles

Dark rate:  $1 \text{ MHz/mm}^2 = 1 \text{ hit/}\mu\text{m}^2/\text{s} = O(\text{Belle II})$

With 20 µm pitch and 12 ns time stamp: occupancy: 2.5 x10<sup>-6</sup>

Power (analogue): ~ 5 μW/cm<sup>2</sup> Dominated by dark rate

#### Possible problems:

- Radiation hardness (dark rate increases due to bulk damage)

- Cross talk

- Efficiency (fill factor)

- Digital power

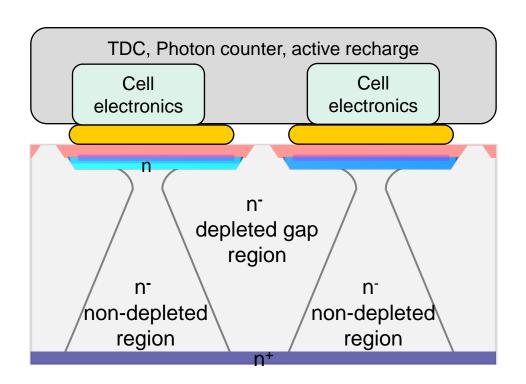

## Next generation SiMPI devices

Topologically flat surface

High fill factor

Adjustable resistor value

Pitch limited by the bump bonding

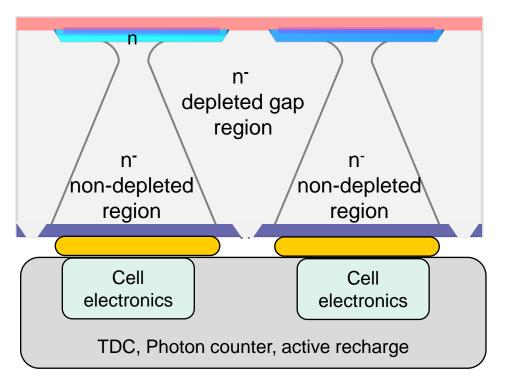

## Next generation SiMPI devices

Topologically flat and free surface High fill factor Sensitive to light

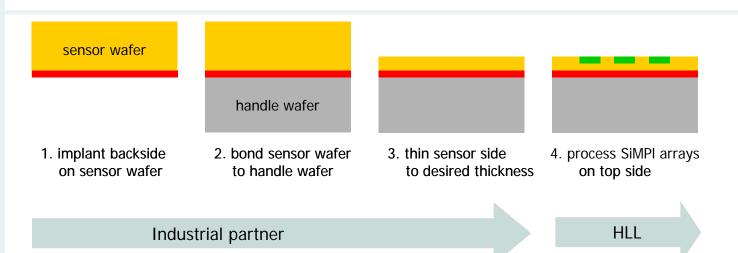

1. Structured implant on backside 2. bond sensor wafer on sensor wafer

3. thin sensor side to desired thickness

4. process SiMPI arrays on top side

## Summary

## Silicon photomultiplier array with individual quench resistors, integrated into the silicon bulk - SiMPI detector

- Required flexibility for quench resistor adjustment comes with wafer bonding technique (for small pixels an epitaxial layer is also suitable)

- No polysilicon resistors, contacts and metal necessary at the entrance window

- Geometrical fill factor is given by the need of cross talk suppression only

- Very simple process, relaxed lithography requirements

Prototype production finished – quenching works, first measurements very promising, functional devices with very high fill factor and low cross talk

#### Next generation SiMPI devices with electronics interconnected

- on front side can be used for trackers at future colliders

- on back side → high sensitivity, high fill factor digital SiPM

## Thank you for your attention!