## HIPPO, a Flexible Front-End Signal Processor for High-Speed Image Sensor Readout

Carl Grace, Dario Gnani, Jean-Pierre Walder, and Bob Zheng

June 10, 2011

# **Outline of Presentation**

- Motivation for HIPPO

- LBNL thick, fully column-parallel CCDs

HIPPO Design

Layout and Results

# High-Speed Image Pre-Processor with Oversampling (HIPPO)

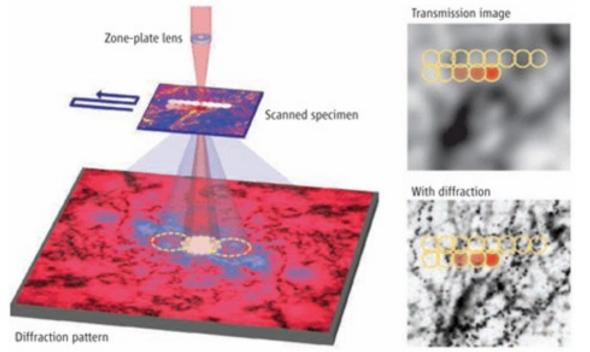

Emerging soft x-ray imaging applications for dynamic processes require greatly increased readout speeds

Ptchyographic x-ray microscopy

Figure: H.N. Chapman, Science 321 352 (2008)

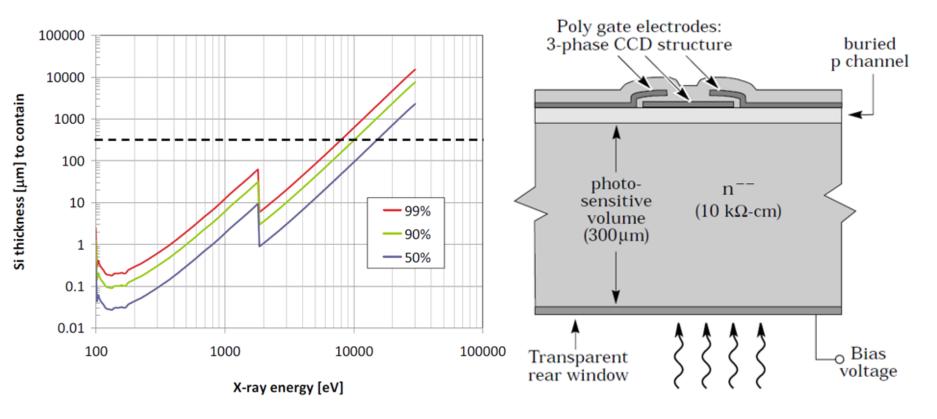

# LBNL thick, high p, fully depleted CCDs

- LBNL-developed thick CCDs provide excellent soft x-ray response

- Lack of field-free region provides excellent point spread function

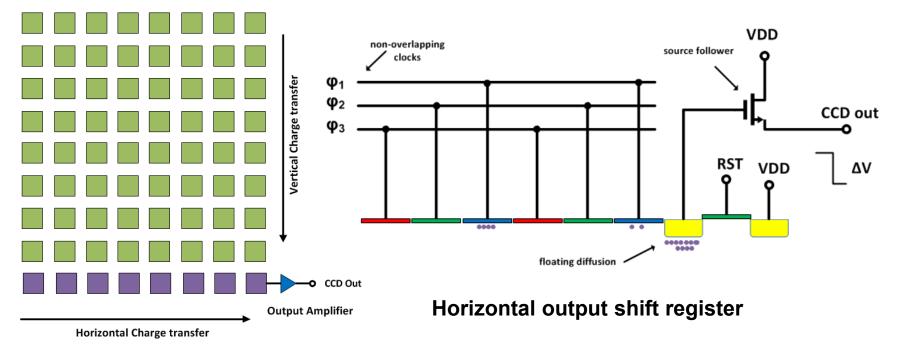

# **Conventional Charge-Coupled Devices**

- Noiseless, nearly lossless charge transfer (high SNR)

- Improved DR\*Size\*Speed product compared to CMOS sensors

- Speed limited by serial output

- Solution  $\rightarrow$  Parallelize column readout (column readout up to 10 MHz)

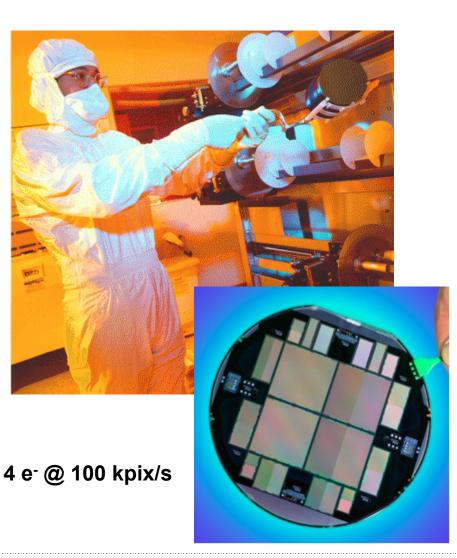

# CCDs @ LBNL Micro Systems Lab (MSL)

LBNL 2k x 4k CCD: Blue: H- at 656 nm Green: SIII at 955 nm Red: 1.02 nm

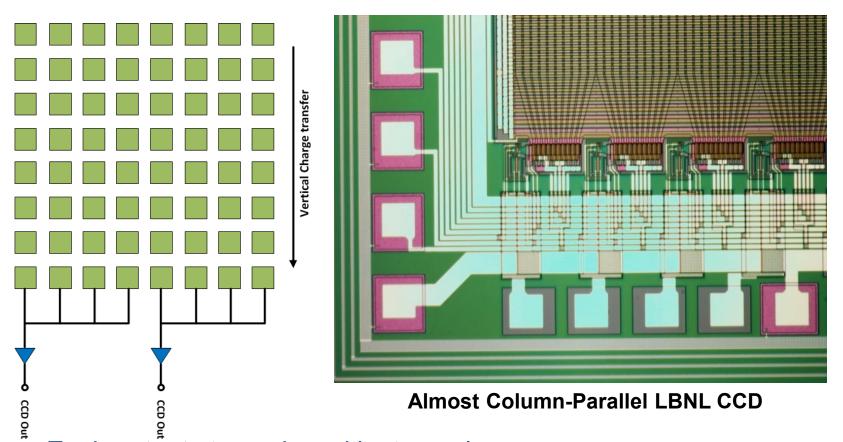

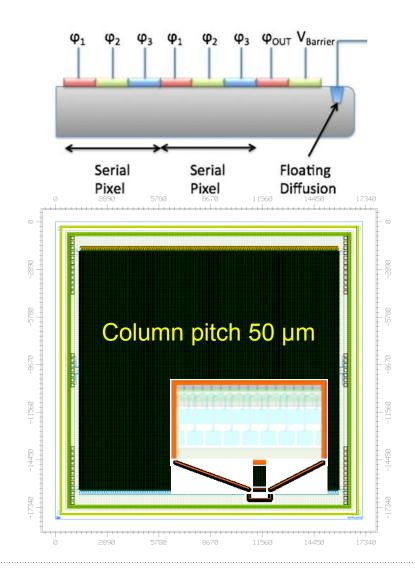

## "Almost" Column-Parallel LBNL CCD

- Each output stage shared by ten columns

- Not practical to make more parallel with on-CCD charge conversion

- Solution → Fully column-parallel CCD

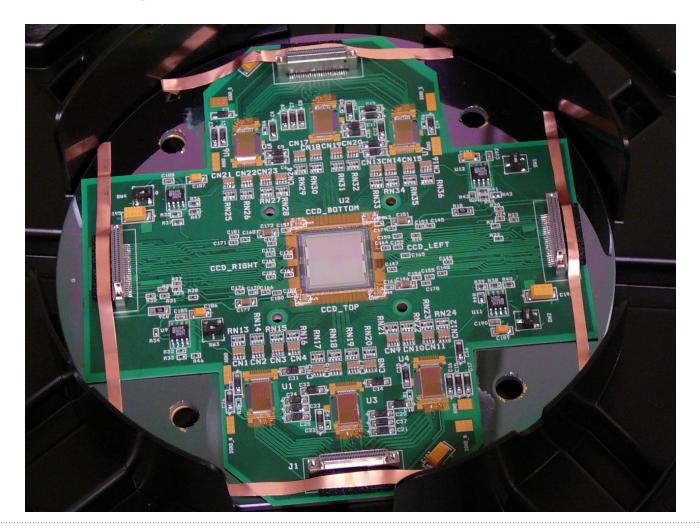

### Fast CCD X-ray camera board

10 e<sup>-</sup> @ 1 Mpix/s

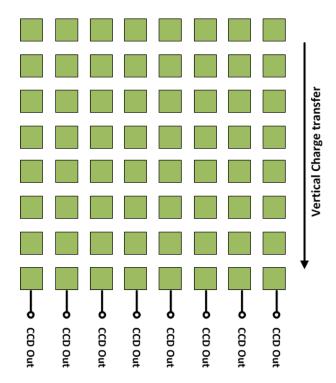

# **Fully Column-Parallel LBNL CCD**

Megapixel square sensor has ~1000 columns  $\rightarrow$  need custom IC readout

No room for output amplifier → need charge-sensitive readout

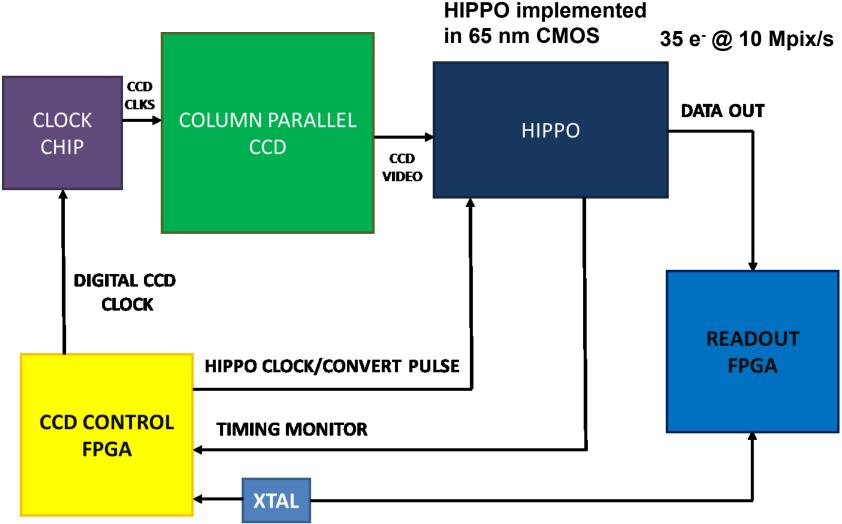

# **HIPPO Application**

### **HIPPO Channel**

Channel pitch-matched to 50 µm CCD column Need X4 ADC multiplexing

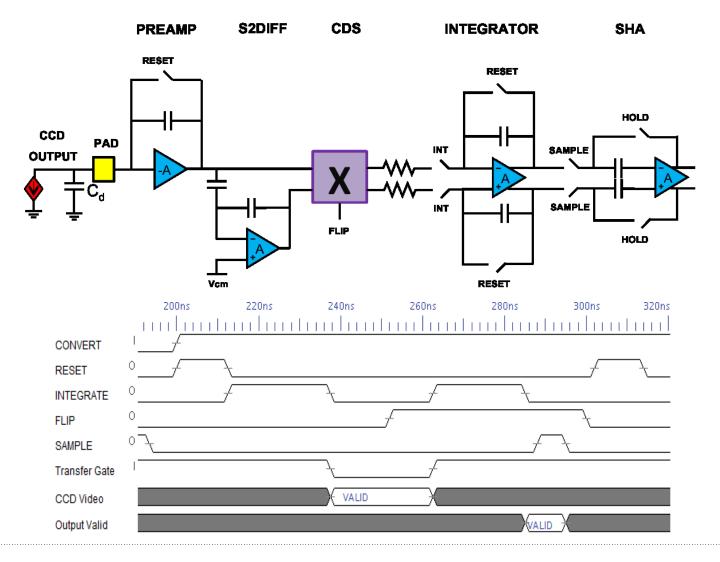

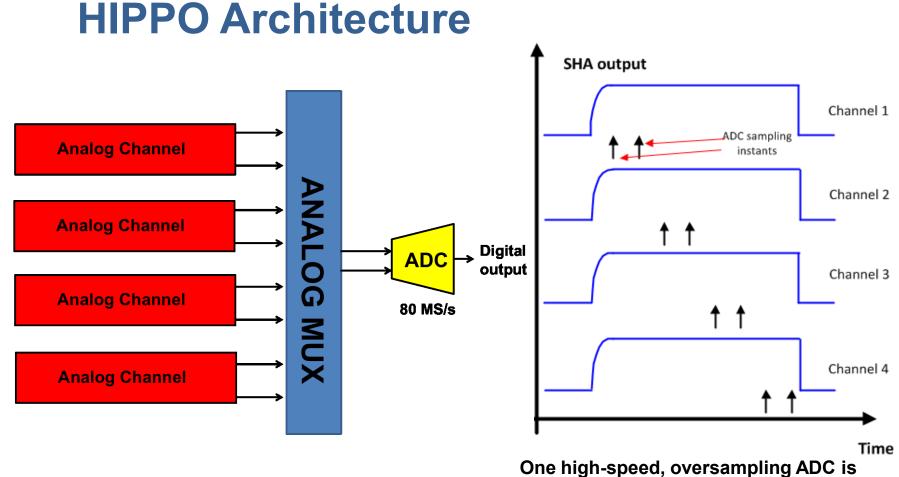

# **HIPPO Timing**

**HIPPO contains 16 readout channels**

multiplexed across each 4 channels

ADC noise reduced as OSR<sup>1/2</sup>

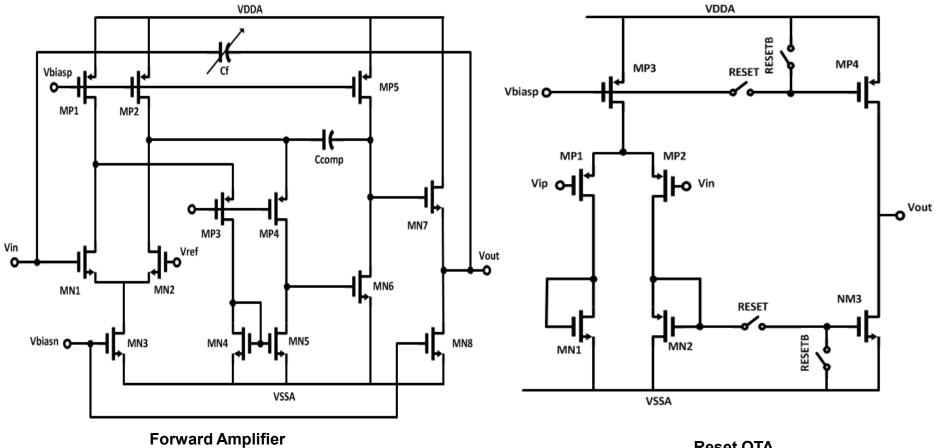

## **HIPPO Preamplifier**

| Parameter            | Value       | Units                               |

|----------------------|-------------|-------------------------------------|

| Full Scale           | 50k /<br>1M | e-                                  |

| CCD charge injection | 200k        | e⁻                                  |

| Input noise          | 35 / 24     | e <sup>-</sup> (max /<br>min speed) |

| Settling time        | < 15        | ns                                  |

| Charge loss          | < 1         | %                                   |

| Linearity            | 10          | bits                                |

| Power                | 5           | mW                                  |

### **HIPPO Preamplifier**

**Reset OTA**

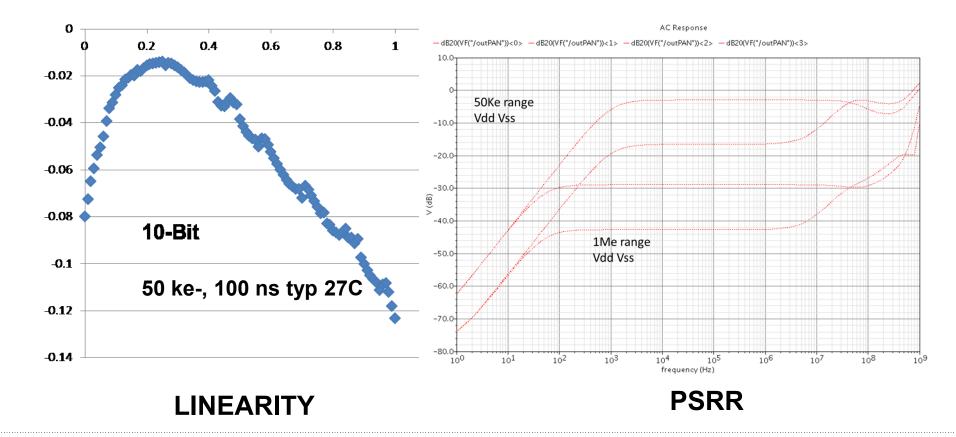

### **HIPPO Preamplifier performance**

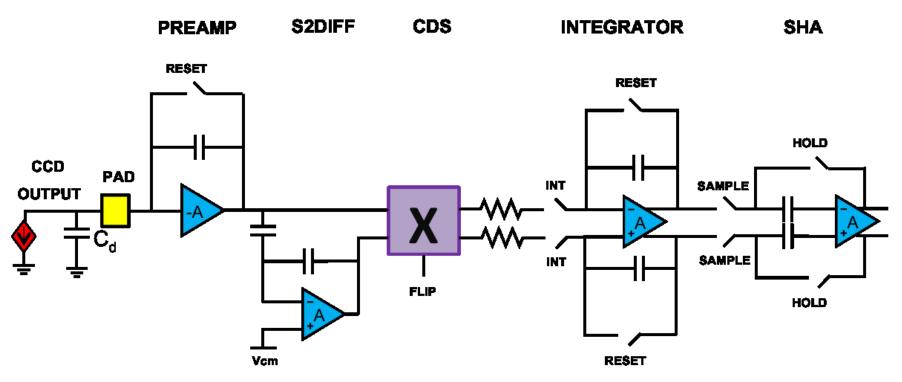

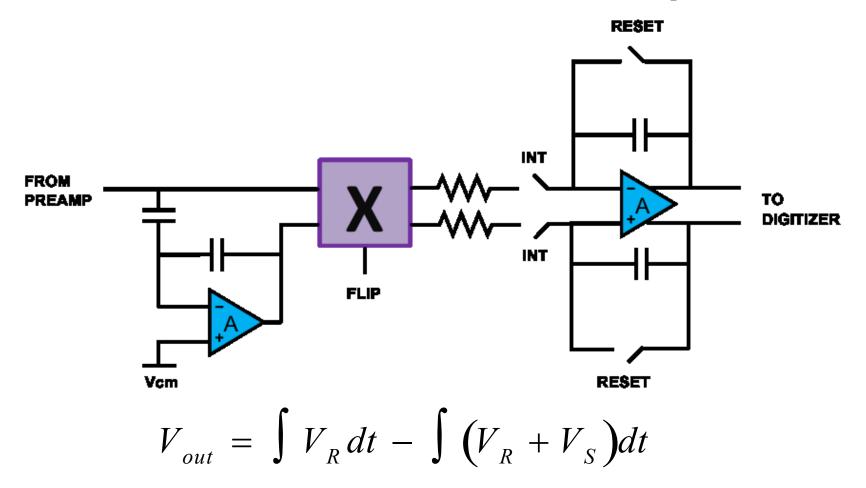

### **HIPPO Correlated Double-Sampler**

### **HIPPO Correlated Double-Sampler**

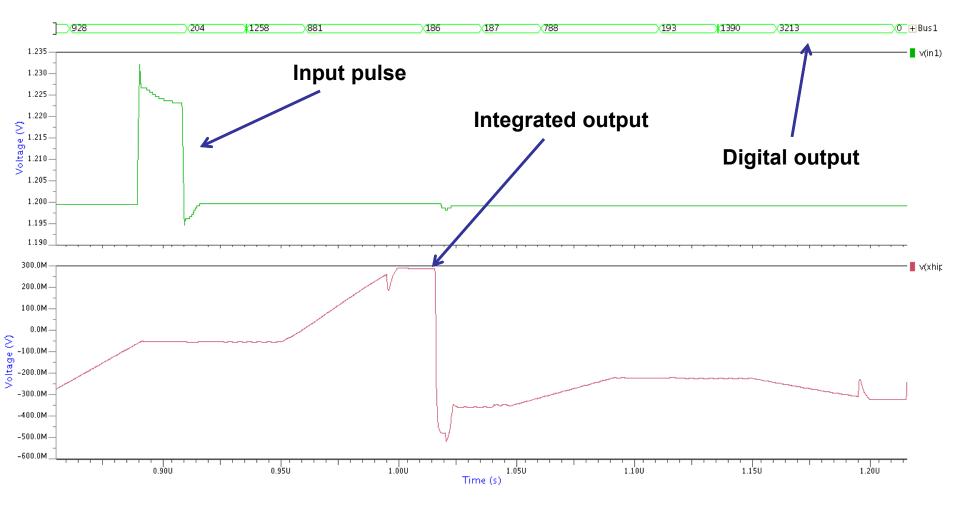

#### **Channel simulation**

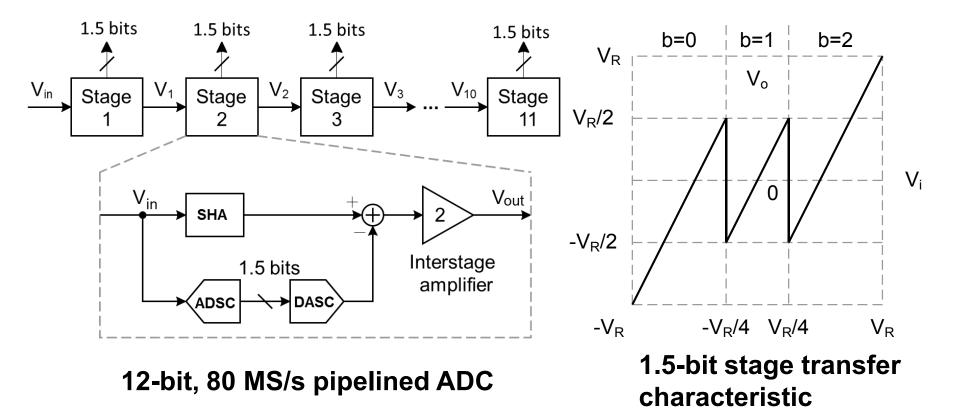

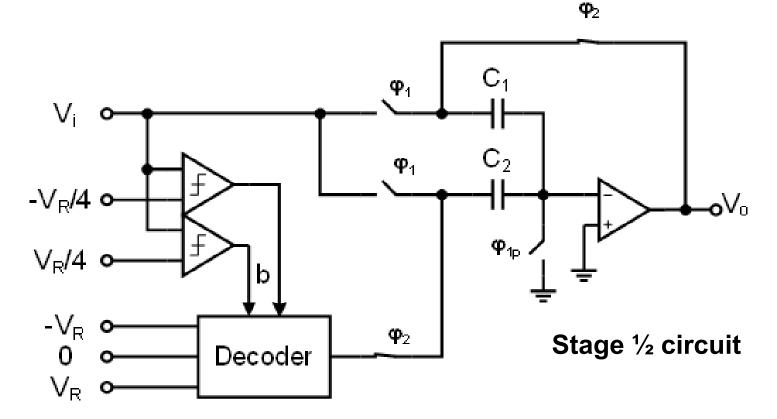

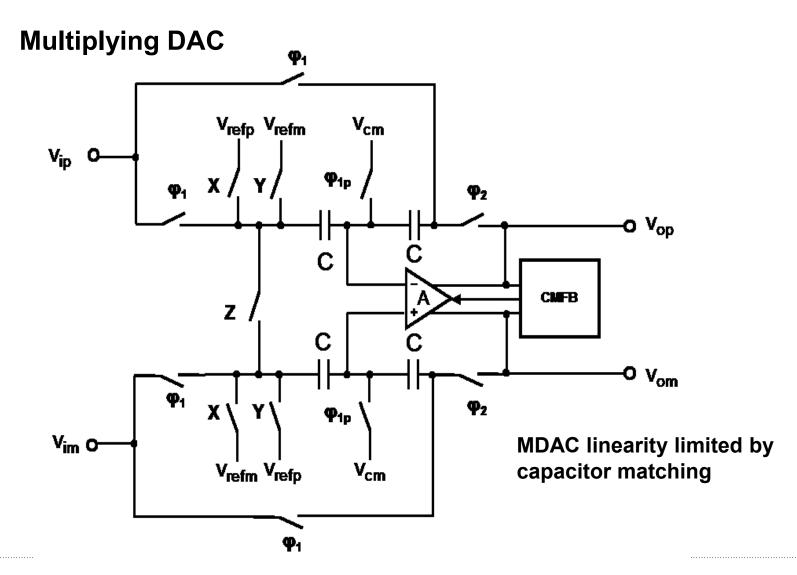

Flip-around MDAC architecture minimizes stage settling time

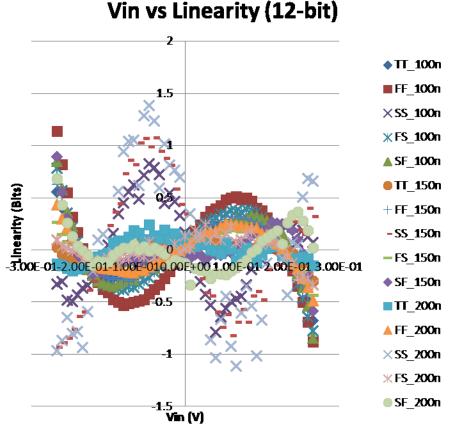

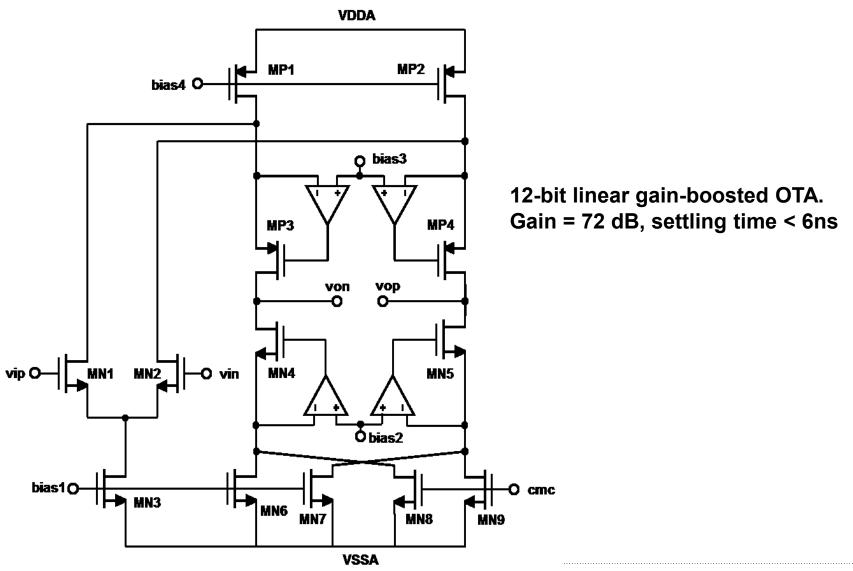

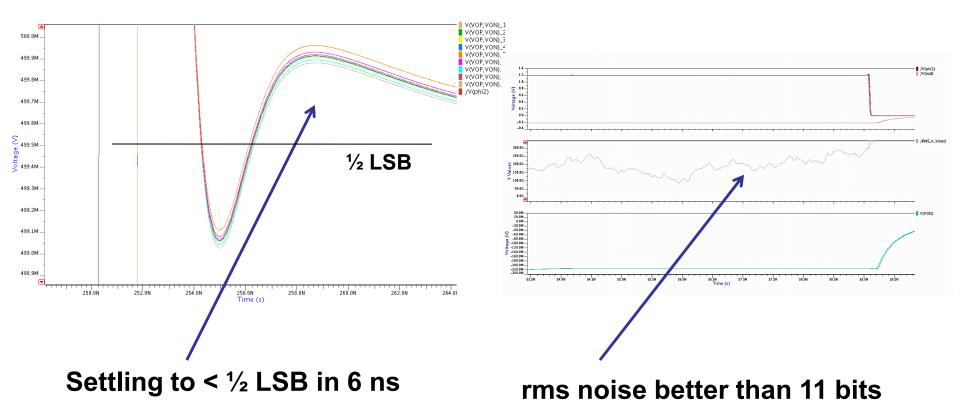

## **MDAC** performance

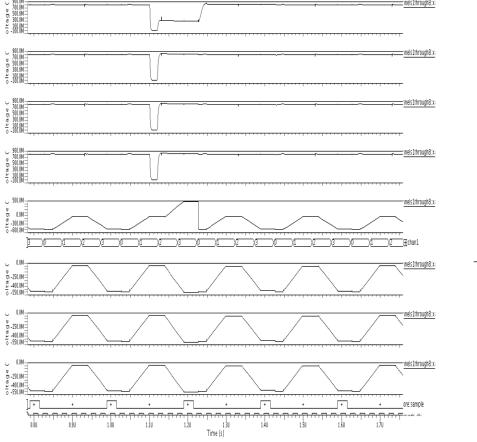

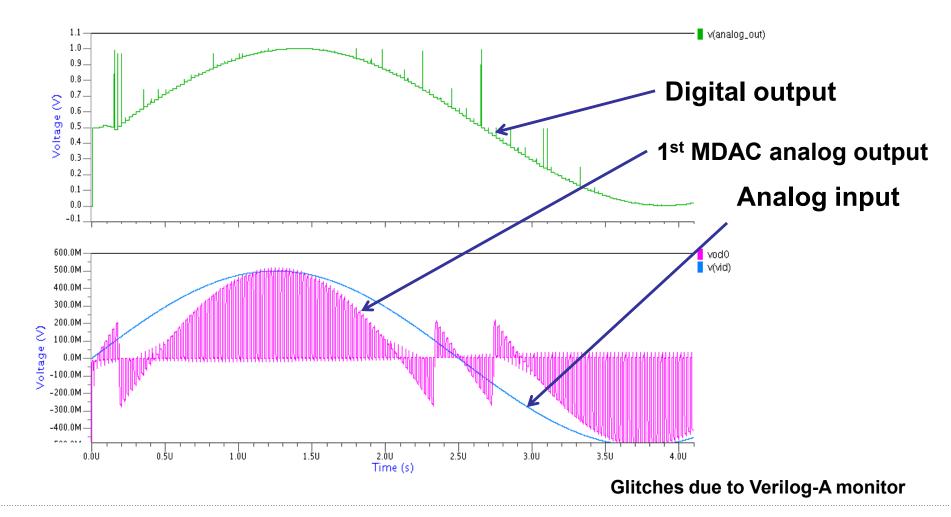

### **Post-layout ADC functional verification**

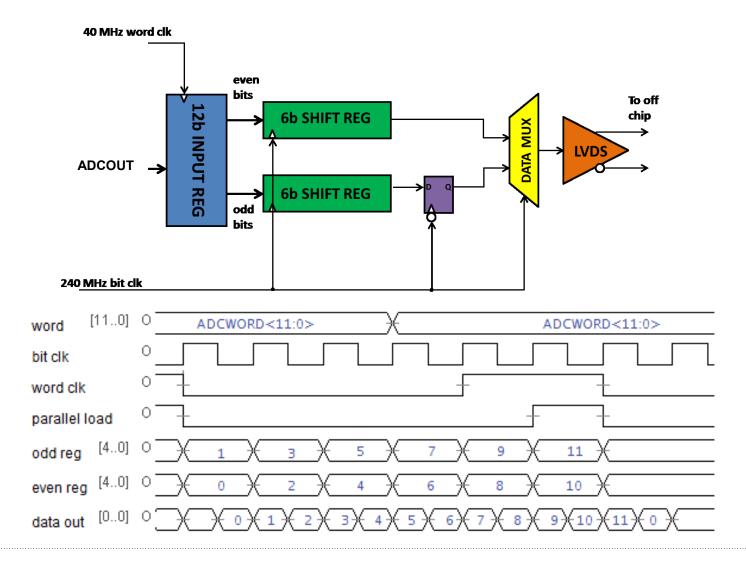

### **Serializer**

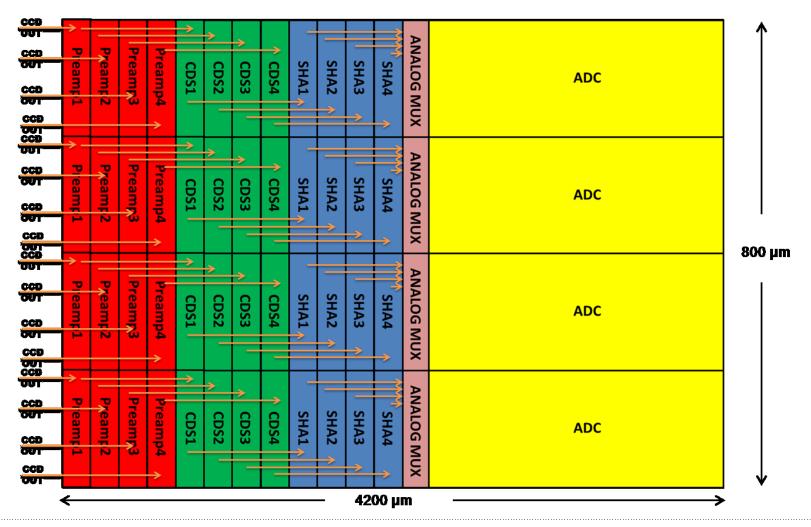

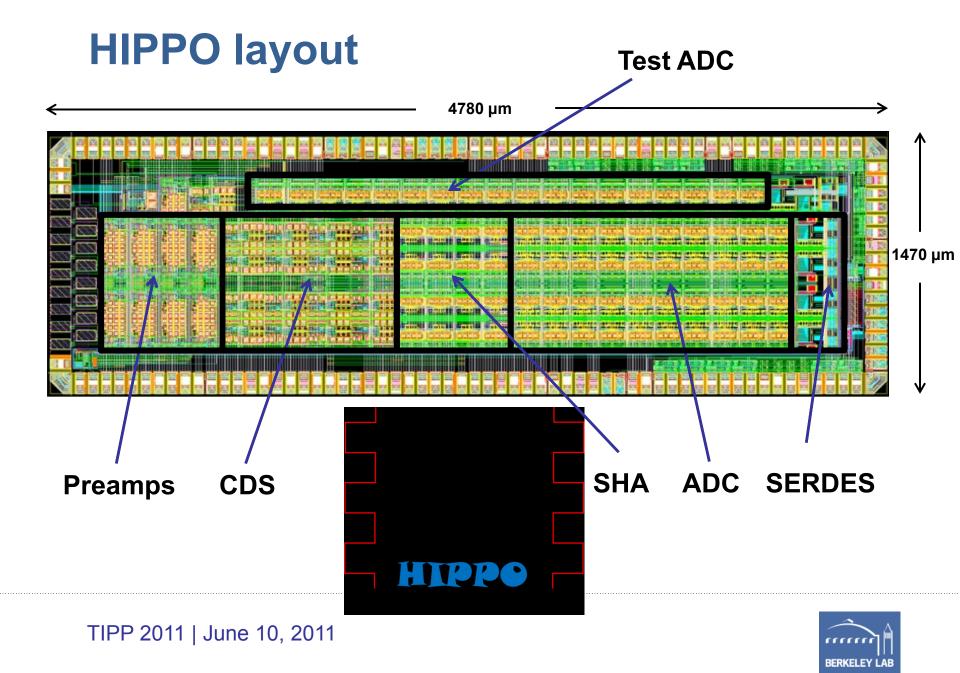

### **HIPPO layout strategy**

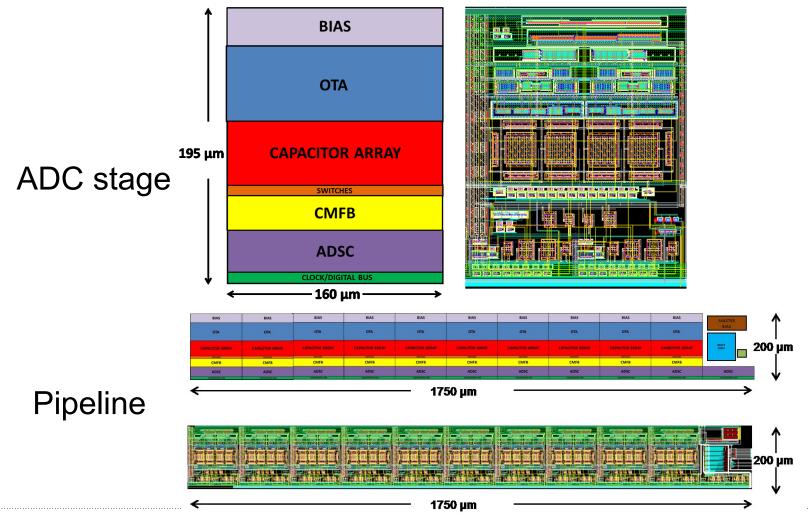

## **Pitch-matched ADC layout**

# **Post-layout full-chip functional simulation**

# Summary

| Requirement       | Performance                                                                           |

|-------------------|---------------------------------------------------------------------------------------|

| Channel rates     | 10, 5, 2.5, 1.25, 0.625 MHz                                                           |

| ADC rates         | 80, 40, 20, 10 MS/s                                                                   |

| Input Noise       | 35 e <sup>-</sup> at 10 MHz, 24 e <sup>-</sup> at 2.5 MHz<br>@ C <sub>in</sub> 500 fF |

| Output resolution | 12 bits                                                                               |

| Linearity         | 0.1 % (10 bits)                                                                       |

| External Clock    | 240 MHz LVDS; fully differential                                                      |

| Output datarate   | 480 Mb/s                                                                              |

| Channel pitch     | 50 µm                                                                                 |

| Power dissipation | 25 mW / channel                                                                       |

| Active area       | 3.5 mm <sup>2</sup>                                                                   |

| Technology        | 65 nm CMOS                                                                            |

## Acknowledgements

• LBNL Detector Development Group

• LBNL Integrated Circuits Group

Department of Energy Office of Basic Energy Sciences

#### UNIVERSITY OF CALIFORNIA