# Recent progress of the pixel detectors R&D based on the SOI technology

#### Toshinobu Miyoshi (KEK IPNS)

Co-Authors:

- Y. Arai, Y. Fujita, R. Ichimiya, Y. Ikegami, Y. Ikemoto, T. Kohriki,

- K. Tauchi, T. Tsuboyama, Y. Unno (KEK)

- K. Hara, K. Shinsho (Univ. of Tsukuba)

- H. Kasai, M. Okihara (OKI SEMICONDUCTOR MIYAGI Co., Ltd.)

- H. Katsurayama, Y. Ono, Y. Onuki (Tohoku Univ.)

- K. Hanagaki (Osaka Univ.)

- A. Takeda (SOUKENDAI)

#### Outline

- 1. Overview

- 2. SOI pixel detectors

- 3. Progress & detector performance

- 4. Current issue

- 5. Conclusion & Schedule

# Overview of the SOI monolithic pixel detector R&D

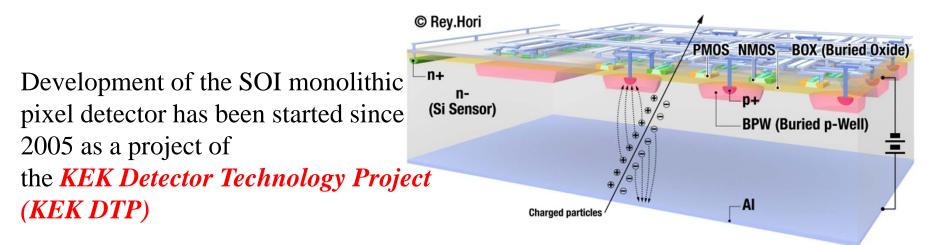

#### The features of SOI monolithic pixel detector

- Use commercial SOI wafer

- High resistivity silicon --- sensor Low resistivity silicon --- circuit SiO<sub>2</sub> --- insulator

- No mechanical bump bonding

- Lower junction capacitance

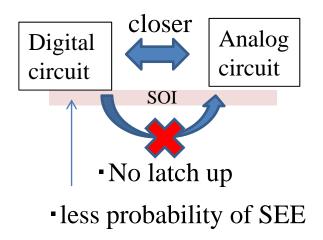

- Full dielectric isolation

- Smaller parasitic capacitance

- Technology based on industry standards

- $\rightarrow$  lower cost

## SOI Process & MPW

| Process (OKI<br>Semiconductor<br>Co. Ltd.) | 0.2μm Low-Leakage Fully-Depleted (FD) SOI CMOS<br>1 Poly, <b>5 Metal layers</b> , MIM Capacitor, DMOS option, Core (I/O) 1.8 (3.3) V                                                                                              |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOI wafer<br>(200 mm ¢<br>=8 inch)         | Top Si : Cz, ~18 $\Omega$ -cm, p-type, ~40 nm thick<br>Buried Oxide: 200 nm thick<br>Handle wafer: Cz ~700 $\Omega$ -cm ( <i>n</i> -type), 650 $\mu$ m thick<br>FZ ~ 8 k $\Omega$ -cm ( <i>n</i> - or p- type), 650 $\mu$ m thick |

| Backside                                   | Thinned to 260 µm and sputtered with Al (200 nm). (to be optimized)                                                                                                                                                               |

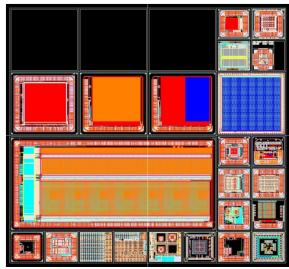

#### Multi Project Wafer (MPW) run

- KEK organizes MPW runs

- Mask is shared to reduce cost of a design

- Including pixel detector chip and SOI-CMOS circuit chip

- Once a year in 2005-2008, 2011

- Twice a year in 2009, 2010, (2012-?

- University & institution

KEK, FNAL, LBNL, Kyoto Univ, Tohoku Univ, Univ. of Tsukuba, RIKEN, JAXA, Krakow, Hawaii, and more...

#### Supporting companies

OKI Semiconductor Co. Ltd., OKI Semiconductor Miyagi Co. Ltd., T-Micro Co. Ltd., Rigaku Co. Ltd

#### MPW FY10-1 (Aug. 2010)

20.8mm

#### **KEK SOI** Pixel detectors

- Integration-type pixel detector

(INTPIX1,2,3a,3b,3c,3e,4 and Dual-mode INTPIX=DIPIX)

A.Takeda's talk ID=282, (11 Sat.)

- Counting-type pixel detector (CNTPIX2,3,4,5)

Specification summary of integration-type pixel detector since 2008

|   |          | pixel size | # of pixels | Effective Area | Chip area   | Fabrication | # of       | CDS in |

|---|----------|------------|-------------|----------------|-------------|-------------|------------|--------|

|   |          | [µm]       |             | [mm]           | [mm]        | year        | pixel type | pixel  |

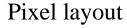

|   | INTPIX3a | 20 x 20    | 128 x 128   | 2.56 x 2.56    | 5 x 5       | FY08        | 8          | No     |

|   | INTPIX3b | 20 x 20    | 128 x 128   | 2.56 x 2.56    | 5 x 5       | FY09-1      | 8          | No     |

| 4 | INTPIX4  | 17 x 17    | 832 x 512   | 14.144 x 8.704 | 15.3 x 10.2 | FY09-1      | 1          | Yes    |

|   | INTPIX3c | 20 x 20    | 128 x 128   | 2.56 x 2.56    | 5 x 5       | FY09-2      | 8          | No     |

|   | INTPIX3e | 16 x 16    | 192 x 192   | 3.072 x 3.072  | 5 x 5       | FY10-1      | 1          | No     |

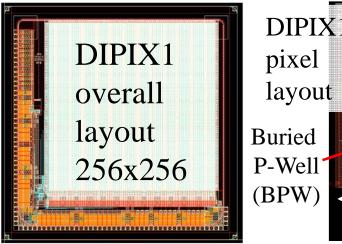

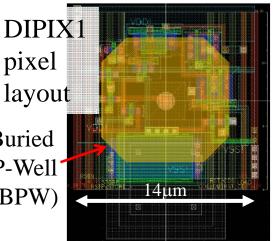

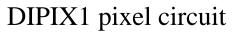

|   | DIPIX1   | 14 x 14    | 256 x 256   | 3.584 x 3.584  | 5 x 5       | FY10-1      | 1          | Yes    |

|   | DIPIX2   | 14 x 14    | 256 x 256   | 3.584 x 3.584  | 5 x 5       | FY10-1      | 2          | Yes    |

## Progress of SOI pixel detector R&D (1)

## Progress of SOI pixel detector R&D (2)

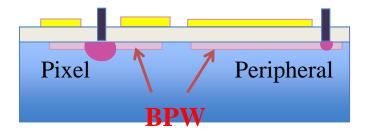

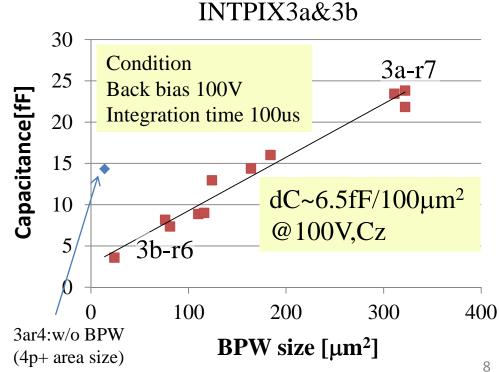

# Sensor gain

Pixel contact size ~ a few µm

"BPW-in-pixel" increases sensor capacitance

→ Sensor gain decreases

- Gain measurement was done using SR X-ray in KEK Photon Factory

- X-Ray from 6 keV 18.5 keV in BL-14A

- Internal gain was measured and then calculated capacitance

-Gain decrease with "BPW-in-pixel" size

-Capacitance ~ 8fF

Gain ~  $20\mu$ V/e- @ 3b-r6 (optimized BPW size)  $\rightarrow$  applied to INTPIX3e

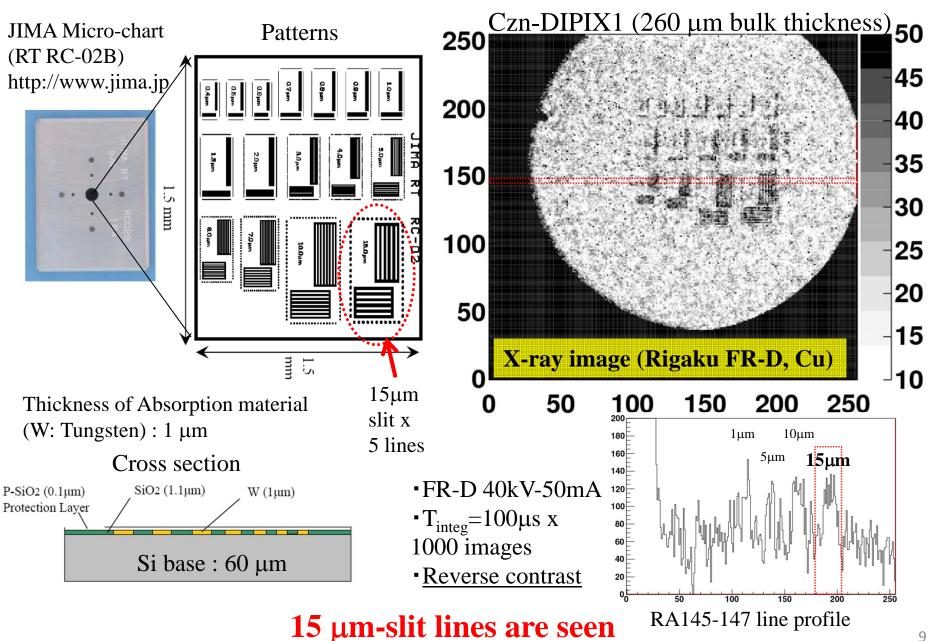

# DIPIX1(14µm pixel) spatial resolution

# Progress of SOI pixel detector R&D (3)

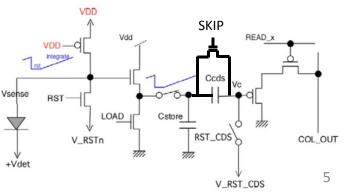

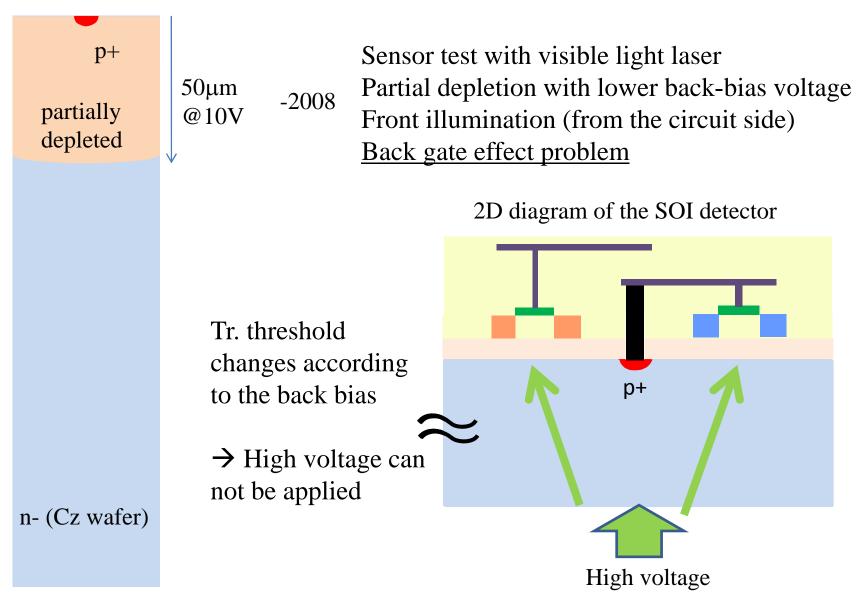

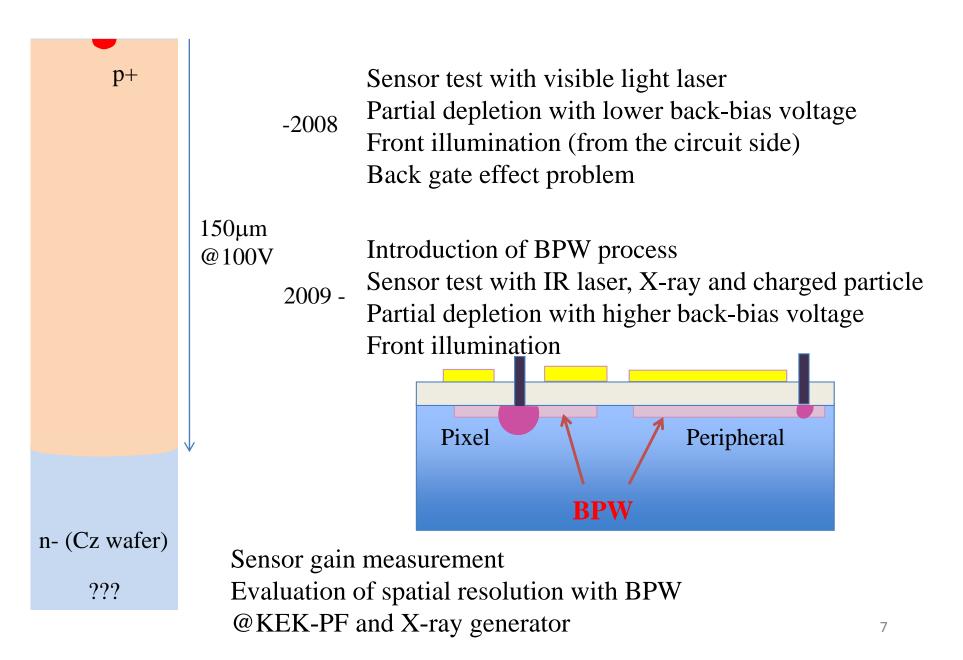

|                        | p+                        | 100μm<br>@~80V       | -2008 <sup>]</sup> | Sensor test with visible light laser<br>Partial depletion with lower back-bias voltage<br>Front illumination<br>Back gate effect problem<br>Introduction of BPW process |

|------------------------|---------------------------|----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                           |                      |                    | Sensor test with IR laser, X-ray and charged particle                                                                                                                   |

|                        | n- (Cz wafer)             |                      | 2009 -             | Wafer thinning by TAIKO process                                                                                                                                         |

|                        |                           |                      |                    | - 100µm bulk thickness                                                                                                                                                  |

|                        |                           | $\checkmark$         |                    | - High energy particle detection (MIP detection)                                                                                                                        |

| г                      |                           |                      | 4                  | - Reduction of material budget                                                                                                                                          |

| TAIKO=drum in japanese |                           |                      |                    | - Full depletion                                                                                                                                                        |

|                        |                           |                      |                    | - Back illumination                                                                                                                                                     |

|                        | La                        | minated Tape         | patterns           |                                                                                                                                                                         |

|                        |                           |                      |                    | Thinned INTPIX3a evaluation experiment                                                                                                                                  |

| 0                      | ~~~                       |                      |                    | - Red & IR laser                                                                                                                                                        |

|                        |                           |                      |                    | - High energy particle detection                                                                                                                                        |

|                        |                           |                      |                    |                                                                                                                                                                         |

| - 1                    | AIKO Process              |                      | ional Process      |                                                                                                                                                                         |

| Photo:                 | http://www.disco.co.jp/jp | /solution/library/ta | iko.html           | 10                                                                                                                                                                      |

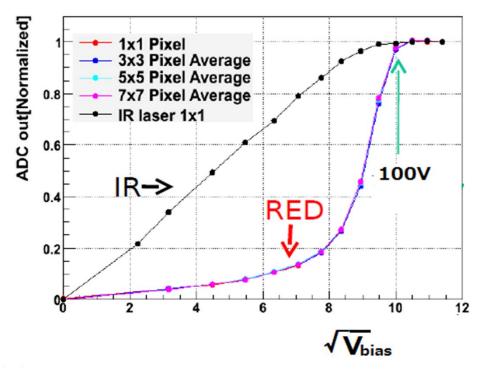

## Sensor response after wafer thinning

Front (IR) & back (red) illumination experiment

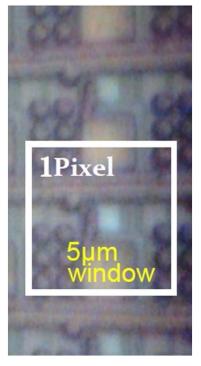

100 μm-INTPIX3a -Integration time = 10 μs -IR laser focused inside 5μm window -1064nm IR : 3mm penetration depth

Red laser 634nm

stops at surface

Remove aluminum

from the back side

Package photo

$(V_{bias} = V_{back} - V_{gnd = bias})$

Pixel photo

#### **Full depletion at ~100V**

Univ. of Tsukuba

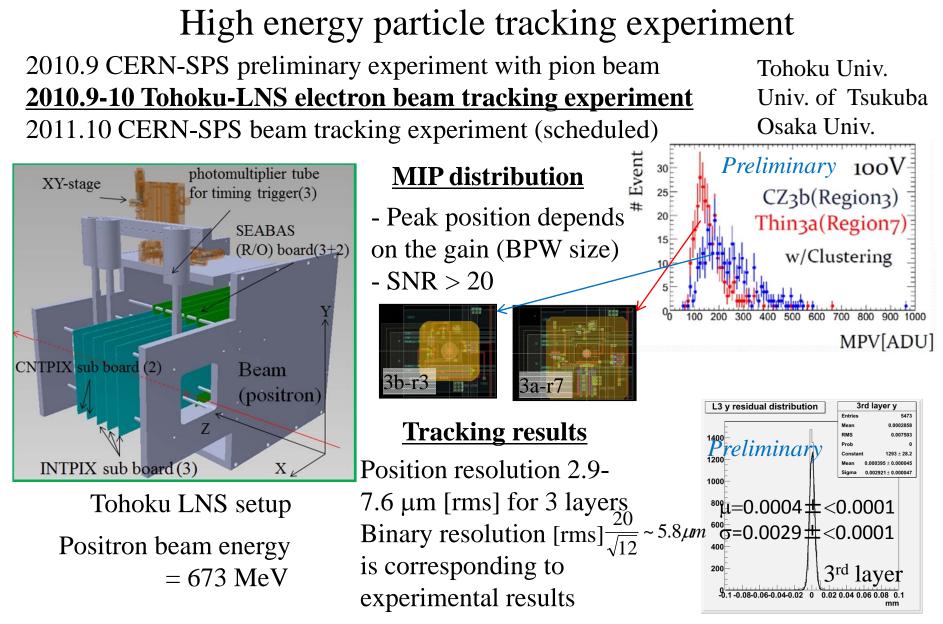

We had achieved the first high-energy particle tracking with KEK-SOI detector

## Progress of SOI pixel detector R&D (4)

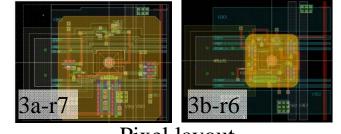

| p+               | -2008 Sensor test with visible light laser<br>Partial depletion with lower back-bias voltage<br>Front illumination<br>Back gate effect problem                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 260μm2009 -Introduction of BPW process@~30VSensor test with IR laser, X-ray and charged particle@~30VPartial depletion with higher back-bias voltageorFront illumination500μmFront illumination |

| n-<br>(FZ wafer) | @~100V<br>Introduction of FZ wafer<br>Sensor test with IR laser, X-ray and charged<br>2010 - particle<br>Full depletion with lower back-bias voltage<br>Back illumination                       |

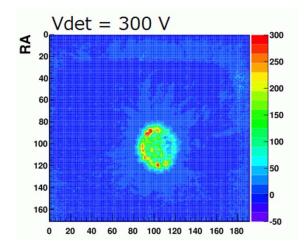

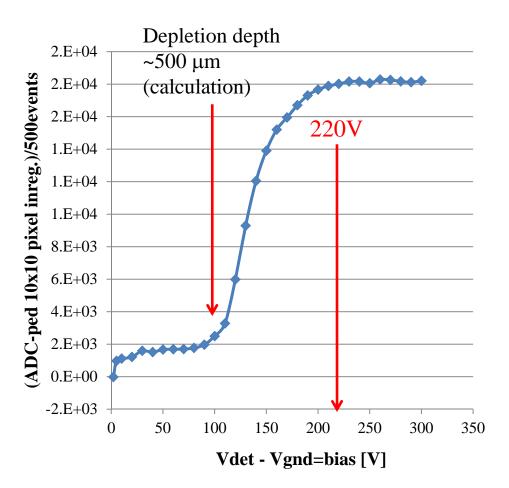

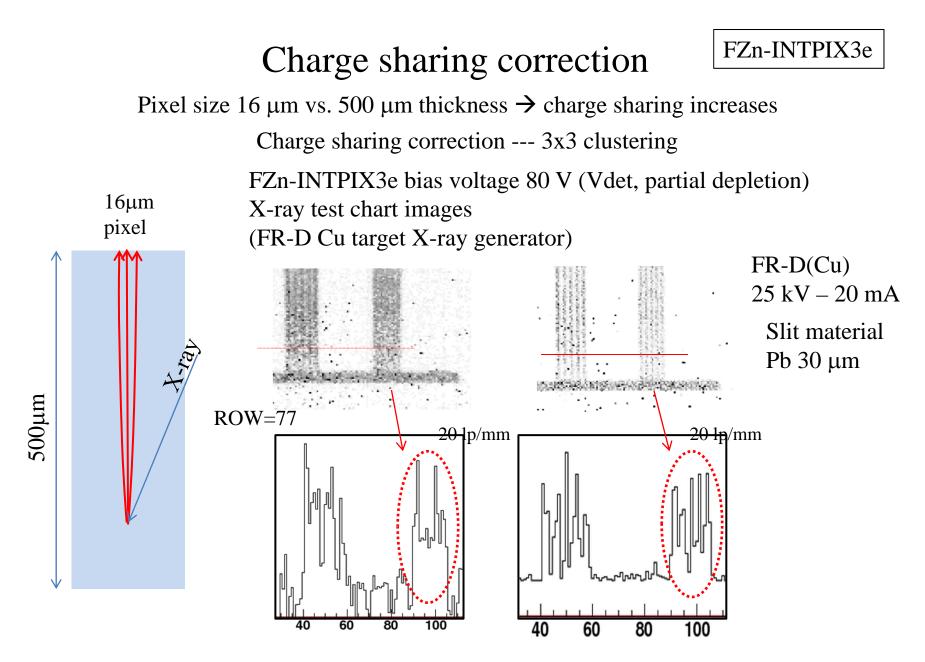

# FZn-INTPIX3e back illumination experiment

#### SOI sensor chip : FZn-INTPIX3e

- Resistivity  $\sim 8k\Omega$  cm

- Bulk thickness 500  $\mu m$

- The back side open (3.1 x 3.1 mm)

Red laser was illuminated from the back side Red laser absorption ~ a few μm 1mmφ Al collimator was used

#### The sensor is fully depleted > 220V

Improvement of the back-side process is required to reach plateau earlier Full depletion at ~30V with 260  $\mu$ m sensor is also confirmed  $\rightarrow$  S. Nakashima's talk ID=348

After the correction, 20 lp/mm slit is clearly seen

## Progress of SOI pixel detector R&D (5)

| p+                      | -2                                         | Sensor test with visible light laser<br>Partial depletion with lower back-bias voltage<br>Front illumination<br>Back gate effect problem                                                                                                                 |  |

|-------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                         | 260μm<br>@~30V<br>or<br>500μm 20<br>@~100V | <ul> <li>Introduction of BPW process</li> <li>Sensor test with IR laser, X-ray and charged particle</li> <li>Partial depletion with higher back-bias voltage</li> <li>Front illumination</li> <li>We don't know what happens at the back side</li> </ul> |  |

| n-<br>(FZ wafer)<br>!!! | S<br>2010 - F<br>B<br>V                    | roduction of FZ wafer<br>nsor test with IR laser, X-ray and charged particle<br>Il depletion with lower back-bias voltages<br>ck illumination<br>e realized that proper back-side processes are<br>quired                                                |  |

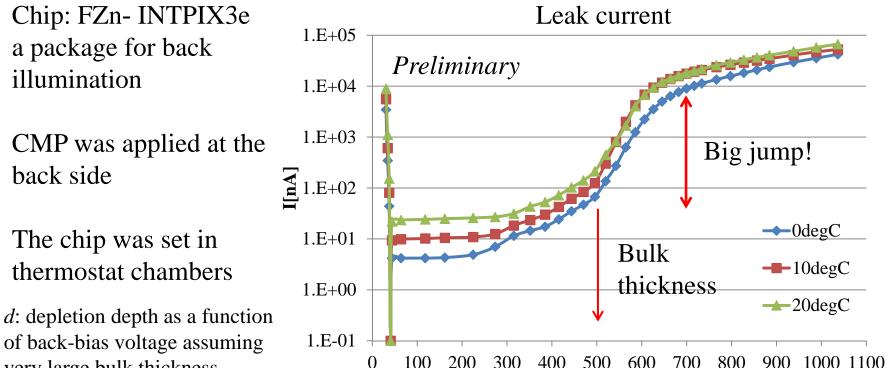

## Current issue : Back-side process

very large bulk thickness  $d(V_b) = \sqrt{\frac{2\varepsilon}{qN_d}(\varphi_B + V_b)}$

$$N_d$$

: n- side dope density

$\varphi_B$ : build-in potential

$V_b$ : back-bias voltage ( $V_{det}$ - $V_{bias=gnd}$ )

$q$ : elementary charge

$\varepsilon$ : permittivity

$\rho_n = l/q N_d \mu_N$ : resistivity

When applied CMP, pixel dark current decreased at more than full depletion voltage (S. Nakashima's talk ID=348)

However, there is a big jump in the I-V curve (above)

OKI Semi. started the optimization of proper back-side process

**Depletion depth d(Vb)** [mm]

# Conclusion

- Thanks to BPW, higher back-bias voltage can be applied and therefore we started evaluation of SOI pixel detectors with spatial resolution, sensor gain and response to X-ray and high energy particles.

- Applying FZ wafer, SOI pixel detectors became operated with full depletion voltage

- A current issue is back-side process and OKI Semi. started the optimization of the back-side process.

- The SOI pixel detector R&D will move to application studies.

The next slide is the final one...

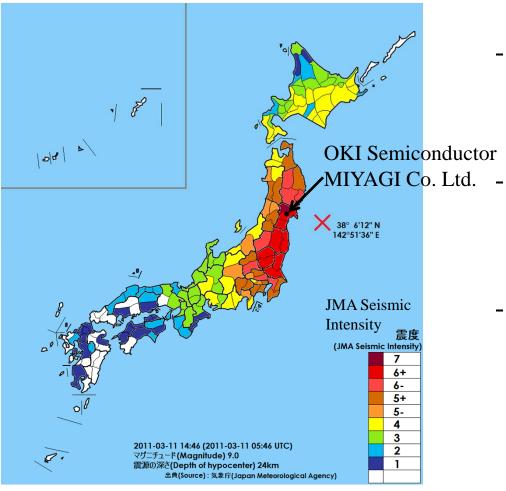

## Schedule

- A large-scale earthquake occurred in Miyagi Prefecture at 2:46 PM on March 11th, 2011.

- No personal suffering and no large scale damage to the OKI Semiconductor Miyagi facilities have been observed

- Operations recommenced mid. of April, and therefore the delay of FY10-2 MPW run will be only 2 months!

FY10-2 MPW process: will complete hopefully in June 2011. FY11 MPW run deadline: Oct. 3<sup>rd</sup>.

For further information, please attend 3D satellite meeting tomorrow, 16:25-16:50