# Results from the NA62 Gigatracker prototype: a low mass and sub-ns time resolution silicon pixel detector

Massimiliano Fiorini (CERN)

on behalf of the NA62 Gigatracker Working Group

Technology and Instrumentation in Particle Physics 2011 Chicago, 9 – 14 June 2011

- The Gigatracker detector system

- □ The NA62 experiment at the CERN SPS: requirements

- Sensors and bump-bonding

- Low-mass cooling system

- Read-out architecture

- Results of prototype bump-bonded assemblies test

- Infra-red laser setup

- Test-beam

- Contributions to detector time resolution

- Future plans

- Conclusions

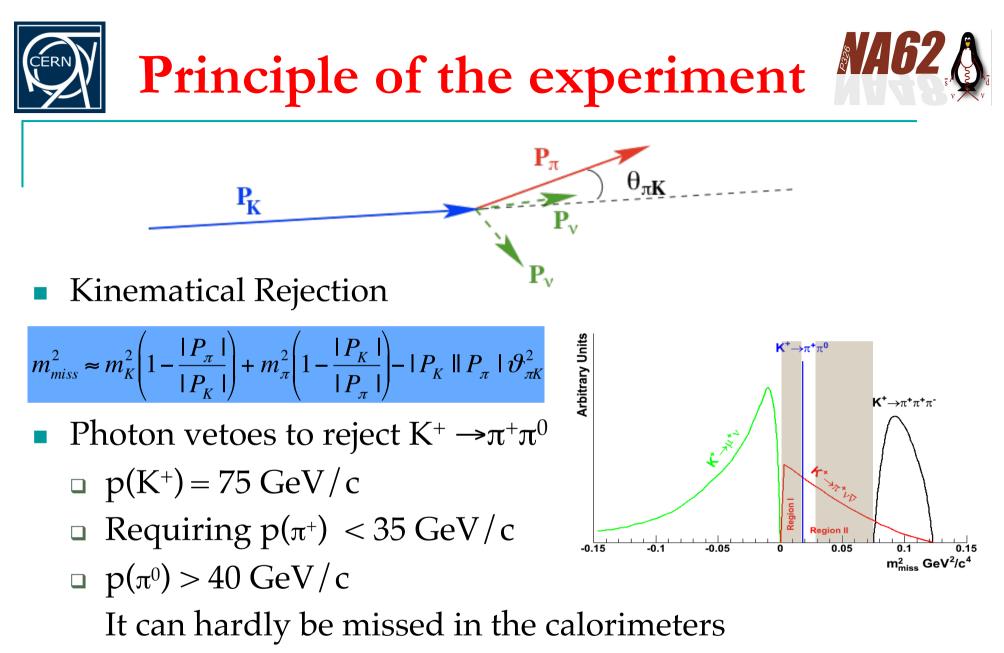

Measurement of  $\mathbf{K}^+ \rightarrow \pi^+ \sqrt{\mathbf{v}}$  at the CERN SPS Un-separated hadron beam LAV: SAV Large Angle Photon Veto  $75 \, \text{GeV/c}$ Small Angle y Veto  $0.8 - 1.0 \, \text{GHz}$ Vacuum Tank π/p/K (~6% K<sup>+</sup>) CHOD Charged **CHANTI** Hodoscope Charged Target Particle Veto CEDAR Gigatracker LKr MUV-----**RICH** Beam Pipe Straw Decay Region: 65 m Tracker

Total Length: 270 m

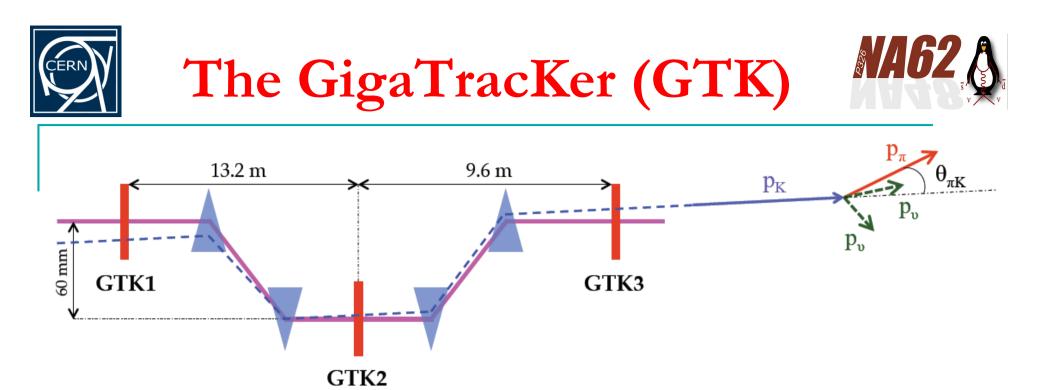

- Beam spectrometer

- provide precise momentum, time and angular measurements on all beam tracks

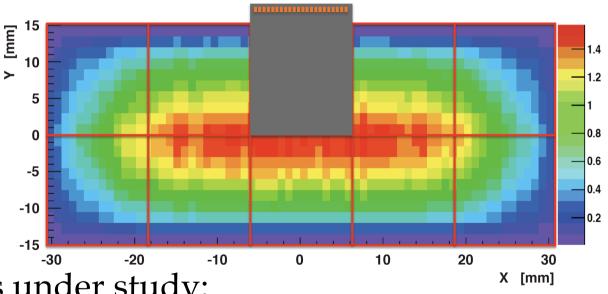

- sustain high and non-uniform rate (~1.5 MHz/mm<sup>2</sup> in the center, 0.8-1.0 GHz total)

- reduce multiple scattering and beam hadronic interactions

X/X<sub>0</sub> <0.5% per station</li>

•

$$\sigma(p_K)/p_K \sim 0.2\%$$

- $\sigma(\theta_K) \sim 16 \mu rad$

- pixel size

300 μm × 300 μm

- σ(t) ~150 ps

on single track

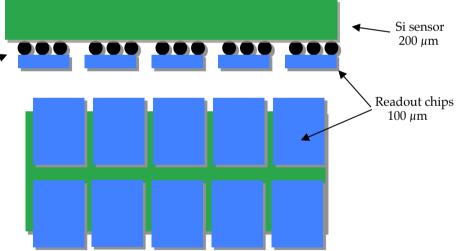

- Hybrid pixel detector

- **300 μm × 300 μm pixels**

- 1 sensor ( $60 \times 27 \text{ mm}^2$ ) bump-bonded to 10 read-out chips

- Material budget:

- □ 200 µm sensor + 100 µm read-out chip  $\rightarrow \sim 0.32\% X_0$

- Bump bonds  $\sim 0.01\% X_0$

- Mechanical support and Bump bonds cooling ~0.15%  $X_0$

- $\Box \quad \underline{\text{Total}} < 0.5\% X_0$

- Minimization of material in active beam area

- beam profile adapted: two rows of read-out chips

- wire connections to R/O chip outside active area

# Sensors and bump-bonding MA62

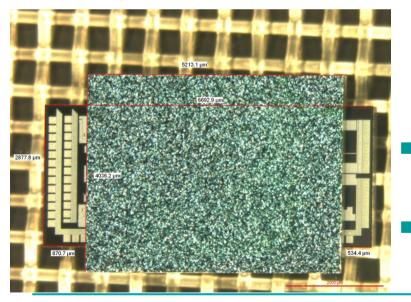

- 200 μm thick p-in-n sensors (produced at FBK, Trento, Italy)

- Over-depleted operation of the detector required to achieve target time resolution (300 V over-bias)

- fast charge collection

- Irradiation of test structures

annealing study following

expected run scenario

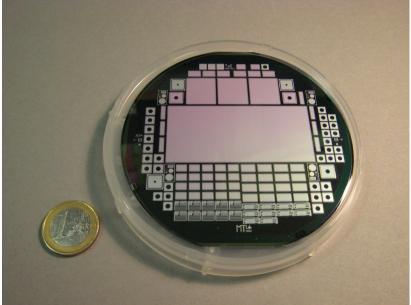

Flip-chip bonding for prototypes done at IZM (Berlin, Germany) in 2010 Target read-out wafer thickness is <100 µm for final production

Technology and Instrumentation in Particle Physics 2011

- GTK stations installed in vacuum

- High and non-uniform radiation levels

- expected fluence is  $\sim 2 \times 10^{14}$  (1 MeV  $n_{eq}/cm^2$ ) during one year of operation (100 days) in the sensor center

- Efficient cooling necessary for stable detector operation

Very low material budget (~0.15% X<sub>0</sub>) in the active beam area

- Two cooling options under study:

- convective cooling in a vessel (gas cooling)

- micro-channel cooling (liquid cooling)

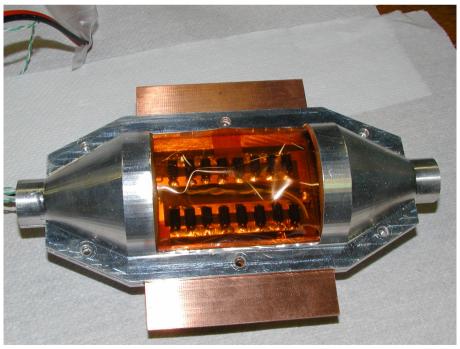

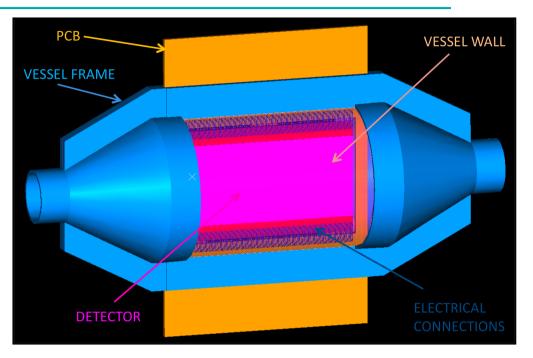

### Gas cooling

- cooling via flow of cold gaseous nitrogen (100 K)

- thin cylindrical kapton windows (100 µm total)

- aluminum vessel frame

full size prototype built

optimizations ongoing to improve uniformity of temperature distribution across sensor area

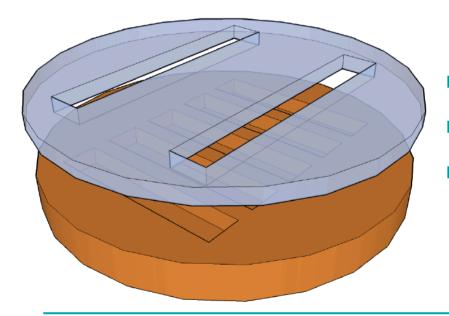

## **Micro-channel cooling**

- micro-channel cooling plate: 2 bonded Si wafers (150 µm total thickness in the active detector area)

- channels plus opening for inlet and outlet manifolds

| Silicon (380 µm)     |                            |                                           |                                                |          |

|----------------------|----------------------------|-------------------------------------------|------------------------------------------------|----------|

|                      |                            |                                           |                                                |          |

| Silicon (380 µm)     |                            |                                           |                                                |          |

| 100µm<br>Mag = 215 X | EHT = 3.00 kV<br>WD = 6 mm | Signal A = InLens<br>Stage at T =   6.9 ° | Date :27 Jan 2011<br>File Name = #8090-008.tif | EPFL-CMI |

- $100 \ \mu m \times 100 \ \mu m$  micro-channels

- rad-hard liquid coolant ( $C_6F_{14}$ )

- full-scale prototype and vacuum test stand built

- optimize manifold to reduce pressure plus wafer thinning

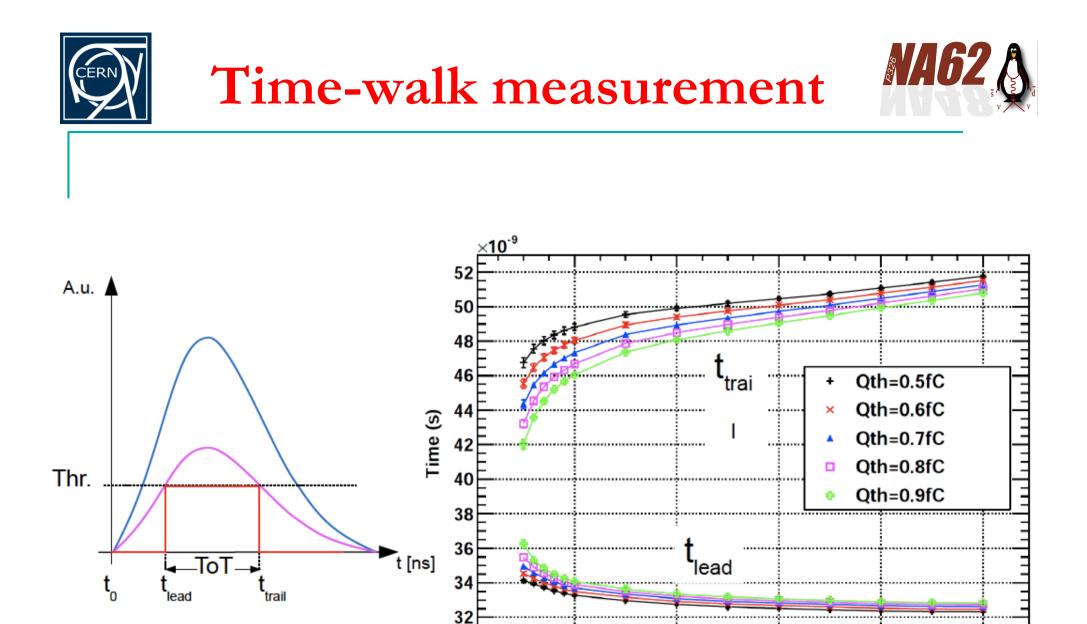

Time-walk compensation necessary to achieve the required timing resolution (16:1 dynamic range)

| <b>"On-pixel" TDC option</b><br>CFD filter | <b>"End of column" TDC option</b><br>ToT discriminator |

|--------------------------------------------|--------------------------------------------------------|

| +                                          | +                                                      |

| on-pixel TDC                               | DLL based TDC shared                                   |

| based on TAC                               | among a group of pixels                                |

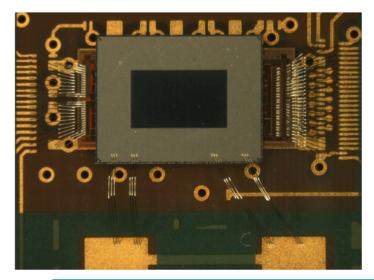

- Small area prototype chips produced in 0.13 μm IBM CMOS technology in 2009, bump-bonded and tested in 2010

- The NA62 Collaboration, after a careful design review, decided to adopt the "End of column" architecture as the baseline option

- decision based on performance of prototype assemblies and the tight time schedule of the experiment

| Pixel matrix           | 40 columns × 45                           |  |  |

|------------------------|-------------------------------------------|--|--|

| Pixels per chip        | 1800                                      |  |  |

| Chip size              | 12 mm × 19 mm                             |  |  |

| Dissipated power       | $\sim 2 \mathrm{W}/\mathrm{cm}^2$         |  |  |

| Dynamic range          | 3600 – 60000 e <sup>-</sup> (0.6 – 10 fC) |  |  |

| Time resolution        | < 200 ps                                  |  |  |

| Peaking time           | 5 ns                                      |  |  |

| Maximum rate per pixel | 140 kHz                                   |  |  |

| Maximum data bandwidth | ~8 Gb/s                                   |  |  |

"End of column" chip architecture presented on June 9<sup>th</sup> by G. Aglieri Rinella ("Front-end electronics" session)

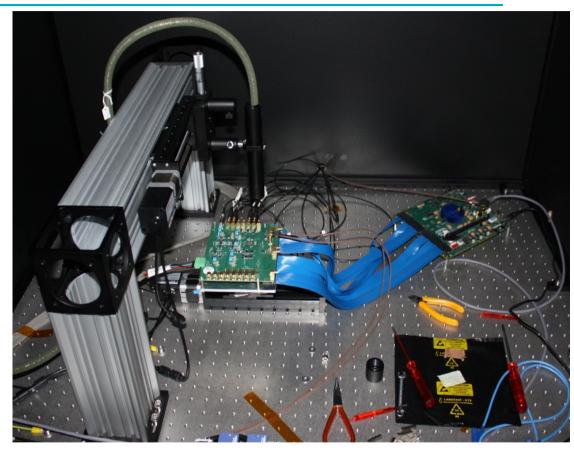

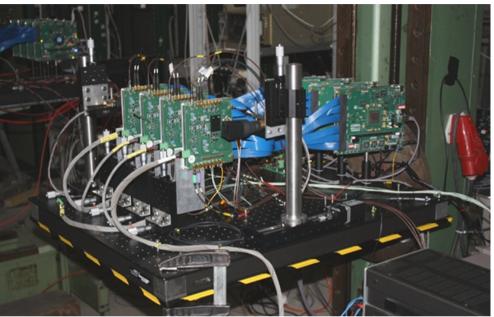

### Laser test setup

- IR light (1060 nm) to mimic minimum ionizing particles

- Characterize GTK

bump-bonded

assemblies on

laboratory bench

- 5 ps time precision

- Absolute calibration of injected charge

radioactive sources (<sup>241</sup>Am, <sup>109</sup>Cd)

Technology and Instrumentation in Particle Physics 2011

Massimiliano Fiorini (CERN)

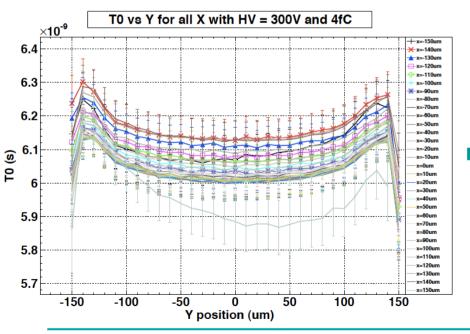

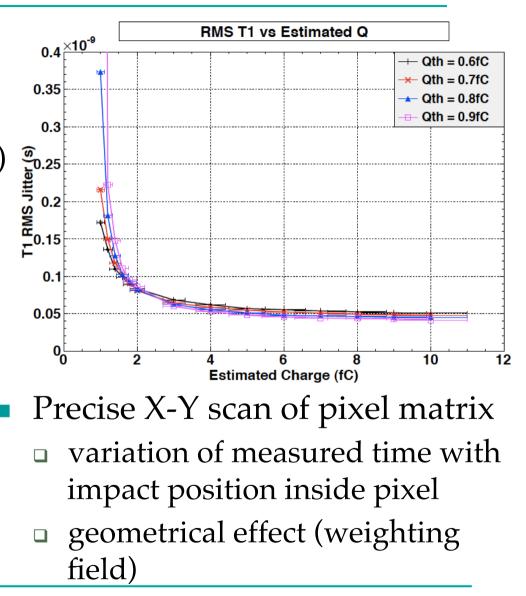

- Time resolution (jitter) of ~75 ps at 3 fC (average charge created by minimum ionizing particle)

- charge injected at the pixel center

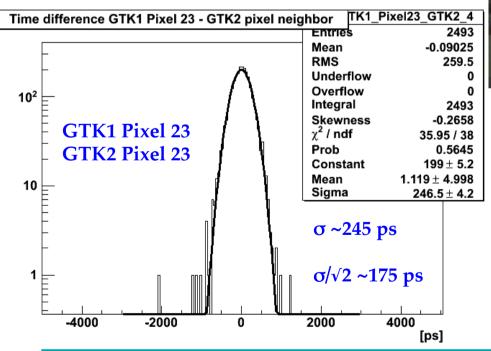

## **Test-beam at CERN PS**

- test-beam at CERN T9 (10 GeV/c  $\pi^+$  and p)

- 4 consecutive GTK planes

- fast scintillators used for timing reference

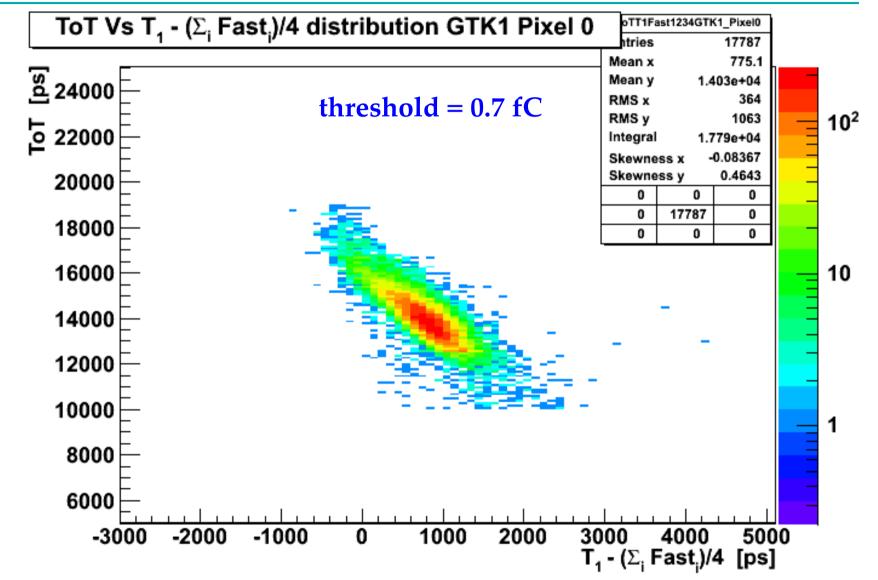

- applied Time-over-Threshold correction (pixel-by-pixel) using scintillator information

procedure validated for NA62

- measured time resolution of

~175 ps at 300 V sensor bias

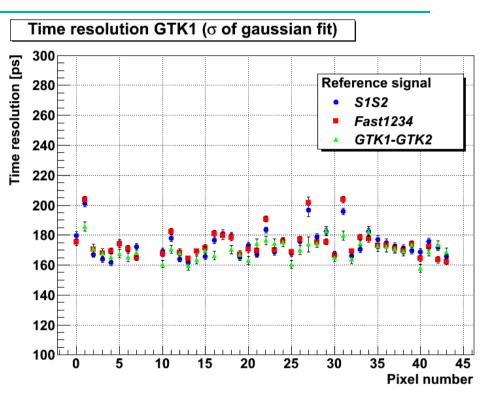

- Time resolution measured for every pixel (45 per GTK prototype assembly)

variations mainly due to

- pixel-by-pixel threshold variation (no trimming)

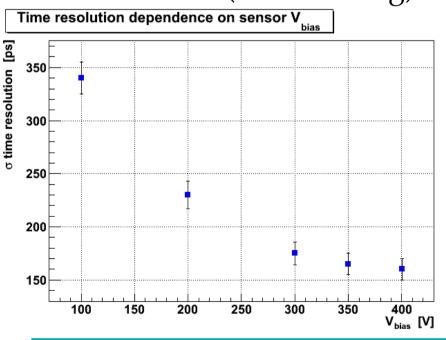

- Clear dependence on sensor bias voltage

- approaching plateau at ~400 V

- high-over depletion mandatory

- Electronic noise from front-end chip

- □ measured ~180 e<sup>-</sup> (ENC) with sensor

- Sensor bias voltage

- variation of charge collection time (signal slope)

- Impact position on pixel sensor

- weighting field variation (geometrical effect)

- Energy straggling in the sensor bulk

non-uniform energy release along track and delta rays

- Ongoing studies to determine and quantify relative contributions to the total time resolution

- alternative sensor technologies under consideration for possible upgrades (e.g. 3D sensors)

| Action                                     | Period         |

|--------------------------------------------|----------------|

| Design of final (full-size) chip           | ongoing        |

| Submission of final chip to IBM            | end 2011       |

| Thinning and bump-bonding of dummies       | ongoing        |

| Production of final bump-bonded assemblies | beginning 2012 |

| Investigation of radiation effects         | ongoing        |

| Selection of baseline cooling solution     | Autumn 2011    |

| Back-end readout system production         | Spring 2012    |

| Complete electro-mechanical integration    | Summer 2012    |

| First NA62 physics run                     | end 2012       |

- Extensive measurements performed on prototype Gigatracker bump-bonded assemblies

- electrical, laser and test-beam

- A time resolution of ~175 ps has been measured with minimum ionizing particles at 300 V

- clear dependence of time resolution on sensor bias

- contributions to total time resolution are being quantified

- Two very-low mass cooling systems (<0.15% X<sub>0</sub>) are being developed in parallel

- prototype tests are encouraging

- baseline cooling option for NA62 will be selected soon

# **SPARES**

To achieve the required timing accuracy, time-walk compensation has to be applied due to the 10:1 dynamic range

#### Two alternatives under consideration:

- Use of a low power Constant Fraction Discriminator (CFD)

- analog signal processing technique of time information without time-walk

- single time measurement, complicated analog design

- Correction via the Time over Threshold (ToT) method

- time-walk correction algorithm based on the signal time over threshold (pulse width), obtained by measuring leading and trailing edges of the pulse

- accurate calibration of the system is required to define the correction algorithm

Technology and Instrumentation in Particle Physics 2011 2

4

10

8

6

Qin (fC)

Technology and Instrumentation in Particle Physics 2011

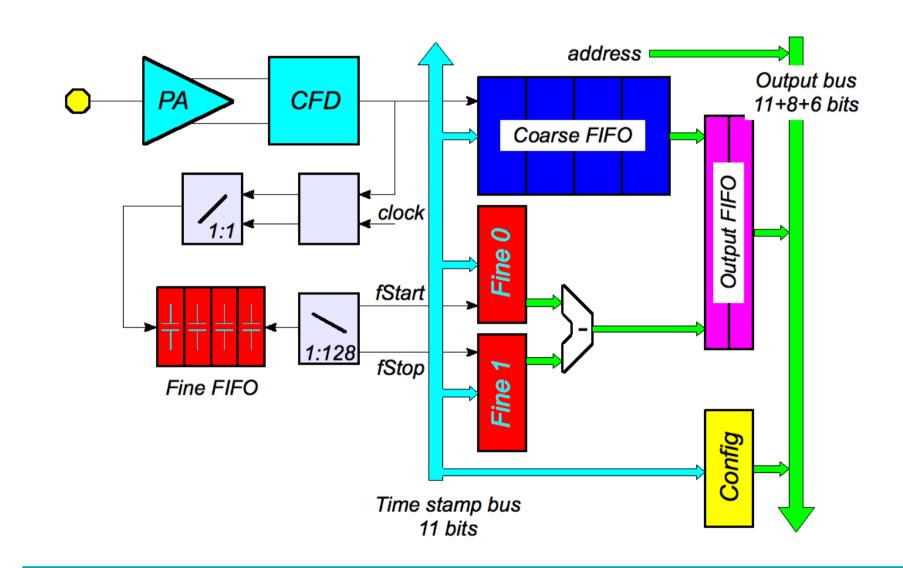

# **TDC** options

- Coarse time measurement by counting clock pulses

- Fine measurement obtained with a Time to Digital Converter (TDC)

#### Two possible solutions:

- On-pixel TDC system

- maximize signal processing on the pixel cell (including TDC) and distribute clock to the pixel matrix (digital noise)

- minimize complexity of end of column logic (no need to propagate the comparator signal outside the pixel)

- must be designed to be radiation-tolerant (total dose and SEU aspects), due to the high radiation dose received in the pixel area

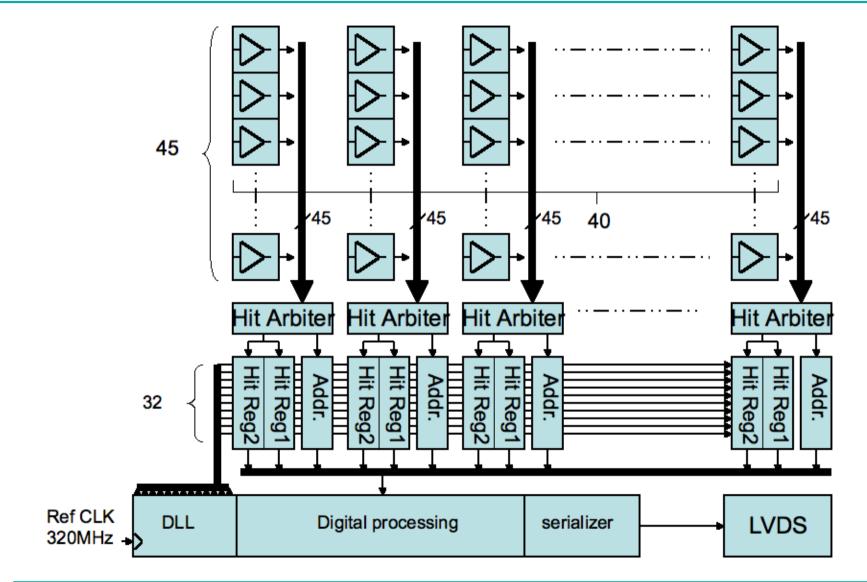

- End of Column (EoC) architecture

- use high precision digital TDC in the end of column, shared by a group of pixels

- minimize on-pixel processing for minimum noise

- pixel comparator signals should be propagated to the chip periphery (communication of ultra-fast signal in column transmission lines)

Technology and Instrumentation in Particle Physics 2011

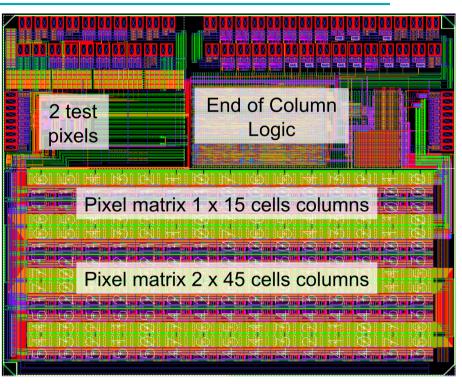

## **EoC Prototype**

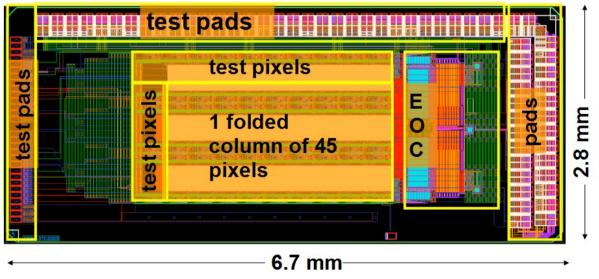

- 2.8 mm × 6.7 mm total size

- 320 MHz reference clock

- 60 pixels divided into 3 groups

- Main array: 45 pixels with 9 EoC readout blocks, each one serving the 5 pixels through the arbiter block

- Small array: 9 pixels

- Test column: 6 pixels with analog output

- Hit Arbiter: defines first arriving pixels out of 5 (asynchronous latch)

- 5 mm × 4 mm total size

- 105 + 2 pixel cells

- 160 MHz clock

- 2 folded columns (45 pixels each) and one smaller column with 15 pixels, plus two test pixels

- For each column a totally independent End-of-Column Controller is implemented

- SEU protection both in the pixel cells and the End of Column controller

- Fine time measured by starting calibrated voltage ramp at CFD rising edge and stopping at next clock rising edge

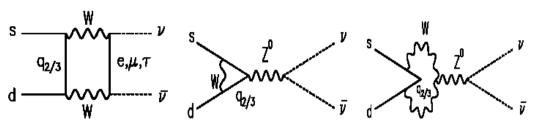

The  $K^+ \rightarrow \pi^+ \nu \overline{\nu}$  decay

FCNC loop processes

- Theoretically very clean: hadronic matrix element can be related to measured quantities

- SM predictions (uncertainties from CKM elements):

- □  $BR(K^+ \rightarrow \pi^+ \nu \overline{\nu}) \approx (1.6 \times 10^{-5}) |V_{cb}|^4 [\sigma \eta^2 + (\rho_c \rho)^2] \rightarrow (8.5 \pm 0.7) \times 10^{-11}$

- □  $BR(K_L \rightarrow \pi^0 \nu \overline{\nu}) \approx (7.6 \times 10^{-5}) |V_{cb}|^4 \eta^2 \rightarrow (2.6 \pm 0.4) \times 10^{-11}$

- The K→πνν decays represent a theoretically clean environment sensitive to new physics

- The NA62 Collaboration (former NA48) aims to measure O(100) K<sup>+</sup>→π<sup>+</sup>νν events with ~10% background at the CERN SPS in two years data taking period

• PID for  $K^+ \rightarrow \mu^+ \nu$  rejection