# **Basic Electronics**

Introductory Lecture Course for

# Technology and Instrumentation in Particle Physics 2011

Chicago, Illinois June 9-14, 2011

**Presented By**

### **Gary Drake**

**Argonne National Laboratory**

**Session 3**

### **Session 3**

### **Semiconductor Devices**

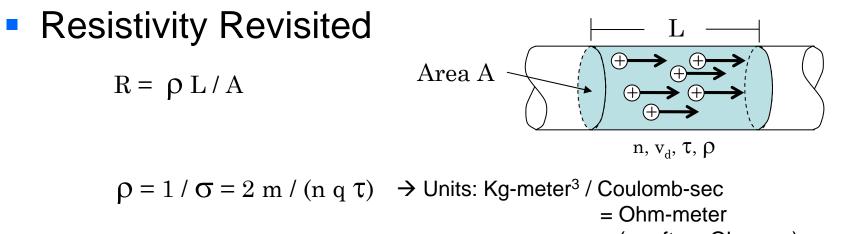

⇒ Only depends on physical properties

### (or often, Ohm-cm)

### **Resitivity of Materials**

| <u>Metals</u>                                                   | <u>Semiconductors</u>                                                                                  | <u>Insulators</u>                                |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 10 <sup>-6</sup> to 10 <sup>-4</sup> Ω-cm                       | 10 <sup>-3</sup> to 10 <sup>+8</sup> Ω-cm                                                              | > 10 <sup>+8</sup> Ω-cm                          |

| <ul> <li>Upper electron</li> <li>shells nearly empty</li> </ul> | <ul> <li>Partially filled shells</li> <li>Bonds covalently to form weakly stable structures</li> </ul> | <ul> <li>Completely<br/>filled shells</li> </ul> |

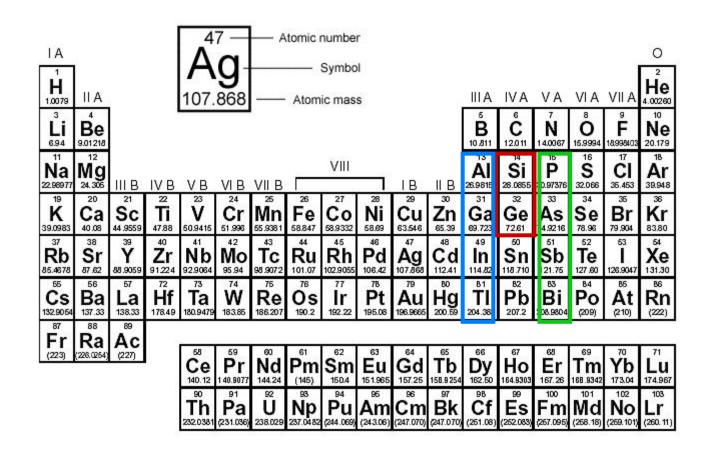

### Semiconductors on the Periodic Chart

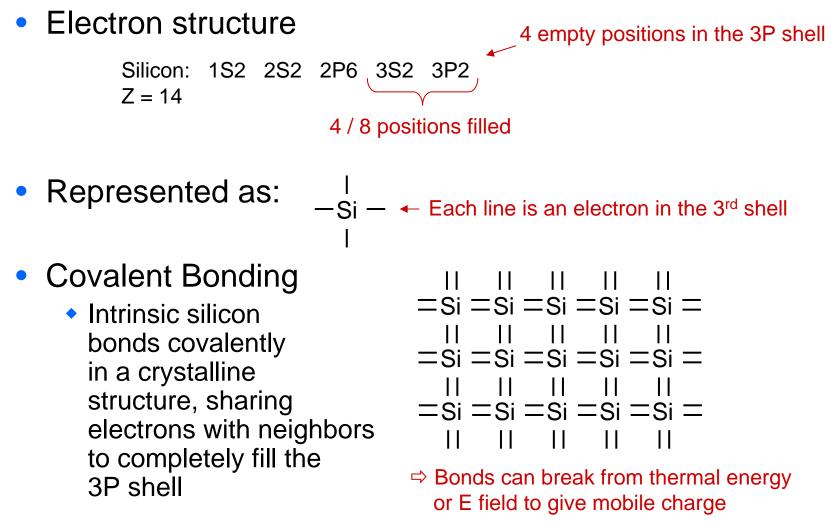

### Atomic Structure of Silicon – Group IVA

Adding Impurities into Silicon

Consider Phosphorous – Group VA

3 empty positions

Phosphorous: 1S2 2S2 2P6 3S2 3P3 Z = 15

5 / 8 positions filled

- Represented as:

P Each line is an electron in the 3<sup>rd</sup> shell

- Introduction into Silicon Crystalline Structure

- Extra electron is weakly

bound, and easily removed

→ Donor Impurity

II

II

Si = Si =

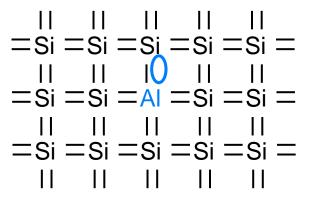

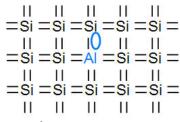

- Adding Impurities into Silicon (Continued)

- Consider Aluminum = Group IIIA

Aluminum: 1S2 2S2 2P6 3S2 3P1  $\leftarrow$  5 empty positions Z = 13

3 / 8 positions filled

- Represented as:

AI ← Each line is an electron in the 3<sup>rd</sup> shell

- Introduction into Silicon Crystalline Structure

- Missing electron is weakly accepted into lattice

Acceptor Impurity

- Concept of mobile "holes"

- When electron is captured, hole moves from location to location

- Adding Impurities into Silicon (Continued)

- Introduction of impurities into intrinsic silicon is called "Doping"

- Amount of doping characterized by concentration of charge carriers

- +  $n^{}_{\rm i}$  = # intrinsic carriers in pure silicon / unit volume  $~\approx$  1.4E10 / cm^3

- N<sub>d</sub> = # donor atoms / unit volume

- N<sub>a</sub> = # acceptor atoms / unit volume

- N-type Silicon

•

$$N_d - N_a >> n_i$$

- High concentration of donor atoms

- Provides excess electrons to lattice as mobile charge carriers

#### P-type Silicon

- $N_a N_d >> n_i$

- High concentration of acceptor atoms

- Provides excess holes to lattice as mobile charge carriers

Basic Electronics – Special Lecture for TIPP 2011 Gary Drake, Argonne National Lab – Session 3

@ 300° K

- Adding Impurities into Silicon (Continued)

- How to make use of mobile charge carriers

- Bonds can be broken by:

- Application of an Electric Field

- » Basic principle of how integrated circuits work

- Application of Light  $\rightarrow$  Photons impart energy

- » Basic principle of how photo cells work

- » Use reverse principle for light emitting diodes (LEDs)

- Heat  $\rightarrow$  Kinetic Energy

- » Basic use for temperature sensors

- » Generally a bad property for semiconductors...

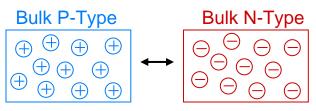

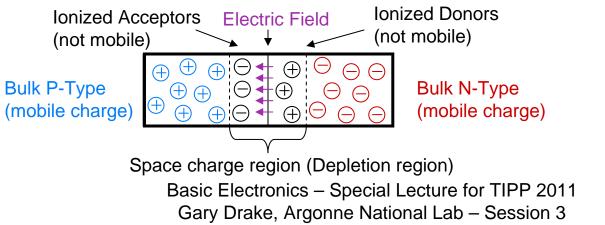

# **PN Junctions**

- Forming a PN Junction

- Take P-type & N-type silicon, and butt them together

- When butt together, opposite charges attract

- Mobile electrons from N-type silicon attracted to vacancies in P-type

- Mobile holes from P-type silicon attracted to vacancies in N-type

- ⇒ Results in Acceptor & Donor atoms being ionized

- Creates space charge regions

- ⇒ Results in the creation of a built-in Electric Field

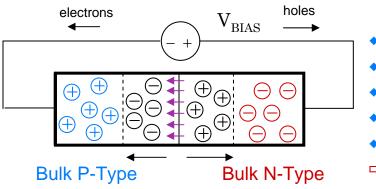

# **PN Junctions**

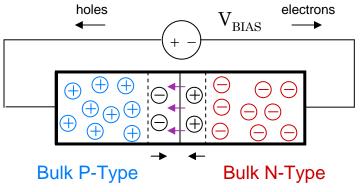

- Biasing a PN Junction

- Suppose apply a voltage to the PN Junction

- Positive terminal of V<sub>BIAS</sub> attracts electrons

- Negative terminal of V<sub>BIAS</sub> attracts holes

- Makes space charge region <u>bigger</u>

- Increases E field across junction

- <u>Reduces</u> ability of current to flow across junction

- ⇒ Reverse Bias

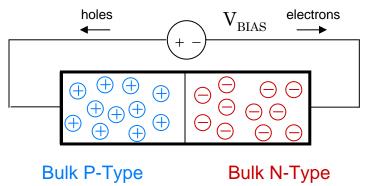

- Now suppose we reverse the polarity of V<sub>BIAS</sub>

- Positive terminal of V<sub>BIAS</sub> adds holes to P region

- Negative terminal of V<sub>BIAS</sub> adds electrons to N

- Makes space charge region <u>smaller</u>

- <u>Decreases</u> E field across junction

- <u>Enhances</u> ability of current to flow across junction

- ⇒ Majority Carrier:

Holes recombine with ionized acceptors Electrons recombine with ionized donors

# **PN Junctions**

- Biasing a PN Junction (Continued)

- At a critical bias, space charge region disappears

- Built-in E field across junction is gone

- Now charge carriers provided by V<sub>BIAS</sub> can move across PN junction

- ⇒ Forward Bias → Conduction

- ⇒ Each new electron/hole pair pushes existing pair out of bulk

- How much voltage is required to reach forward bias?

- Answer: Related to how much energy is required to remove bound electrons (or holes) from their nuclei

- $\rightarrow$  Work Function

- Depends on doping concentrations

- Depends on intrinsic carrier concentration

- Depends on temperature

$\phi = kT/q \ln [N_d N_a / n_i^2]$

```

Basic Electronics – Special Lecture for TIPP 2011

Gary Drake, Argonne National Lab – Session 3

```

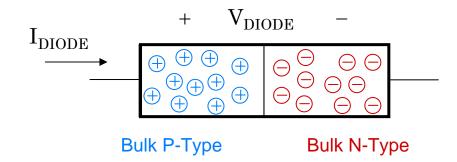

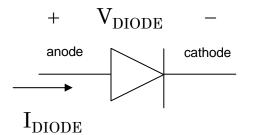

- Physical Description

- Essentially a simple PN Junction

Symbol

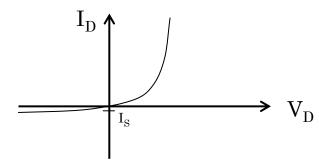

- IV Characteristics

- Shockley Diode Equation

$$I_D = I_S [e^{-[k V_D/(n q T)} - 1]$$

⇒ Nonlinear IV relationship

Where:  $I_S = Reverse Saturation Current$  k = Boltzman Constant (1.38E-23 J/K) T = Temperature (° Kelvin)  $q = charge (1.6E-19 C/e^-)$   $n = quality factor, 1 \ge n \ge 2$   $V_T = k T / q = 25.8 mV @ room temp$  = Thermal Voltage $\Rightarrow In most diodes, I_S is very small$

Basic Electronics – Special Lecture for TIPP 2011 Gary Drake, Argonne National Lab – Session 3

13

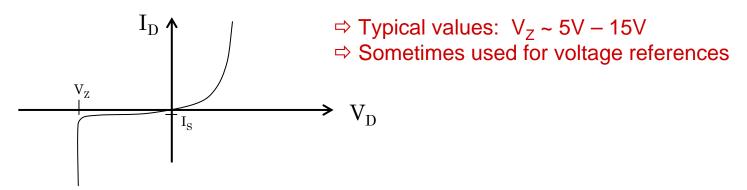

- IV Characteristics (Cont.)

- Many diodes exhibit reverse breakdown → Zener Effect

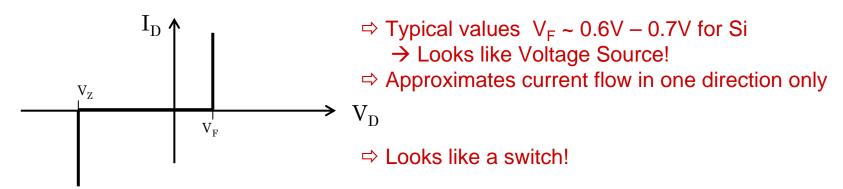

- Ideal Characteristics

- Sometimes, it is useful to use a linear approximation

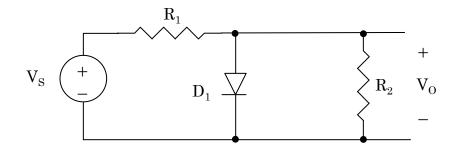

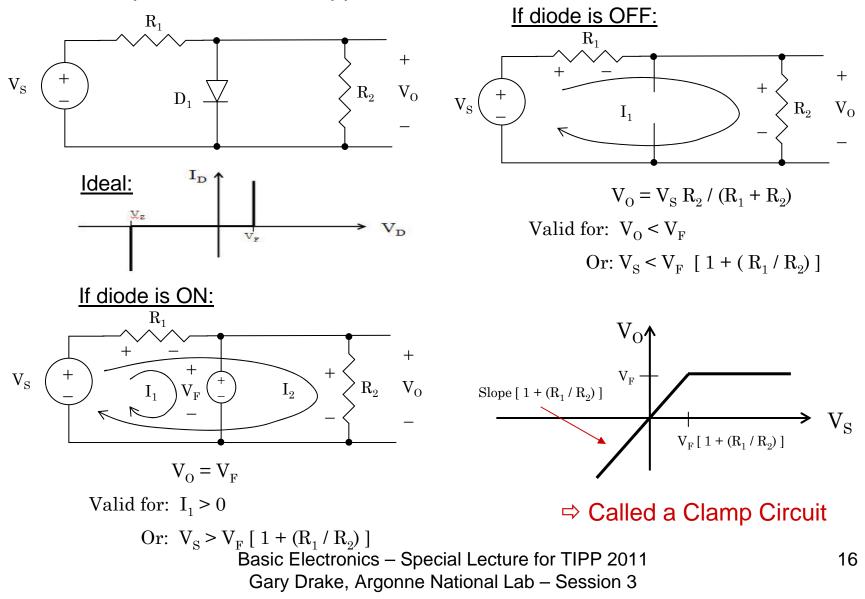

- Circuits

- Rarely use Shockley equation in hand calculations

- SPICE uses Shockley equation or behavioral models

- Gives accurate solution

- For hand calculations 2 methods:

- Use linear approximation

- Use graphical techniques

- Circuits (Continued)

- Example Use Linear Approximation:

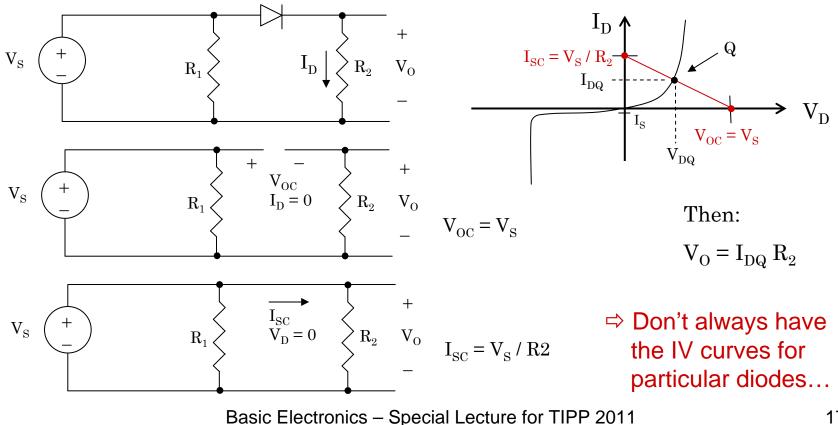

- Circuits (Continued)

- Example Use Graphical Methods  $\rightarrow$  Load Line Analysis:

- Take Diode out Calculate open-circuit voltage  $\rightarrow$  I<sub>D</sub> = 0

- Then replace diode with short Calculate short circuit current  $\rightarrow$  V<sub>D</sub> = 0

- Plot on diode IV graph → Find Operating Point Q

Gary Drake, Argonne National Lab – Session 3

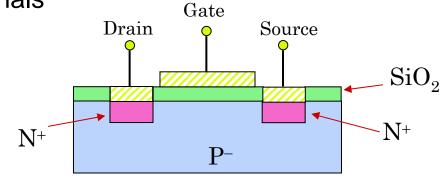

## **Field Effect Transistors**

### Introduction

- Field Effect Transistors (FETs) are 3-terminal devices, where the current flow between two of the terminals (Drain & Source) is controlled through the use of an electric field applied at the third terminal (Gate), which modulates a conduction channel between the two active terminals.

- Current flow is achieved by drift currents through the channel

- Charge carriers are majority carriers (p-type → holes, n-type → electrons)

- Current flow is uni-directional

- Several different kinds:

- Junction FET (JFET)

- Metal Oxide Semiconductor FET (MESFET)

- High Electron Mobility Transistor (HEMT)

- Depleted FET (DEPFET)

- (Many other variations...)

- Gate Gate Source

- We will focus on this today

⇒ Used extensively in HEP

- ⇒ Custom ASIC design!

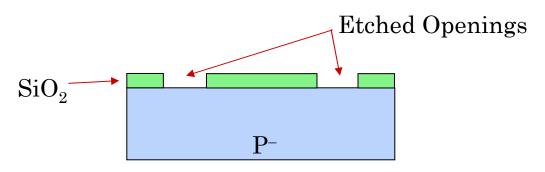

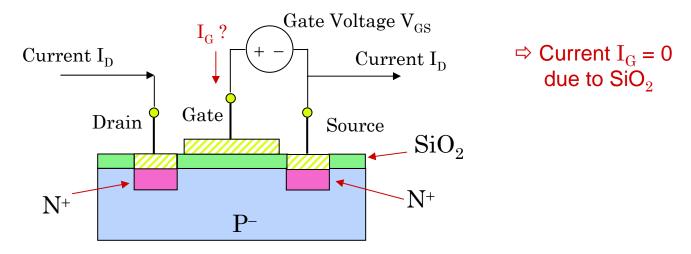

- Basic Construction

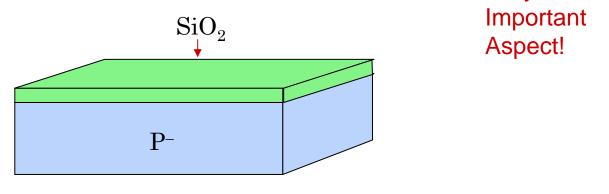

- Begin with lightly-doped P-type substrate (could be N-type as well...)

- Cover surface with layer of silicon dioxide (SiO2)

- Like glass

- Insulator  $\rightarrow$  Very high resistivity  $\rightarrow \rho \sim 1E18 \Omega$ -cm  $\Rightarrow$  Very

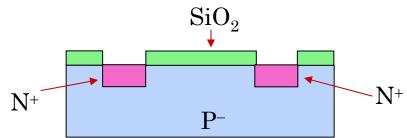

- Basic Construction (Continued)

- Etch openings into the SiO<sub>2</sub> using hydrofluoric acid (HF)

- Dissolves SiO<sub>2</sub> but not the silicon underneath

- Diffuse donor impurities into substrate to make N-type implants

- Heavy doping  $\rightarrow$  N<sup>+</sup>

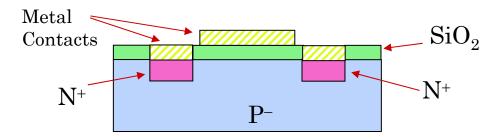

- Basic Construction (Continued)

- Add metal contacts

- Applied using Sputtering or Evaporating Metal

- Basic construction done

- All process steps done with masks → lithography

- Define terminals

### Basic Operation

Idea is to use the Drain and Source terminals for conduction, and to control the flow of current through these terminals by applying a voltage to the Gate

- There are three states of operation:

- Accumulation

- Depletion

- Inversion

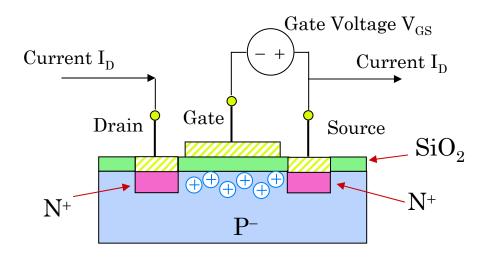

- Basic Operation (Continued)

- Accumulation

- Occurs when Gate voltage creates an electric field in the region between the N wells that <u>attracts majority carriers</u> → holes

- To attract holes in a P-type substrate, use a negative gate voltage

- The electric field lines from the Gate terminate on the accumulated holes, so that there is no attraction of electrons from the Drain and Source regions

- ⇒ Results in no current flow between Drain and Source

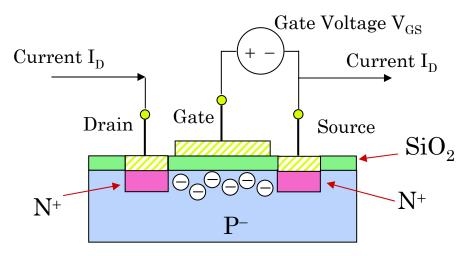

- Basic Operation (Continued)

- **Depletion**

- Occurs when Gate voltage creates an electric field in the region between the N implants that <u>repels majority carriers</u> → holes

- To repel holes in a P-type substrate, use a positive gate voltage

- Note that charge under Gate region is fixed charge, created by removing holes from their acceptor atoms in the P substrate

- The electric field lines from the Gate terminate on the depleted acceptor atoms

⇒ Results in no current flow between Drain and Source

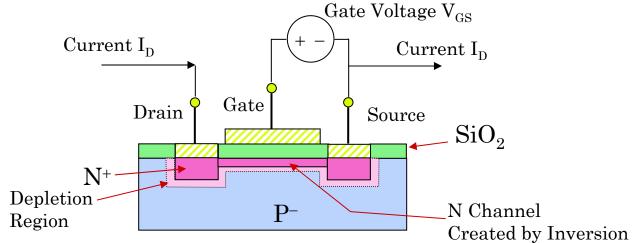

Basic Operation (Continued)

#### • Inversion

- Occurs when Gate voltage reaches a critical point, where electrons begin to be attracted from N<sup>+</sup> Drain and Source regions

- Forms an N-type channel between the Drain and Source

- Density of electrons in the channel ~ density of donor atoms in the  $N^{\rm +}$  implants

- Now can have flow of electrons from Drain to Source

- Current flow is controlled by the Gate Voltage

- The point at which the Gate voltage creates a conductive channel under the Gate is called the Threshold Voltage  $V_{\rm Th}$

$$V_{GS} \geqq V_{TH} \\ \text{Basic Electronics} - \text{Special Lecture for TIPP 2011} \\ \text{Gary Drake, Argonne National Lab} - \text{Session 3} \\ \end{array}$$

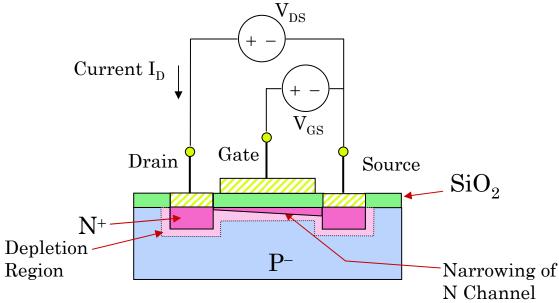

- **Basic Operation (Continued)**

- *Inversion* (Continued)

- Suppose now connect a voltage source between Drain and Source

- Allows current to flow between Drain and Source

- Results in voltage drop across channel

→ Channel begins to narrow at Drain end

- Holes pumped into the Drain recombine with ionized acceptors in the channel near the Drain

- Electric field from the Gate is not strong enough to sustain the full width of the channel at the Drain, resulting in a narrowing of the channel

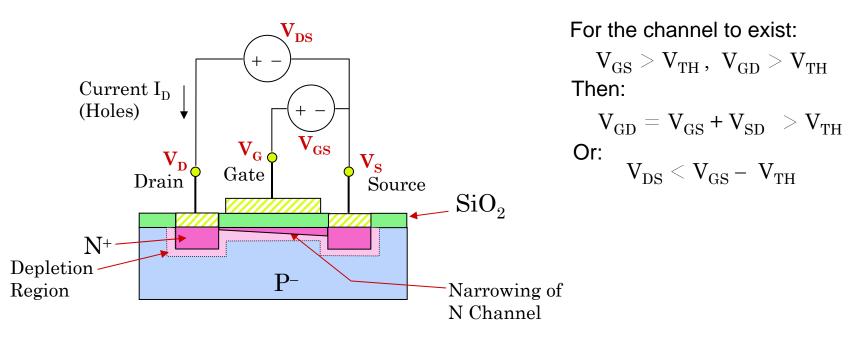

- Basic Operation (Continued)

- Inversion (Continued)

- If there is a voltage drop across the channel, then the voltage at the drain must be greater than at the source:

- It can be shown that, for this mode of operation, the voltage drop in the channel is resistive, and that the current  $I_D$  is given by:

$$\label{eq:ID} \begin{split} I_D \approx ~K~V_{DS}~[~V_{GS}-~V_{TH}~]\,,\, valid~for~V_{DS} < V_{GS}-~V_{TH} \\ \\ \hline & \text{Basic Electronics}-\text{Special Lecture for TIPP 2011} \end{split}$$

Gary Drake, Argonne National Lab – Session 3

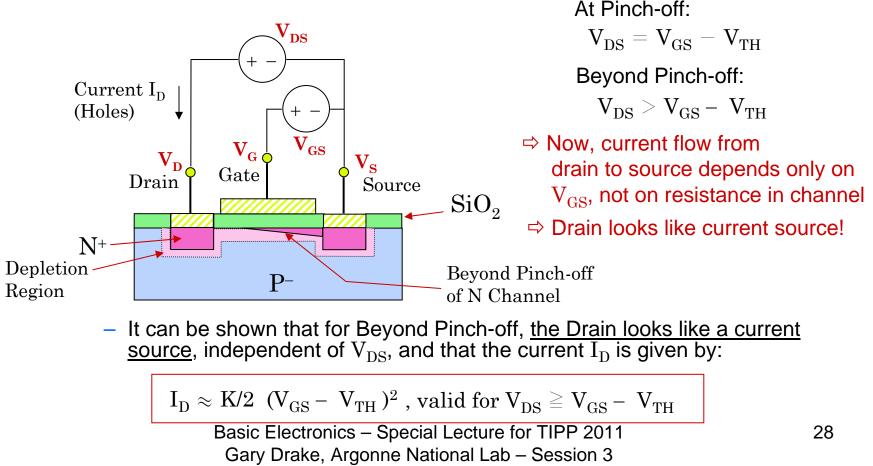

- Basic Operation (Continued)

- Inversion (Continued)

- As continue to increase V<sub>DS</sub>, channel reaches a point where the width goes to 0 at the Drain → *Pinch-Off*

- As continue to increase VDS, channel begins to recede at the Drain

→ Beyond Pinch-Off

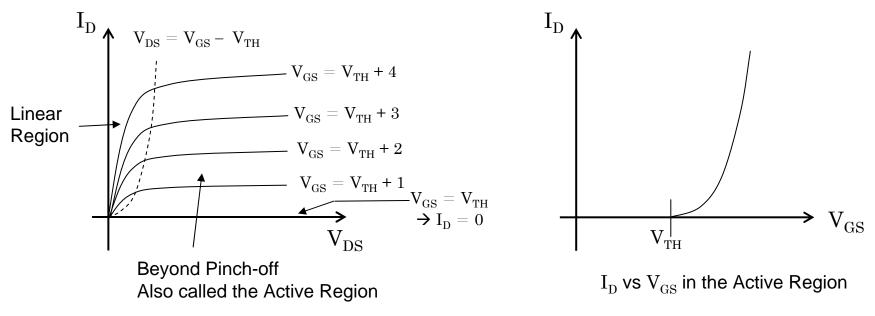

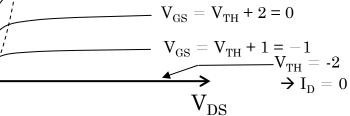

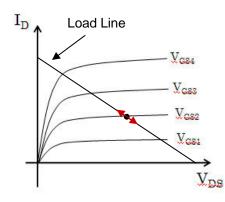

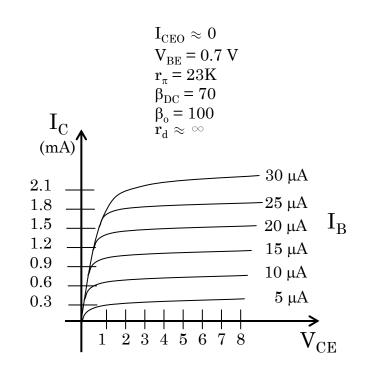

#### IV Characteristics

- Have defined 2 regions of operation

- Linear region  $\rightarrow$  IV characteristics look <u>resistive</u>  $\rightarrow$  Voltage-controlled resistor

- Beyond Pinch-off → IV characteristics look like a <u>current source</u>

- Typically plot  $I_D$  versus  $V_{DS}$  as a function of  $V_{GS} \; \Rightarrow$  Family of curves

- Linear Region:  $I_{D}$  =  $K \: V_{DS} \:$  [  $V_{GS}$   $\: V_{TH}$  ], valid for  $V_{DS} < V_{GS}$   $\: V_{TH}$

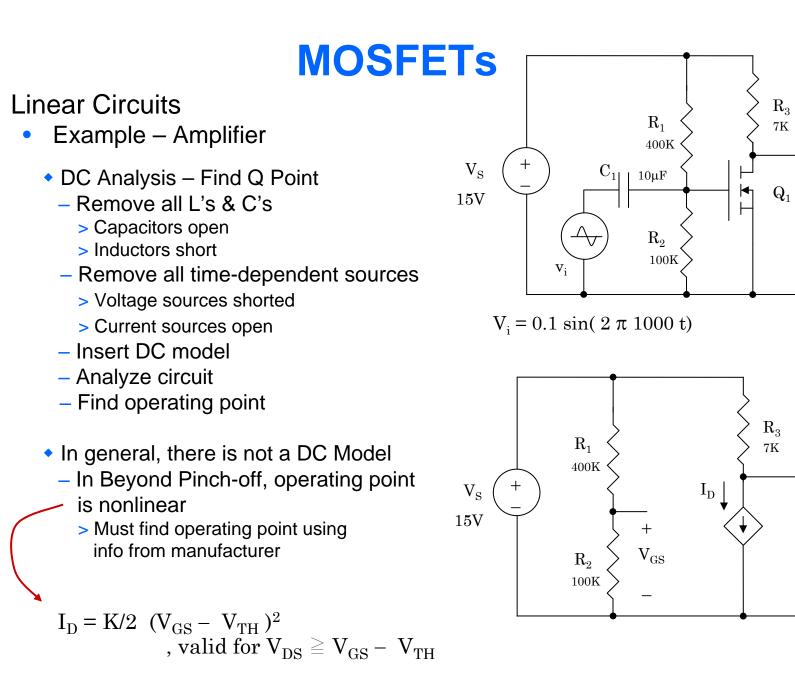

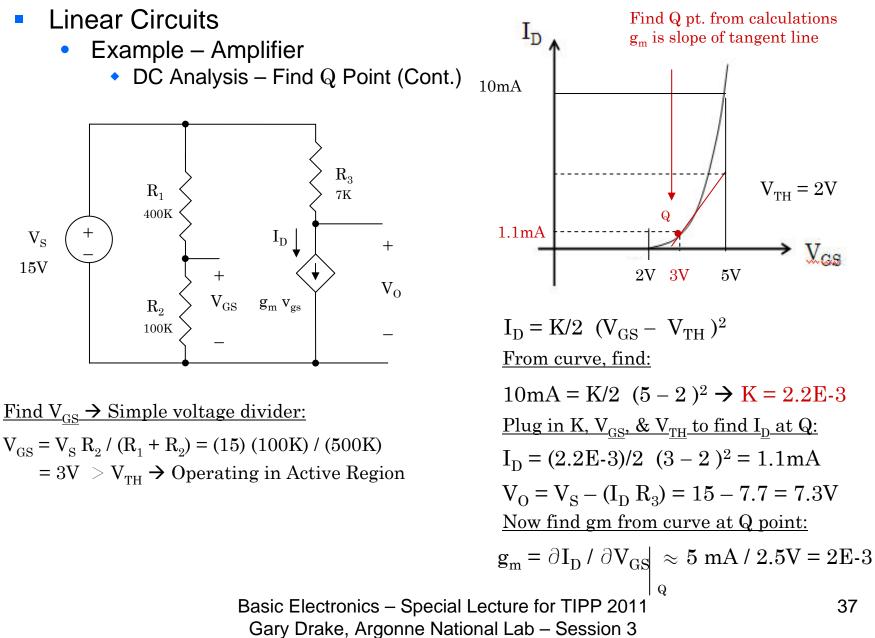

- Active Region:  $I_D$  = K/2  $(V_{GS} V_{TH})^2$  , valid for  $V_{DS} \ge V_{GS} V_{TH}$

Basic Electronics – Special Lecture for TIPP 2011 Gary Drake, Argonne National Lab – Session 3 29

Basic Electronics – Special Lecture for TIPP 2011

Gary Drake, Argonne National Lab - Session 3

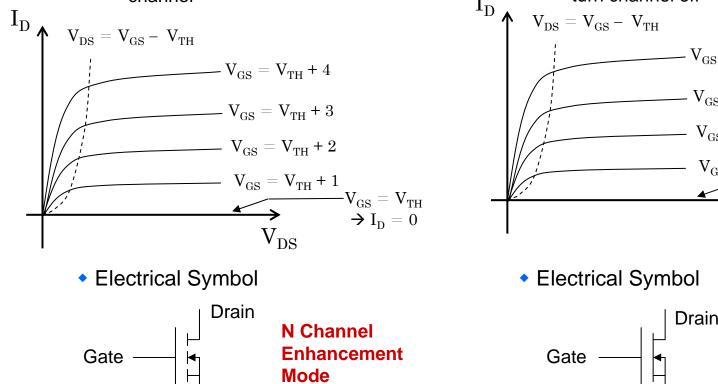

#### Types of N-Channel MOSFETs

- Enhancement Mode FETs

- Channel <u>does not</u> exist at  $V_{GS} = 0$

- This is what has been described previously

- Must provide bias  $V_{\rm GS}$  to create channel

Source

These devices are made this way through doping the channel Must provide negative bias  $V_{\rm GS}$  to turn channel off  $V_{GS} = V_{TH} + 4 = +2$  $V_{GS} = V_{TH} + 3 = +1$

Channel <u>does</u> exist at  $V_{GS} = 0$

**Depletion Mode FETs**

Source

**N** Channel

Depletion Mode

30

■ Types of P Channel MOSFETs ⇒ Everything is reversed...

⇒ Same plots, just use absolute value signs...

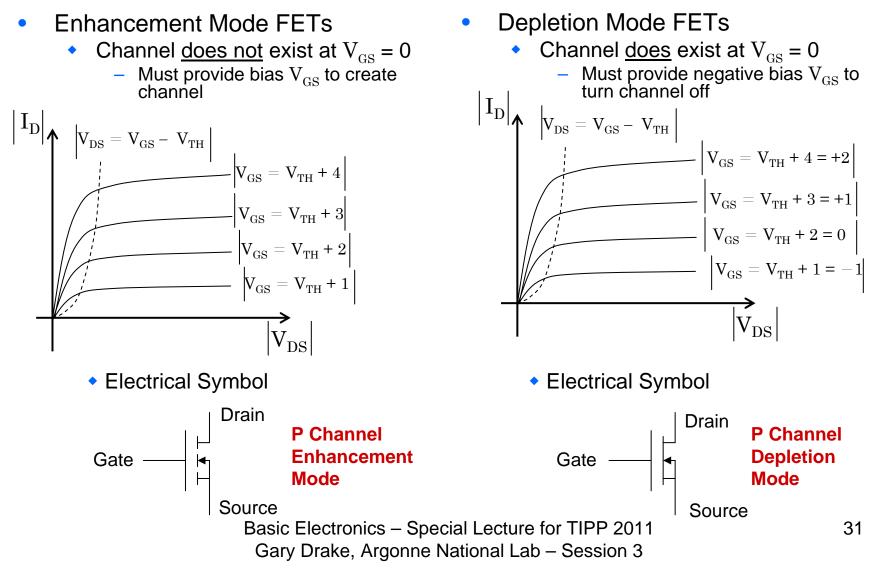

### **MOSFETS**

- **Circuit Applications**

- Linear circuits → Amplifiers

- Voltage-controlled current source with gain

- Excellent when need high input impedance

- Analog Switches

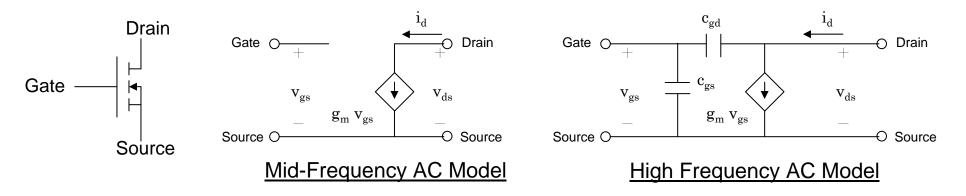

- Linear Circuit Models (N channel Enhancement Mode)

- Properties:

- High impedance between Gate and Source

- In Active Region, Drain-Source looks like a voltage-controlled current source

- Generally, there are two types of models:

- DC biasing

- AC performance

- General Approach

- Find DC operating point

- AC parameters found from small excursions around operating point

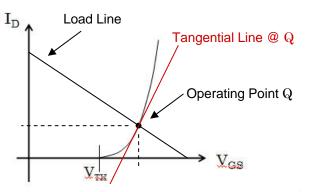

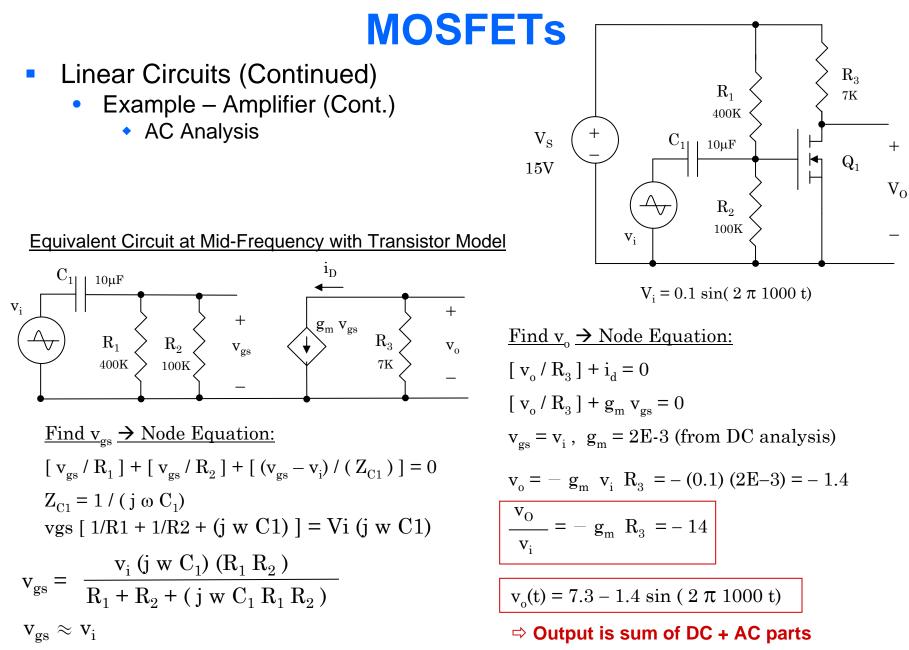

AC Transconductance:  $g_m = \partial I_D / \partial V_{GS}$ Found at Operating Point Q

Generally, AC response occurs at small deviations around Operating Point

#### ⇒ Output will be the sum of the DC operating point + the AC response

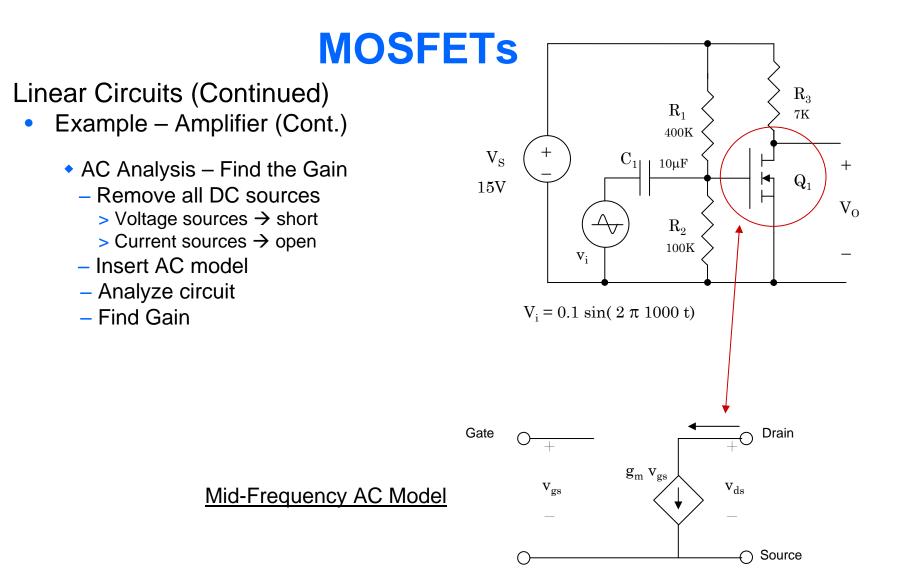

- Linear Circuit Models (N channel Enhancement Mode) (Continued)

- AC Model (assumes operation in active region)

- Includes voltage-dependent current source with transconductance  $g_m$

- + Sometimes includes parasiitic capacitances between Gate and Drain  $c_{\rm gd}\text{,}$  and between Gate and Source  $c_{\rm gs}$

- ⇒ Usually, FET parameters are supplied by the manufacturer

- Spice Models

- Level 2: Use equations

- BSIM: Behavorial

- Much more accurate

- Takes advantage of knowing process parameters

- Used extensively for ASIC design

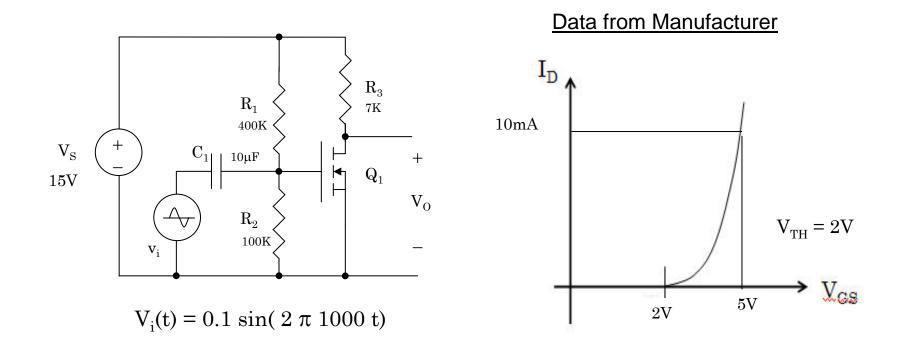

- Linear Circuits

- Example Common Source Amplifier N-channel, Enhancement Mode

Basic Electronics – Special Lecture for TIPP 2011 Gary Drake, Argonne National Lab – Session 3 36

+

Vo

+

Vo

#### **MOSFETs**

Basic Electronics – Special Lecture for TIPP 2011 Gary Drake, Argonne National Lab – Session 3 39

#### **MOSFETS**

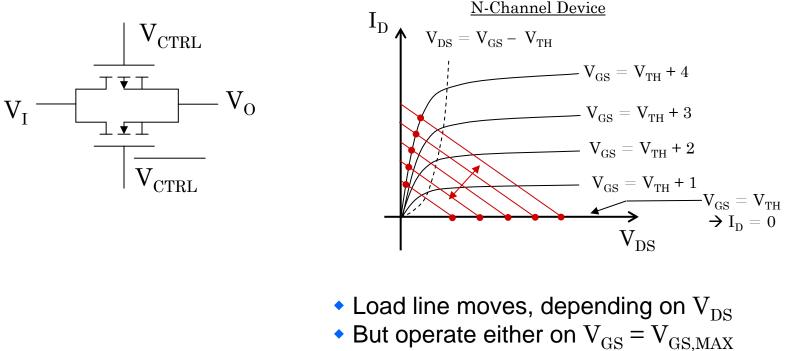

- Analog Switches

- Principle: Operate either in ohmic region, or at ID = 0

But operate either on V<sub>GS</sub> = V<sub>GS,MAX</sub> or on V<sub>GS</sub>=V<sub>TH</sub>

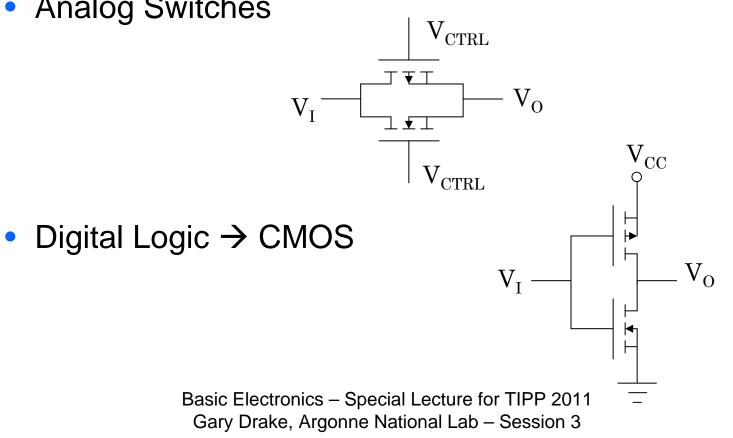

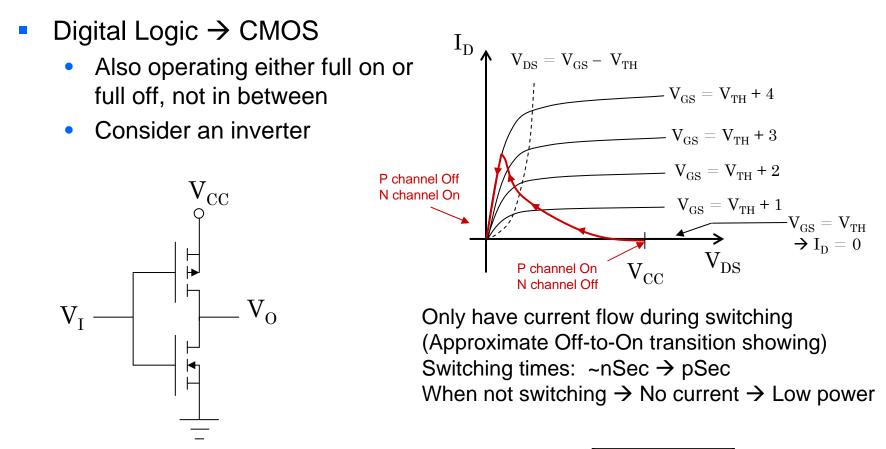

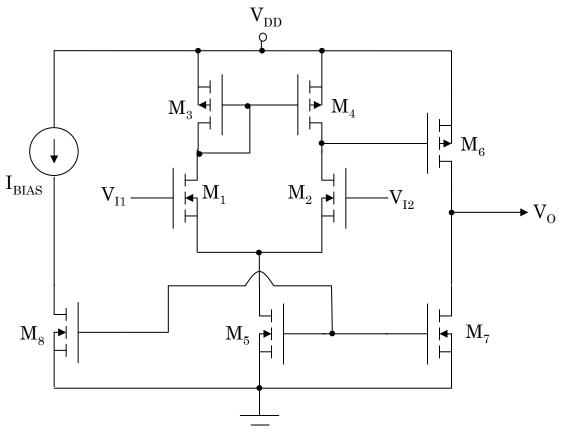

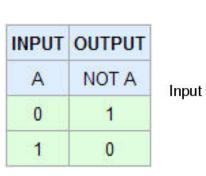

#### **MOSFETS**

• When

$$V_I = V_{CC}$$

,  $Q_2$  ON,  $Q_1$  OFF  $\rightarrow$   $V_0 = 0V$

• When  $V_I = 0V$ ,  $Q_2$  OFF,  $Q_1$  ON  $\rightarrow$   $V_0 = V_{CC}$

| V <sub>IN</sub> | V <sub>OUT</sub> |

|-----------------|------------------|

| L               | Η                |

| Н               | L                |

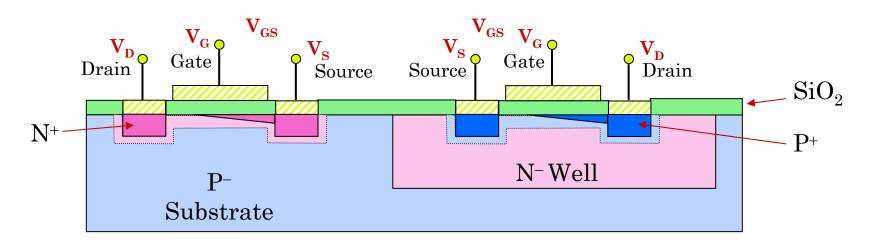

### CMOS

#### Motivation

- For many circuits (amplifiers, switches, digital logic), it is useful to have both N-channel and P-channel devices on the same substrate

- How is this done?  $\rightarrow$  P wells & N wells

- Basic Construction

#### ⇒ Basis for modern IC fabrication technologies

#### Introduction

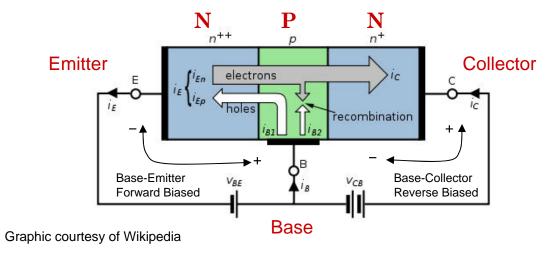

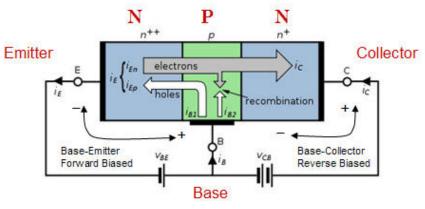

- Bipolar Junction Transistors (BJTs) are 3-terminal devices, where the current flow between two of the terminals (Collector & Emitter) is controlled by injecting charge into the third terminal (Base), which creates diffusion currents between the two active terminals.

- Current flow is achieved by diffusion currents between the two highly-doped active terminals (Collector & Emitter)

- Charge carriers are minority carriers

(p-type → electrons, n-type → holes)

- Current flow is bi-directional (both electrons and holes participate)

- Basic Construction NPN Transistor

- Conceptual construction

- ⇒ Looks like two back-to-back diodes

- ⇒ Base-Emitter junction is forward-biased

- ⇒ Base-Collector junction is reverse biased

- Basic Construction NPN Transistor

- How does it work?

- Start by injecting a hole into the Base from external source

- Extra hole in Base attracts electrons from the Emitter

- As electrons enter Base from Emitter, they are swept through the base by the strong electric field seen by the reverse-biased Base-Collector junction

Graphic courtesy of Wikipedia

- Generally, N electrons are swept through from Emitter to Collector before hole in Base can migrate to Emitter

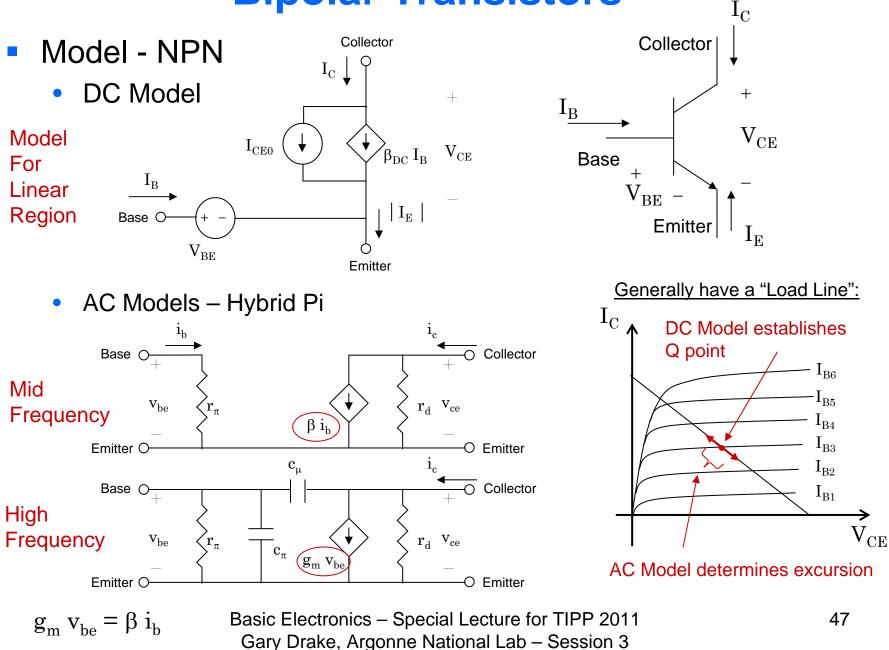

- Gives Current Gain  $\beta$  =  $I_{\rm C}$  /  $I_{\rm B}$

- Some holes in Base recombine in Base with electrons from Emitter

- Most holes make it to the Emitter

- The unique construction of the junctions, along with the special doping levels, make this work

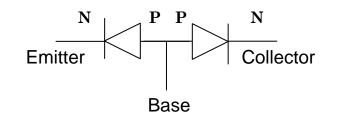

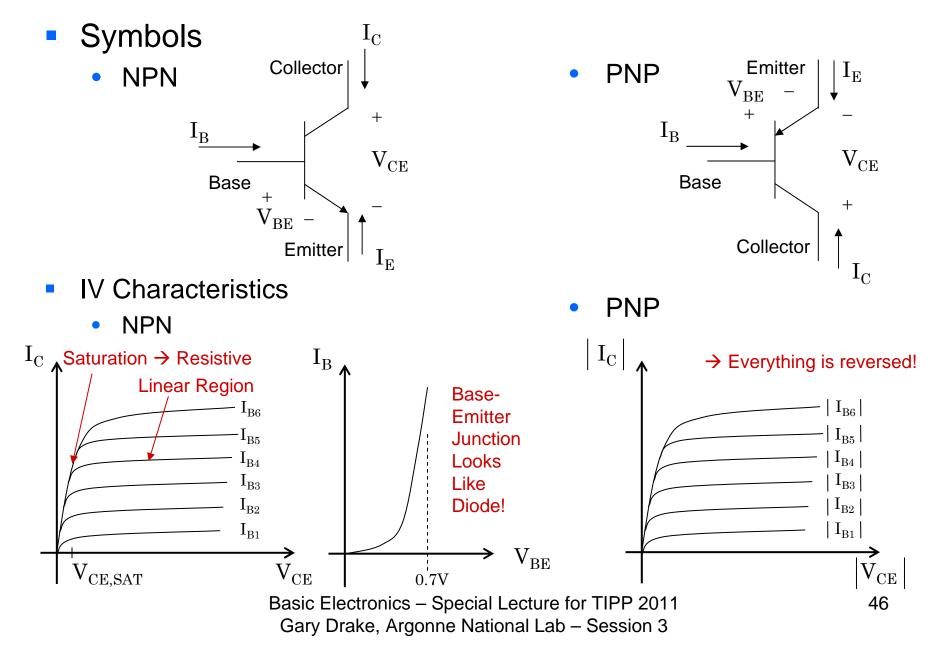

- ⇒ Can have NPN, or PNP Transistors

Basic Electronics – Special Lecture for TIPP 2011 Gary Drake, Argonne National Lab – Session 3

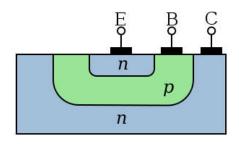

#### **Typical Construction**

Graphic courtesy of Wikipedia

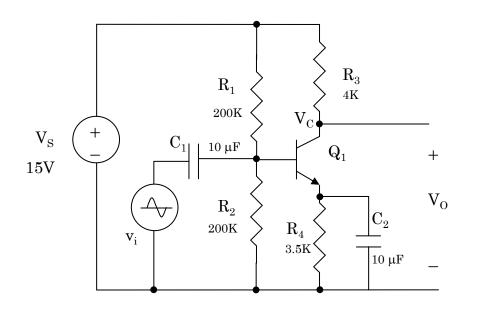

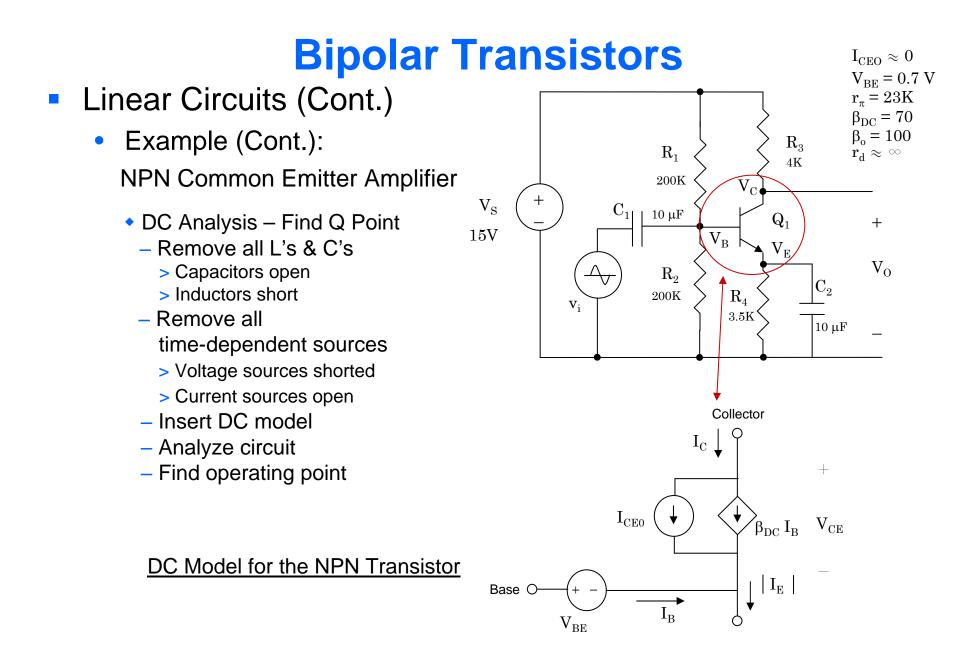

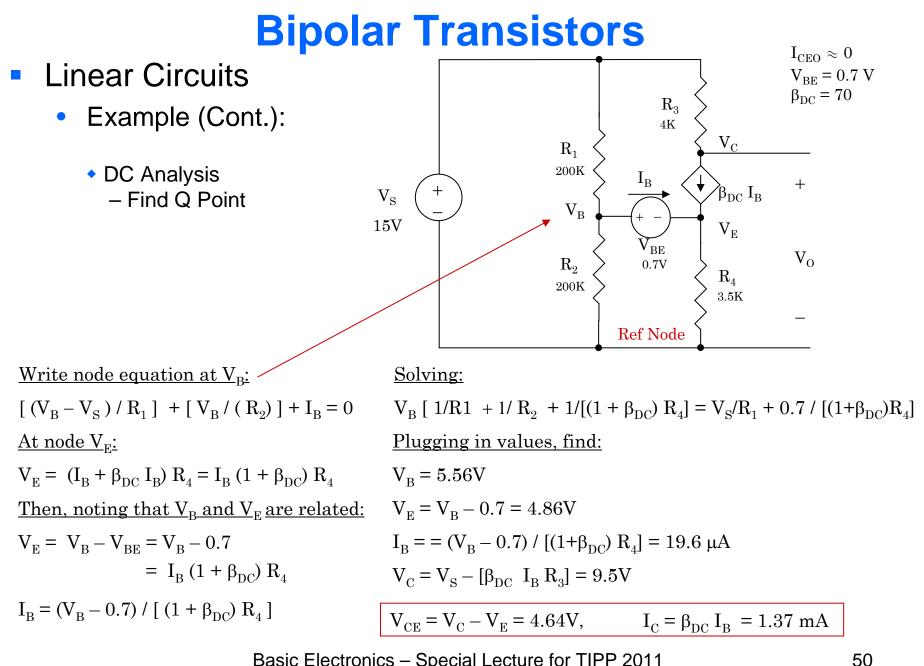

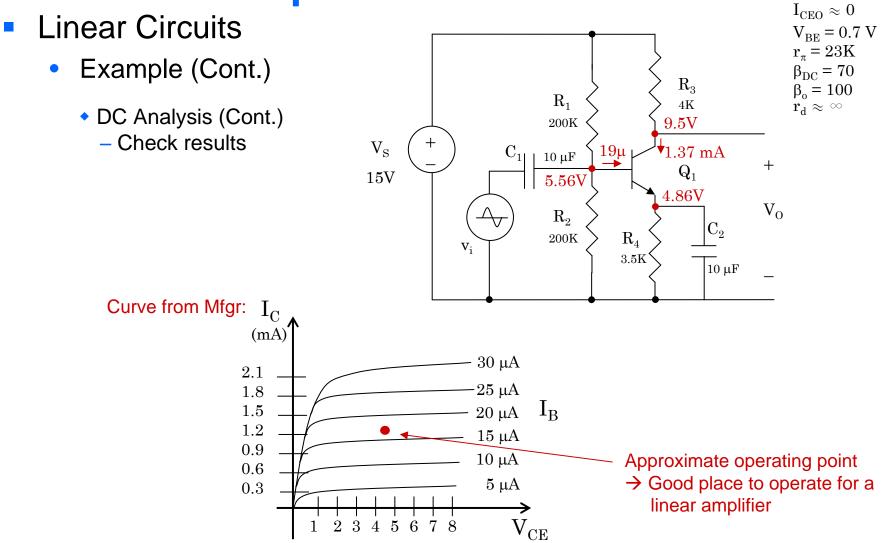

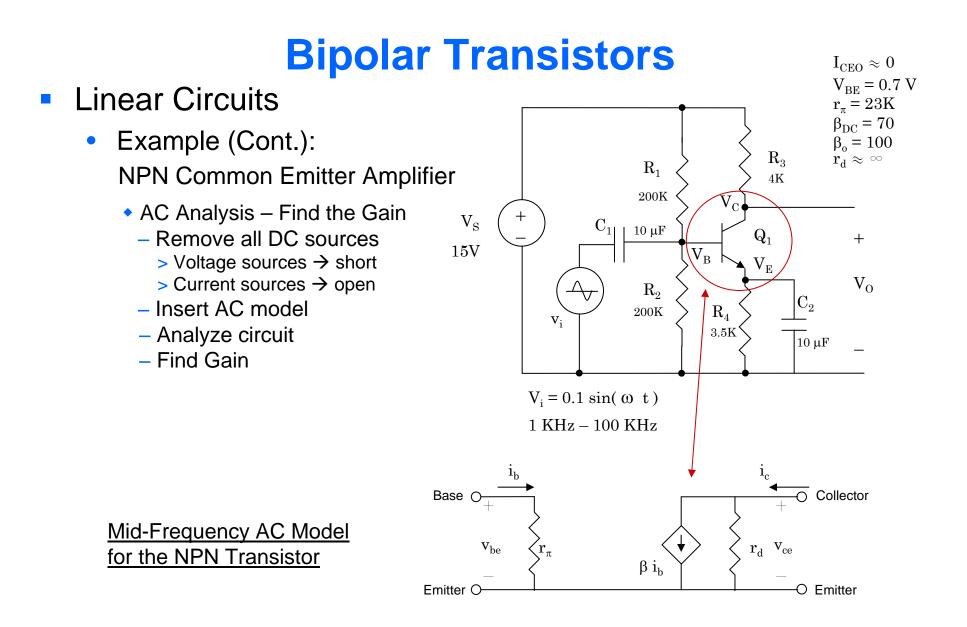

- Linear Circuits

- Example: NPN Common Emitter Amplifier

$V_i = 0.1 \sin(\omega t)$ Frequency of operation: 1 KHz – 100 KHz

Basic Electronics – Special Lecture for TIPP 2011 Gary Drake, Argonne National Lab – Session 3

48

Basic Electronics – Special Lecture for TIPP 2011 Gary Drake, Argonne National Lab – Session 3 49

Basic Electronics – Special Lecture for TIPP 2011 Gary Drake, Argonne National Lab – Session 3 53

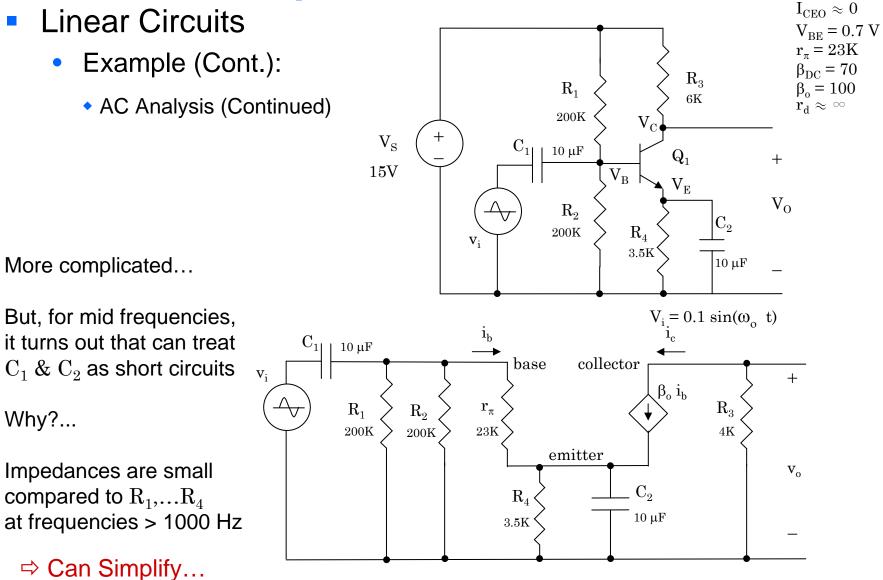

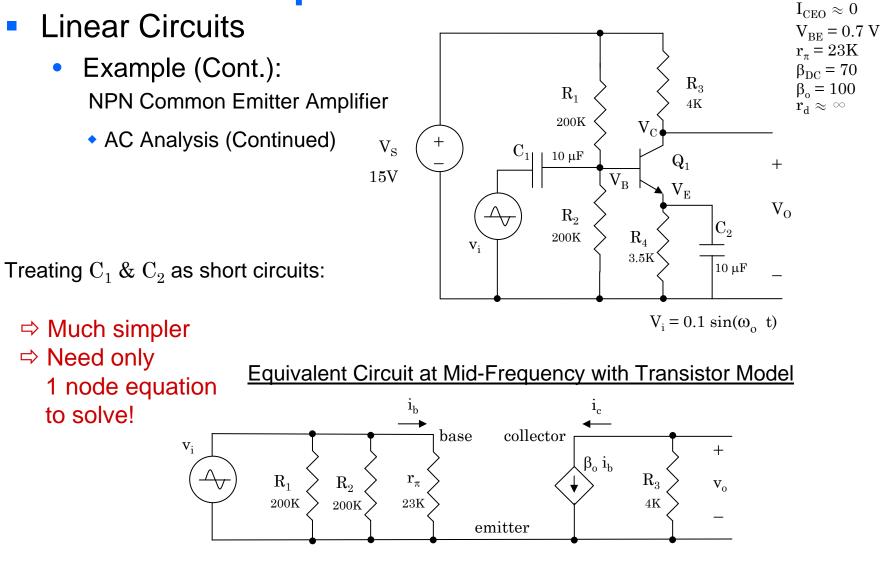

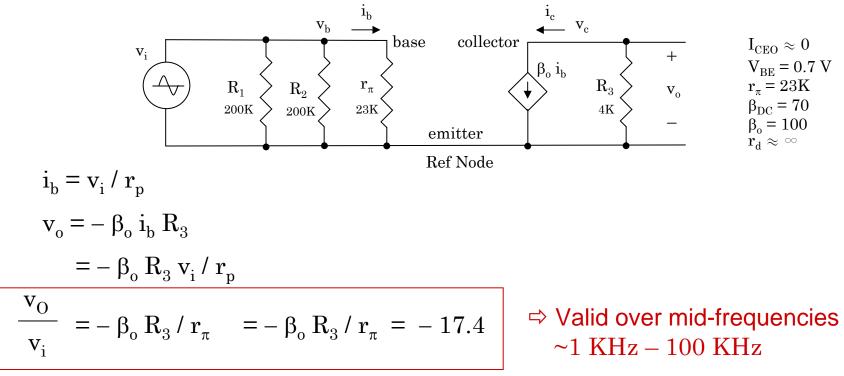

- Linear Circuits

- Example (Cont.): NPN Common Emitter Amplifier

- AC Analysis (Continued)

For:  $v_i(t) = 0.1 \sin(2 \pi 10,000 t) \rightarrow v_o(t) = 9.5 - 1.74 \sin(2 \pi 10,000 t)$

#### ⇒ Output is sum of DC + AC parts

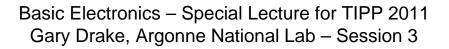

# **CMOS Analog Circuits**

- A Basic CMOS, Differential, 1-Stage Amplifier

- Uses P channel and N channel devices

- No resistors!

- Simple circuit can have gains ~1000

- → ASICS

- Designer chooses transistor width and length of channel

- Uses same principles introduced in this lecture

- Each transistor has a role...

- Generally use SPICE to simulate, but first design pass uses hand calculations

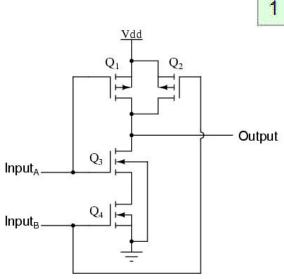

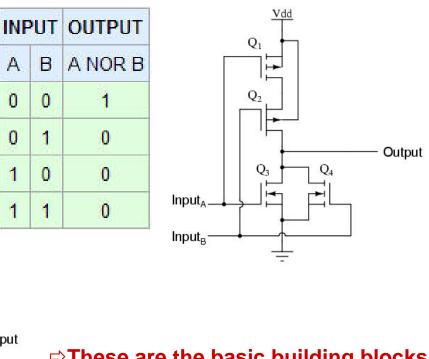

# **CMOS Digital Circuits**

NAND

| INF | UT | OUTPUT   |

|-----|----|----------|

| A   | в  | A NAND B |

| 0   | 0  | 1        |

| 0   | 1  | 1        |

| 1   | 0  | 1        |

| 1   | 1  | 0        |

NOR

These are the basic building blocks for flip-flops, counters, registers Programmable Logic, Microprocessors, ....

Images from allaboutcircuits.com

# Thank You for your Attention!

I hope that you enjoyed the course and found it useful!