# Front End Readout Electronics of the MicroBooNE Experiment

Hucheng Chen On behalf of the MicroBooNE FEE Working Group June 9<sup>th</sup>, 2011

a passion for discovery

### Outline

- Introduction

- MicroBooNE Experiment

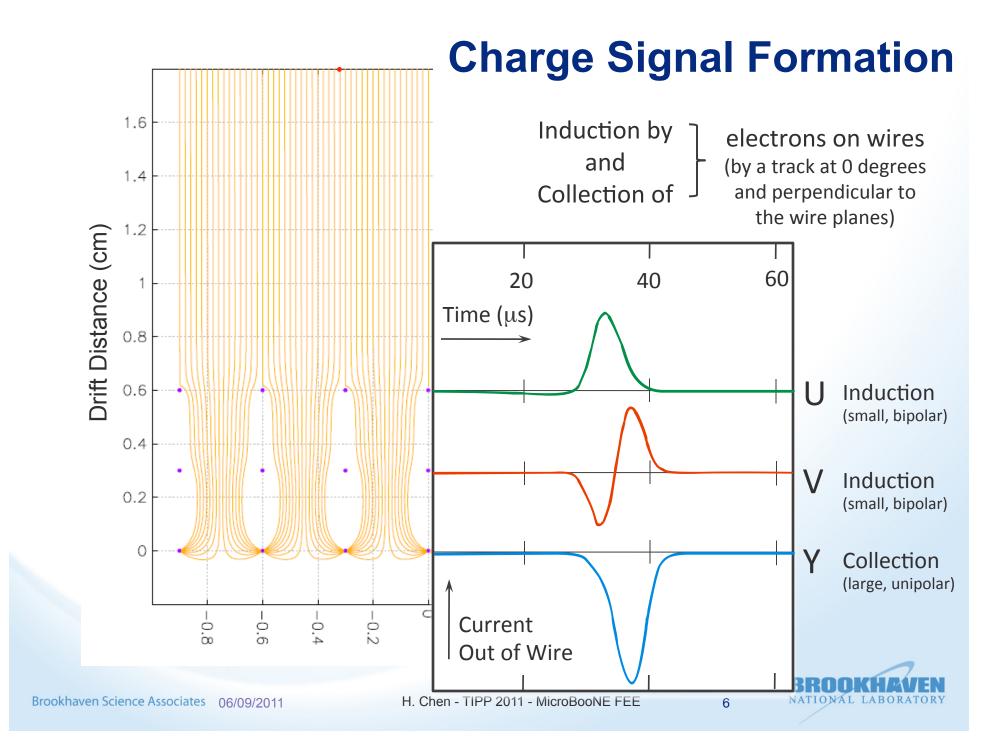

- Liquid Argon Time Projection Chamber (LAr TPC)

- LAr TPC Signal Properties

- MicroBooNE Front End Readout Electronics

- Readout Electronics System Architecture

- Cryogenic Electronics

- Front End Readout Electronics Development

- Front End Electronics (FEE) Test Stand at BNL

- Summary

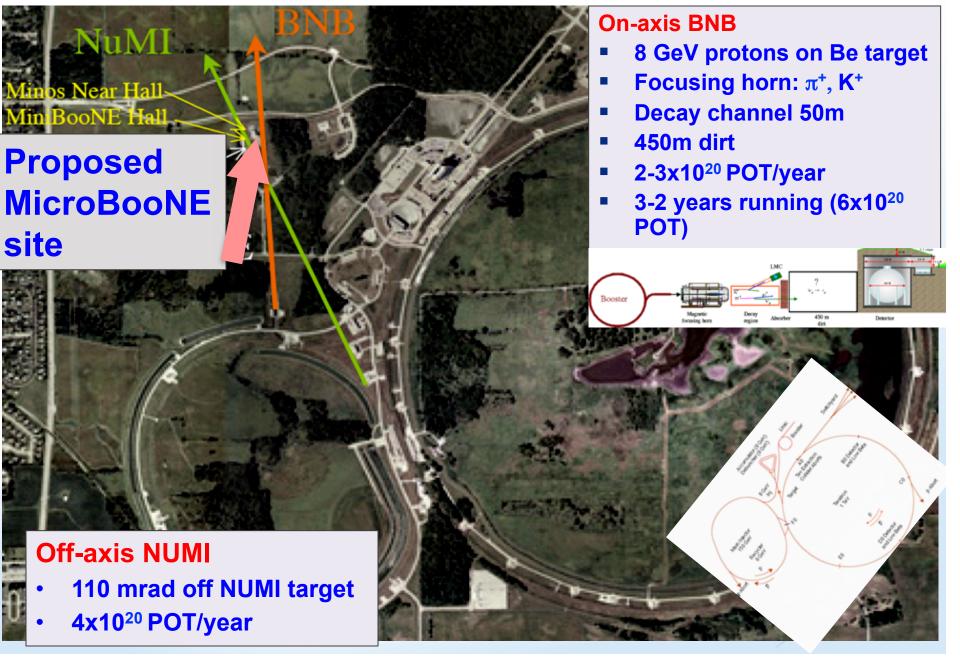

### MicroBooNE (Booster Neutrino Experiment)

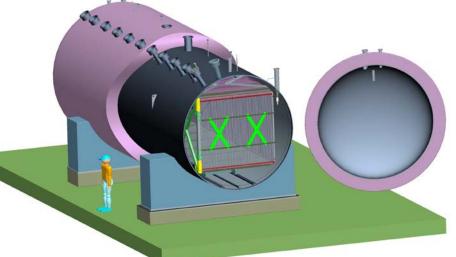

- A 150 ton (~63 ton fiducial) volume LAr TPC on the BNB/NuMI at FNAL

- Collaboration formed in 2007

- 10 univ+labs/50 phys.+eng.

- Successful DOE CD-1 review in Mar. 2010

- Prepare for CD-2 review in 2<sup>nd</sup> half of 2011

- http://www-microboone.fnal.gov

- MicroBooNE physics

- Low energy excess events observed by MiniBooNE

- Low energy neutrino cross section measurements

- MicroBooNE serves as the necessary next step in a phased program towards massive LAr TPC detectors

- Test of purity in un-evacuated, fully instrumented vessel

- Continued development of purification and filtration systems

- Cold electronics development

- Evacuable, passive (foam) insulation vessel

- TPC: ~2.5 x 2.3 x 10.4m long

- 2.5m drift @ 500V/cm

- 3 readout planes

- 3mm wire pitch

- 2 induction planes (U,V at ±60° from vertical)

- 1 collection plane (vertical wires, 2.5m long)

3

- Readout based on cryogenic analog front end

- 0.18µm CMOS technology

- 8,256 channel

- Warm feed-through

Brookhaven Science Associates 06/09/2011

### **MicroBooNE Experiment**

## How Does a LAr TPC Work?

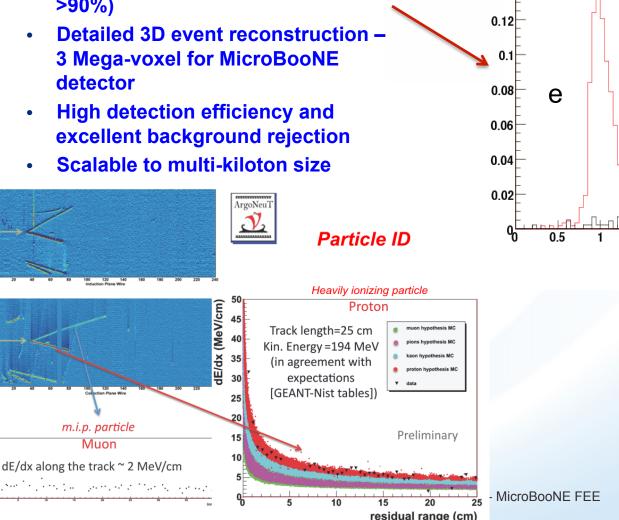

### • Why use LAr TPC

1800 1600 1400

1800 1600 1400

120

1000

- High spatial and energy resolution

- Particle identification (e/γ/π°) by dE/dx measurements (e/γ separation >90%)

Energy loss in the first 24mm of track: 250 MeV electrons vs. 250 MeV gammas 0.16 0.14 0.12 0.12 0.14 0.12 0.14 0.12 0.14 0.12 0.14 0.12 0.16 0.14 0.12 0.16 0.14 0.12 0.16 0.14 0.12 0.10 0.08 C 0.06 0.04 0.06 0.04 0.06 0.04 0.06 0.04 0.06 0.04 0.06 0.04 0.06 0.04 0.06 0.04 0.02 0.05 1 1.5 2 2.5 3 3.5 4 MIPs

5

BROOKHAVEN

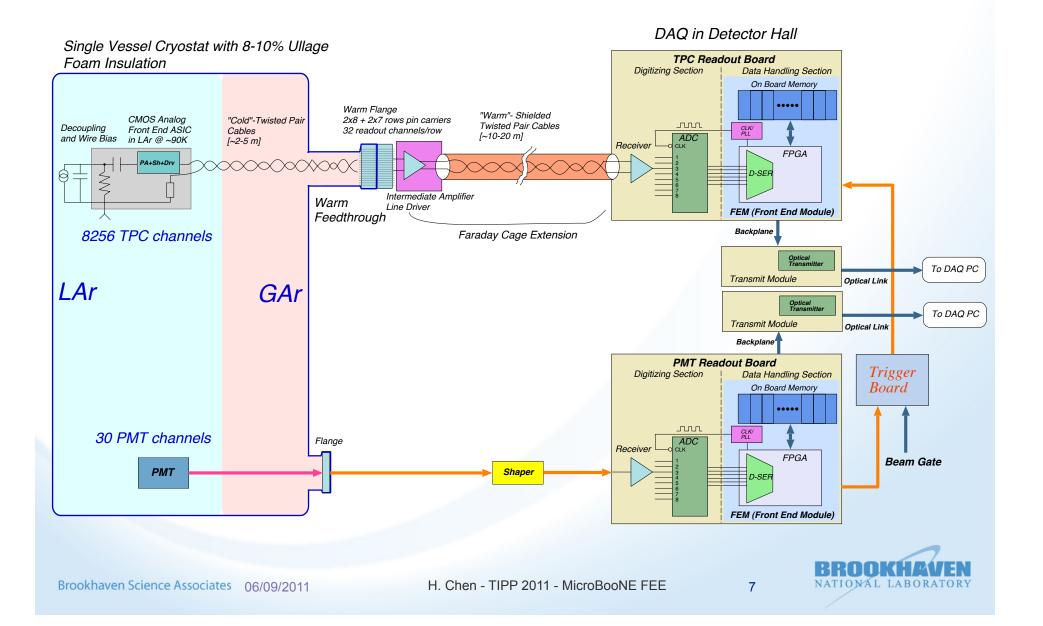

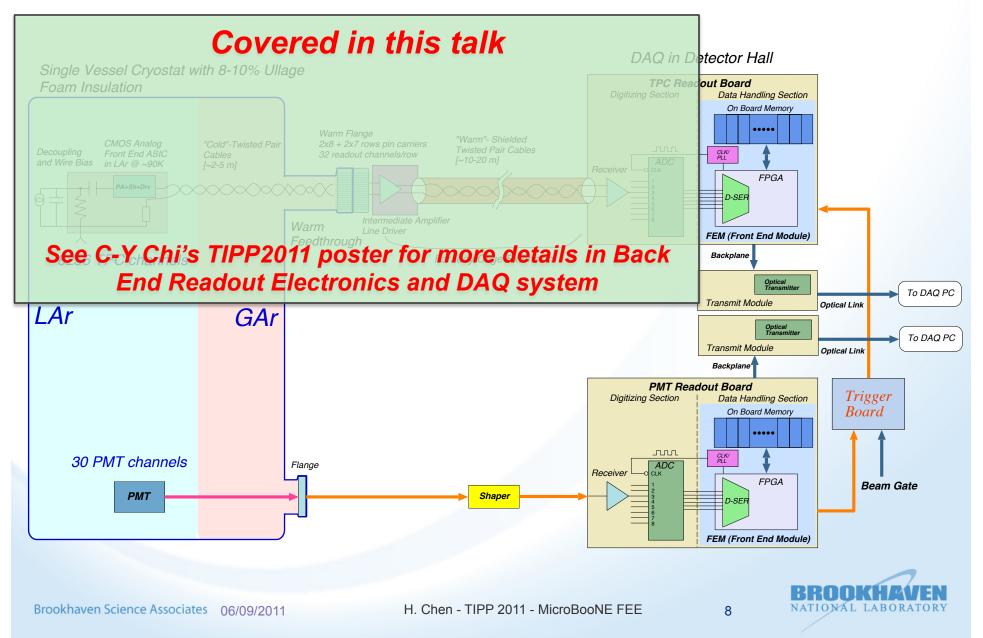

### **MicroBooNE Readout Electronics System**

### **MicroBooNE Readout Electronics System**

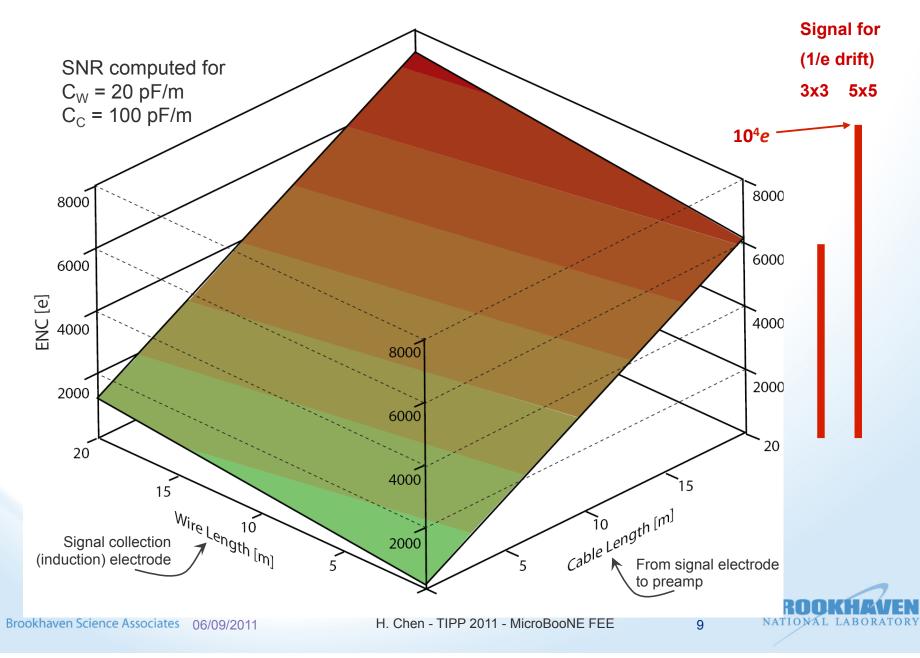

### Why Use Cryogenic Electronics

# **Cryogenic Electronics Development**

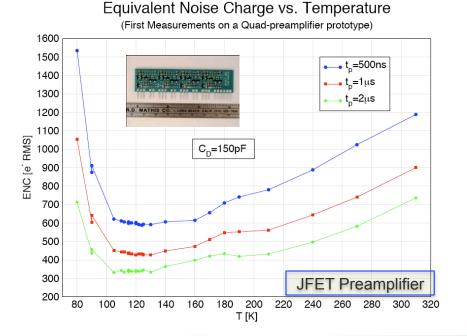

### JFET based preamplifier designed for MicroBooNE

- Bulk mobility and transconductance increase as temperature decreases, carrier freeze out causes ENC increasing when temperature lower than ~100K

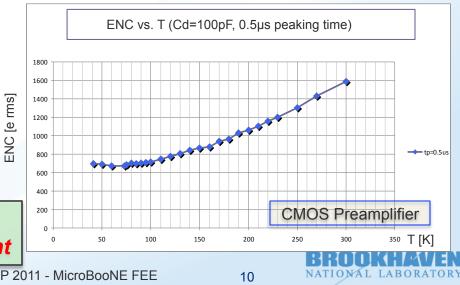

- CMOS technology preliminary test result of existing ASIC in 0.25 µm (not designed for LAr)

- CMOS in LAr has less than half the noise as that at room temperature, higher mobility and higher transconductance/current ratio

- **MicroBooNE** has adopted the cryogenic CMOS analog front end ASIC developed for LBNE LAr TPC program

See Craig Thorn's TIPP2011 talk for more details of cryogenic electronics development

Brookhaven Science Associates 06/09/2011

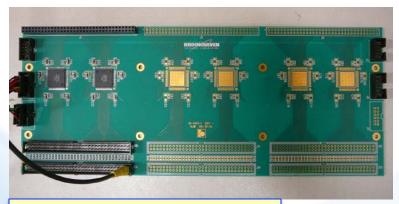

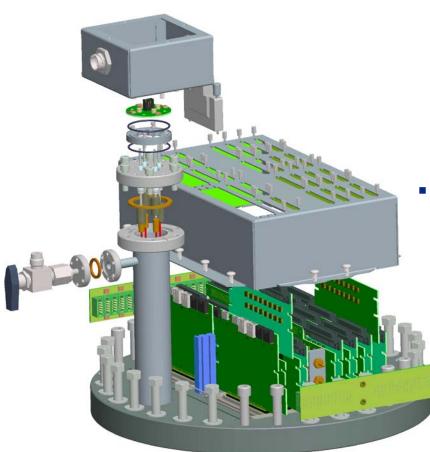

## **MicroBooNE Cryogenic Electronics**

Cold motherboard with 4 ASIC chips (64 channels) populated

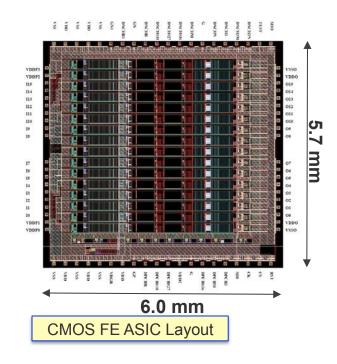

#### CMOS Analog Front End ASIC

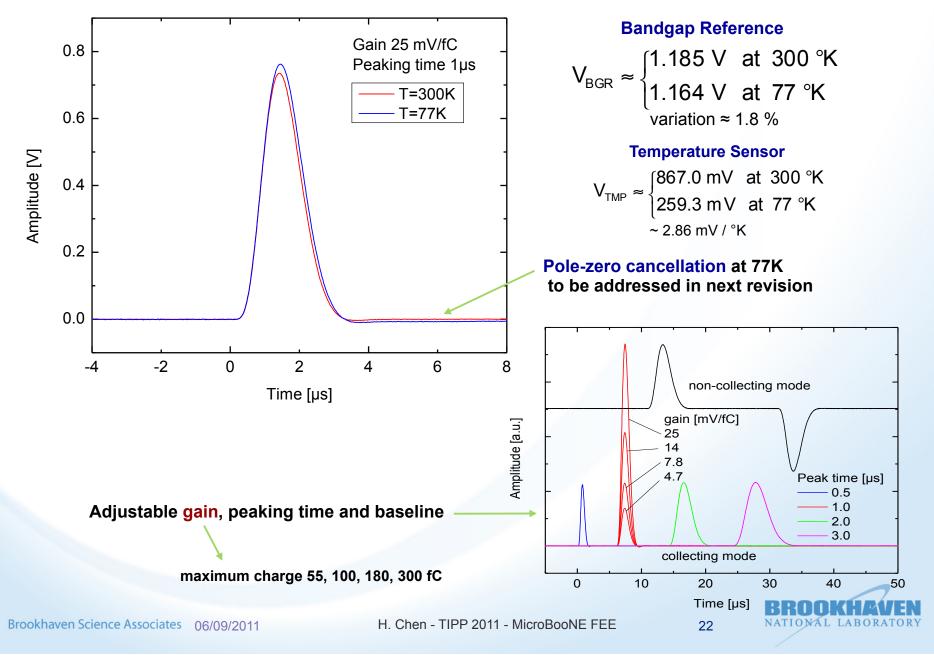

- 16 channels per chip

- Charge amplifier, high-order filter

- Adjustable gain: 4.7, 7.8, 14, 25 mV/fC (55, 100, 180, 300 fC)

- Adjustable filter time constant (peaking time): 0.5, 1, 2, 3 µs

- Selectable collection/non-collection mode (baseline)

- Selectable dc/ac (100 µs) coupling

- Rail-to-rail analog signal processing

- Band-gap referenced biasing

- Temperature sensor (~ 3mV/°C)

- 136 registers with digital interface

- 5.5 mW/channel (input MOSFET 3.6 mW)

- ~ 15,000 MOSFETs

- Designed for long cryo-lifetime

- Technology CMOS 0.18 μm, 1.8 V, 6M, MIM, SBRES

- Cold Mother Board

- House front end ASIC

- Rogers 4000 series base material

- Provide detector signal interconnections

- Provide ASIC control and monitoring signals, calibration network

- Provide bias voltage distribution for wire planes

- Horizontal version

- 96 "Y" channels, 48 "U" channels and 48 "V" channels

- Vertical version

- 96 "U" or "V" channels

Brookhaven Science Associates 06/09/2011

### **MicroBooNE Warm Interface Electronics**

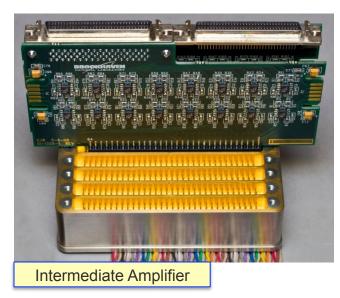

### Intermediate Amplifier

- 32 channels per board

- Differential driver to improve noise immunity

- Provide an appropriate gain (~12 dB) to detector signals to make it suitable for long distance (10 – 20 m) transmission

- Installed on the top of signal feed-through and housed by a Faraday cage to ensure good shielding and better noise performance

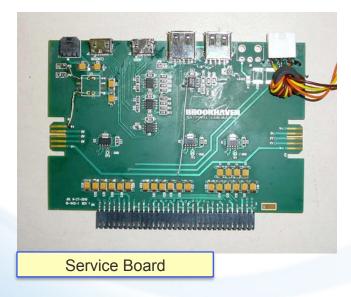

### Service Board

- Provide low voltage (+1.8 V), control and monitoring to front end ASICs

- Provide low voltage (+3.3 V, -3.3 V) filtering and distribution to intermediate amplifiers

- Provide calibration pulse driver to front ASIC which has build in switch to turn on/off pulse injection to individual channels

- Installed on the top of signal feed-through and housed by a Faraday cage

- ASIC Configuration Board

- Provide ASIC configuration signals driver from commercial off-the-shelf digital I/O board

- Provide interface between ASICs and PC

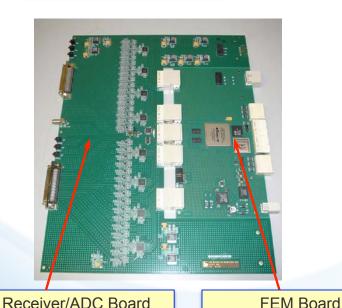

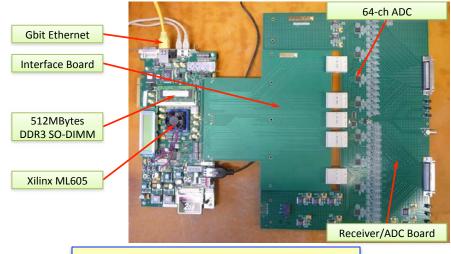

### **MicroBooNE Receiver and ADC Board**

Receiver and ADC Board

Receiver and ADC Board

- 64 channels per board

- Receive detector signals and drive to ADC input

- Each detector signal is digitized individually and continuously

- 12-bit ADC AD9222 from Analog Devices

- 8 channels per ADC

- Mating with Nevis FEM (Front End Module) to form a TPC Readout Board

- First TPC readout board assembly, mechanical integration in custom designed crate has been verified successfully

Brookhaven Science Associates 06/09/2011

### Signal Feed-through, Cable Assembly and PS

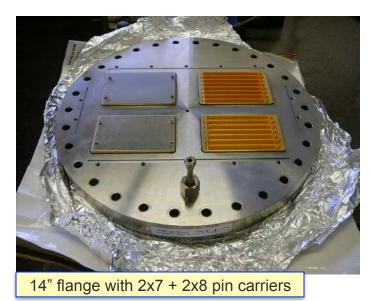

#### Signal Feed-through

- ATLAS LAr Calorimeter style feed-through, technology exists

- Pin carriers welded on flange: 100% hermetical

- 2x8 + 2x7 rows pin carriers: high signal density (1920 pins)

- Custom designed bias voltage feed-through

- Faraday box is built and mounted on feedthrough

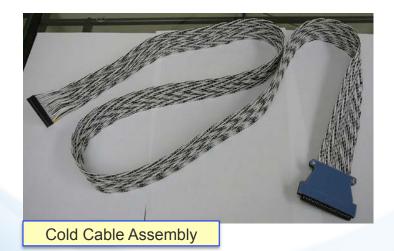

#### Cable Assemblies

- Cold cable: Teflon FEP insulation, 100  $\Omega$  +- 10%, AWG 26 solid core sliver plated

- Cold cable terminate assembly: commercial connector and jackscrews with custom designed shells to provide reliable assembly and easy handling

- Warm cable assembly is commercial off-the-shelf SCSI-3 Ultra LVD/SE MD68M/M cable

- Warm cable connector: Micro-Density 68-pin, 34 pairs

- Warm cable has aluminum-foil shielding with 10% overlap to provide Faraday cage extension

#### Power Supplies

- Front end power supplies: commercial power supply will be used to power front end electronics

- Bias voltage power supplies: commercial power supply will be used to bias detector wire planes

### Signal Feed-through, Cable Assembly and PS

Full signal feed-through assembly drawing

#### Signal Feed-through

- ATLAS LAr Calorimeter style feed-through, technology exists

- Pin carriers welded on flange: 100% hermetical

- 2x8 + 2x7 rows pin carriers: high signal density (1920 pins)

- Custom designed bias voltage feed-through

- Faraday box is built and mounted on feedthrough

#### Cable Assemblies

- Cold cable: Teflon FEP insulation, 100 Ω +- 10%, AWG 26 solid core sliver plated

- Cold cable terminate assembly: commercial connector and jackscrews with custom designed shells to provide reliably assemble and easier handling

- Warm cable assembly is commercial off-the-shelf SCSI-3 Ultra LVD/SE MD68M/M cable

- Warm cable connector: Micro-Density 68-pin, 34 pairs

- Warm cable has aluminum-foil shielding with 10% overlap to provide Faraday cage extension

- Power Supplies

- Front end power supplies: commercial power supply will be used to power front end electronics

- Bias voltage power supplies: commercial power supply will be used to bias detector wire planes

ONAL LABORATORY

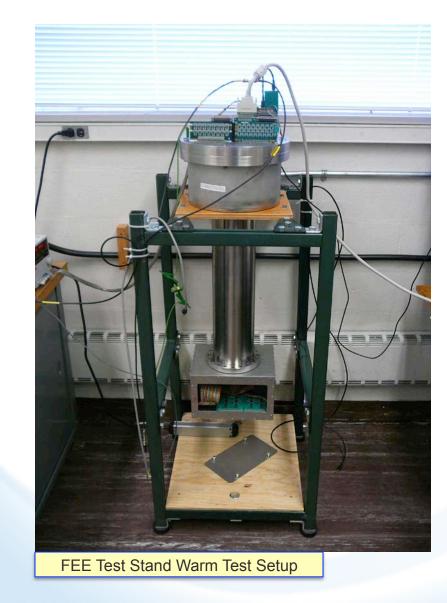

### **MicroBooNE FEE Test Stand**

FEE Test Stand Cold Test Setup

16

Brookhaven Science Associates 06/09/2011

## **FEE Test Stand Warm Test**

FEE Test Stand Back End Setup

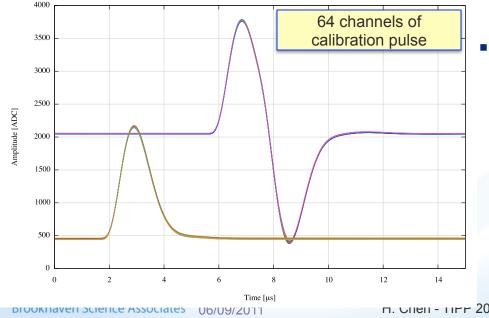

MicroBooNE FEE Test Stand Signal Readout Waveforms

- Full front end readout electronics chain

- Analog front end ASICs

- Cold mother board

- Cold cable

- Signal feed-through assembly with Faraday cage

- Intermediate amplifier

- Service board

- Calibration board

- Warm cable

- Receiver/ADC board

- Data is acquired to PC through an interface board, FPGA board and Gigabit Ethernet

#### FEE test stand is fully up and running

- Warm test is being performed

- Cold test will be followed

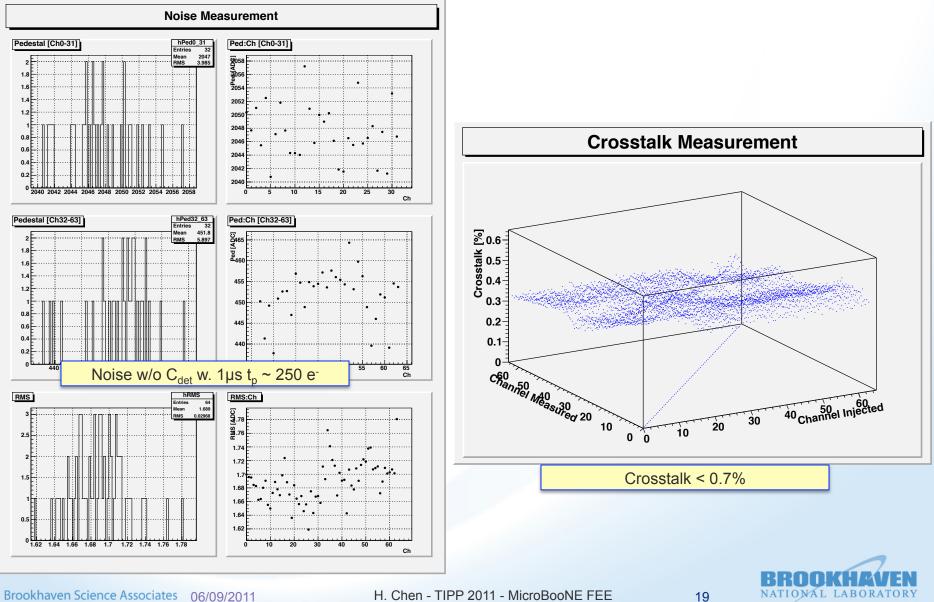

- Without detector capacitance, noise is ~250e<sup>-</sup> with 1us peaking time

- With 150pF capacitance, noise is ~1000e<sup>-</sup> with 1us peaking time

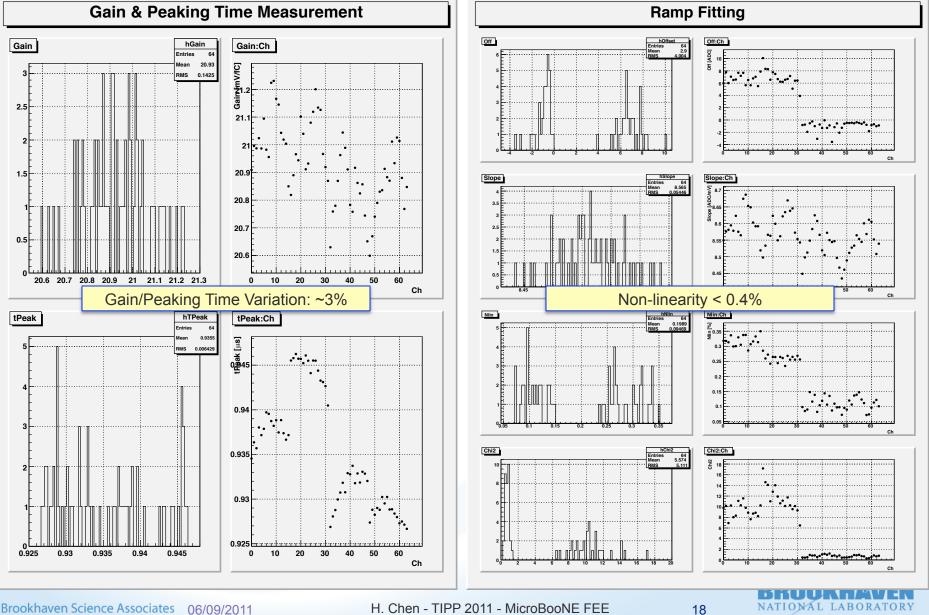

- Nonlinearity is less than 0.4%, crosstalk is less than 0.7%

17

### **Preliminary Warm Test Results**

Brookhaven Science Associates 06/09/2011

H. Chen - TIPP 2011 - MicroBooNE FEE

NATIONAL LABORATORY

# **Preliminary Warm Test Results**

# Summary

- LAr TPC is a high resolution imaging technology with excellent background rejection for neutrino oscillation measurement, proton decay with potential to reveal new physics

- Cryogenic electronics installed close to the detector elements is critical to ease scaling issues and improve signal to noise ratio

- MicroBooNE will be the first running neutrino experiment to use a specific implementation of cryogenic front end electronics

- MicroBooNE front end readout electronics system

- Readout architecture and data flow are well defined to accommodate the different running modes

- MicroBooNE will be instrumented with cryogenic CMOS analog front end ASIC

- MicroBooNE front end electronics parts have been prototyped successfully

- MicroBooNE FEE test stand has been constructed and is fully functioning

BROCKHAVEN

### **Backup Slides**

Brookhaven Science Associates 06/09/2011

H. Chen - TIPP 2011 - MicroBooNE FEE

21

### 1<sup>st</sup> Version of CMOS ASIC – Signal Measurement

#### 1800 **Layout Detail** T=300K 1600 T=77K 1400 C<sub>IN</sub>=220pF (MICA) ENC (electrons r.m.s.) 1200 target at 90K 1000 Input Line Input MOSFET 800 L≈1 mm L = 270 nm measured $W = 3.5 \,\mu m$ W = 10 mm (M3 + M4) (50µm x 200) 600 R ≈ 11 Ω g<sub>m</sub> ≈ 40 mS (25 Ω) 400 900 simulated at 1µs T=77K C\_=220pF dielectric: - MICA 200 800 - NP0 2 3 0 r.m.s.) Peaking Time (µs) ENC (electrons r 009 002 Measurements include: input line parasitic resistance ~11 Ω • ~ 350 e<sup>-</sup> at 77 K dENC $\approx \sqrt{2kTC_{IN}tg\delta}$ addressed in next revision 210e<sup>-</sup> for NPO 500 • C<sub>IN</sub> dielectric noise (not present in wire) ≈ 0 2 3 100e<sup>-</sup> for MICA • ~ 100 e<sup>-</sup> at 77 K Peaking Time (µs)

### 1<sup>st</sup> Version of CMOS ASIC – Noise Measurement

Brookhaven Science Associates 06/09/2011

H. Chen - TIPP 2011 - MicroBooNE FEE

23