## EP-ESE/SY-BI Collaboration Seminar June 2021

## BLM SYSTEM: RADIATION TOLERANT DEVELOPMENTS

Christos Zamantzas on behalf of the BLM team

Belen Salvachua, Eva Calvo, Ewald Effinger, Francesco Martina, Mathieu Saccani, William Vigano'

# SYSTEM OVERVIEW

## LHC BLM System Overview

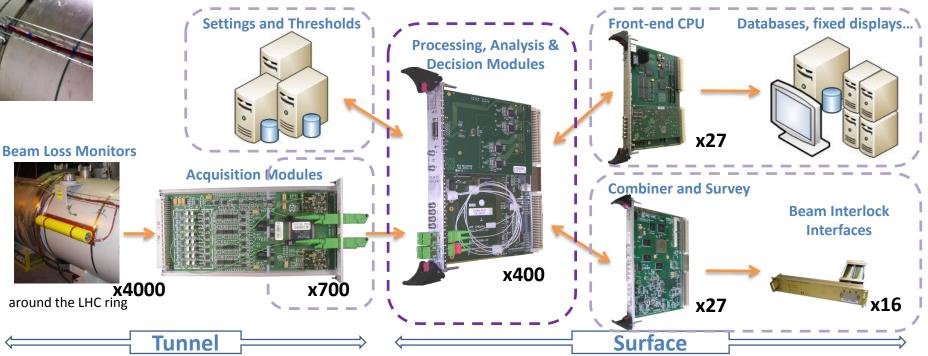

- Highly critical system for the protection of LHC

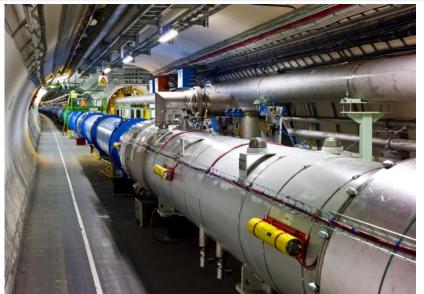

- Deployed all around the 27 km of the tunnel

- Speed, Reliability, Fail-safety is required

- Large amount of measurement data are published continuously

## Specifications

### 5. USE OF THE BLM'S FOR MACHINE PROTECTION

The strategy for machine protection impacts on the BLM design in two ways, its time response and the reliability.

Protection of the machine from beam losses has two aspects:

- protection against beam losses that could lead to damage of equipment,

- protection against beam losses that could lead to a quench of a magnet.

Since a repair of superconducting magnets would take several weeks, the protection against damage has highest priority and damages should be strictly avoided (SIL 3, 1E-8 to 1E-7 1/h).

In case of a quench, the quench protection system would prevent equipment damage. However, the beam would be lost and reestablishing operation would take several hours. Therefore the number of quenches should be minimized

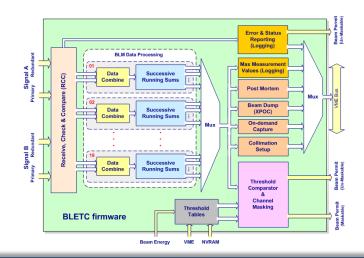

## LHC BLM System Data

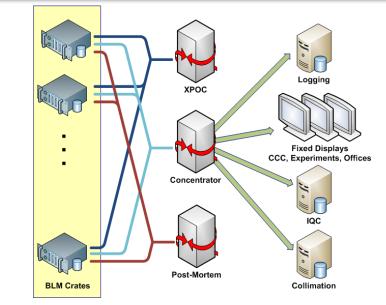

- High data volumes & multiple applications

- 8.6 billion records/day , 100'000 variables, 300 GB/day

- Recording at 1Hz in a Logging DB via a Data Concentrator

- Measurements and Thresholds used

- System statuses and diagnostic data

- Designed system monitoring processes to protect and predict failures from degradation and aging

- System is self-tested continuously

- Automatic external regular checks

## LHC Tunnel Installation

Detector positions

ARC electronics

Signal and HV distribution

DS & LSS electronics

#### christos.zamantzas@cern.ch

## **Future Specifications Summary**

- Equal/similar specifications needs for SPS and LHC

- Deployment at LHC during LS4, i.e. after validation in SPS

- Harmonisation across the Accelerator Complex with two systems to maintain (PS Complex and LHC/SPS systems)

- Reduce effort in procurement, testing and spares management

### Main functionalities

- Radiation tolerant electronics up to 1 kGy

- 10 μs acquisition period & real-time processing

- 8 orders of dynamic range (from few pA to 1 mA)

- On-board diagnostics and telemetry

- Bidirectional communication with the acquisition electronics

## Deployment Strategy

- LS3 populate SPS Ring with new system

- New crate with standard CFC v2 module

- ARC: front end in the tunnel with fibre connection

- LSS: copper cables from the detector to the surface.

- Some locations to be populated with the BLMASIC for development.

- LS3 upgrade processing electronics at LHC

- First step for the system consolidation

- Temporary use of fibre optic elements (adapters and SFP receivers)

- LS4 upgrade acquisition electronics at LHC

- Deploy new crate and CFC v2 at the LHC tunnel

- Deploy in parallel BLMASIC modules in strategic locations

- Aim for the new triplets and long cables at collimation areas

- Acquisition electronics in the tunnel

# **DEVELOPMENT PROGRESS**

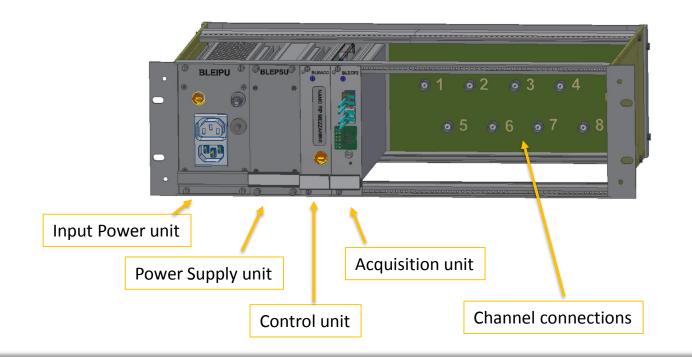

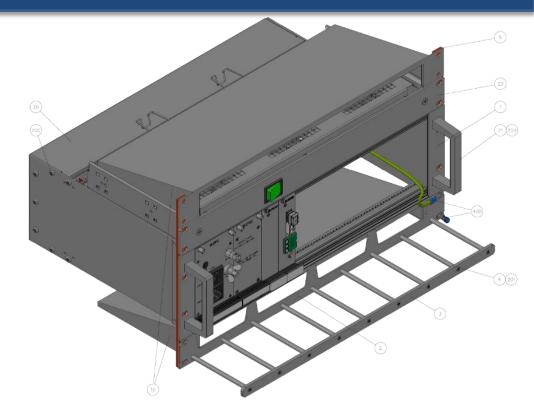

## Acquisition crate (SPS)

- First functional version of the crate ready including power supplies and backplane

- Working on the remote control card (via nanoFIP) and acquisition modules

All connections from the front side Electronics enclosed in a mini-rack

## **Acquisition Electronics**

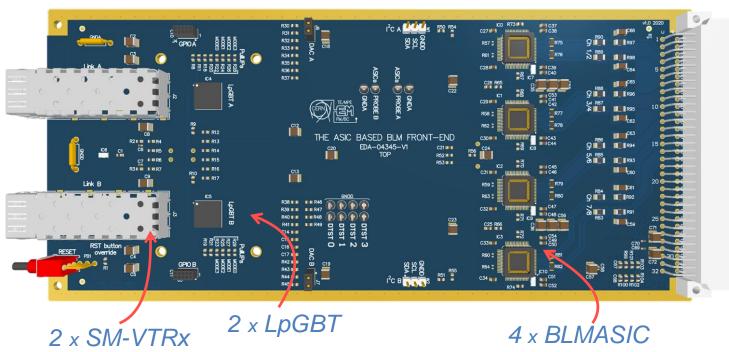

Two distinct designs on-going

- BLECF v2 (upgrade) with distinct components (COTS & ASIC)

- BLMASIC encapsulating both analogue & digital functions in rad-hard ASIC

## Commonalities pursuit

- Size and form factor, i.e. one cartridge of 6HP

- Backplane connection and power scheme

- Communication (lpGBT & SM-VTRx)

- Acquisition frequency and range

- Additional advantages (TBC)

- Interchangeable where necessary

- Main processing blocks common

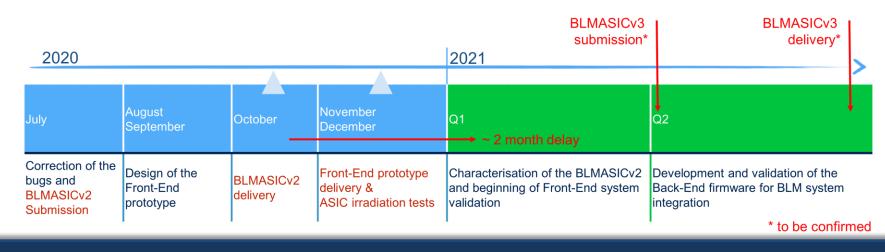

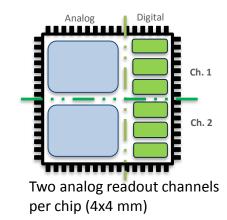

## BLMASIC: Current-to-Frequency or $\Delta/\Sigma$ Converter

- Two analogue-to-digital converter circuits under investigation:

- Current-to-Frequency (CFC) &  $\Delta/\Sigma$  converter

- v2 achieved linearity and low current measurement specs

- Preliminary results from x-ray irradiation exceeds specs

- Next version (v3) will focus on the CFC type only

- Address ESD, power and minor digital part issues

- Some delays due to COVID-19

- Dependency on foundries and packaging of the devices

Standard 64-pin Quad Flat Package (10x10 mm)

## BLEIC: Printed Circuit Board Prototype (1/2)

#### New prototype PCB design complete

- Includes all functionalities expected from the final system

- Can accept any of the two analogue-to-digital converter circuits under investigation:

- Current-to-Frequency

- Δ/Σ

- Common digital parts, control and form with standard BLM acquisition board.

- Secured prototypes of the other custom parts, e.g. the SM-VTRx and LpGBT.

### Currently at production a variant able to accommodate both BLMASIC v2 & v3 $\,$

| 2019                    | 2019                            |                      |                                                     | 2020 |                                                                          |                       |                                                           | 2020                                                            | 2020                                                     |                                                       |                       | 2021                                                        |                                                                                      |                                                                                    |

|-------------------------|---------------------------------|----------------------|-----------------------------------------------------|------|--------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------|-----------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                         |                                 |                      |                                                     |      |                                                                          |                       |                                                           |                                                                 |                                                          |                                                       |                       |                                                             |                                                                                      |                                                                                    |

| June<br>2019            | July<br>August                  | September<br>October | November<br>December                                |      | February<br>March                                                        |                       | May                                                       | June                                                            | July                                                     | August<br>September                                   | October               | November<br>December                                        | Q1<br>──→ ~ 2 month delay                                                            | Q2                                                                                 |

| BLMASICv1<br>Submission | Design of the<br>Test-bench PCB |                      | Beginning of the<br>preliminary<br>characterisation |      | Noise measurements<br>acquisition on the $\Delta \pmb{\Sigma}$<br>device | results and BLMASICv2 | Noise<br>measurements<br>acquisition on the<br>CFC device | Investigation on<br>the Wilkinson<br>ADC issue<br>(BLMASIC-CFC) | Correction of the<br>bugs and<br>BLMASICv2<br>Submission | Design of the<br>installation Front-<br>End prototype | BLMASICv2<br>delivery | Front-End prototype<br>delivery &<br>ASIC irradiation tests | Characterisation of the BLMASICv2 and<br>beginning of Front-End system<br>validation | Development and validation of the Back-<br>End firmware for BLM system integration |

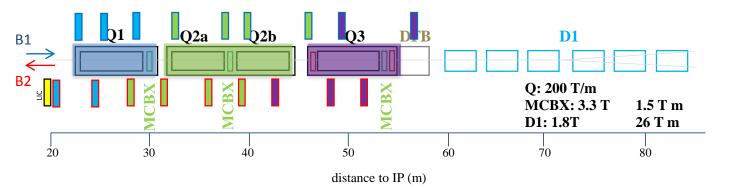

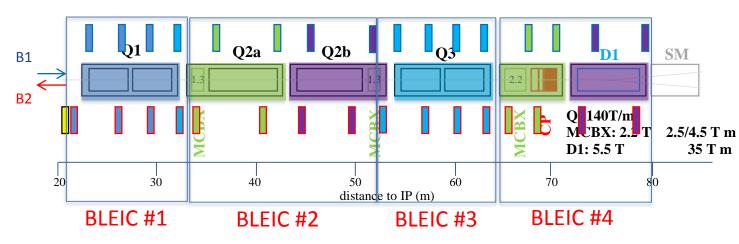

## BLEIC: LS3 Triplet Layout BLM detectors

#### Work in progress

### LHC triplet layout

### **HL-LHC triplet layout**

### Option 2: BLECF // (BLEIC/2) Half channel redundancy

| Number of detectors: IP-side |                         |                         |                 |  |  |  |  |

|------------------------------|-------------------------|-------------------------|-----------------|--|--|--|--|

|                              | Present System<br>Run 3 | HL-LHC Upgrade<br>Run 4 | New in<br>Run 4 |  |  |  |  |

| BLECF – standard             | 18                      | 32                      | 14              |  |  |  |  |

| BLEIC – new                  | 0                       | 16                      | 16              |  |  |  |  |

| subtotal                     | 18                      | 48                      | 30              |  |  |  |  |

| Number of detectors: IP1 + IP5 (both sides) |                         |                         |                 |  |  |  |  |

|---------------------------------------------|-------------------------|-------------------------|-----------------|--|--|--|--|

|                                             | Present System<br>Run 3 | HL-LHC Upgrade<br>Run 4 | New in<br>Run 4 |  |  |  |  |

| BLECF – standard                            | 72                      | 128                     | 56              |  |  |  |  |

| BLEIC – new                                 | 0                       | 64                      | 64              |  |  |  |  |

| Total IP1+IP5                               | 72                      | 192                     | 120             |  |  |  |  |

1 multiwire cable / module 1 BLEIC module = 8 channels

14/06/2021

# **RAD-TOL/HARD COMPONENTS**

# BLECF v2: Current-to-Frequency Converter

Components

Reliability level SIL3 (1E-7 to 1E-8 failure/h)

Measurement range 2.5pA to 1mA

- ✓ Input protection

- Current ~ 10A @100us

- Voltage ~ 1500V @100us

- Test features for system check

- Survey of the card voltage supplies

- Survey of detector high voltage supply

- Radiation tolerant up to 500 Gy

- Increase to ~ 1 kGy

### Integration time of 40 μs

Decrease to 10 μs

### Redundant optical data transfer to surface

- Redundant bidirectional link

- Add control over fibre

8 inputs Current-to-Frequency Converter (COTS)

- AD41240 ADC (EP-ESE)

- LM4140 voltage reference

- Antifuse FPGA for data collection

- Redundant GOH from CMS (EP-ESE)

- CRT910 Line driver (EP-ESE)

- AD5346 DAC

- Op-Amp: OPA627 -> OPA657, LTC6268, LTC6244 OneShot: 74HC123 -> 74LS123, 74HCT12 Comparator: NE521 Switch: J176 -> searching for new JFET or MOSFET

- No alternative found; new production done

- Searching

- Aim to deprecate

- Replace with LpGBT & SM-VTRx

- New ASIC to design & produce

- New DAC or SCT from LpGBT

## Rad-hard components

- Produced the AD41240 ADC

- Necessary due to End of Life (EOL) for CMOS6SF (250nm) products

- 24 wafers produced and stored at EP-ESE long-term storage (~25 kpcs)

- To be packaged and tested when we give the green light (some additional costs)

- Reserved

- IpGBT (2640 pcs includes 20% spare)

- SM-VTRx (3200 pcs incl. 30% spare)

- Order under preparation for the transmitter part (i.e. TOSA)

- Missing/searching

- Voltage regulators (e.g. LHC7913 and LHC4913 from STMicroelectronics)

- See presentation from William

- Open requests (need designs to advance further)

- SCE (for slow control and additional diagnostics)

- Level shifters for ADC connections (EP-ESE to design & produce with 1 year warning)

- FPGA (for data collection and control)

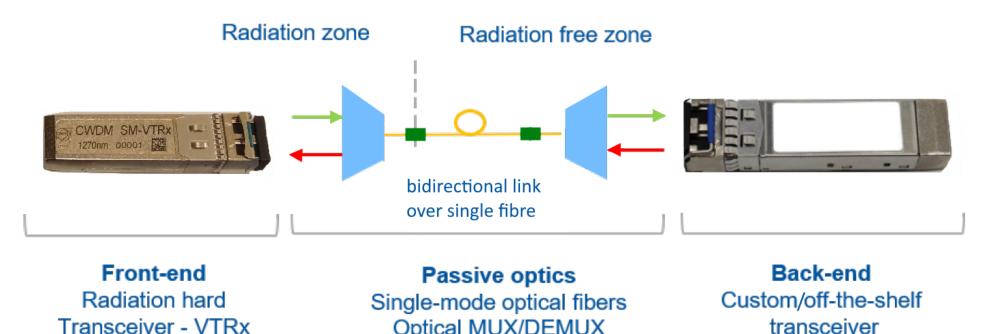

## **Optical Link Configuration**

- Bi-directional communication over single fibre with wavelength multiplexing

- Radiation qualified components

- New version of SM-VTRx packaged as SFP module

- Note, pins don't follow SFP standard

christos.zamantzas@cern.ch

**Optical MUX/DEMUX**

CONCLUSIONS

## Summary

- Consolidation (with additional functionalities) of the BLM systems at SPS and LHC is being planned

- Equal or similar functional needs

- Deployment at SPS in LS3 & LHC in LS4, i.e. after validation in SPS

- Harmonisation across the Accelerator Complex with two systems to maintain (i.e. the PS Complex and the LHC/SPS systems)

Pro: Reduce effort in procurement, testing and spares management

**Con**: Complex design effort with more parameters to account for.

- Main functionalities

- Radiation tolerant electronics up to 1 kGy

- 10 μs acquisition period & real-time processing

- 8 orders of dynamic range (from few pA to 1 mA) measurements

- On-board diagnostics and telemetry

- Bidirectional communication with the acquisition electronics

# Acknowledgements

## ■ ADC & other rad-hard ICs:

- Kostas Kloukinas

- Alessandro Marchioro

- BLMASIC:

- Jan Kaplon

- Luca Giangrande

- Pedro Pinheiro

## ■ LpGBT

- Daniel Hernandez Montesinos

- Paulo Moreira

### ■ SM-VTRx

- Jan Troska

- Carmelo Scarcella

- Leonardo Marcon

- Manoel Barros Marin

- Rad-Tol COTS:

- Rudy Ferraro

- Salvatore Danzeca

- Fibre & Copper connections:

- Jeremy Blanc

- Daniel Ricci

Many thanks to our colleagues for contributing with their technical expertise !!!