### FD2-VD Bottom CRP Electronics CDR: ASIC design status

David Christian Fermilab May 28, 2021

### Contents

- Comment on vertical drift

- LArASIC Front End Amplifier/Shaper

- COLDADC Digitizer

- COLDATA Controller/Data Concentrator

### **Comment on Vertical Drift**

- The vertical drift charge readout plane anodes are being designed with the cold electronics developed for the APA-based horizontal drift TPC in mind.

- The printed circuit board hole size, board thickness, and the spacing between boards are chosen so that the induced currents will be similar to the currents induced in APA wires.

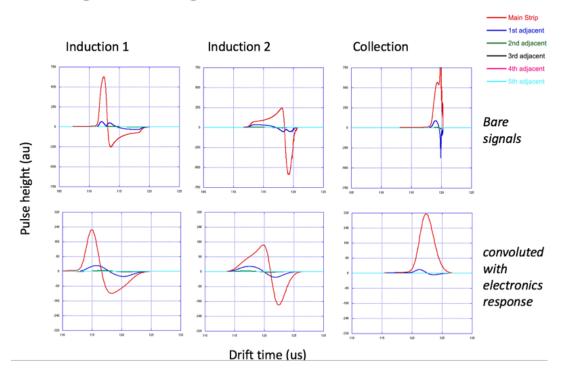

Average current signals for the 3-view reference case

- Induced currents computed by Francesco Pietropaolo for one of the proposed 3-view anodes (show at last week's collaboration meeting)

- The electronics response used was LArASIC w/2 μs shaping time.

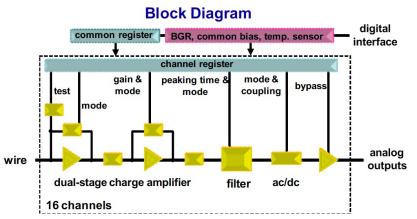

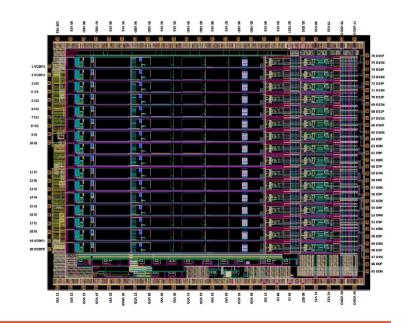

### LArASIC\_V5 (received May 2021)

- LArASIC has been developed over a number of years and versions have been used successfully in MicroBooNE and ProtoDUNE-SP

- Changes since ProtoDUNE:

- Eliminated "ledge" issue observed in ProtoDUNE.

- Added a single ended to differential converter to allow optimal coupling to COLDADC.

- Modified the band gap reference circuit to improve yield (~7% of LArASIC\_P2 chips failed to start up at cryogenic temperature).

- Modified the test charge injection pulser DAC to improve linearity for small signals while maintaining large dynamic range.

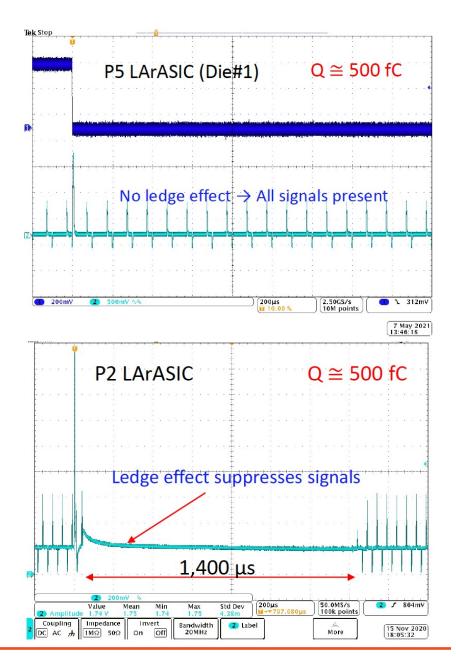

# Ledge Effect

- Ledge Effect observed in ProtoDUNE-SP has been understood and eliminated.

- Test Method:

- LArASIC internal calibration pulser is enabled (regular smaller amplitude signal)

- Large charge pulse is injected into a normal input.

🔆 Fermilab 🖂 💦

### **Single Ended to Differential Converter**

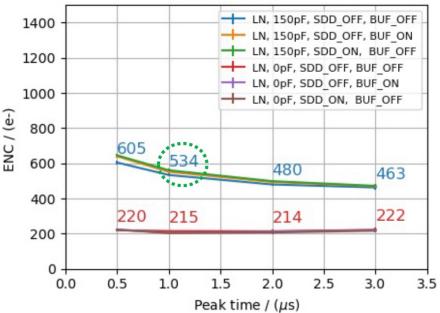

- Tests using LArASIC\_V5 and COLDADC\_P2 have been performed.

- Good results obtained with both single ended and differential outputs.

**ENC Measurement**

### **Band Gap Reference Circuit**

- 7% of the LArASIC\_P2 chips that were used in ProtoDUNE-SP and will be used in SBND fail QC because the band gap reference circuit fails to start when the chip is cold.

- The likely root cause of this failure was identified and corrected for LArASIC\_V4.

- Validation of the fix will be possible later this year when ~150 packaged LArASIC\_V5s will be tested before assembly on FEMBs.

7

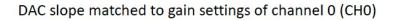

### **Test Charge Injection Pulser DAC**

Data from tests of LArASIC\_V5

Monotonic and linear operation even for large charge injection

Fermilab DUNE

### Summary

LArASIC\_V5 meets DUNE requirements for both HD & VD TPCs.

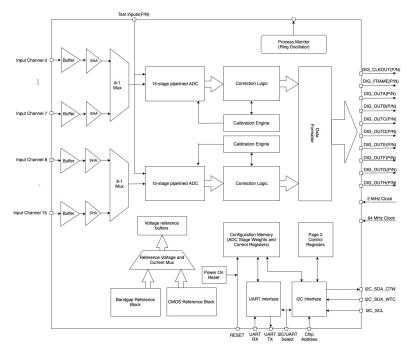

## COLDADC\_P2

- First version of COLDADC was functional (& was used in the recent test of 3-ASIC FEMBs in ICEBERG), but a number of issues were addressed for COLDADC\_P2:

- Forgotten level shifters included in input buffer block

- Power distribution improved & IR drop tool used in redesign

- Bandgap reference Op Amp "flavor error" corrected

- Automatic pipeline calibration logic fixed

- Sample and hold multiplexer linearity improved

- ADC data overflow detection & correction logic included

- Power-on-reset added

- Sampling clock control simplified

🔆 Fermilab 🖂 💦

## **COLDADC\_P2** Testing

- COLDADC\_P2 operates as designed with nominal bias voltages (2.25V & 1.1V).

- Both CMOS and Bandgap reference blocks work as designed.

- Automatic pipeline calibration works.

- Small crosstalk associated with the sample and hold multiplexer has been reduced by more than a factor of 10.

🛠 Fermilab 🖂

- crosstalk is now < 0.06%.

- All other design changes were successful.

11

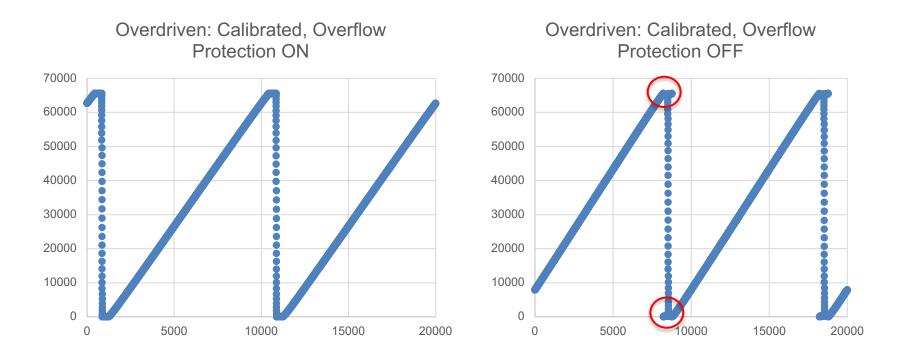

## **Overflow Protection**

If the pipeline interstage gain is greater than 2, the output can exceed 16 bits. Correction logic is included to peg overflows at the maximum ADC value and underflows at the minimum ADC value.

🛠 Fermilab 🛛 🕬

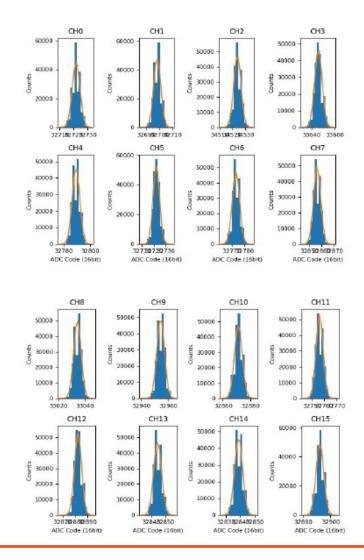

# **ADC Noise**

- COLDADC\_P1 had very low noise.

- COLDADC\_P2 also has very low noise.

- Measured noise with differential inputs at LN<sub>2</sub> temperature is ~ 130 μV rms (2.8 LSB 16-bit).

#### 🗱 Fermilab 🕬

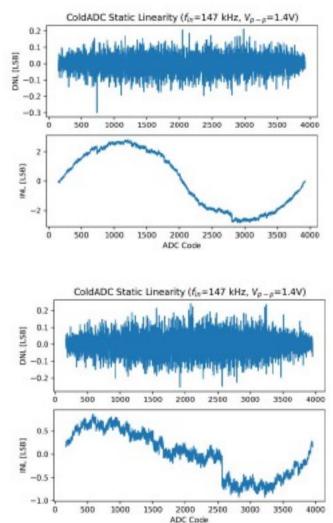

# Static Linearity (DNL & INL)

- Differential non-linearity is very good (typically less than +/- 0.2 LSB 12-bit; always much less than +/- 1 LSB)

- Integral non-linearity is not as good as expected.

- There are significant INL differences channel to channel.

- Chip to chip differences are smaller than channel to channel differences.

- Response is stable (doesn't change day to day or month to month).

- INL can be corrected with a simple polynomial fit.

- Source of non-linearity appears to be capacitor dielectric absorption.

- See Carl Grace's slides.

- Since the non-linearity can be corrected, no redesign is planned.

🔆 Fermilab 🖂 💦

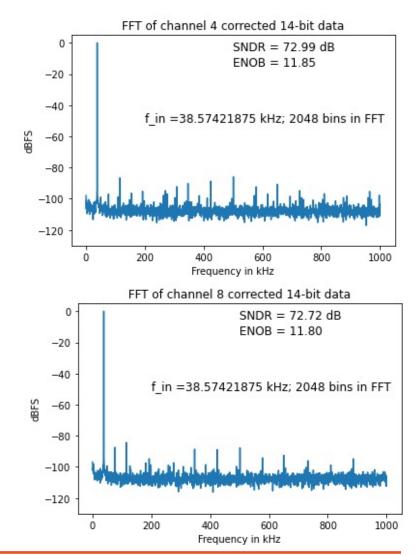

# **Dynamic Linearity (SNDR/ENOB)**

- After correction with a polynomial, dynamic linearity is very good, with little channel to channel variation.

- Our current measurements appear to be limited by our test setup and the linearity of our waveform generators.

- The measured ENOB is above 11 for input sinusoidal frequency up to 227 kHz

### Summary

COLDADC\_P2 meets DUNE requirements for both HD & VD TPCs.

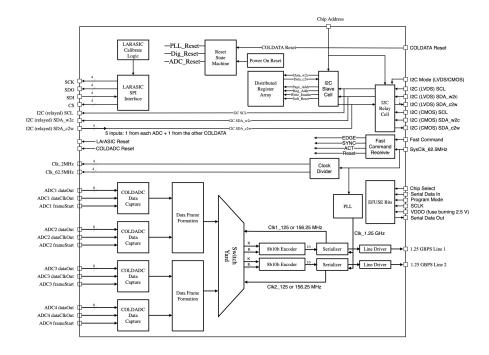

### **COLDATA Controller/Data Concentrator**

- The first full prototype of COLDATA (COLDATA\_P2) was fully functional and is being used in systems tests.

- Minor bug fixes and a handful of new features were added for the current version.

🔆 Fermilab 🖂 💦

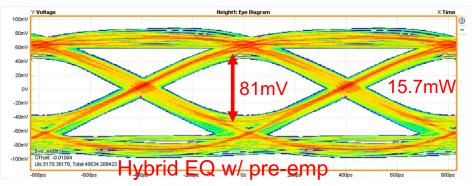

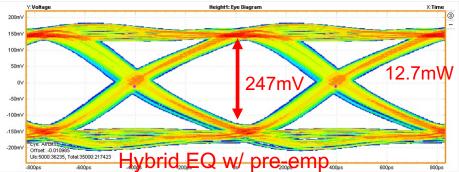

# Ability to drive long cables

- The 1.25 Gbps hybrid-mode line driver is designed with current-mode transmitter equalization and voltage-mode preemphasis to drive 25-35 meter long twinaxial cables. The current-mode transmitter equalization circuit uses a finite impulse response (FIR) filter to distort the data pulse and compensate for the large frequency-dependent signal loss over a long twinax cable with low dynamic power consumption. The voltage-mode main driver and preemphasis circuit uses source-seriesterminated (SST) output stages to provide a large output voltage swing and low static power consumption.

- The eye diagrams on the right were obtained from COLDATA\_P2.

#### Warm 35m

#### Eye diagrams for PRBS7

### New for COLDATA\_P3

- PLL

- Now locks to 62.5 MHz system clock instead of dedicated 40 MHz clock.

- 1<sup>st</sup> version failed to lock at room temp with 1.1V bias (required 1.17V at RT; locked at 1.1V when cold).

- I2C relay

- 1<sup>st</sup> command to a new I2C address failed if it was a read

- Misc:

- Timestamp now counts 62.5 MHz clock ticks and has been extended to 15 bits (16<sup>th</sup> bit used to indicate test pulse issued to LArASIC)

🛟 Fermilab 🖂 💦

- Registers used to control time between LArASIC pulse edges extended to 16 bits

- Additional functionality

- Added a means to determine cable delay from WIB

- Added 3 more general purpose I/O pads & made all 5 of these bits tri-stateable

- Procedure to read EFUSE registers made more user friendly

- Modified data frame structure to make WIB microcoding easier

## **COLDATA\_P3 Testing**

- PLL locks at nominal bias voltage both at room temp and cold.

- I2C bug was fixed.

- Almost all new features work as intended.

- Two minor bugs found:

- All 5 general purpose I/O bits are shorted together

- The LArASIC SPI clock is very asymmetric (still can program LArASICs)

- These will be corrected before submission of engineering run

### Summary

- COLDATA\_P3 meets DUNE requirements for both HD & VD TPCs.

- The 5 general purpose I/O bits of COLDATA\_P4 will allow more features to be included in the FEMB.

### **A Final Comment**

- No change will be required to any of the ASICs in order for them to be used for the vertical drift detector.

- COLDATA can drive 35 m long twinax cables.

- The only thing we need to verify is that the signal integrity is maintained if a patch panel is included in the signal path.

- Shanshan will discuss this in the next presentation.