# **Radiation tolerance of ITkPixVI**

Maria Mironova on behalf of the RD53 collaboration

The 30<sup>th</sup> International Workshop on Vertex Detectors 28/09/2021

# Introduction

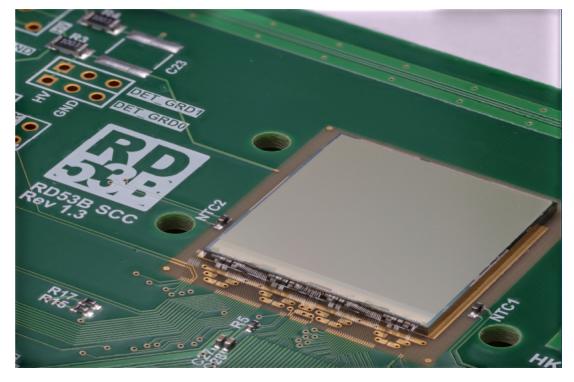

- Readout chips designed by RD53 collaboration @ CERN

- First joint ATLAS and CMS prototype: **RD53A**

- Based on this, development of improved **RD53B** chip

- Common design produced in two versions:

- ATLAS ITkPixVI

- CMS CROC

- Main difference between ATLAS and CMS chip in size and type of analog front-end used (differential for ATLAS, linear for CMS)

- ATLAS ITk pixel detector is expected to receive doses of up to I Grad during the lifetime of HL-LHC

- Need to understand the impact of TID damage on the readout chips

- $\rightarrow$  Irradiate chip prototypes using X-ray systems

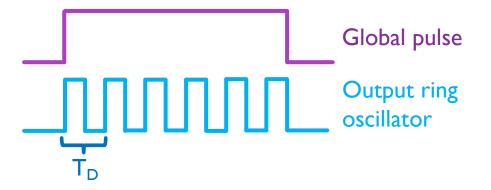

# Ring oscillators in ITkPixVI

- ITkPixVI includes ring oscillators for radiation testing (located at the chip bottom)

- 42 ring oscillators made with different logic cells and different transistor sizes (strength 0, 1 and 4)

- Oscillator drives a 12-bit counter, enabled for a given period of time

#### $\rightarrow$ Calculate frequency f or delay T<sub>D</sub>=1/(N · f)

- During irradiation ring oscillator frequency decreases

- → Characterise radiation damage on the different kinds of logic cells

### $\rightarrow$ Proxy to understand gate delay

- $\rightarrow$  too large delay will cause digital logic to fail

- $\rightarrow$  > 200% increase in delay shows issues in simulation

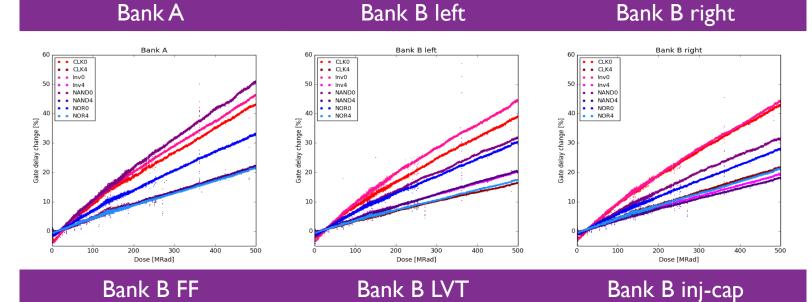

| Group                  | Туреѕ                                                                   | #     |

|------------------------|-------------------------------------------------------------------------|-------|

| A<br>B left<br>B right | CLK, Inv, NAND, NOR<br>Driving strength 0 and 4<br>w/ different lengths | 3 x 8 |

| B FF                   | Scan/standard/neg-edge<br>D-flip-flop                                   | 6     |

| B LVT                  | LVT inverter & 4-input NAND<br>Strengths 0 and 4                        | 4     |

| B CAPA                 | Injection-capacitor loaded<br>4-input NAND                              | 8     |

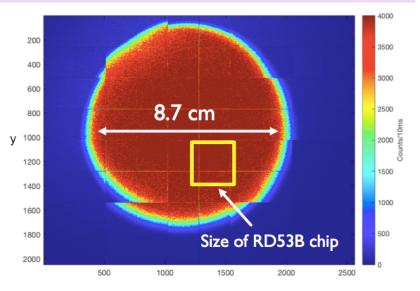

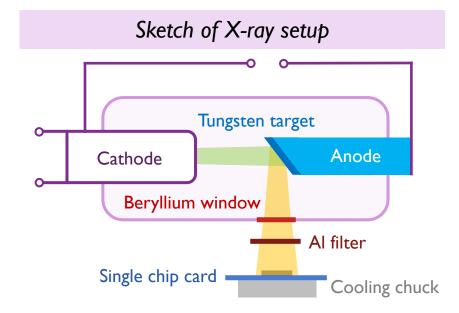

# Irradiation setup

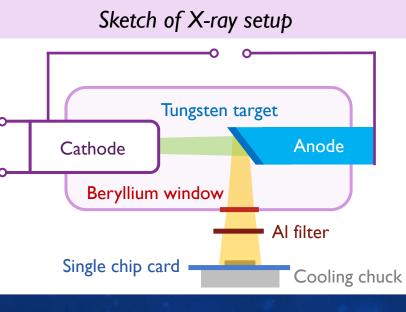

- Irradiation setup at Oxford:

- X-ray tube with a tungsten target

- Peak X-ray flux at 50kV, 60 mA (3kW)

- Dose rate calibration using calibrated diodes → consistent with different sites

- Common irradiation procedure:

- Characterise chip before irradiation (ring oscillators, threshold distributions)

- During irradiation, read the ring oscillator frequency (at least every 0.1 Mrad)

- Otherwise, keep the chip busy by running digital scans

- Keep the chip cold (-10 ± 1 C)

- Monitor (at least) the digital voltage (VDDD) and temperature

#### Beam spot 10 cm from the source

# Ring oscillators in ITkPixVI

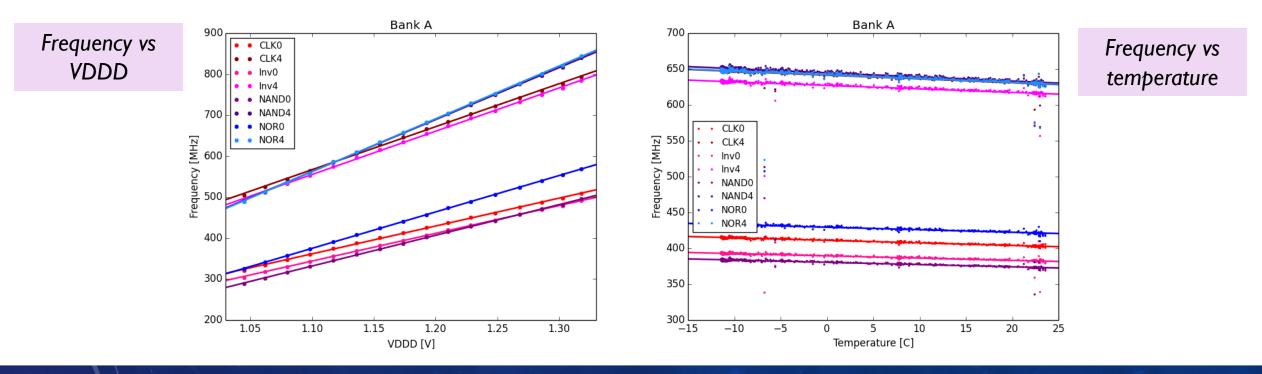

- Ring oscillators frequency depends on digital voltage (VDDD) and temperature

- Measurements before irradiation:

- Frequency vs VDDD: change by up to 200 MHz between 1.0 and 1.3 V → used to account for VDDD changes during irradiations

- Frequency vs temperature: change by up to 20 MHz

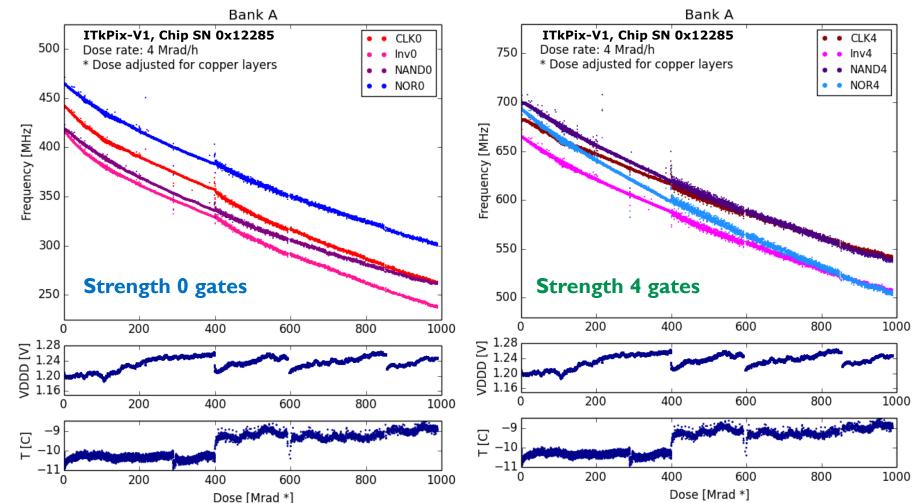

# High dose rate irradiations

- Several high dose rate irradiation campaigns performed

- E.g. with 4 Mrad/h @ Oxford

- Monitoring of VDDD and temperature

- No operational issues up to I Grad

- Expected decrease in ring oscillator frequencies

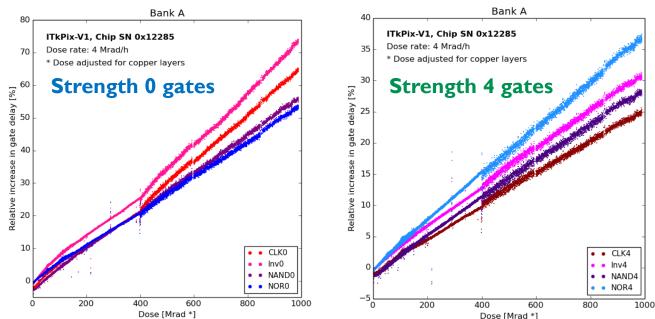

# High dose rate irradiations

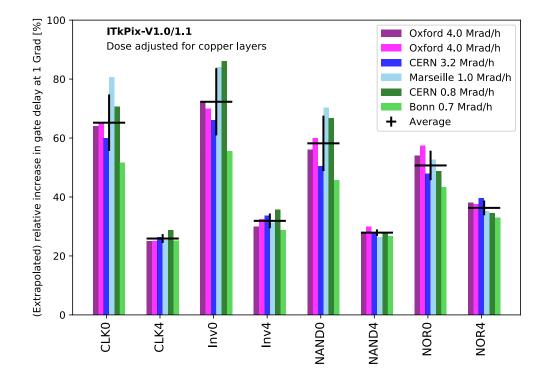

- Calculate relative increase in gate delay for each ring oscillator as  $T_D {=}\ 1/(N \cdot f)$

- At high dose rate:

- Increase for strength 0 gates up to 80% (→ not used in the chip)

- Increase for strength 4 gates up to 40%

- Comparison of high dose rate irradiations at different sites

- → Good agreement, especially for strength 4 gates

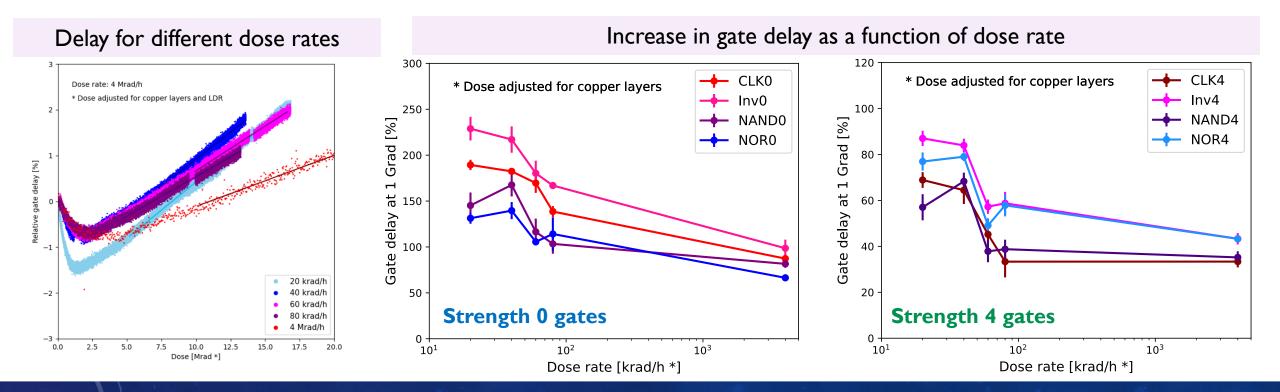

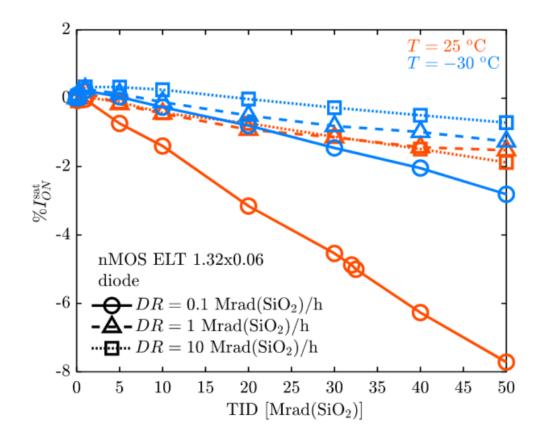

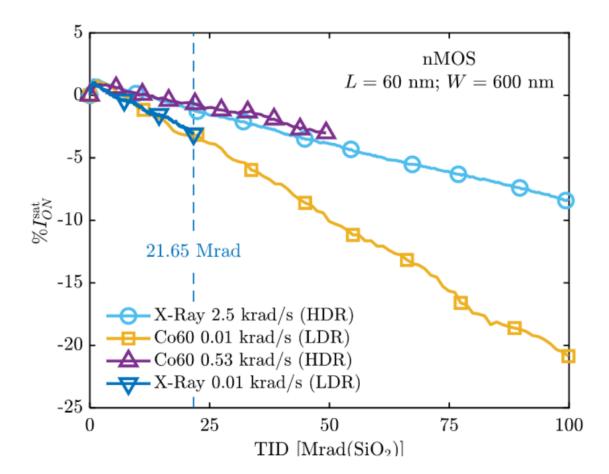

### Low dose rate effects

- Impact of low dose rate (<100 krad/h) effects studied for low total doses in X-ray setups

- Damage increases for low dose rate by approximately factor 2 (assuming optimistic linear extrapolation) → effect stronger for strength 0 gates

- Trend flattens out at both low and high dose rates

#### Maria Mironova

28/09/2021

### Low dose rate delay degradation

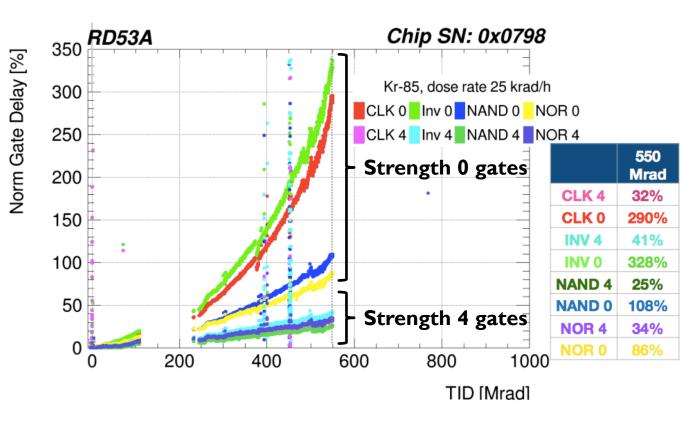

- Measurements with SLIPPER (SLow Irradiation of Phase-2 PixEl Readout)

- Low dose rate irradiation of RD53A chip with Kr-85 at 25 krad/h

- $\rightarrow$  collected 550 Mrad of total dose over 3 years

- Delay degradation seen to be non-linear with for strength 0 gates

- → Linear scaling of HDR results seems to not be appropriate

- $\rightarrow$  Further study needed

- $\rightarrow$  Additional SLIPPER setups planned with RD53B

- Note: Strength 0 gates not used in RD53B logic

Results from Aleksandra Dimitrevska

# Analog performance

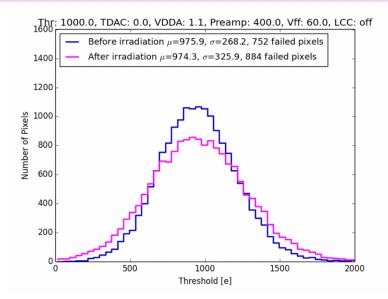

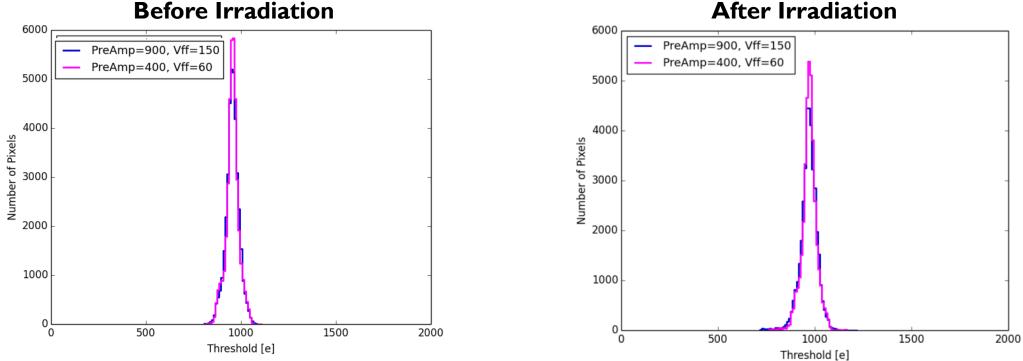

- Analog performance of ITkPixVI after irradiation to I Grad

- Performed threshold scans after irradiation for a large range of parameters  $\rightarrow$  to compare with measurements before irradiation

- Number of failed pixels <5% for most parameter settings

- $\rightarrow$ Increase in width of threshold distributions

- Chip operational for most settings after irradiation to I Grad

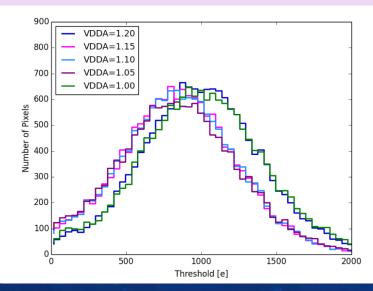

- At chip settings given by simulations, decrease analog voltage (VDDA)

- RD53A stopped working at VDDA < 1.1 V</li>

$\rightarrow$  Even after irradiation ITkPixVI is operational down to 1.0V

#### Threshold scan before and after irradiation

#### VDDA study after irradiation

# Conclusions

- Presented irradiation results on the latest ATLAS readout chip prototype

- High dose rate irradiation results

- Several HDR irradiations performed up to I Grad, gate delay increase of up to 40% observed for strength 4 gates

- Low dose rate irradiation results

- Several LDR irradiations performed at different dose rates, increase in damage at low dose rate observed

- $\rightarrow$  Non-linear behaviour of delay degradation at high total dose rates

- Analog FE performance during and after irradiation

No significant issues with AFE after I Grad

Most aspects of the ITkPixVI chip tested and performing well up to total doses of I Grad

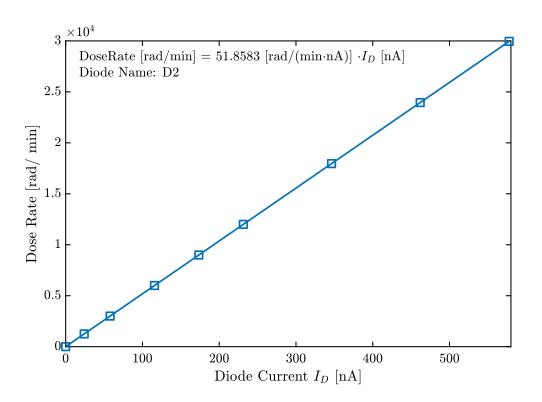

# **Calibration setup**

- X-ray tube with tungsten target, operated at 40kV

- 150  $\mu$ m Al filter for to remove low-energy components

- Dose rate calibration using AXUVHS5 calibrated pin diodes

- Properties:

- Sensitive depth: 50 µm

- Sensitive area: I mm<sup>2</sup>

- Biasing voltage: 50 V

- Measures current which can be used to convert into  $SiO_2$  equivalent dose

Example calibration curve for AXUVHS5 diode

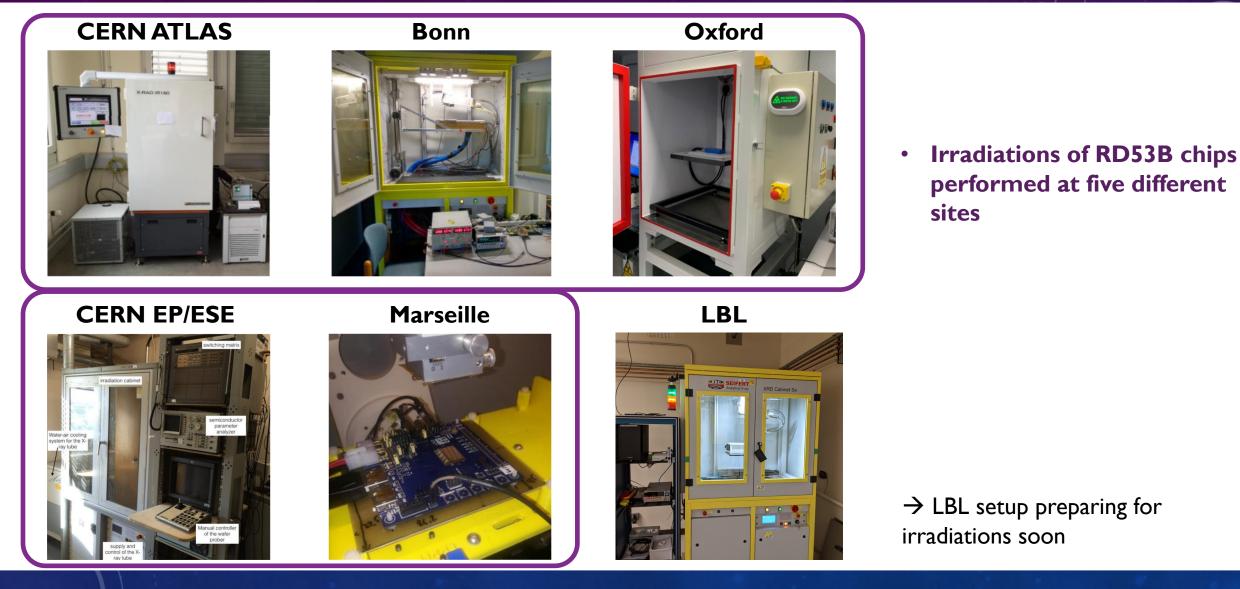

### Irradiation sites

#### X-ray calibration meeting (Link)

Maria Mironova

#### 28/09/2021

# **Common irradiation procedures**

- Decided on common configuration for X-ray setups involved in irradiations of ITkPixV1 (40 kV, 150µm Aluminium filter)

- Dose rate calibration using calibrated diodes (provided by CERN F. Faccio et al.)

- Common calibration procedure described in document <u>here</u>

- Add additional 20% correction factor to delivered dose due to absorption in the copper layers in the chip (<u>backup</u>)

- Common irradiation procedure:

- Perform pre-irradiation measurements of ring oscillators and analog front-end

- During irradiation, read the ring oscillator frequency (at least every 0.1 Mrad)

- Otherwise, keep the chip busy by running digital scans

- Keep the chip cold (-10 ± 1 C)

- Monitor (at least) the VDDD voltage and temperature

#### Calibration diode

# **Analog FE after irradiation - Tuning**

- Tune and measure threshold at two points with target threshold 1000:

- Preamp=900 + Vff=150 and Preamp=400 + Vff=60

- Other parameters: VDDA= 1.2, LCC off

- $\rightarrow$  Chip still well tuneable after irradiation to 1 Grad

After Irradiation

28/09/2021

#### Maria Mironova

Pixels

Number

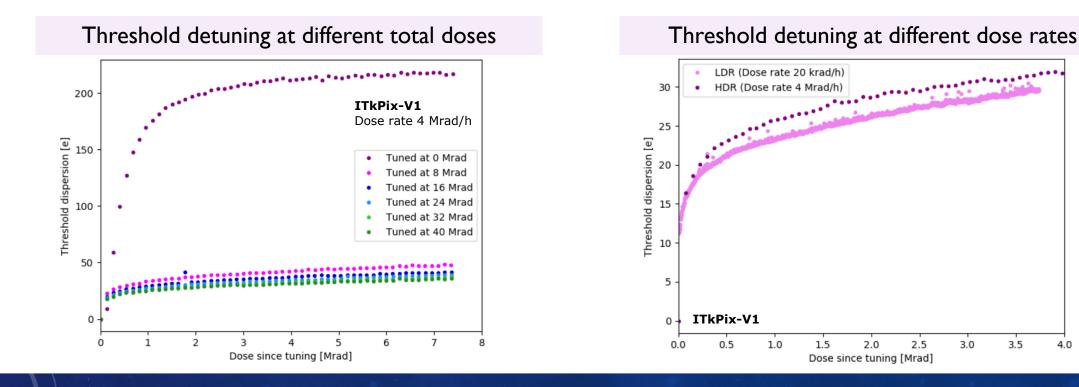

# **Analog front-end during irradiation**

- Characterise damage to analog front-end (AFE) during irradiation ٠

- Calculate how quickly a tuned threshold distribution disperses with irradiation ٠

- $\rightarrow$  very quick dispersion at the beginning of the irradiation, afterwards thresholds disperse much slower

- $\rightarrow$  most damage to the AFE in the first few Mrad

- No significant difference between low and high dose rate  $\rightarrow$  expected due to larger transistor size ٠

2.5

28/09/2021

3.0

3.5

4.0

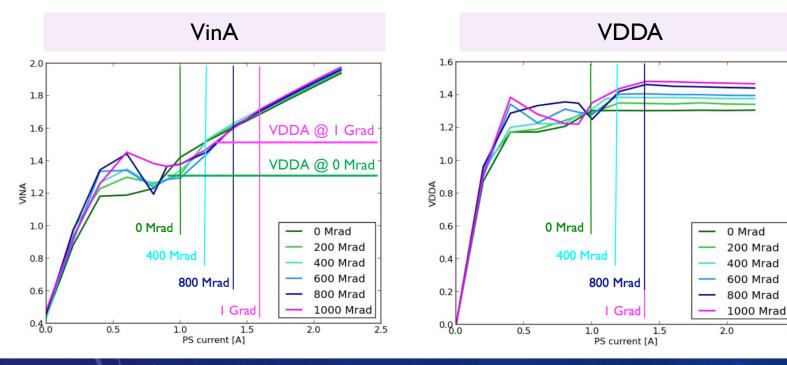

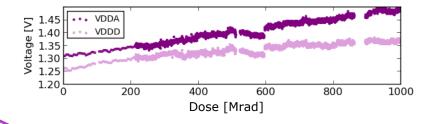

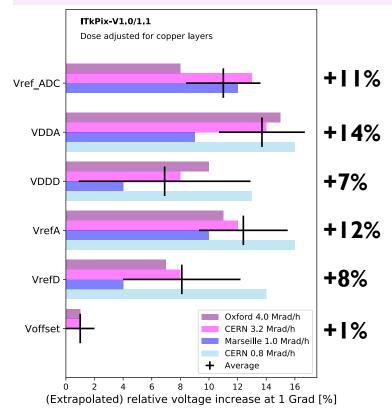

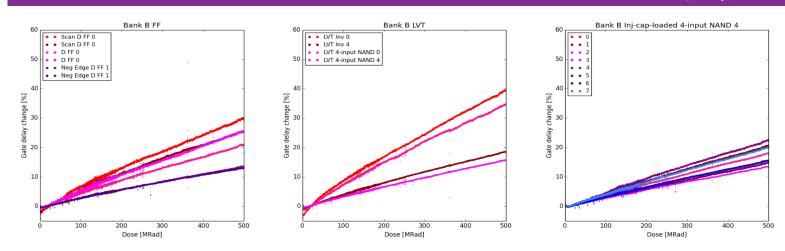

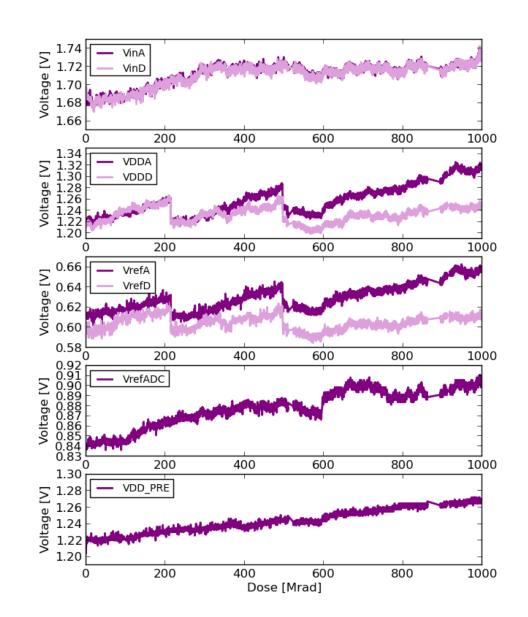

# **SLDO** irradiation

- Drift of different chip reference voltages observed with irradiation (up, to +15%)

- Irradiation campaigns focusing on SLDO behavior performed

- No start-up issues observed after irradiation to I Grad

- Later start-up due to shift in untrimmed VDDA value

VDDA/VDDD with irradiation

#### Increase of voltages after I Grad

#### Maria Mironova

2.5

### Low dose rate expectations

F. Faccio and G. Borghello

# Extrapolation of gate delay at LDR

- Use the ratios calculated previously and HDR results

- $\rightarrow$  calculate expected ring oscillator delay degradation at 500 Mrad of LDR

- Largest for NAND 0 (50%) (but just for Bank A)

- Inv 0 (~45%) and CLK 0 (~40%) consistent between Bank A and Bank B

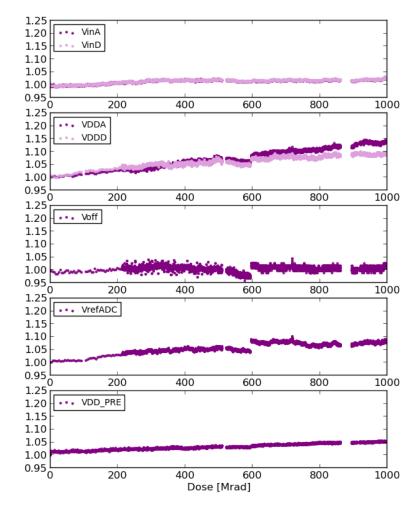

### **Monitored voltages**

- Main focus of campaign on voltages and currents relevant to chip operation

- Chip voltages measured from the SCC pins using the AnaMon card

- VDDA and VDDD were regularly trimmed to be around 1.2V

- For both Vref and VDD the analog voltage seems to increase faster → consistent with what was observed in measurements at other sites

- In comparison, VDD\_PRE stays fairly constant

### **Monitored voltages**

#### **Absolute values**

#### **Relative change**

- Check voltages without change in trimbit settings

- VDDA increases more than VDDD

- Vofs stays very constant

•

Relative increases over 1 Grad:

| Voltage  | Increase |

|----------|----------|

| VinA/D   | + 2 %    |

| VDDA     | + 15 %   |

| VDDD     | + 10 %   |

| V_ofs    | < 1%     |

| Vref_ADC | + 8%     |

| VDD_PRE  | + 5%     |

28/09/2021

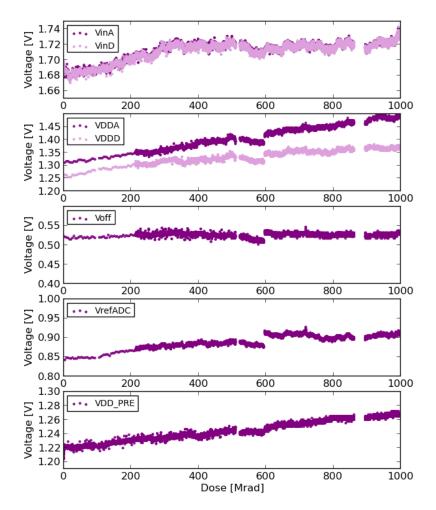

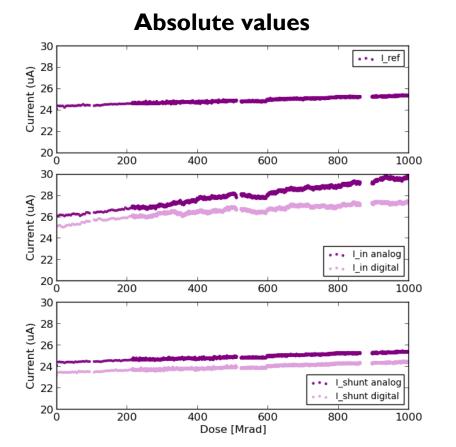

### **Monitored currents**

#### **Relative change** 1.15 ••• I\_ref 1.10 1.05 1.00 0.95 L 0 200 400 600 800 1000 1.15 1.10 1.05 1.00 I in analog I in digital 0.95 L 200 800 400 600 1000 1.15 ••• I\_shunt analog I shunt digital 1.10 || 1.05 1.00 0.95 └─ 0 800 200 400 600 1000 Dose [Mrad]

# Monitored currents from the IMUX

•

• Relative changes over I Grad:

| Current                 | Increase |  |

|-------------------------|----------|--|

| Iref                    | + 4 %    |  |

| l <sub>in</sub> analog  | + 14 %   |  |

| l <sub>in</sub> digital | +9%      |  |

| I <sub>shunt</sub> A/D  | + 5%     |  |