The 30<sup>th</sup> International Workshop on Vertex Detectors VIRTUAL (Oxford) 27-30 September 2021

## Status of the TimeSPOT project results on silicon sensors and electronics 30/9/2021 **Adriano Lai**

## For the TimeSPOT team

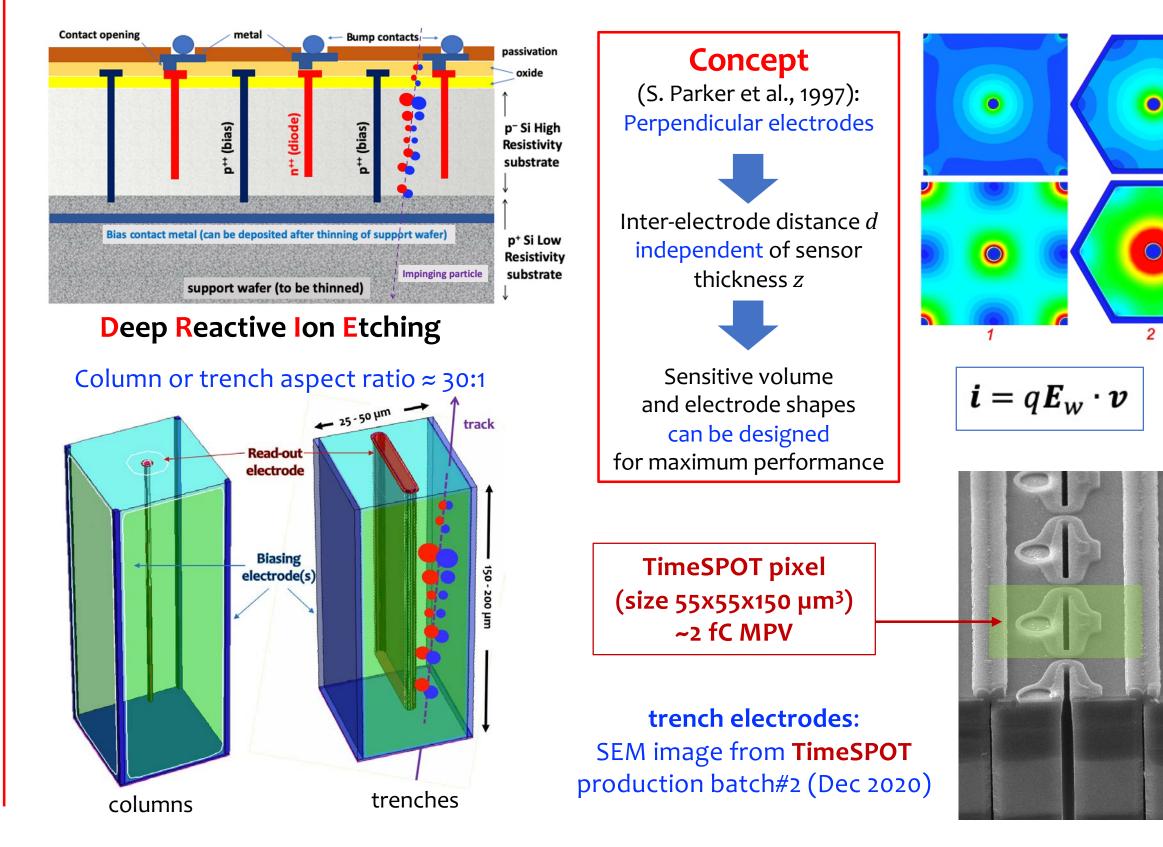

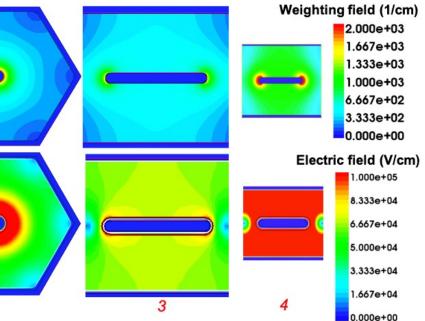

## 3D silicon sensors: a geometric approach

### High and uniform E field

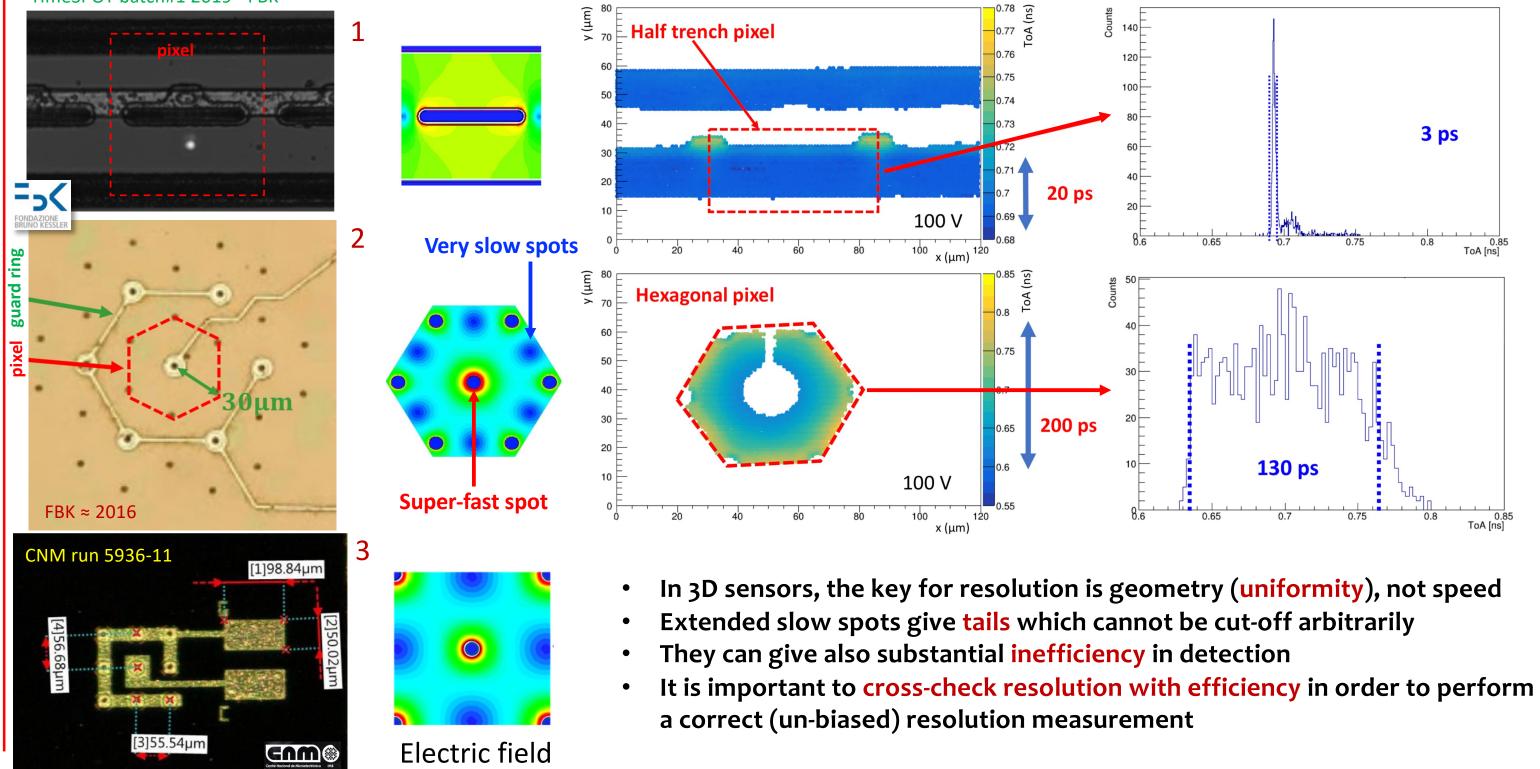

## Tails, efficiency and time resolution (1)

Experimental comparison with other geometries

TimeSPOT batch#1 2019 - FBK

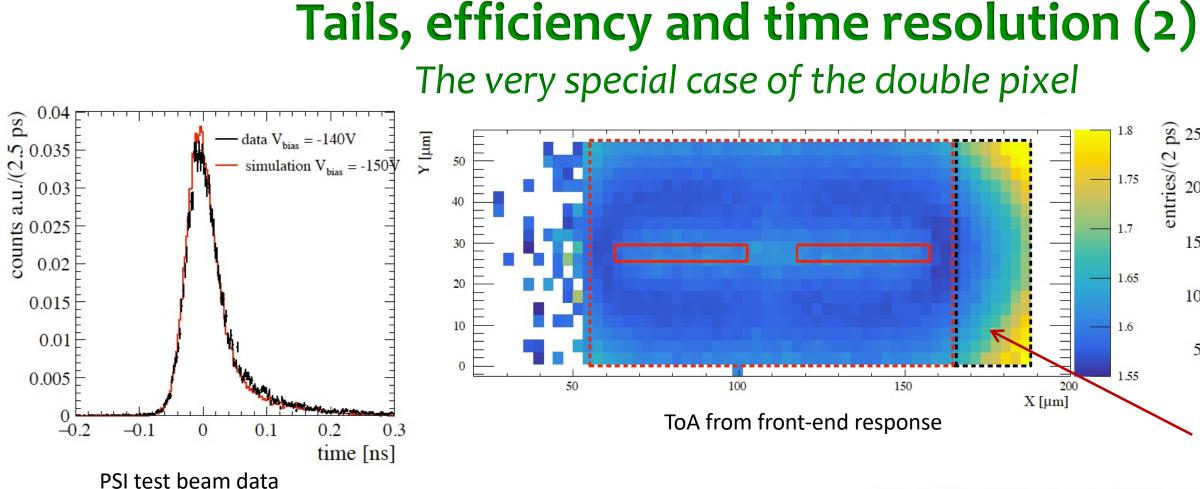

Tails have been studied with very accurate pixel modeling, from the ionization process to the front-end output.

A clear assignation of the tail contribution was done to the (out)side region of the pixel (outside the nominal pixel area in this particular case).

### Double pixel picture

### Details of this analysis on:

D. Brundu et al., Accurate modelling of 3D-trench silicon sensor with enhanced timing performance and comparison with test beam measurements JINST 2021 16 P09028.

### **3D-trench silicon sensors**

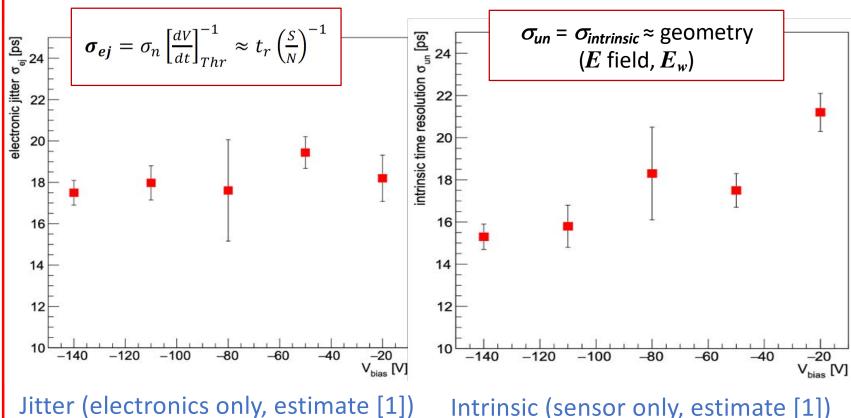

[1] L. Anderlini et al., Intrinsic time resolution of 3D-trench silicon pixels for charged particle detection. JINST 15, P09029, 2020. [2] D. Brundu et al., Accurate modelling of 3D-trench silicon sensor with enhanced timing performance and comparison with test beam measurements. JINST 16, P09028, 2021.

$\sigma_t \cong \sqrt{\sigma_{un}^2 + \sigma_{ej}^2}$

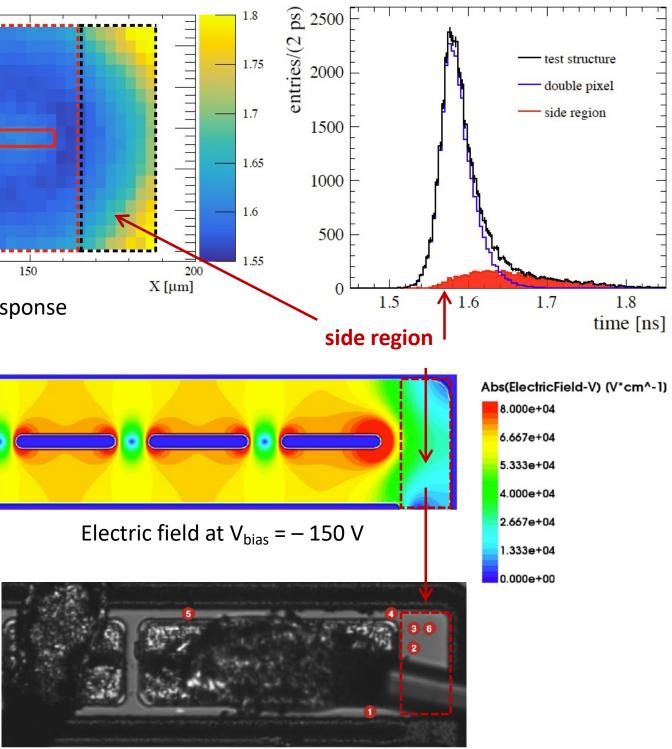

Double pixel  $55x110 \ \mu m^2$

### Total $\sigma_{t}$ is obtainable as the quadrature sum of the two main contributions

$\sigma_t$  is dominated by the contribution of the front-end electronics  $\sigma_{ei}$ This estimate is pessimistic especially for the intrinsic resolution as includes inextricable systematic effects (time correlations, extrinsic noise).

### Very accurate simulations give more unbalanced indications [2]

| Simulation [2] |                                |                           | Measurement [2] |                  |

|----------------|--------------------------------|---------------------------|-----------------|------------------|

| $V_{bias}[V]$  | $\sigma_{ m intrinsic}[ m ps]$ | $\sigma_{ m t}[{\sf ps}]$ | $V_{bias}[V]$   | $\sigma_{t}[ps]$ |

| -50            | 9.6 ± 0.1                      | 18.9 ± 0.2                | -50             | 20.7 ± 0.3       |

| -100           | 8.0 ± 0.1                      | 16.7 ± 0.2                | -110            | 19.8 ± 0.2       |

| -150           | 7.0 ± 0.1                      | 16.3 ± 0.2                | -140            | 19.0 ± 0.2       |

Ż

### room temperature

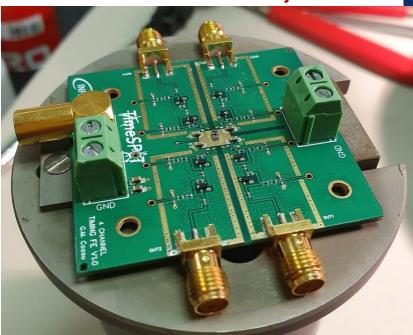

### **3D-trench pixel readout and custom electronics (ASIC)** Max obtainable performance (TimeSPOT sensor) vs ASIC specifications (e.g., LHCb)

**3D-sensor specs:**  $\sigma_{ei}$  < **15 ps**

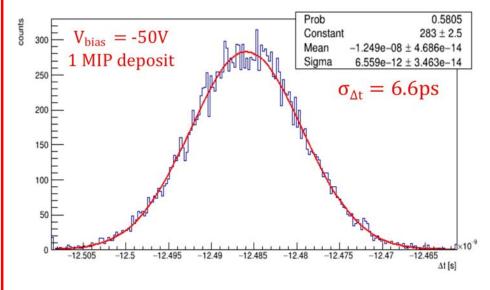

WB Si-Ge input stages  $t_r \approx 100 \text{ ps}$ Measured  $\sigma_{ei}$  ~ 6.6 ps

### LHCb-U<sub>2</sub> specs

| Requirement                                                             | scenario ${\cal S}_A$ | scenario ${\cal S}_B$ |

|-------------------------------------------------------------------------|-----------------------|-----------------------|

| Pixel pitch [µm]                                                        | $\leq 55$             | $\leq 42$             |

| Lifetime fluence $[1 \times 10^{16} 1 \text{ MeV } n_{eq}/\text{cm}^2]$ | > 6                   | > 1                   |

| TID lifetime [MGy]                                                      | > 28                  | > 5                   |

| Sensor Timestamp per hit [ps]                                           | $\leq 35$             | $\leq 35$             |

| ASIC Timestamp per hit [ps]                                             | $\leq 35$             | $\leq 35$             |

| Hit Efficiency [%]                                                      | $\geq 99$             | $\geq 99$             |

| Power per pixel $[\mu W]$                                               | $\leq 23$             | $\leq 14$             |

| Pixel rate hottest pixel [kHz]                                          | > 350                 | > 40                  |

| Max discharge time [ns]                                                 | < 29                  | < 250                 |

| Bandwidth per ASIC of 2 $\rm cm^2~[Gb/s]$                               | > 250                 | > 94                  |

- High rate (~ 1 TDC per pixel)

### The TimeSPOT ASIC designer's challenge:

What is the best time resolution we manage to reach (15 ps <  $\sigma_{ei}$  < 50 ps) integrating 1 TDC per pixel (55x55 µm<sup>2</sup>) and possibly keeping the consumption in the range of 20-30  $\mu$ W/pixel ?

LHCbU2 specs from physics needs. U2 FTDR preliminary (2020). 50 ps per hit on the full chain (sensor + AFE + TDC) Low consumption < 1.5 W/cm<sup>2</sup> (power dissipation issues)

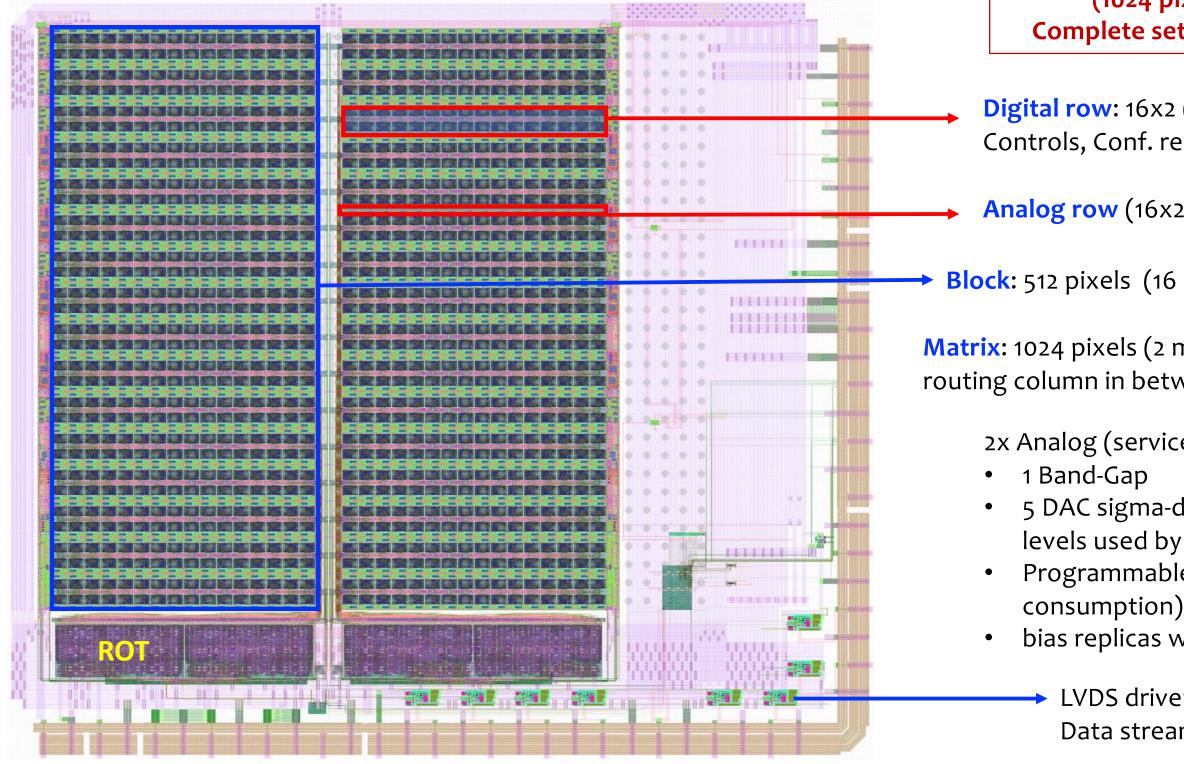

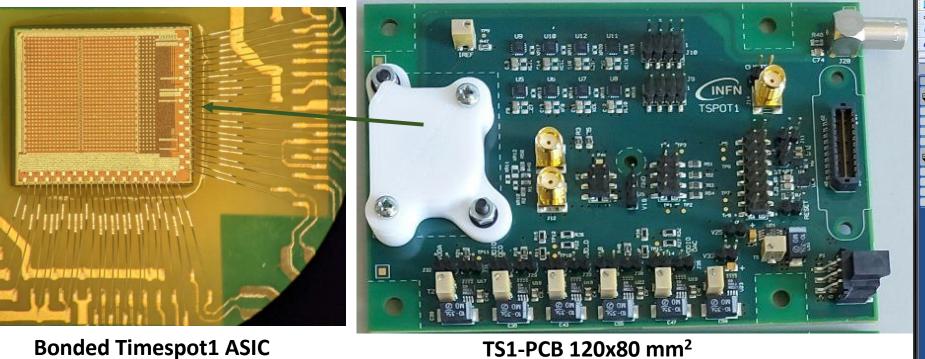

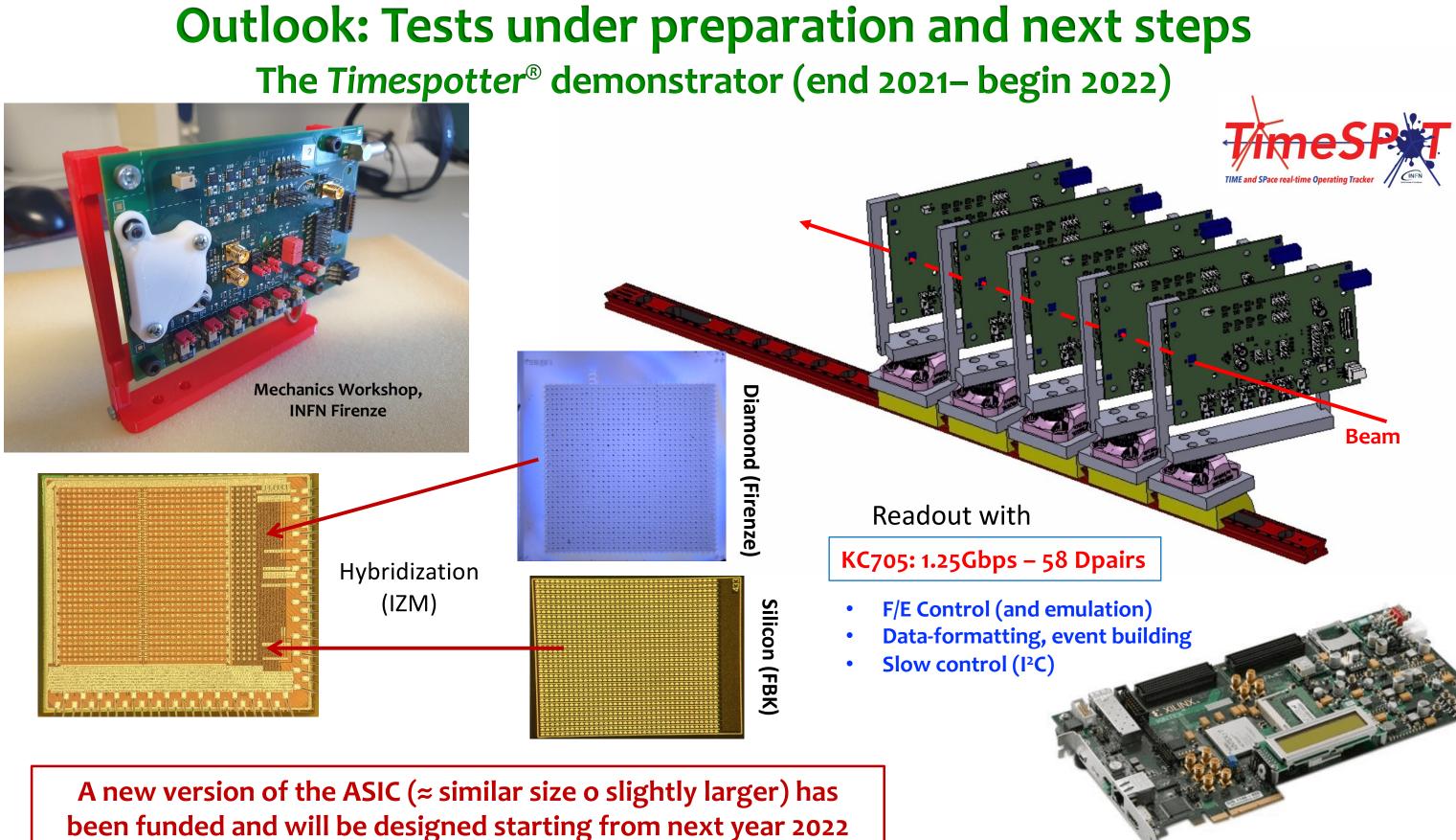

The pixel matrix has no dead area and is 4-side buttable (when using TSV): reduced pixel pitch and RDL to sensor

**Reduced size** (1024 pixels, 6 mm<sup>2</sup>), **Complete set of functionalities**

Digital row: 16x2 (mirrored) TDC + Controls, Conf. registers, I<sup>2</sup>C I/F)

**Analog row** (16x2 mirrored AFE)

Block: 512 pixels (16 double rows of 32 pixels)

Matrix: 1024 pixels (2 mirrored blocks + data routing column in between. Can host TSV)

> 2x Analog (service) columns. Each: 5 DAC sigma-delta (producing analog levels used by pixels) Programmable bias cell (for power

bias replicas with source followers.

LVDS driver 8 x 1.28 Gbps Data stream is highly pad limited

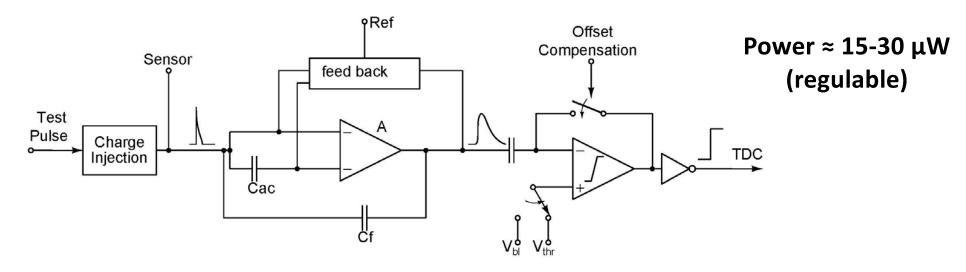

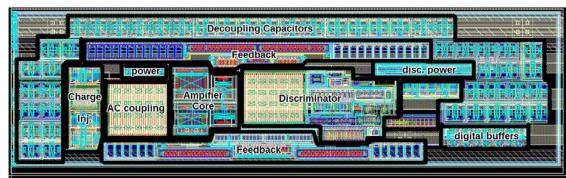

## **Pixel: Analog Front End and TDC**

**Inverter core amplifier with double Krummenacher feedback** Leading edge discriminator with discrete-time Offset Compensation (OC)

High resolution – "low" consumption TDC based on DCO and Vernier architecture

All digital, fully synthesizable architecture (standard cells)

Maximum input signal TDC rate = 3 MHz 24 bits output word (ToA + ToT) serial @160 MHz Power depends on input rate  $\approx 20$  $\mu$ W (stand-by) – 175  $\mu$ W (3 MHz)

The TDC gives the phase of the signal wrt the master 40MHz clock The TDC and the counter use the same DCO-generated Clk (~1 GHz) **Clock is active during conversion only**

### 50x15 µm<sup>2</sup>

50x31.5 µm<sup>2</sup>

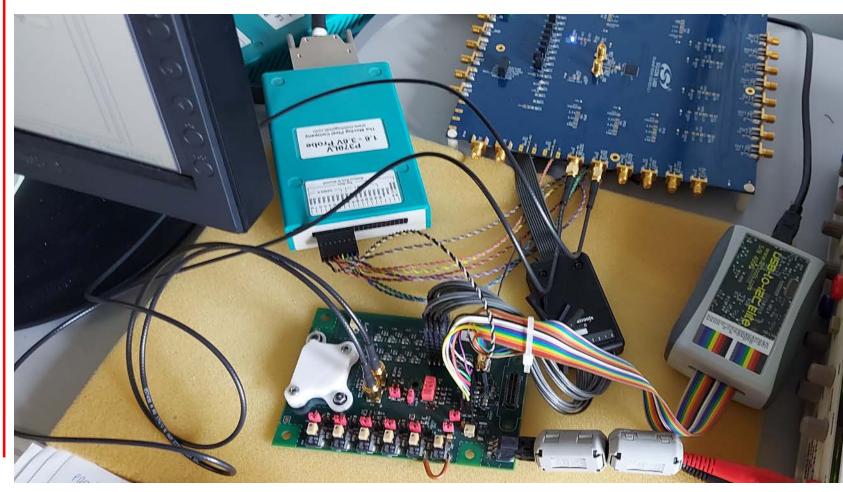

### Stand-alone tests (no sensor)

TS1-PCB 120x80 mm<sup>2</sup>

•

aaniVu: Col aniVu: CO(7 qniVu: C0/6 gniVu: COI aaniVu: Col ( gniVu: CO(3

gniVu: CO(2 gniVu: CO(1

- and analog+digital (AFE+TDC)

- tests) with dedicated DAQ

- Hybridization is on the way @ IZM

Tests via I<sup>2</sup>C I/F (slow: max pulse rate 10 kHz) and TLA

**Test pulses on individual channels**: digital only (TDC)

Nominal high-rate tests will be performed on hybridized device on the same PCB (laser pulses and particle beam

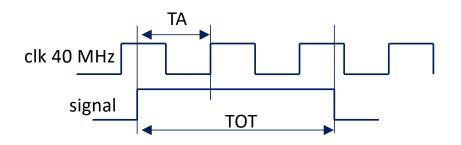

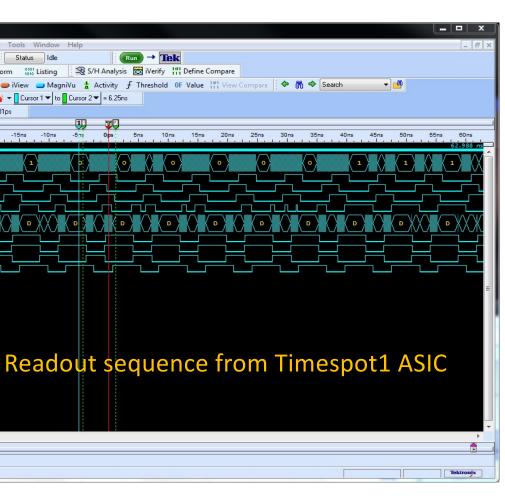

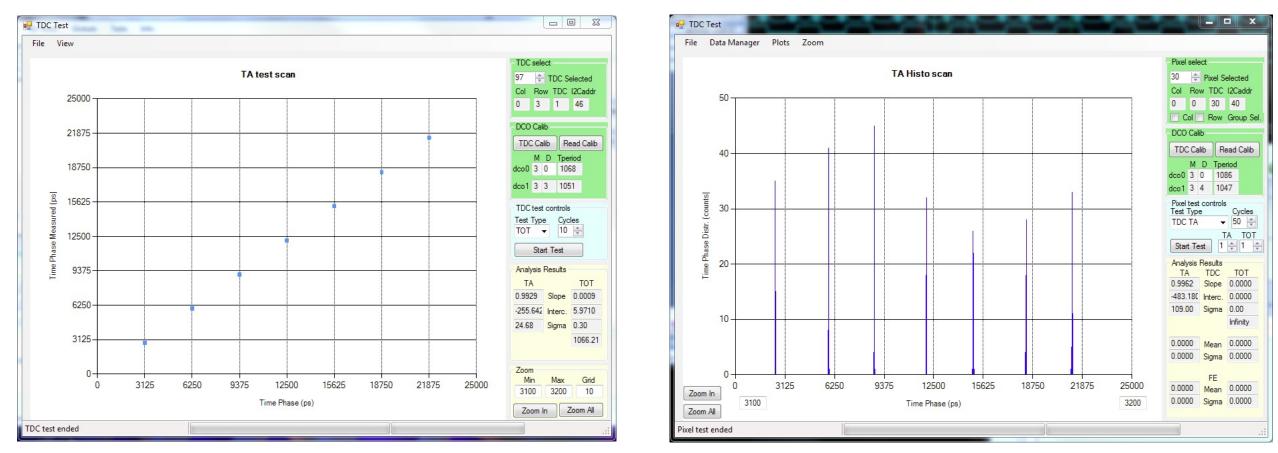

## **TDC operation and tests**

TA linearity on 7 phase positions

TA resolution on 7 phase positions

- **DCO** calibration ٠

- auto-tuning of the frequency difference  $\Delta f$  for Vernier mechanism (performed after each reset). It is possible to set 4 different  $\Delta f$ , fixing what we define the "Venier resolution"

- TA (Time of Arrival)

- phase difference between pulse rising edge and the 40 MHz reference clock 7 possible phase positions

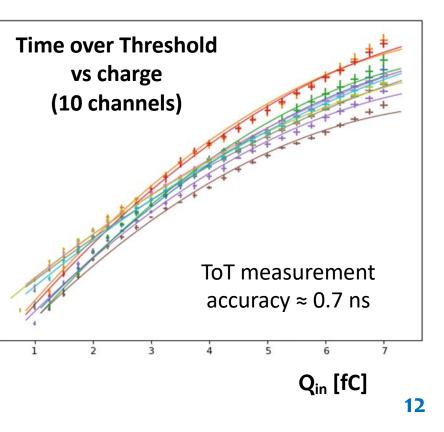

- **TOT (Time over Threshold)**

- 32 programmable digital pulse widths. The DCO-set frequency is used as clock for the ToT counters

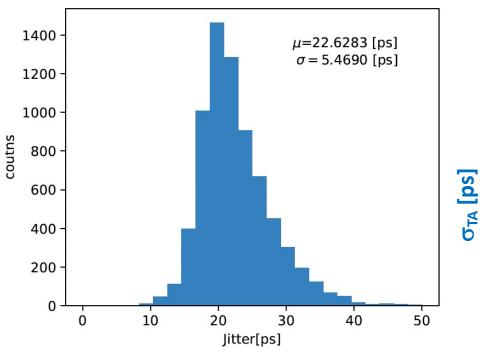

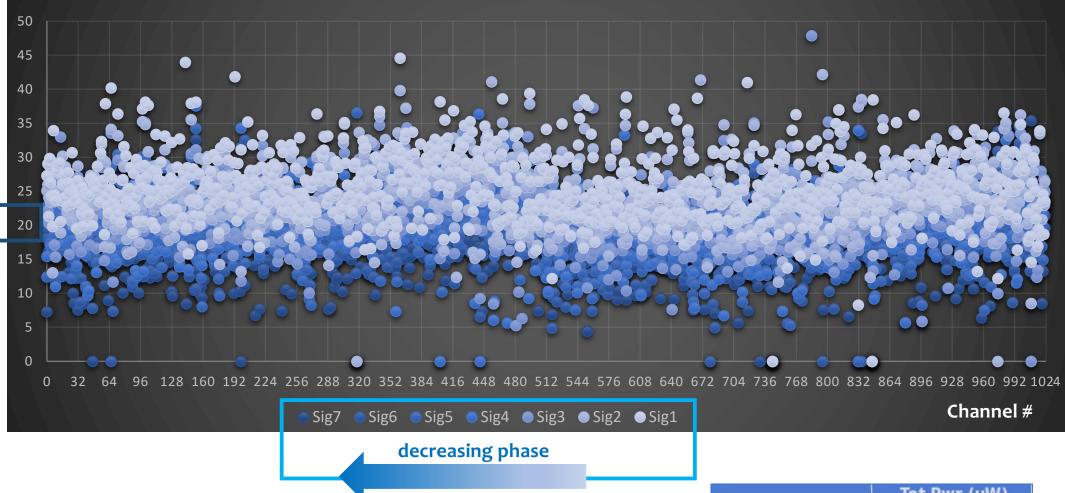

## **TDC test results: resolution on TA**

Distribution of the TA standard deviation across 1024 channels and 7 phases. Each point is computed from 100 repeated measurements.

- Average  $\sigma_{TA}$  much better than 50 ps:  $\sigma_{TA} = (22.6 \pm 5.5)$  ps

- "only" 14 dead channels out of 1024.

- The TDC design had 4 programmable resolution (Vernier gauges), but the best resolution is obtained with the coarsest one (Res = 3)

$\rightarrow$  The real limit to resolution appear to be the master clock jitter and/or power distribution

- Signal phase dependence (lower phases behave better)  $\rightarrow$  drift in Vernier operation

- Slight but evident dependence on geographical position of the channel (IR drop?)

### All phases, Res = 3, statistics of 100 samples per point

|             | Tot Pwr (uW) |

|-------------|--------------|

| IDLE        | 20.7         |

| Calibration | 552          |

| DAQ 3MHz    | 175          |

| DAQ 1MHz    | 69.3         |

| DAQ 500kHz  | 45.5         |

| DAQ 100kHz  | 25.7         |

Simulated TDC power consumption (to be tested at high input rate)

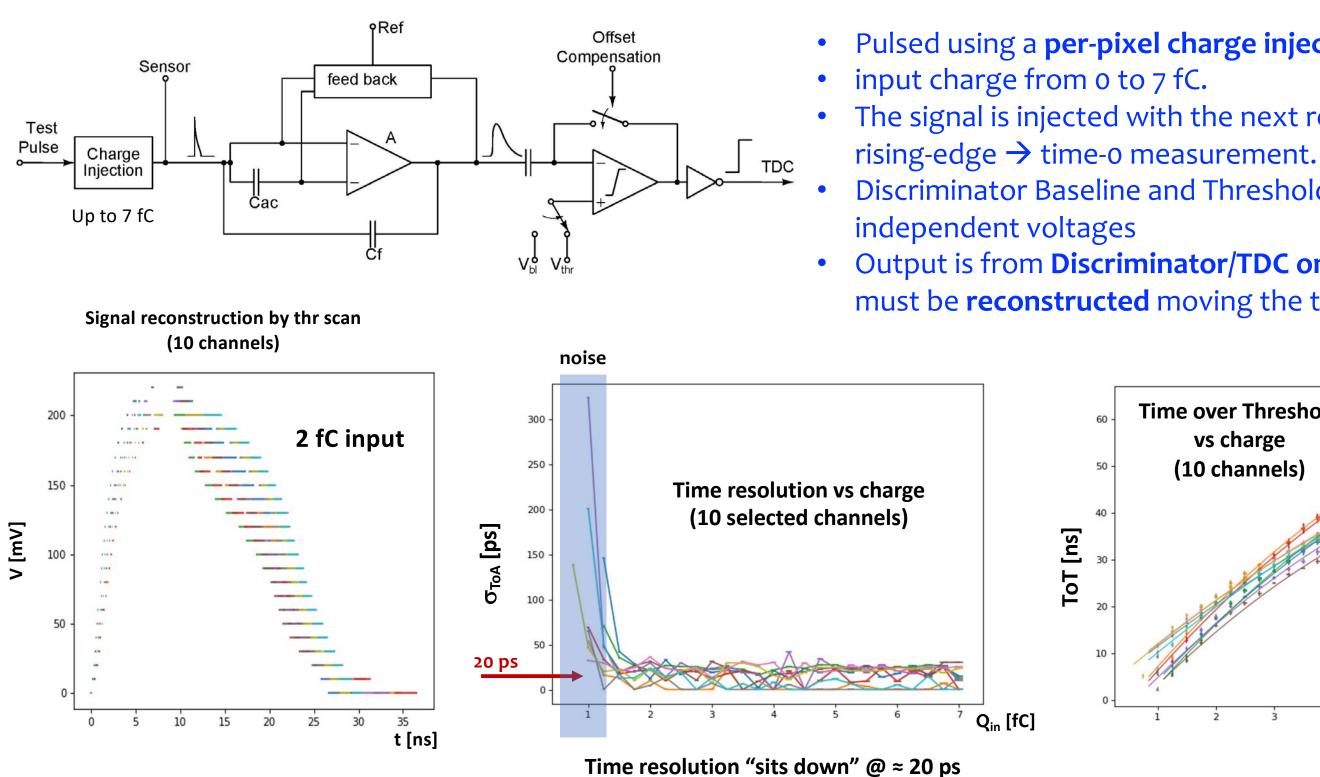

## **AFE tests**

Ż

Pulsed using a **per-pixel charge injection** capacitance The signal is injected with the next reference clock Discriminator Baseline and Threshold set via 2

### Output is from **Discriminator/TDC only** $\rightarrow$ CSA signal must be **reconstructed** moving the thresholds

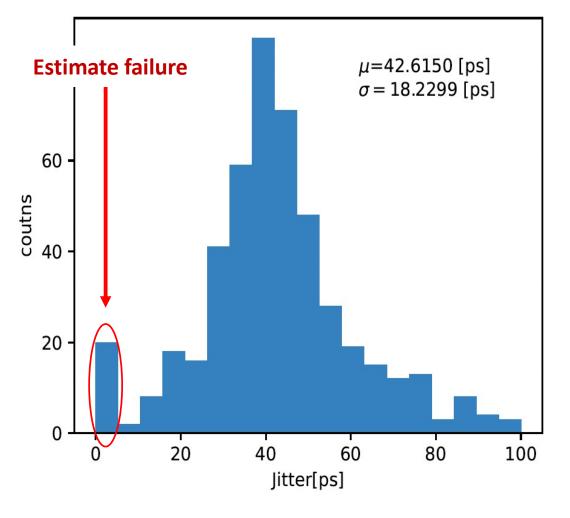

# AFE tests: time resolution $\sigma_{TA}(\sigma_{ei})$

Distribution of TA standard deviation across 512 channels. Input charge 2 fC (expected MIP). Each point computed from 100 repeated measurements. TDC contribution has been removed.

Power consumption =  $15 \mu W$

Preliminary

- AFE intrinsic time resolution CANNOT be measured directly ullet

- It must be **estimated** by subtracting out the TDC contribution:

$\begin{cases} \sqrt{\sigma_{FE}^2 - \sigma_{TDC}^2} & \text{if } \sigma_{FE} \ge \sigma_{TDC} \\ 0 & \text{if } \sigma_{FE} < \sigma_{TDC} \end{cases}$  $\sigma_{ej, estimate} = \left\{ \right.$

≈ 40 ps ??

- This produces a strong bias in the estimate

- However, the AFE appears to have a worst  $\sigma_{TA}$  than the TDC

- The performance appears much worse than expected from simulations (< 20 ps): Is there a limit in the circuit or anything else?

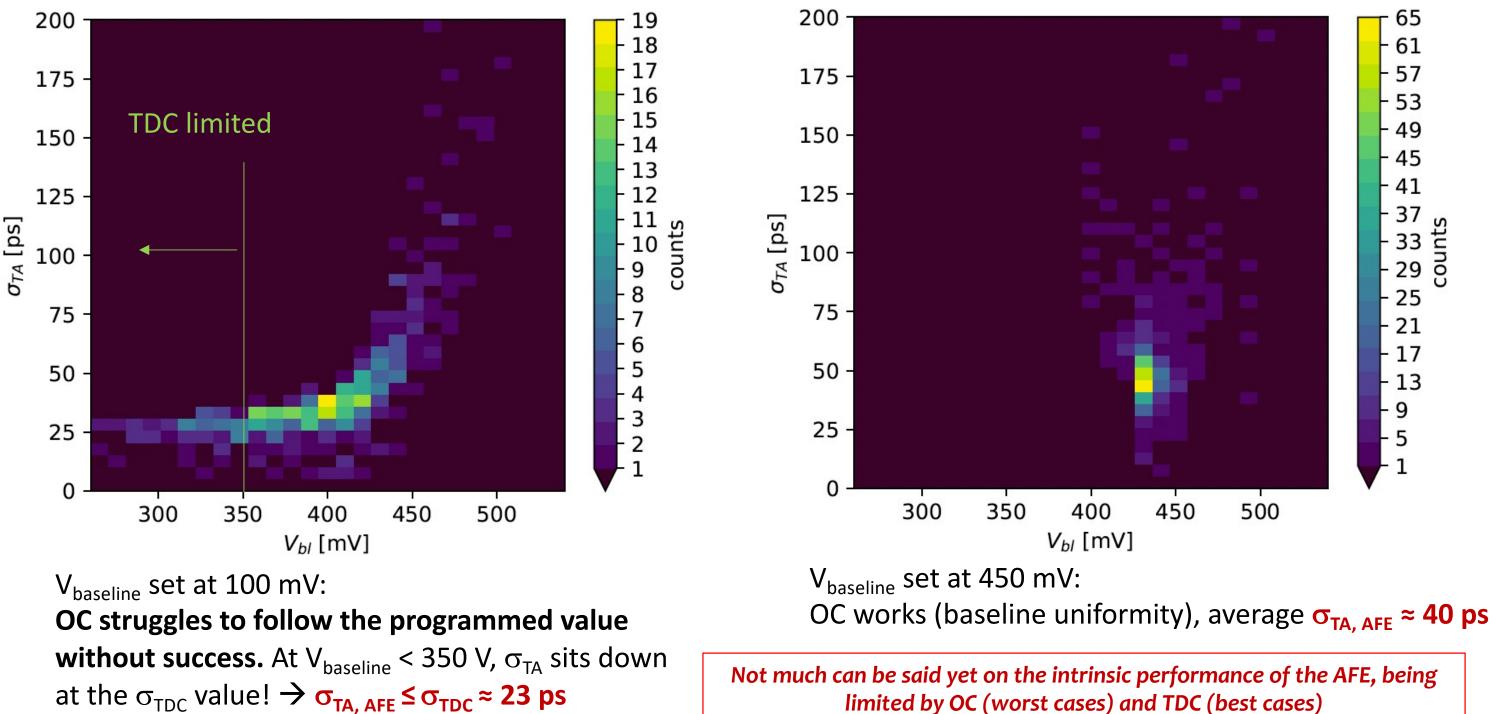

- $\rightarrow$  Issue with the Offset Compensation mechanism: OC fails when V<sub>baseline</sub> is set to low values !

### OC problem, $V_{\text{baseline}}$ and $\sigma_{TA}$ The amplifier is working properly, OC is not...

## A (preliminary) summary on the 28-nm ASIC

What we learned up to now

- A pixel readout performance < 30 ps time resolution (F/E + TDC) is there. It will be reached once minor modifications are performed:

- OC bug correction should be already sufficient,

- more accurate clock distribution can even improve the performance towards 20 ps

- Something can still be gained from technology (HPC  $\rightarrow$  HPC+, HVT-LVT accurate choice)

- We think that power budget ("dissipation" budget ~ 1.5 W/cm<sup>2</sup>) must be increased for higher timing performance. 20 ps or even less are within reach with a moderate increase (~30%)

- System-level R&D in cooling techniques is vital for timing

- Effective timing pixel performance depends on ASIC size and "collective" effects

- **Uniformity** across the whole area is a major difficulty in CMOS 28-nm (important IR drops), critical clock tree

- **VERIFICATION** at the full ASIC level is the mainly critical step

- Full data BW is critical: >100 Gbps needs innovative solutions in data seralizers and links

The 30<sup>th</sup> International Workshop on Vertex Detectors VIRTUAL (Oxford) 27-30 September 2021

# **THANK YOU everyone!**

### **Adriano Lai** adriano.lai@ca.infn.it

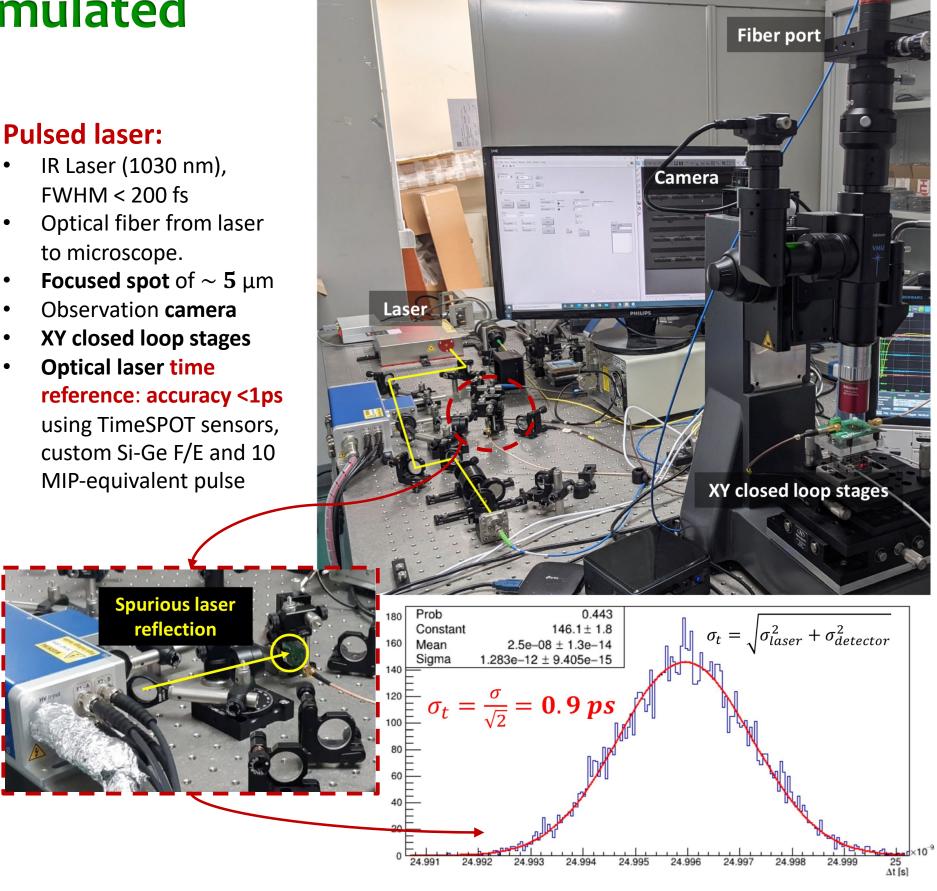

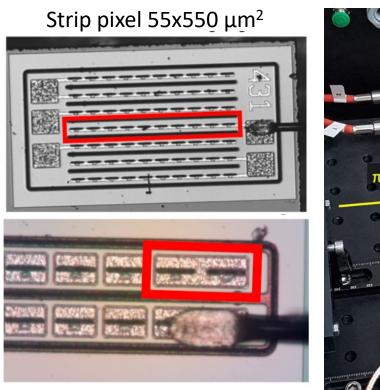

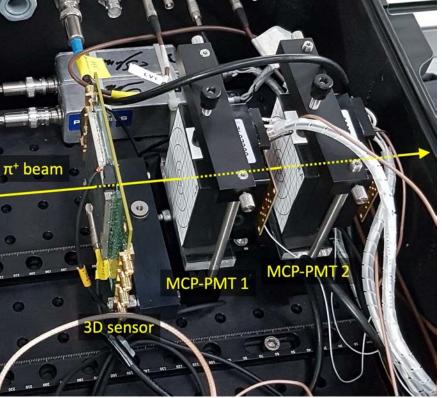

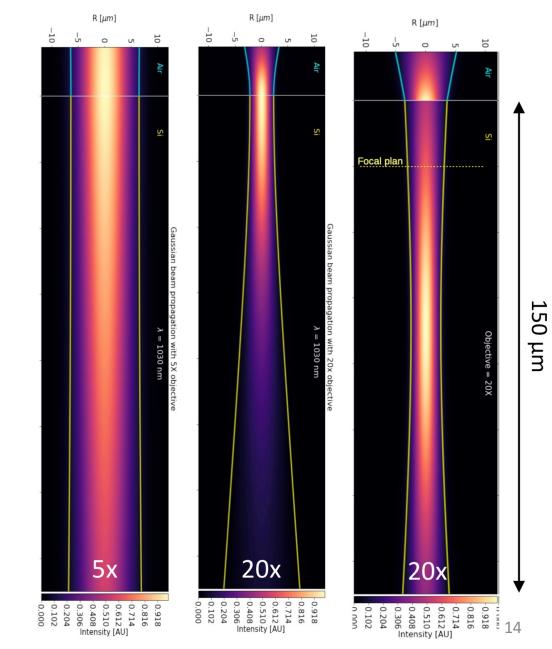

## **Time resolution: laser-emulated MIP studies**

By choosing the waist shape (changing optics) and properly calibrating the laser intensity (using a precision CSA) a MIP-like deposit is generated

- IR Laser (1030 nm), FWHM < 200 fs

- to microscope.

- Observation camera

- **Optical laser time** reference: accuracy <1ps using TimeSPOT sensors, custom Si-Ge F/E and 10 MIP-equivalent pulse