# **Test Beam Studies of Passive CMOS Strips**

Surabhi Sharma, Jan-Hendrik Arling, Marta Baselga, Leena Diehl, Ingrid-Maria Gregor, Marc Hauser, Tomasz Hemperek, Fabian Lex, Ulrich Parzefall, Arturo Rodriguez, Niels Sorgenfrei, Dennis Sperlich, Jens Weingarten

BTTB10 Lecce Italy: 22.06.2022

## **Motivation for passive CMOS**

- Requirements for future HEP detectors

- All silicon-based tracker

- Large surface

- Possibly more radiation tolerant

- Why CMOS sensors

- Cost effective-> Use of commercial CMOS production processes

- Stitched sensors for large surface

- Thin detectors

#### R&D program to study feasibility of passive CMOS strip sensors

Surabhi Sharma | Passive CMOS Strips DESY.

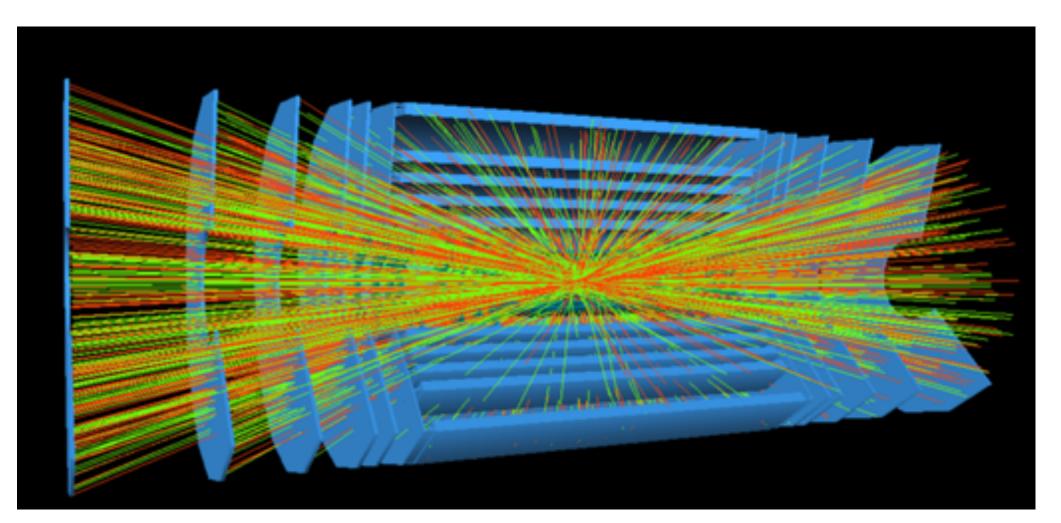

#### **ATLAS detector in HL-LHC**

Picture of ATLAS endcap structure showing silicon strip sensor with up to 10 X 10  $cm^2$

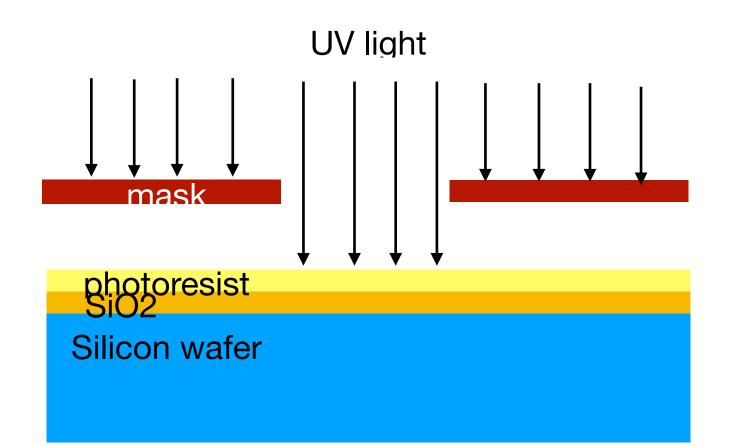

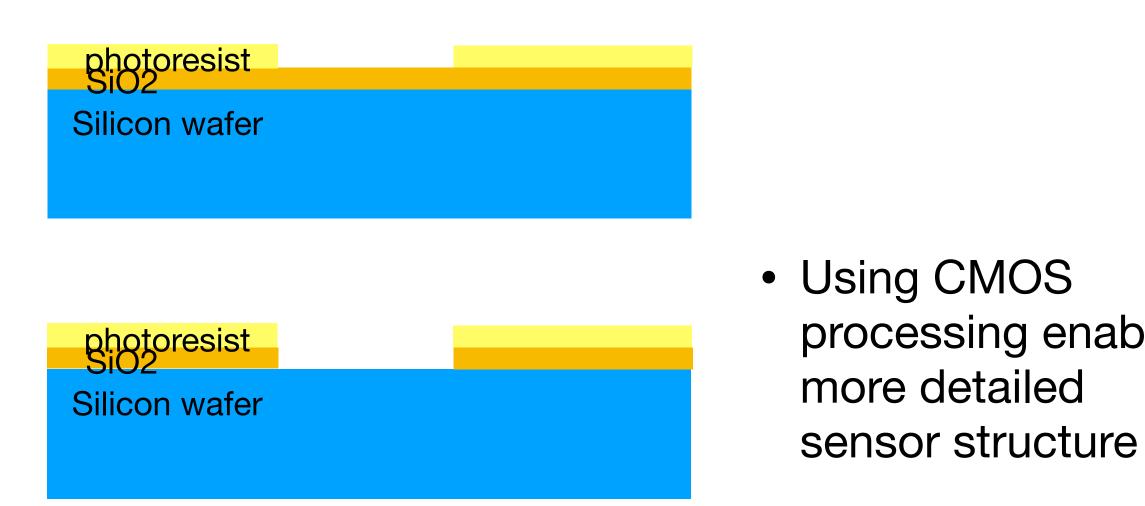

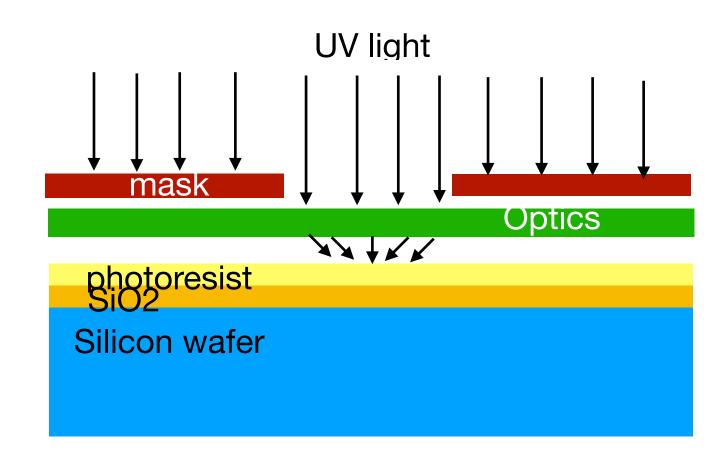

#### CMOS processing compared to microelectronics processing Microelectronics photolithography CMOS photolithography

#### Surabhi Sharma | Passive CMOS Strips DESY.

processing enables

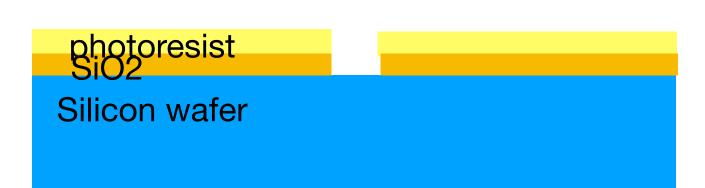

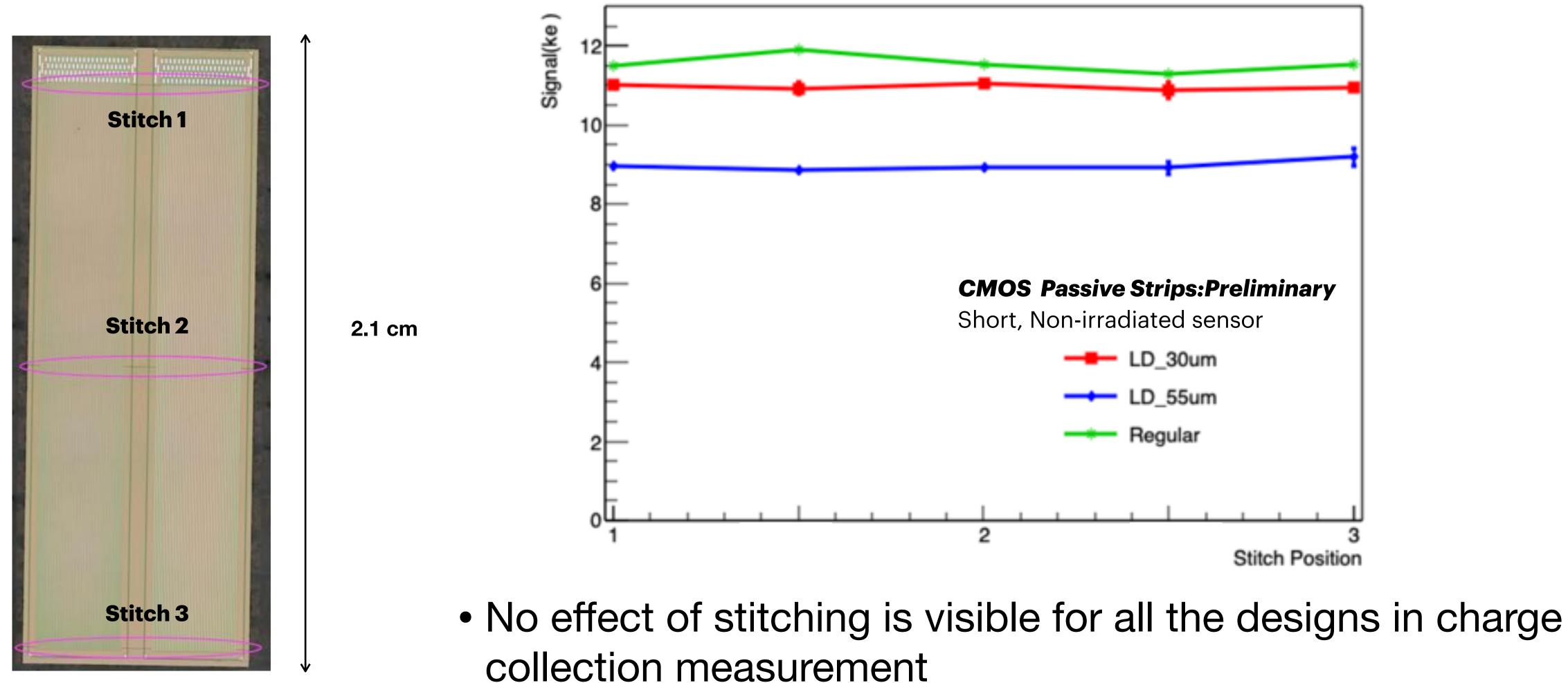

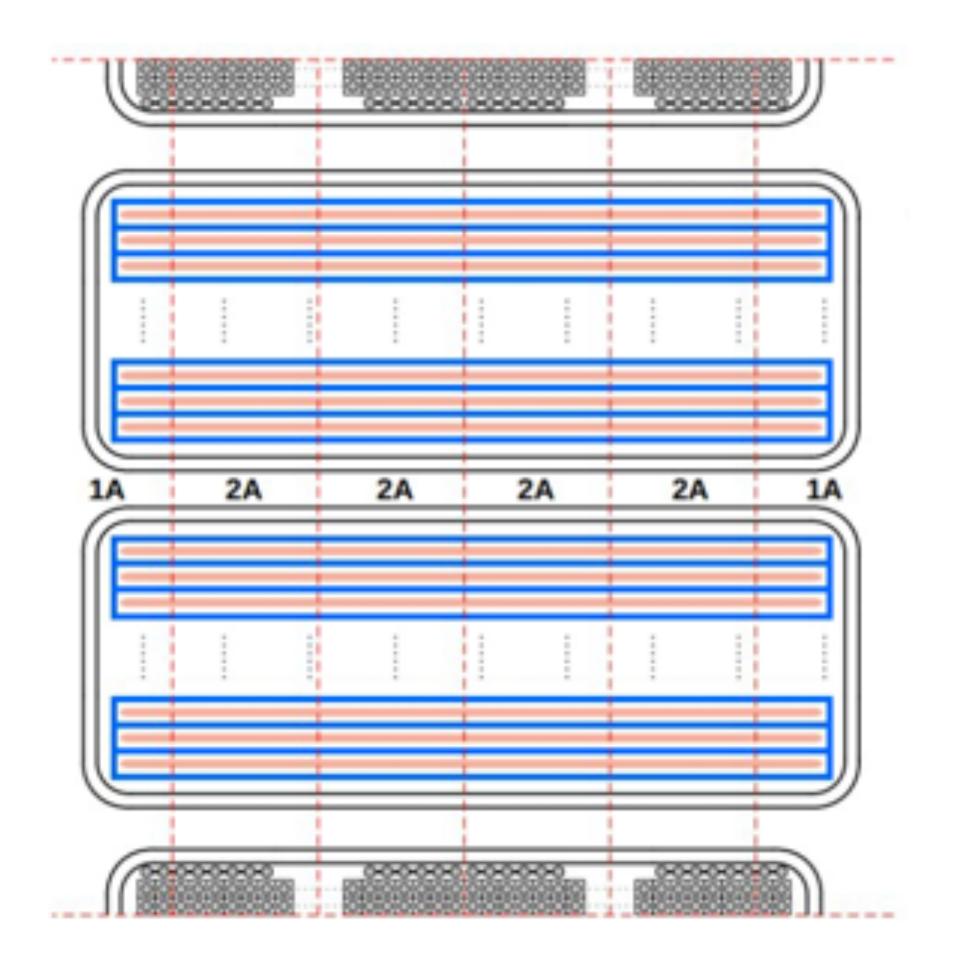

# Stitching design

- Stitching merges multiple design structures on a wafer during the photolithographic process -> creates large sensor

- Stitched every ~1 cm along strip length

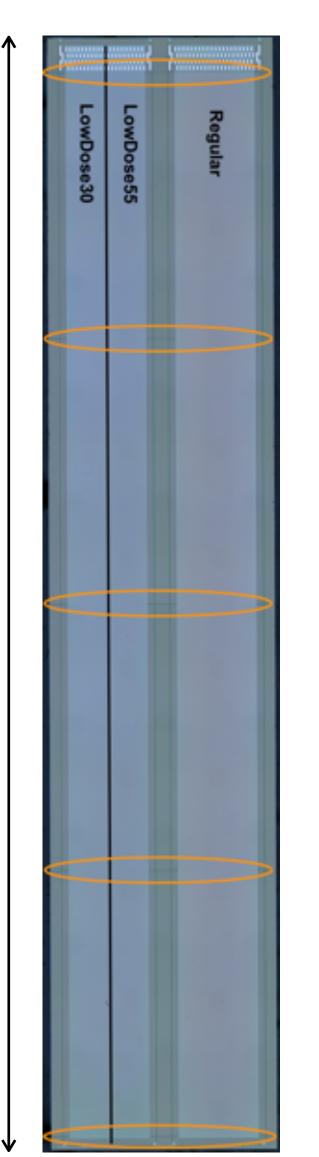

## Sensor Details

2.1 cm

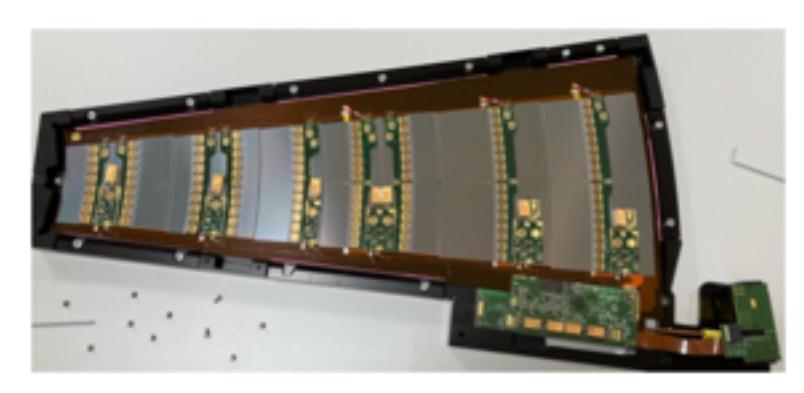

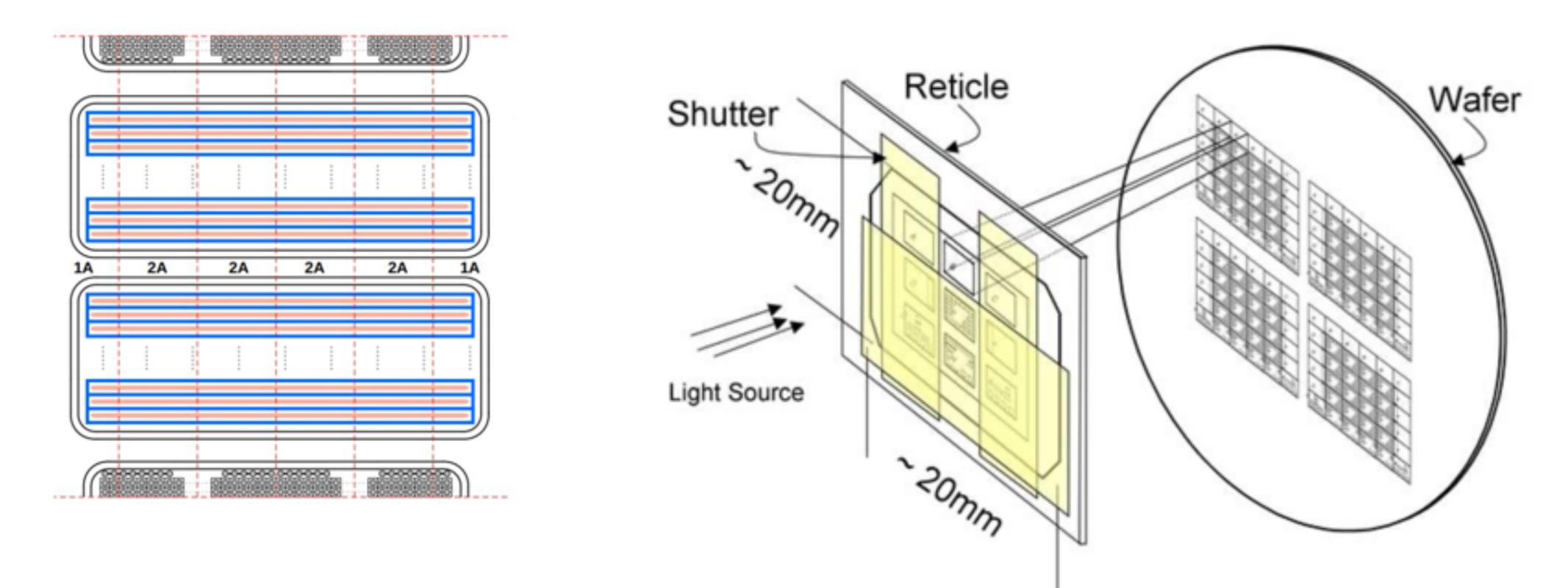

- First stitched strip sensor produced on 8" wafer by a commercial foundry

- L-Foundry 150 nm process (deep N-well/P-well) • Up to 7 metal layers Resistivity of wafer: 3000 - 5000 Ω·cm Float-zone wafer

- The strip sensors have 2 different lengths : 2.1 cm and 4.1 cm

- First Batch: Low p+ dose and no metallisation • Second Batch: Increased p+ dose and metal layer

- Frontside process: Reticle stitching for large sensors Backside process: Additional p+ implant

4.1 cm

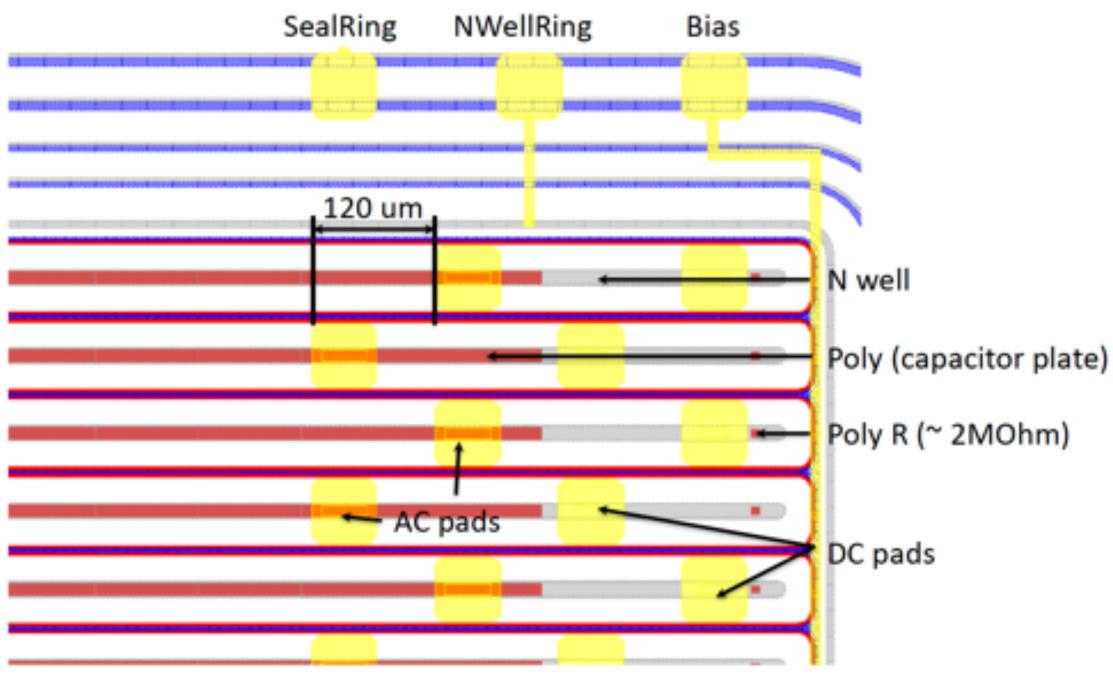

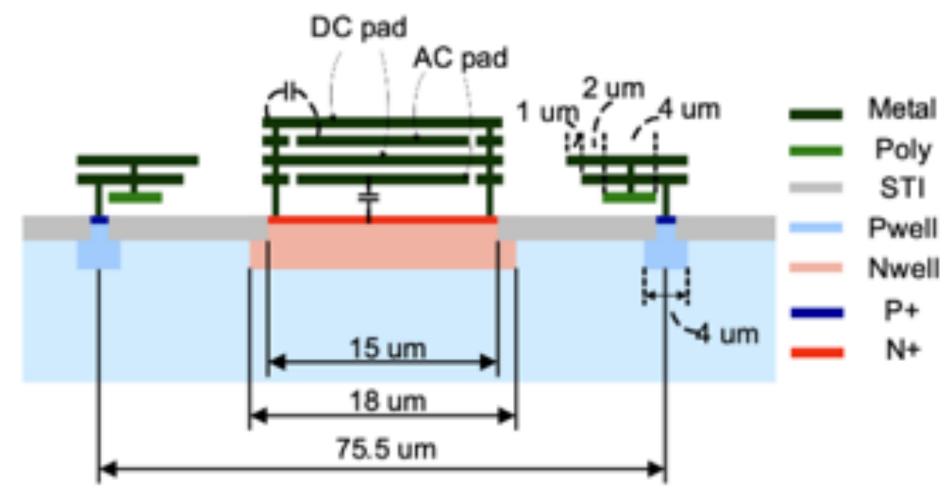

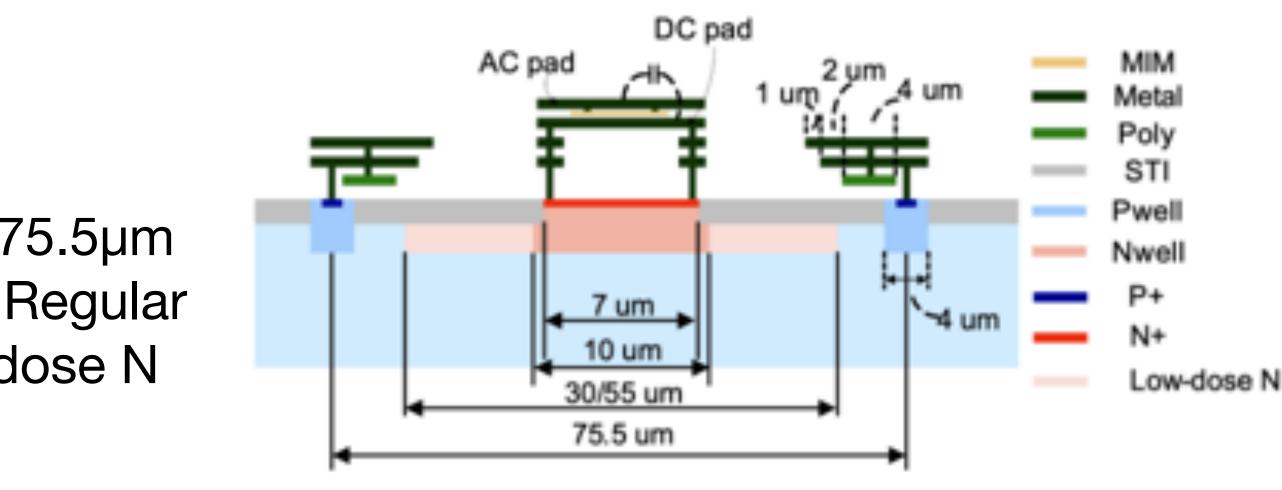

## Sensor Structure

- Sensor thickness  $\sim 150 \pm 10 \,\mu m$

- Sensor has 40 strips each, with strip pitch =  $75.5\mu$ m

- Three different designs: LowDose 30/55 and Regular

- LowDose design comes in two different low dose N widths, 30 & 55 um with 20 strips per design

Surabhi Sharma | Passive CMOS Strips DESY.

#### **Regular design**

#### Low Dose design

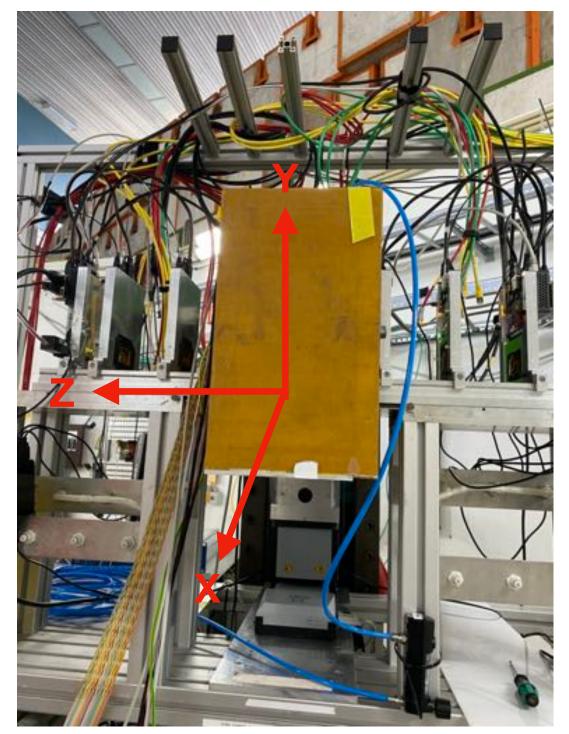

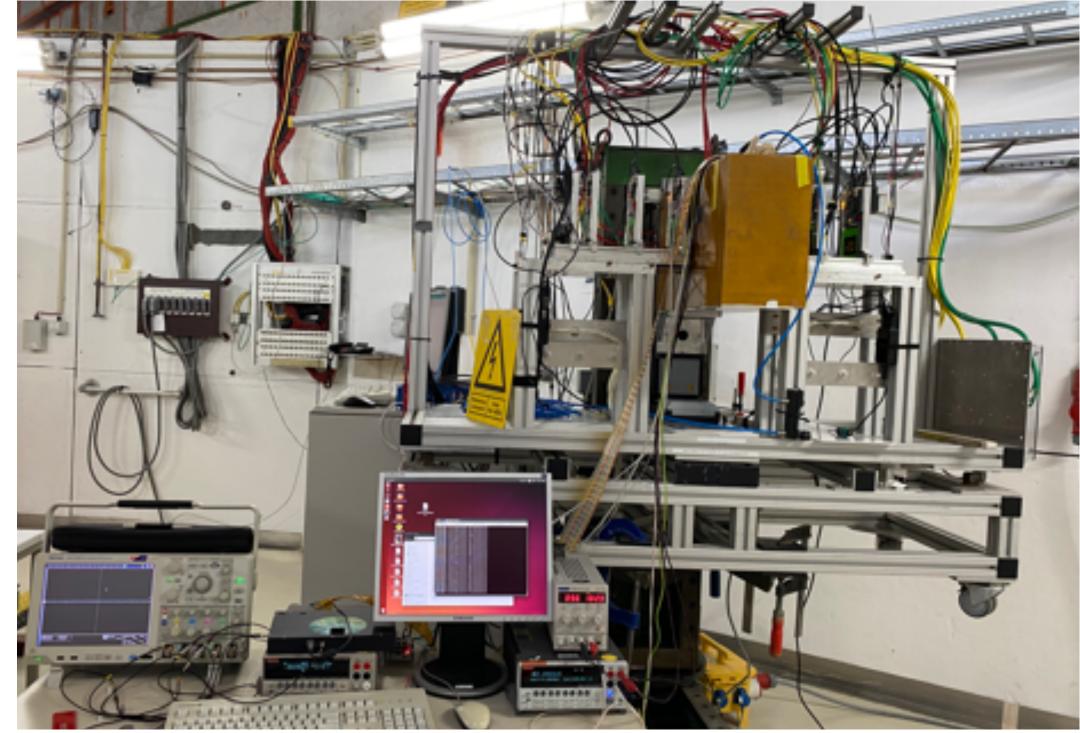

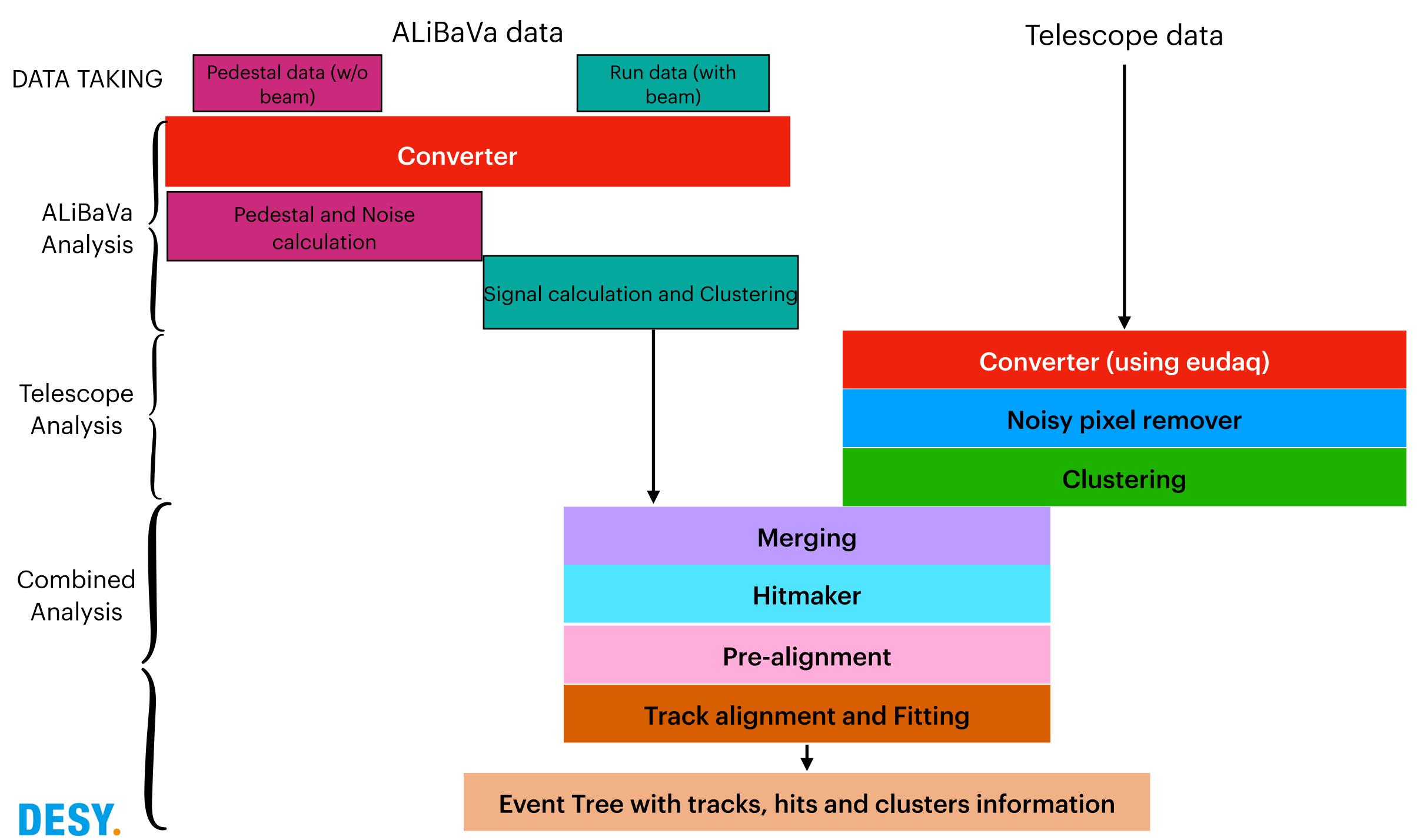

# TestBeam Setup

- Data taken at DESY II

- Electron beam with beam energy 3 GeV and 3.4 GeV is used

- Using beam line 22 and ALiBaVa system is used for the readout

- Non-irradiated and irradiated sensors tested

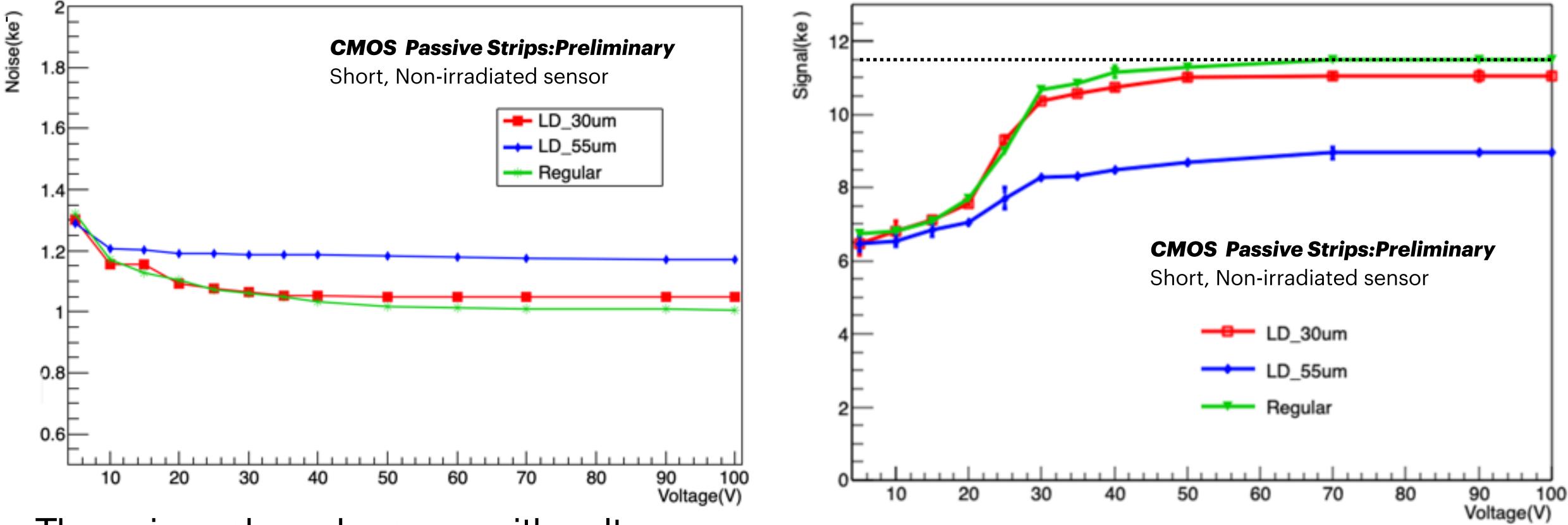

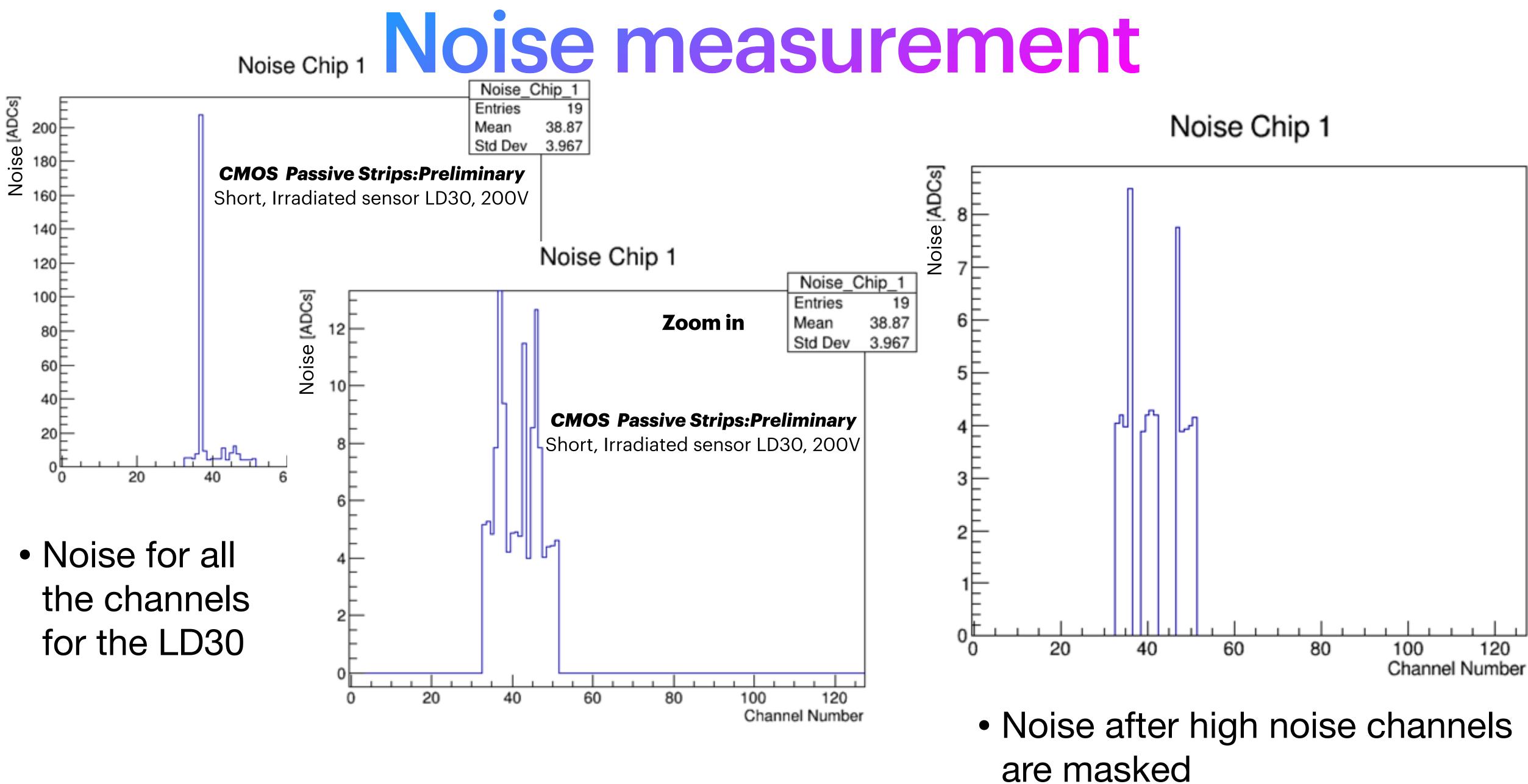

### **Noise and Signal measurement**

All measurements are performed at 18° C

- The noise values decrease with voltage

- Highest signal in Regular sensor, low noise value for regular sensor

- capacitance of LD55)

**DESY.** | Surabhi Sharma | Passive CMOS Strips

Low dose 55 design has a systematic offset – related to Beetle chip configuration (high

## **Signal Measurement- Stitching**

All measurements are performed at 18° C

**DESY** | Surabhi Sharma | Passive CMOS Strips

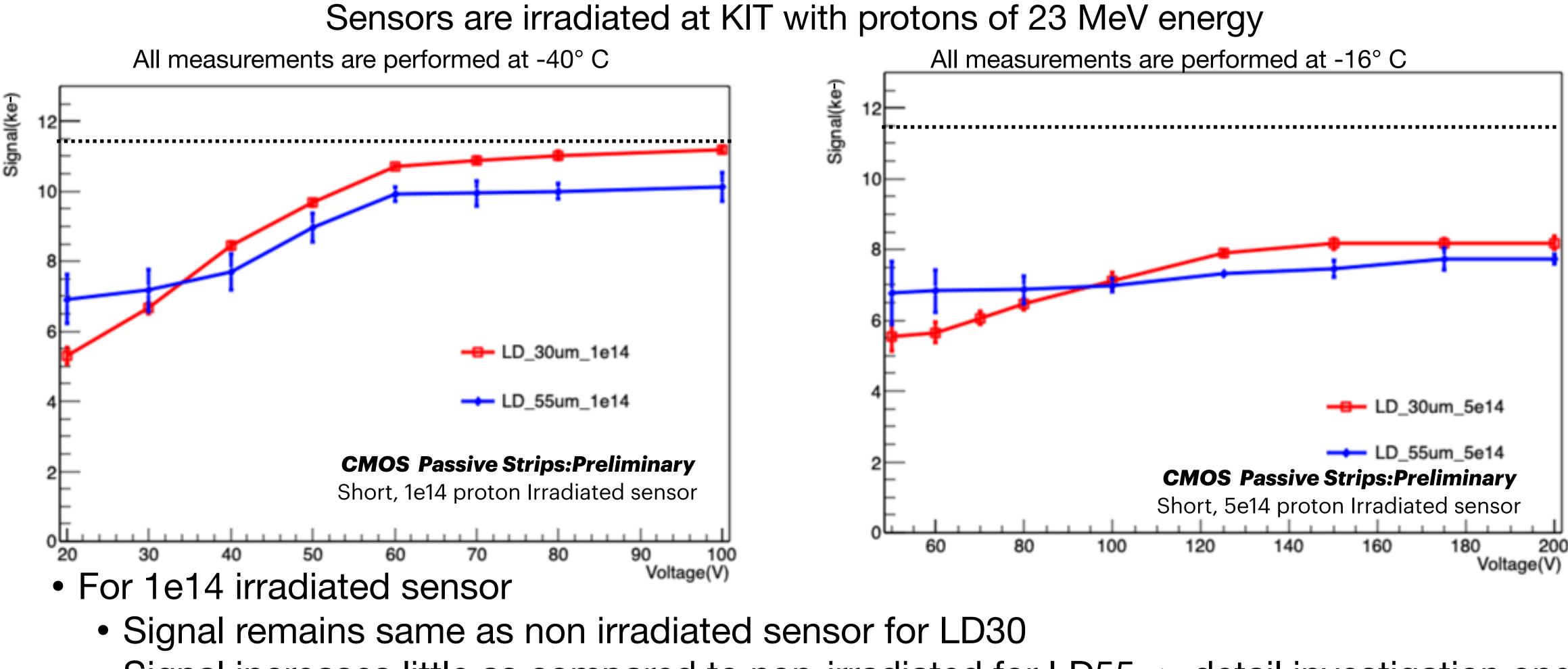

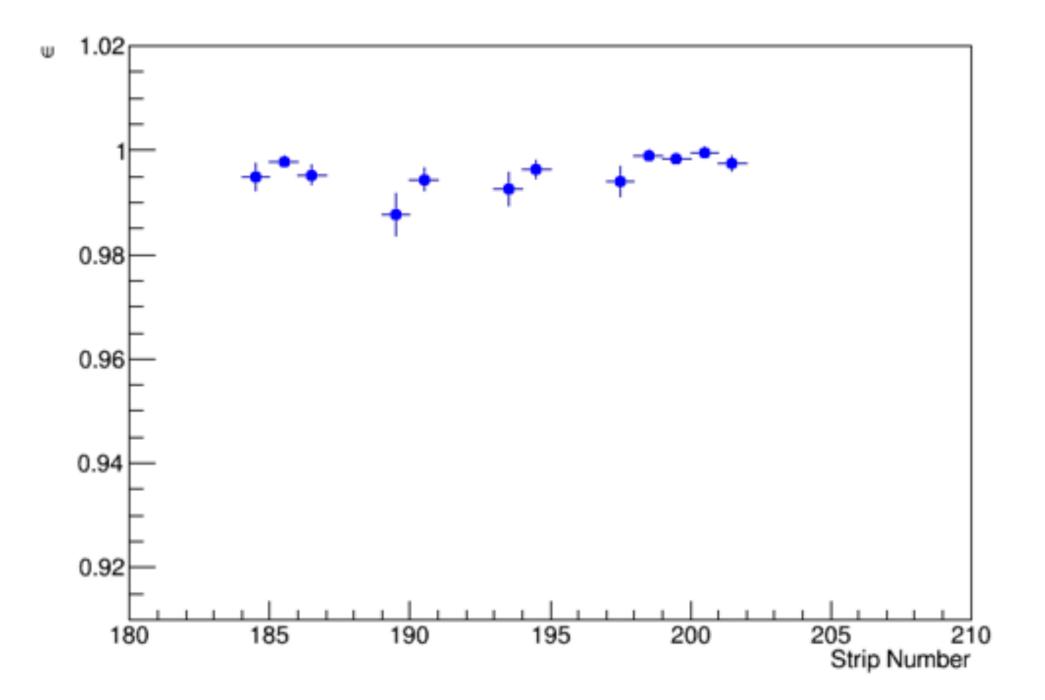

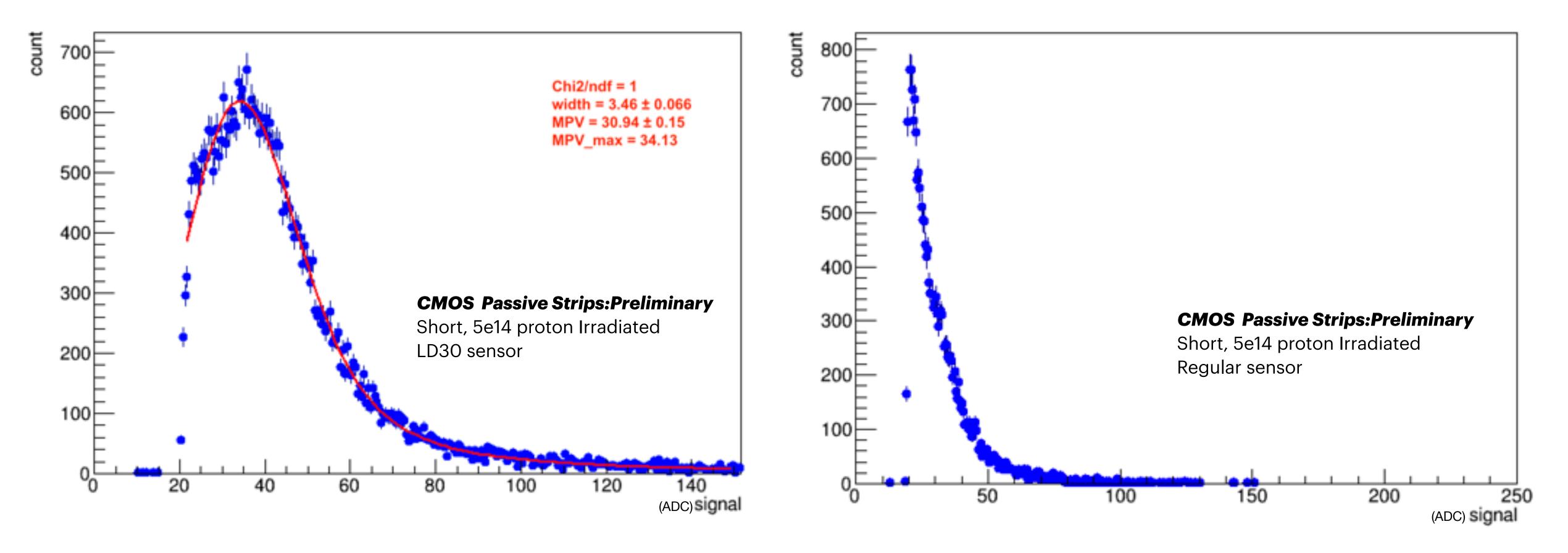

### **Signal measurement - Irradiated**

• For 5e14 irradiated sensor, collected signal drops significantly till 200V

#### Surabhi Sharma | Passive CMOS Strips DESY.

• Signal increases little as compared to non-irradiated for LD55 -> detail investigation ongoing

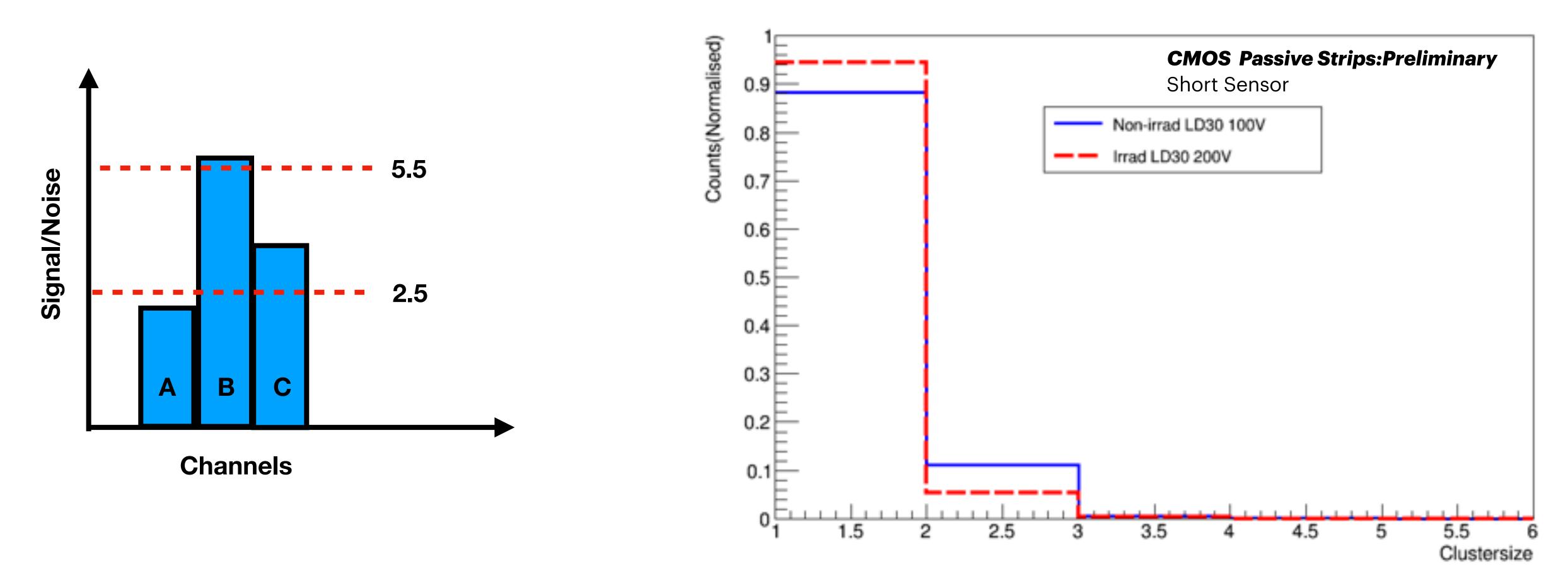

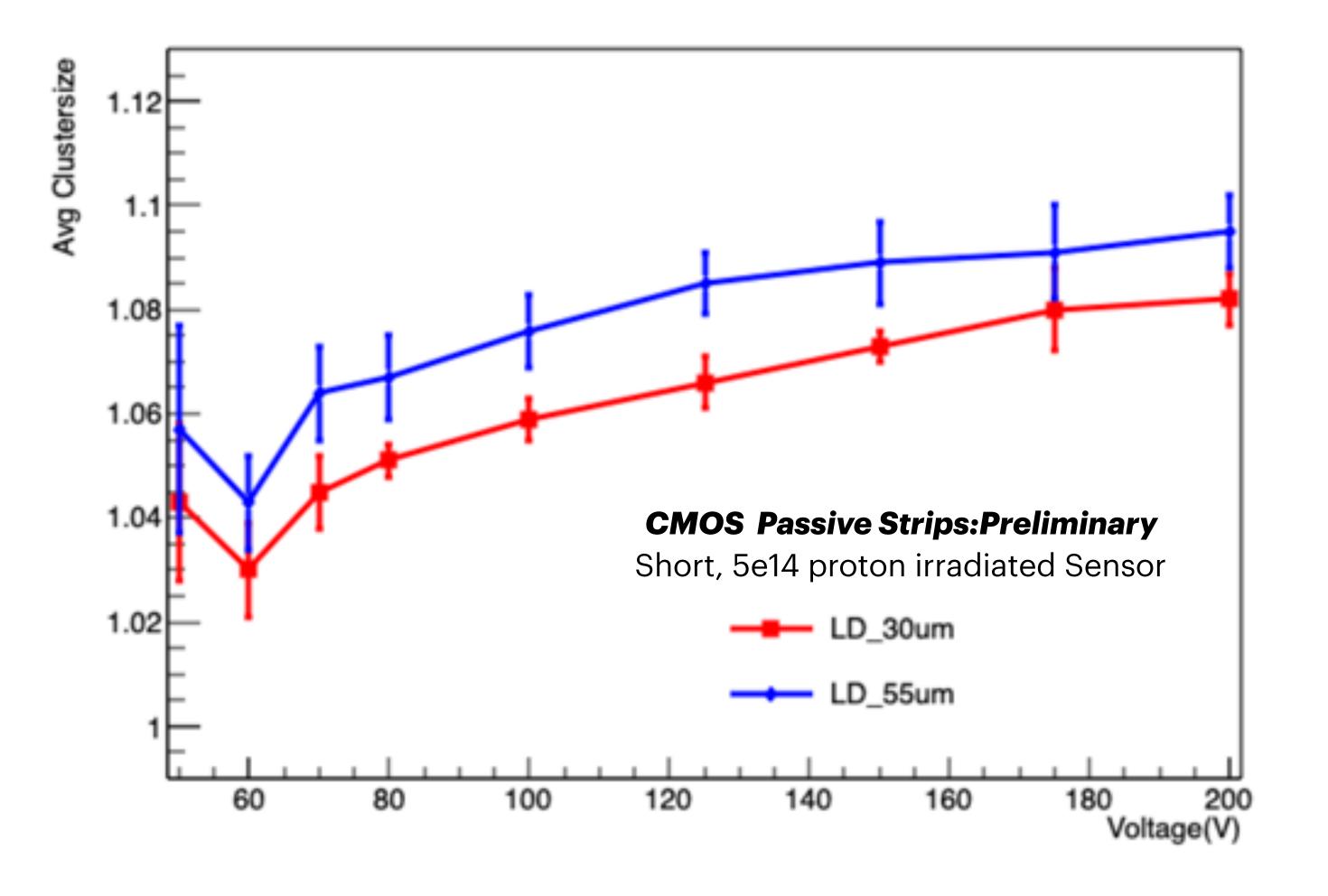

- Cluster size calculated with maximum of 5 strips

- With irradiation -> Cluster size decreases

**DESY.** | Surabhi Sharma | Passive CMOS Strips

### **Cluster size**

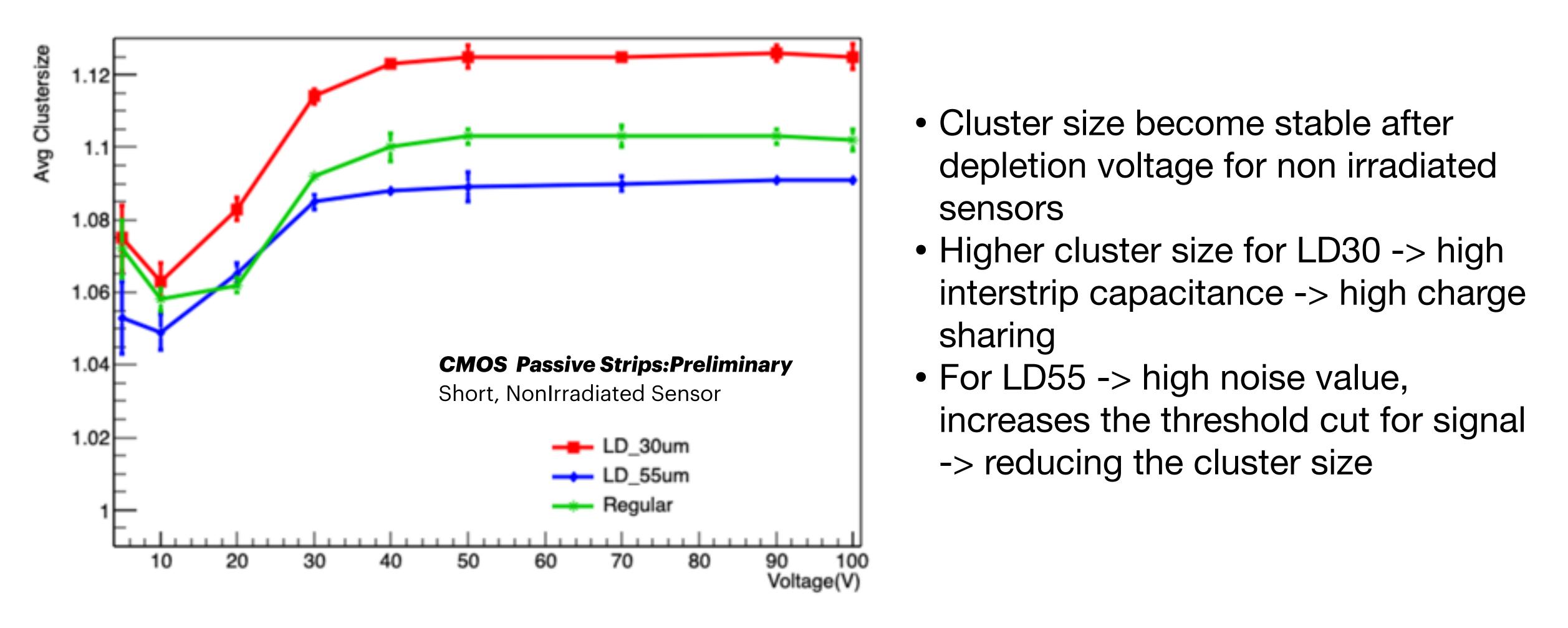

### **Cluster size -nonirradiated sensor**

**DESY.** | Surabhi Sharma | Passive CMOS Strips

### **Cluster size- Irradiated sensor**

**DESY.** | Surabhi Sharma | Passive CMOS Strips

- For irradiated sensor, the cluster size doesn't show high increase

- For LD55, small number of strips are available after irradiation (high noise)

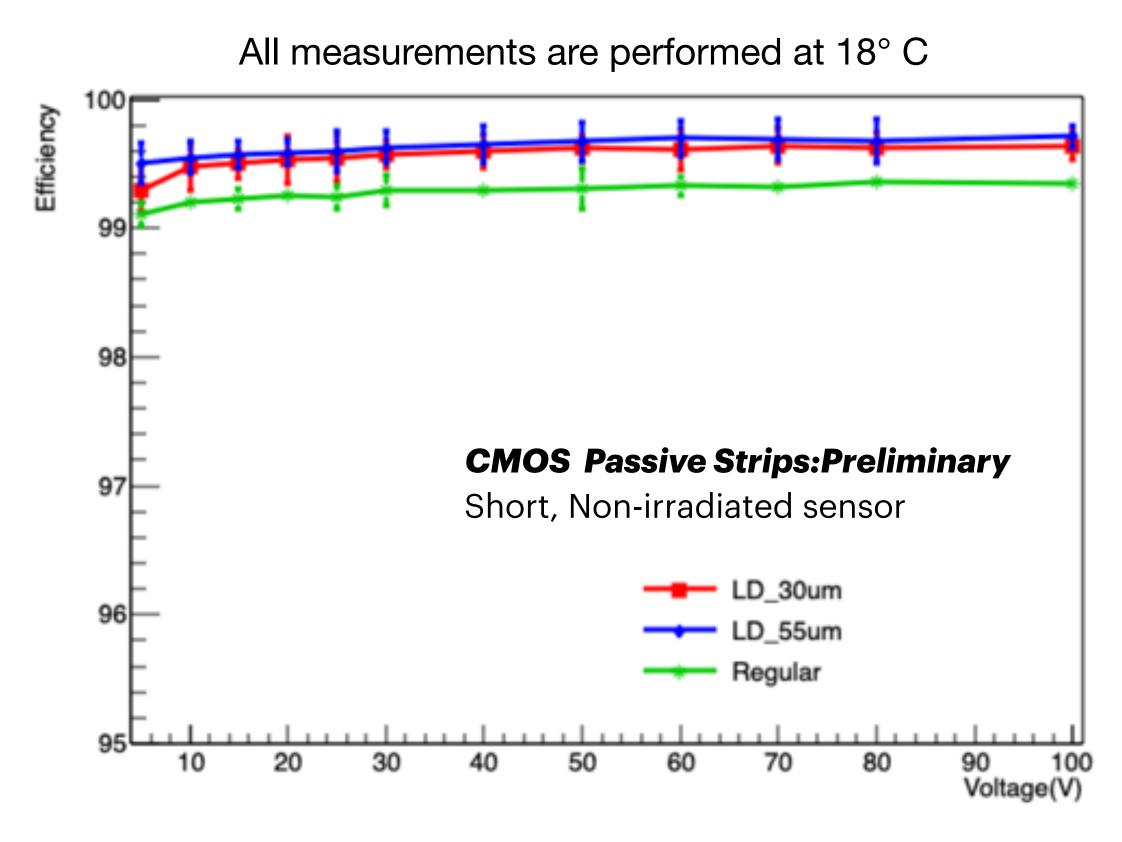

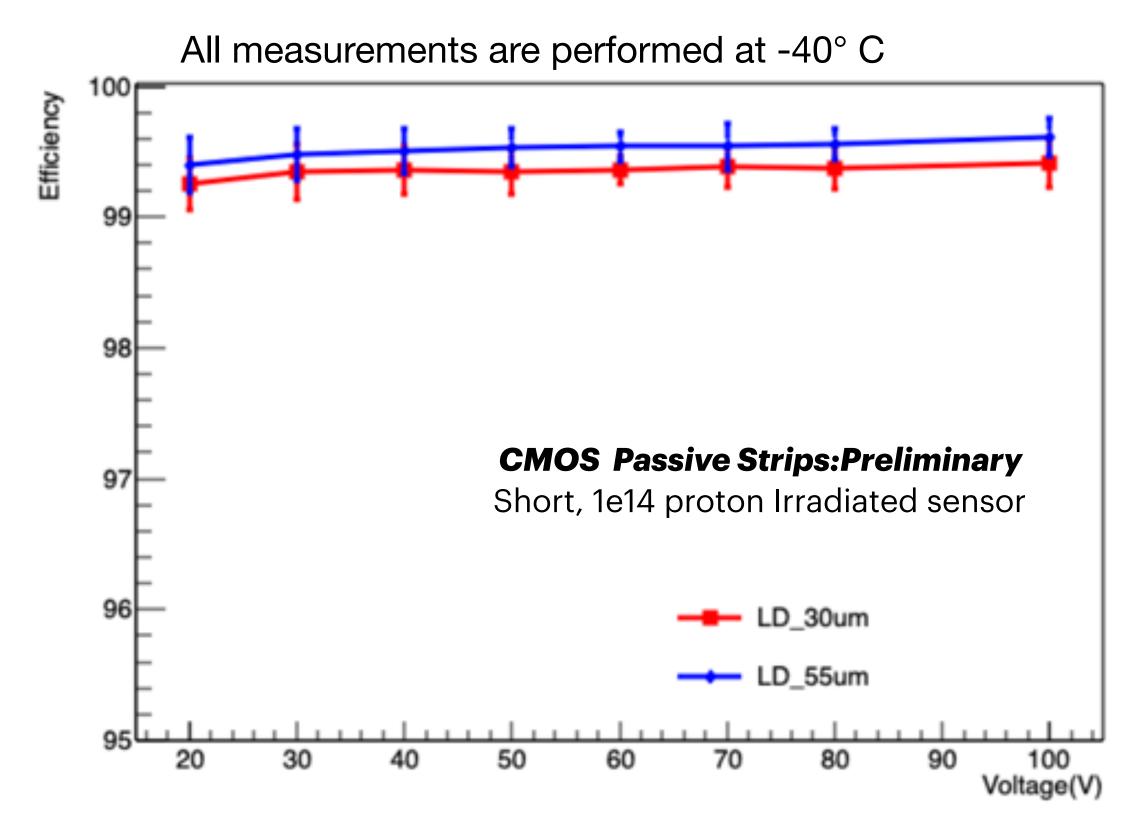

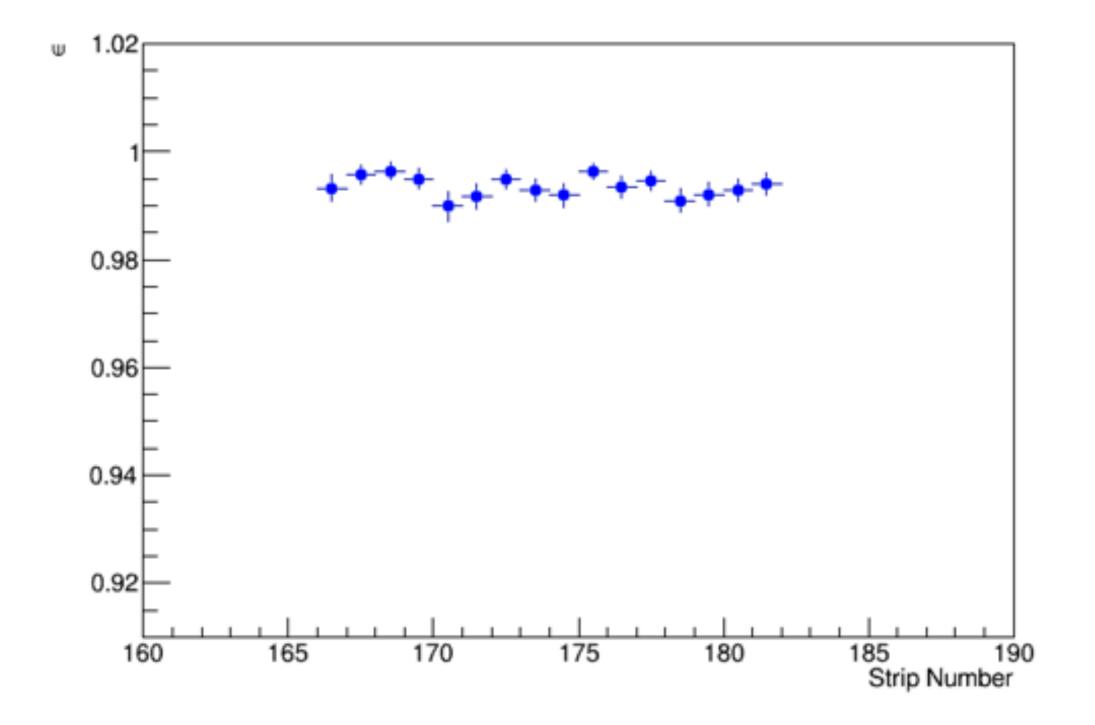

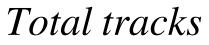

## Hit detection efficiency

- Before irradiation -> Efficiency is greater than 99 % for all designs

- Fully efficient also at low bias voltage • Fully efficient also at lower voltages • Fulfils ATLAS ITk requirement > 97%

**DESY** | Surabhi Sharma | Passive CMOS Strips

After irradiation with 1e14 fluence -> Efficiency is still greater than 99 % for all designs

- No negative effects of stitching is observed before irradiation

## Outlook

$\succ$  Further analysis from the test beam data is ongoing > TCT and charge collection measurements of irradiated neutron sample are ongoing

**DESY** | Surabhi Sharma | Passive CMOS Strips

Successful testbeam campaign for the Passive CMOS strips sensor • Hit efficiency above 99% for both non-irradiated and irradiated sensor

## Thank You for Attention

The measurements leading to these results have been performed at the Test Beam Facility at DESY Hamburg (Germany), a member of the Helmholtz Association (HGF)

**DESY.** | Surabhi Sharma | Passive CMOS Strips

Back-up

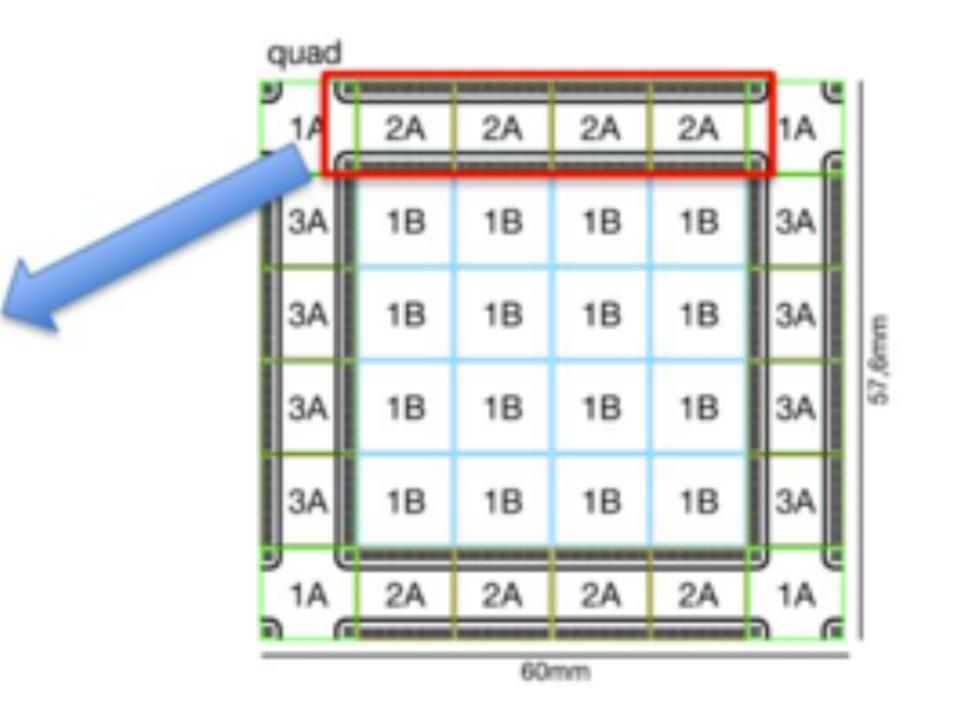

# Wafer design

**DESY** Surabhi Sharma | Passive CMOS Strips

- Strip sensor implemented in 1/2A

- Stitched every ~1 cm along strip length

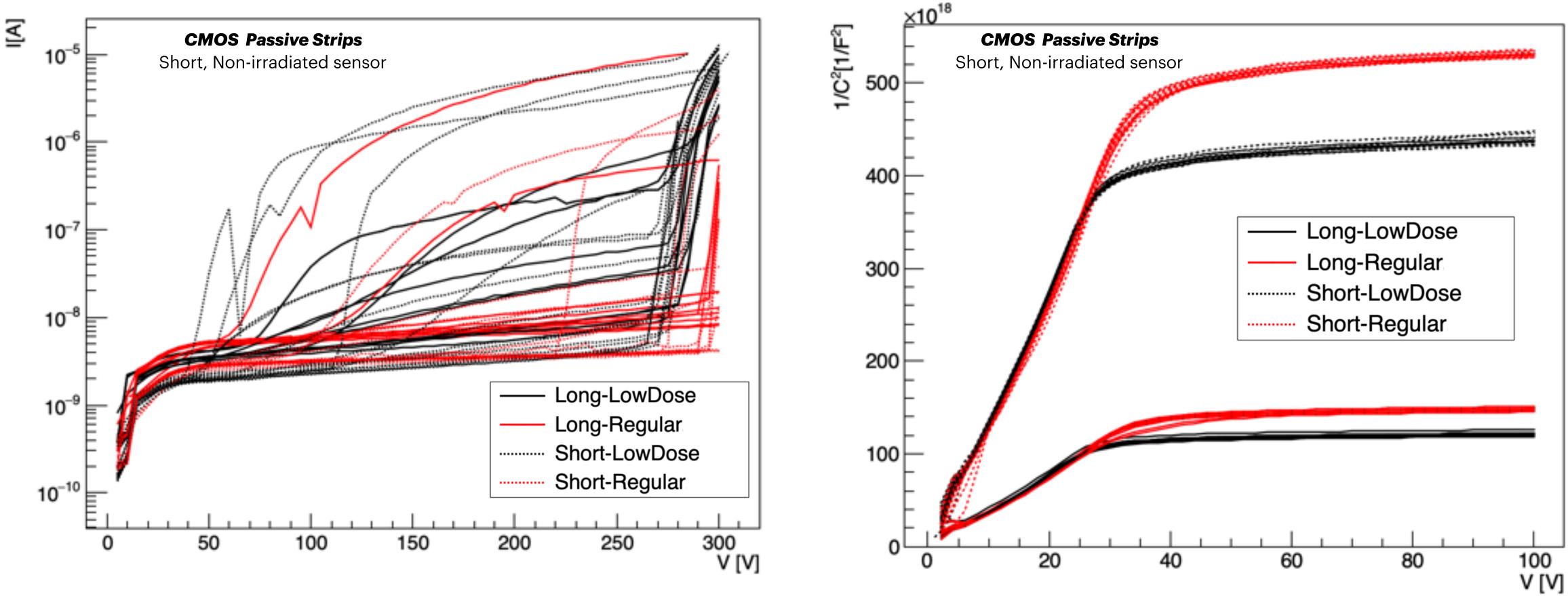

### **IV and CV Measurements**

#### All measurements are performed at room temperature

- Breakdown voltage above 250V, improved for batch II (higher backside implant doping) concentration, metallization)

- Depletion voltage for LowDose implant (30V) < Depletion voltage for Regular implant <math>(36V)

- Stable capacitance behavior: Bulk capacitance ~50pF (short sensors), ~100pF (long sensors)

- Surabhi Sharma | Passive CMOS Strips DESY.

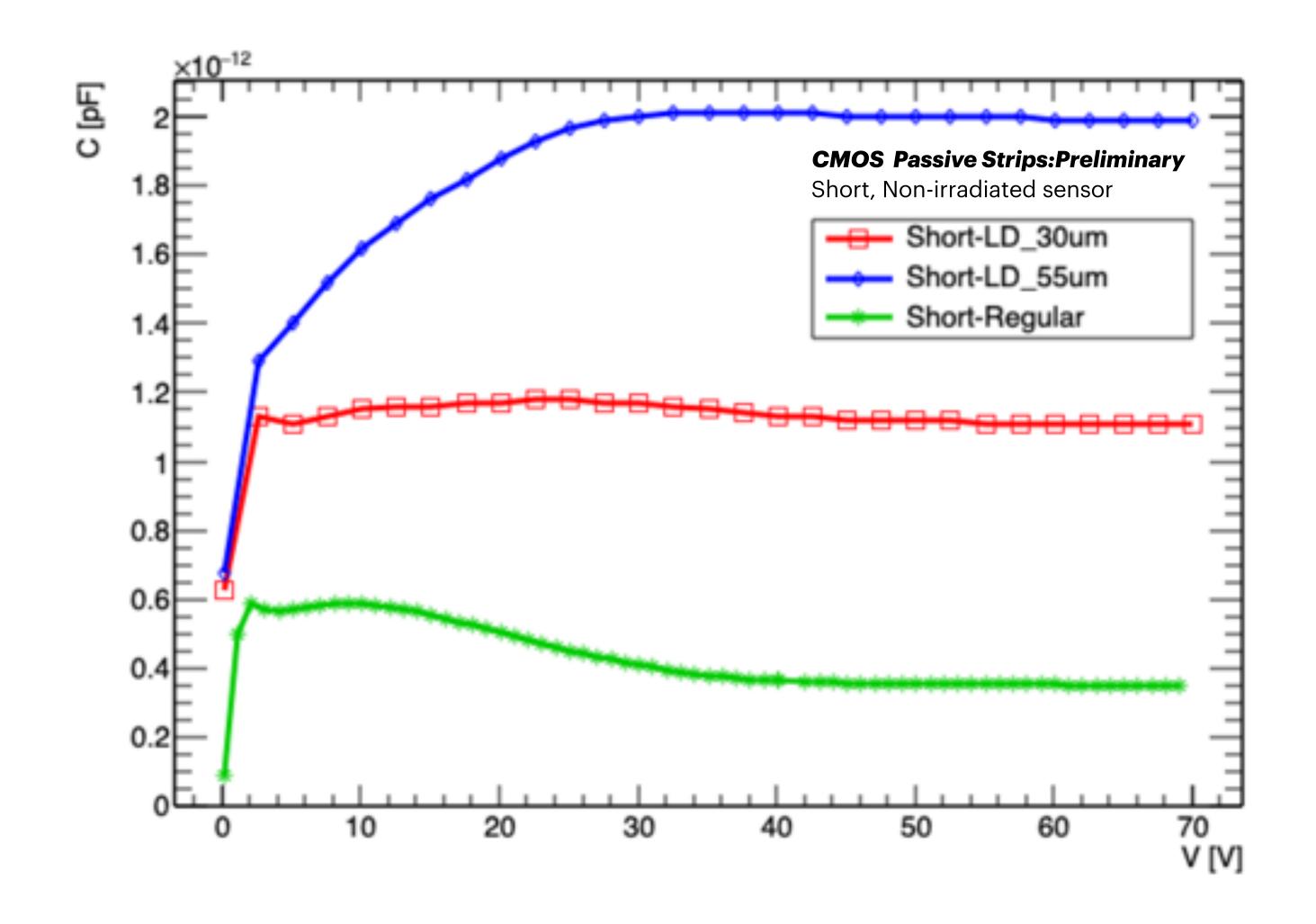

#### **Measurement at room temperature for frequency of 500kHz**

- With increasing width of implant capacitance increases -> highest for LD55 sensor

- Capacitance becomes stable after depletion voltage

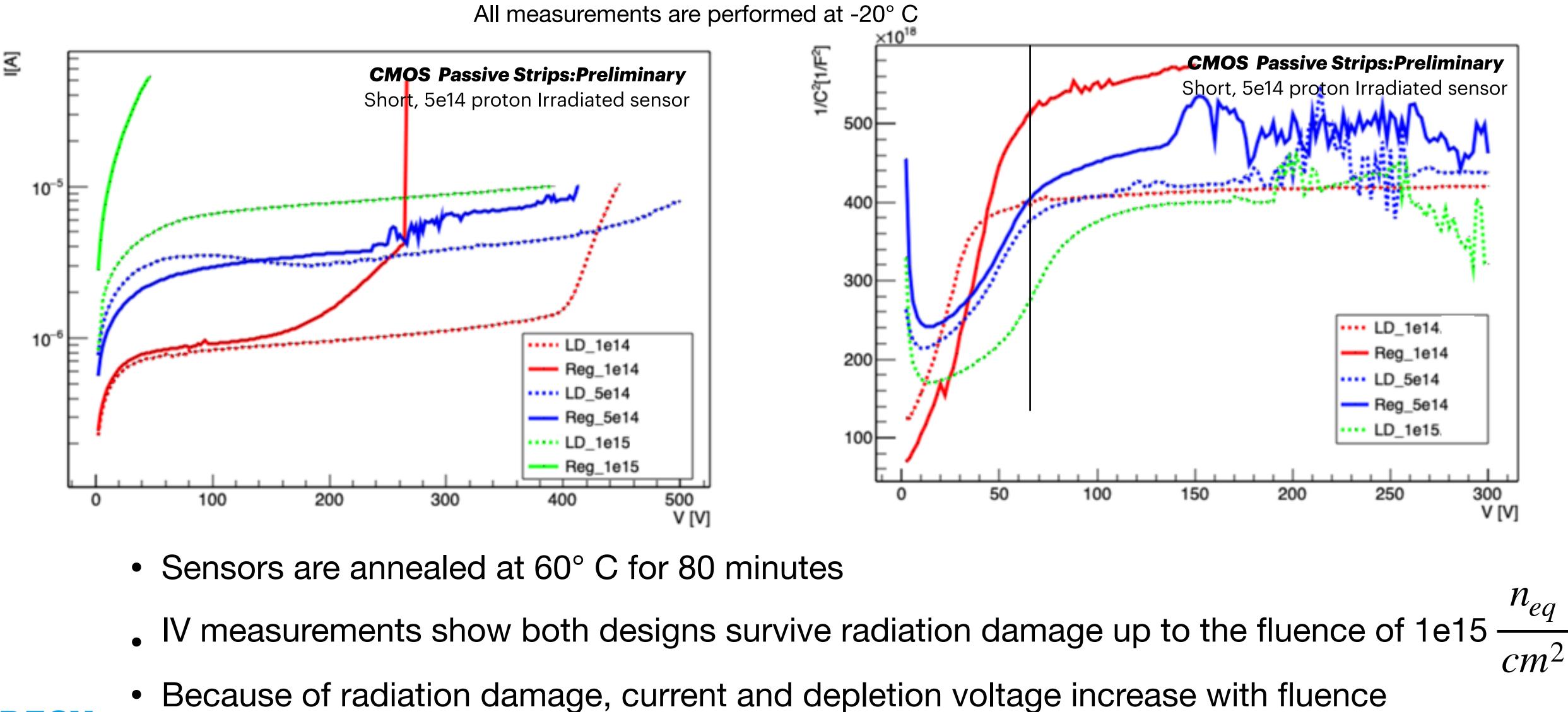

## IV and CV measurements

#### Sensors are irradiated at KIT with protons of 23 MeV energy

Surabhi Sharma | Passive CMOS Strips DESY

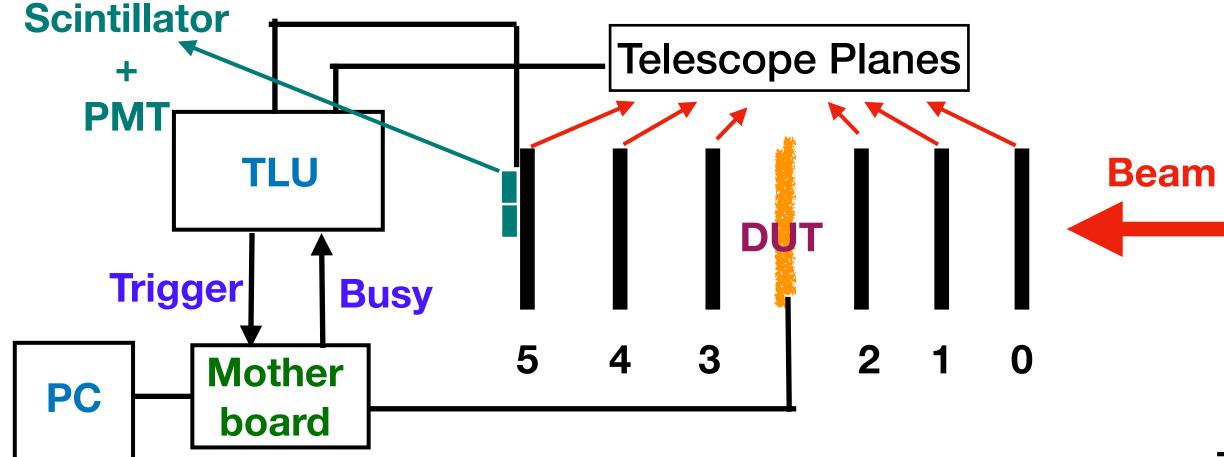

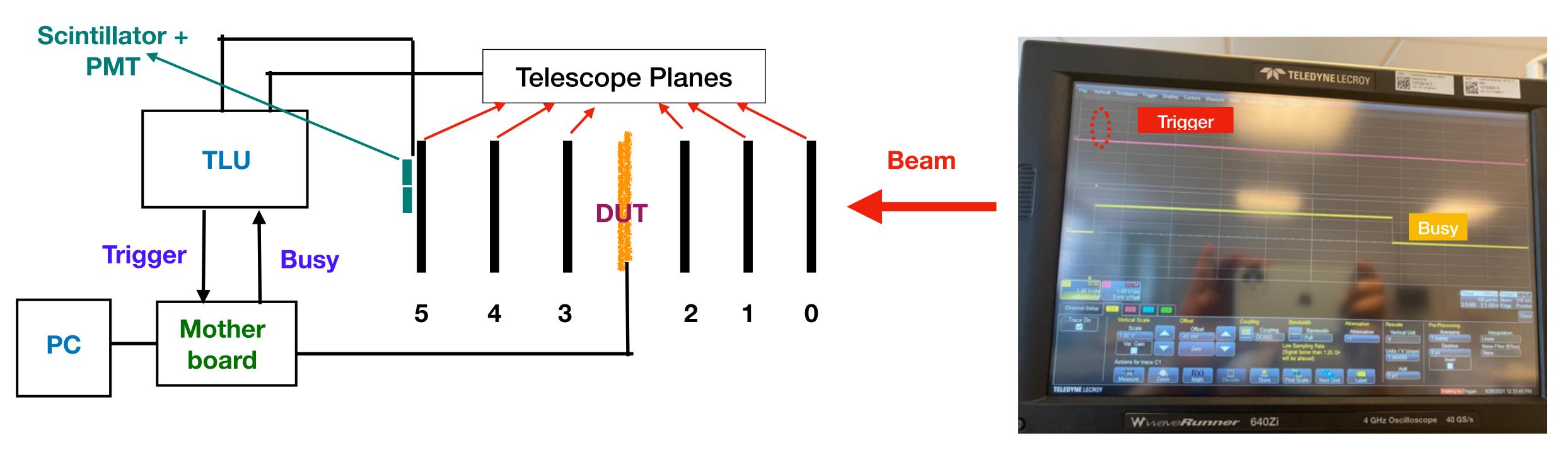

### **TestBeam Connection**

- Two overlap Scintillator at the back and Tracks passing through both qualifies for the trigger to TLU

- TLU setting in EUDET mode

- TLU sends the trigger to the Mother board (Alibava system) and mother boards looks into the received signal with 25 ns timestamp and sends the Busy to TLU -> so no extra trigger come from TLU to motherboard

- The trigger is 25ns long (from TLU to Alibava)

- The busy is 630 µs long (from Alibava to TLU)

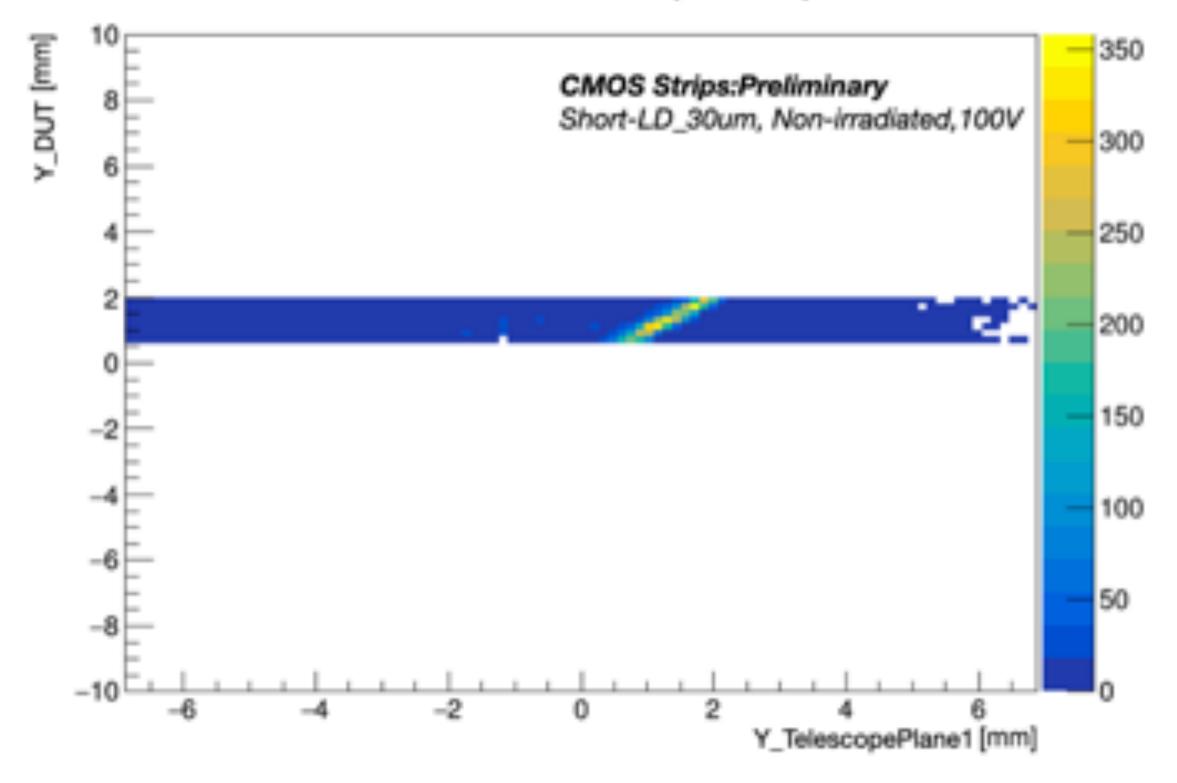

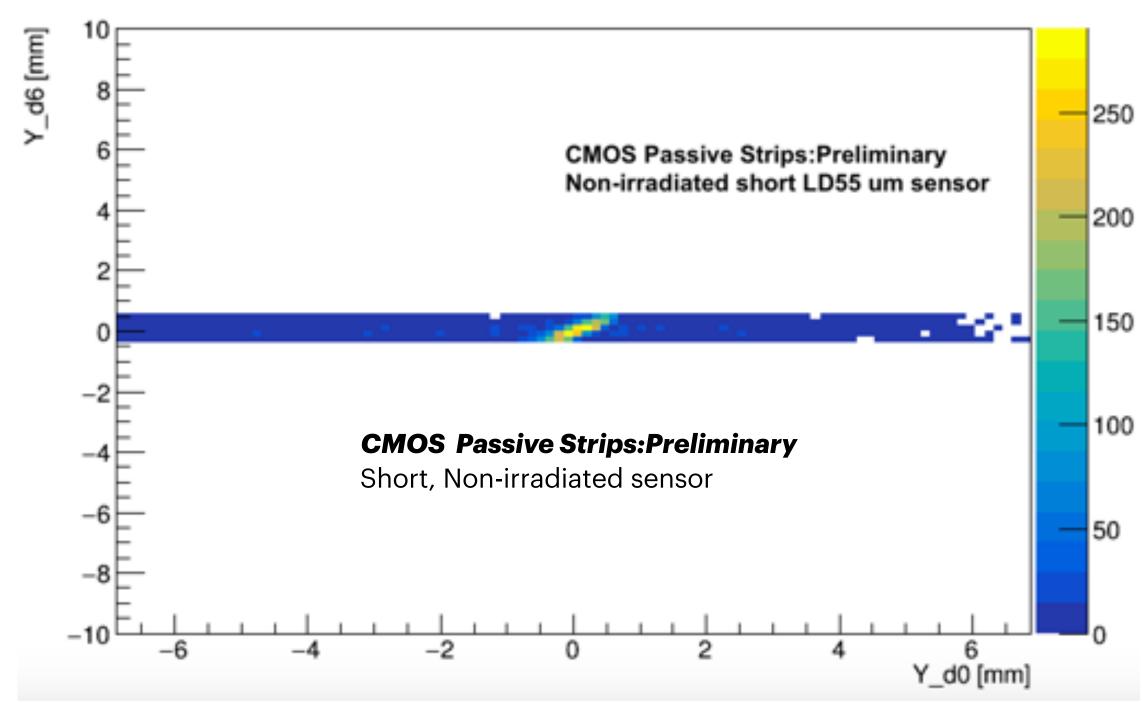

#### Hit correlation in Y (d0->d6)

The correlation plot for LD30 and LD55 sensor Similar behaviour is seen in Regular sensor

Surabhi Sharma | Passive CMOS Strips DESY.

### Correlation

Hit correlation in Y (d0->d6)

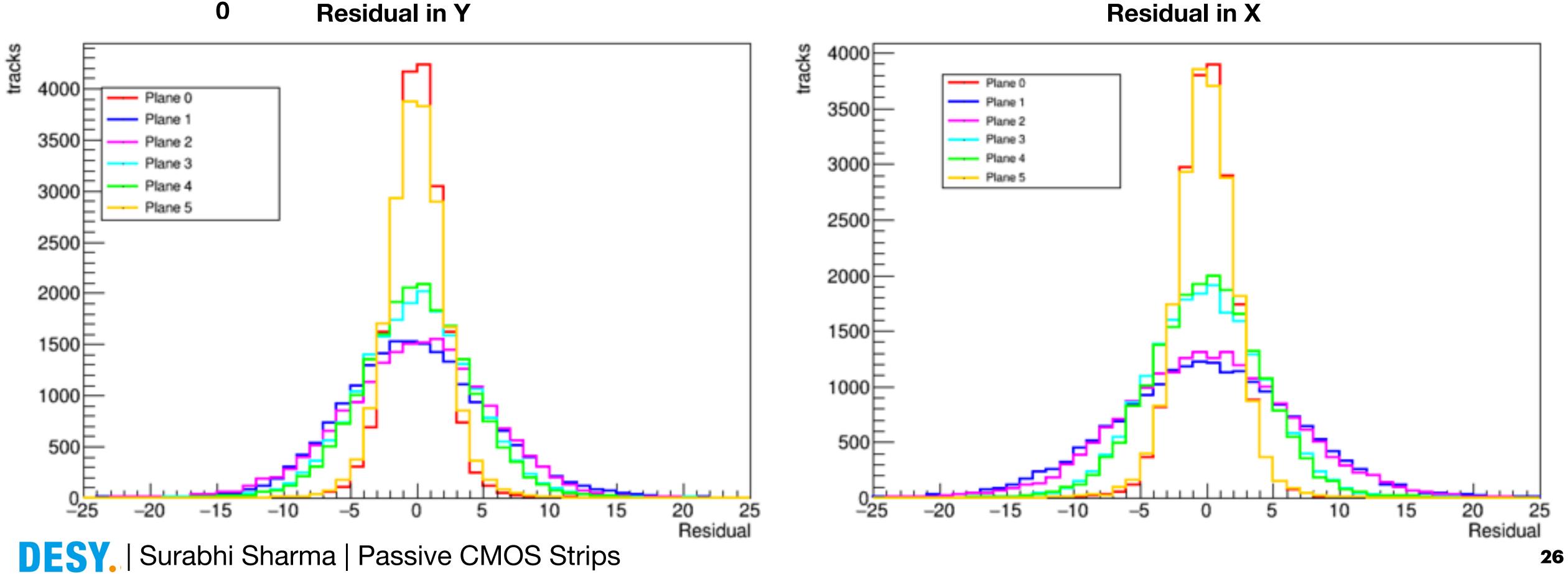

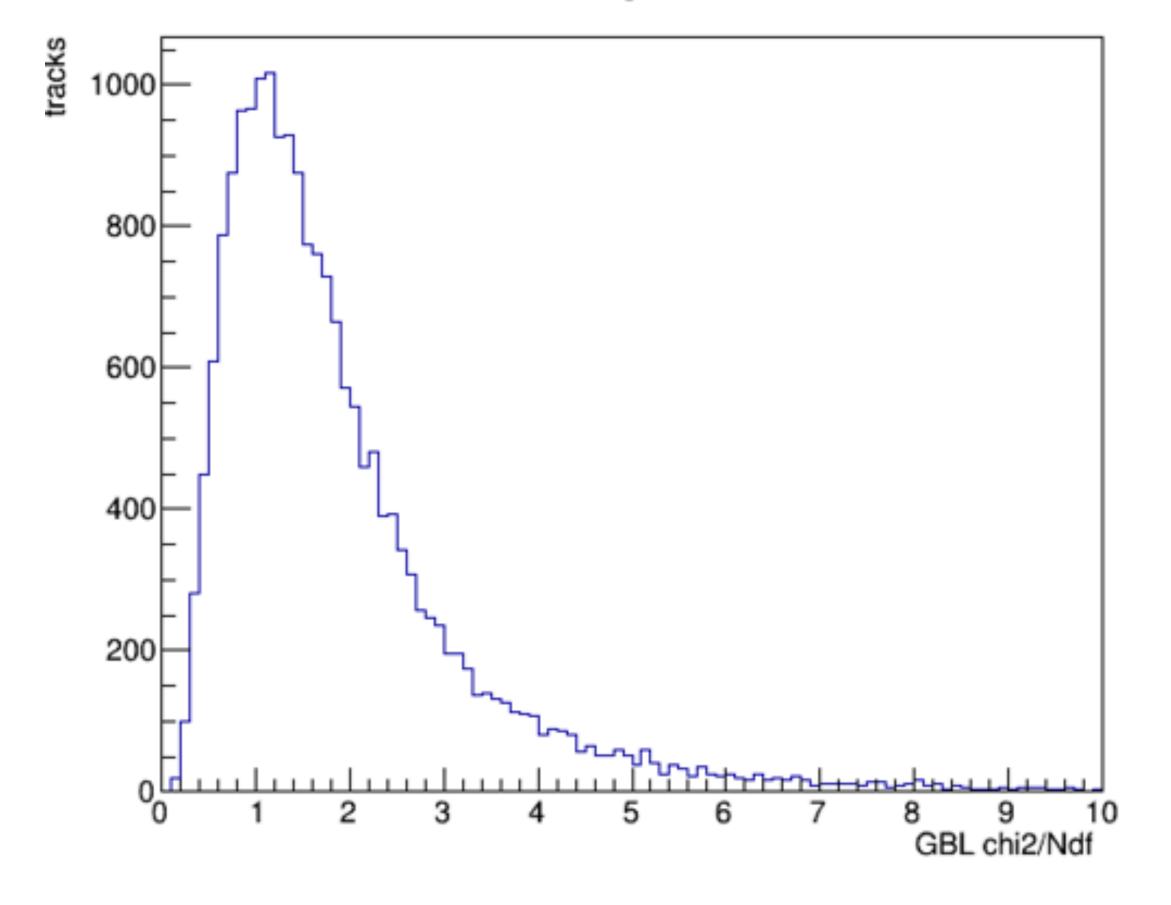

### **Tracks Parameters**

**Residual in Y**

#### **Residual in X**

#### GBL fit chi2 / degrees of freedom

**DESY** | Surabhi Sharma | Passive CMOS Strips

#### **Tracks Parameters**

### **Tracks Parameters**

$Hit Efficiency = \frac{Fraction \ of \ tracks \ with \ associated \ hits \ on \ the \ DUT}{T}$

**DESY** | Surabhi Sharma | Passive CMOS Strips

All measurements are performed at -16° C

- Signal plot for LD30 and Regular sensor No charge collection is seen for Regular sensor

- Surabhi Sharma | Passive CMOS Strips DESY.

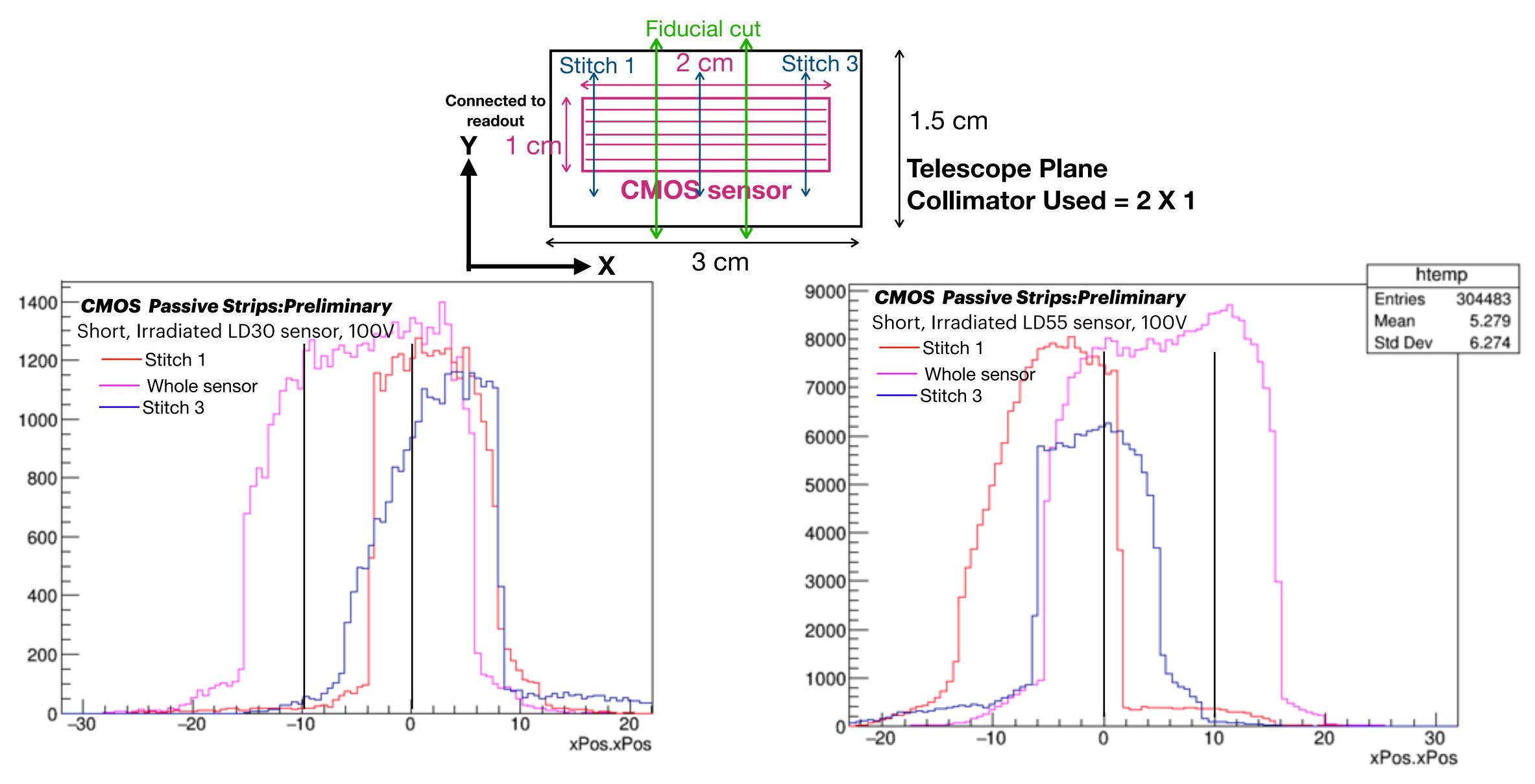

### Tracks Cuts across strips

**DESY** | Surabhi Sharma | Passive CMOS Strips