## Nikhef Digital Pixel Test Structure characterization with the ALPIDE telescope

Roberto Russo, on behalf of ALICE BTTB10, 22.06.2022

#### Motivation

ALIC

- Development and characterization of sensors for the ALICE Inner Tracking System (ITS) upgrade

- Monolithic CMOS pixel sensors (MAPS) with small collection electrode

- Low noise, low power consumption, reduced material budget

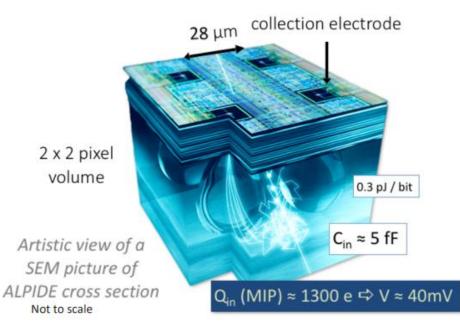

- ALPIDE (ALice Pixel DEtector) chip (180 nm CMOS MAPS) is the base of the current tracker

- > It is the starting point for the ITS3 development

#### Motivation

- Development and characterization of sensors for the ALICE Inner Tracking System (ITS) upgrade

- Monolithic CMOS pixel sensors (MAPS) with small collection electrode

- Low noise, low power consumption, reduced material budget

- ALPIDE (ALice Pixel DEtector) chip (180 nm CMOS MAPS) is the base of the current tracker

- ➢ It is the starting point for the ITS3 development

- Target technology for ITS3 is 65 nm CMOS process

(12 inch wafers)

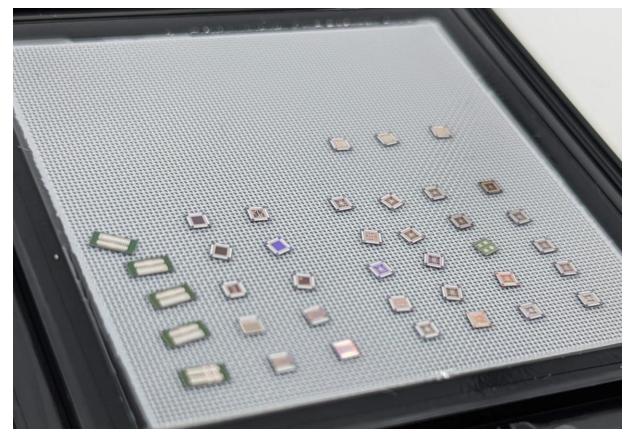

- Several test structures available for testing

O APTS, DPTS, CE65, ...

- Intensive laboratory and testbeam characterization effort

- Flexible and advanced tools required

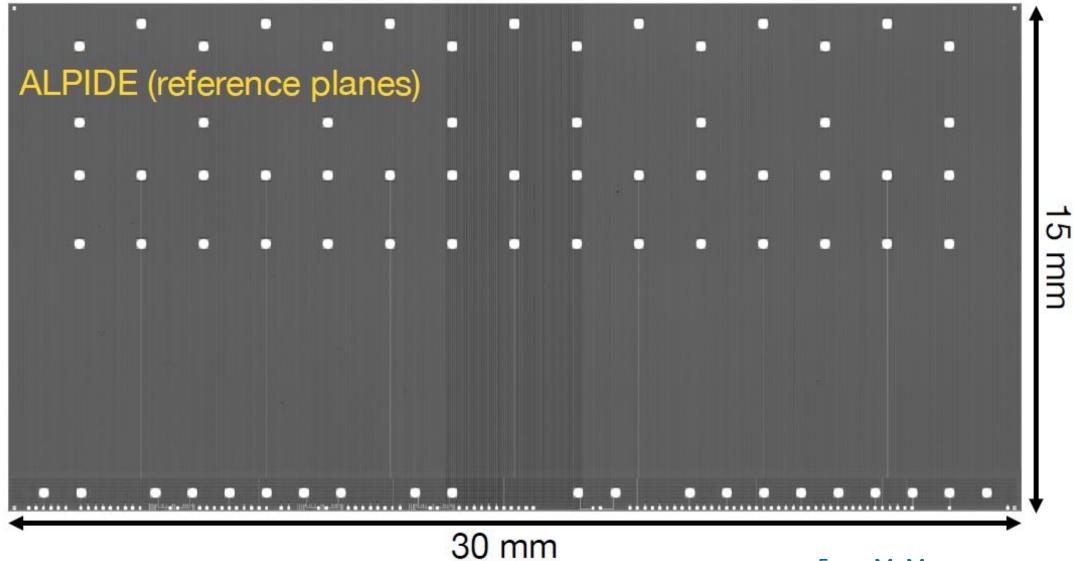

## The ALPIDE telescope

- Based on the ALPIDE chip

- $1024 \times 512$  pixels, 29 µm  $\times$  27 µm pixel size

- Reduced material budget (50 μm of silicon per plane)

- 5 μm spatial resolution

- Detection efficiency above 99.99%

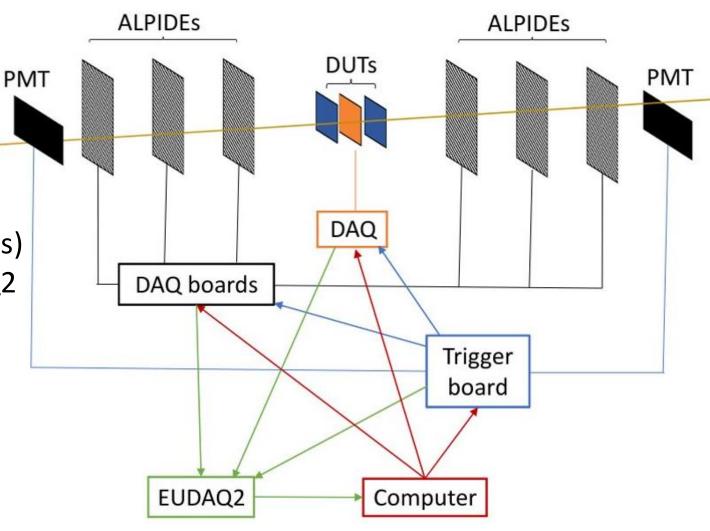

### The ALPIDE telescope

ALICE

- Based on the ALPIDE chip

- 1024 × 512 pixels, 29 μm × 27 μm pixel size

- Reduced material budget (50 μm of silicon per plane)

- 5 μm spatial resolution

- Detection efficiency above 99.99%

- 6 ALPIDE tracking planes as standard configuration

- 3 planes before the Device(s) Under Test (DUT)

- 3 planes after the DUT(s)

- 2.5 cm distance between planes

- 3 µm tracking resolution on the DUT plane

- Designed for high flexibility and portability

40 cm

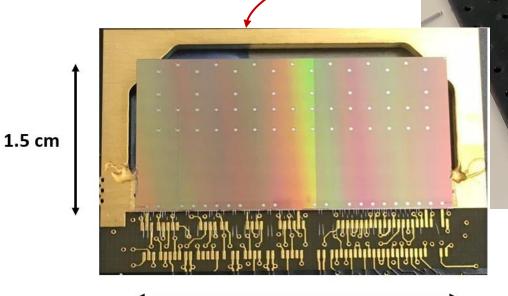

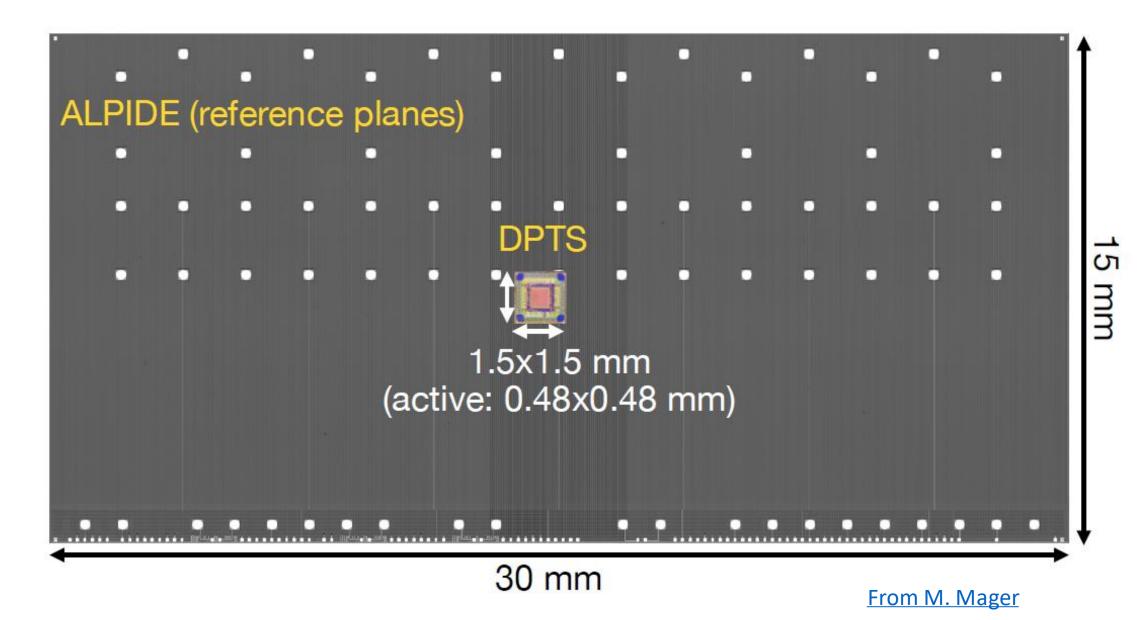

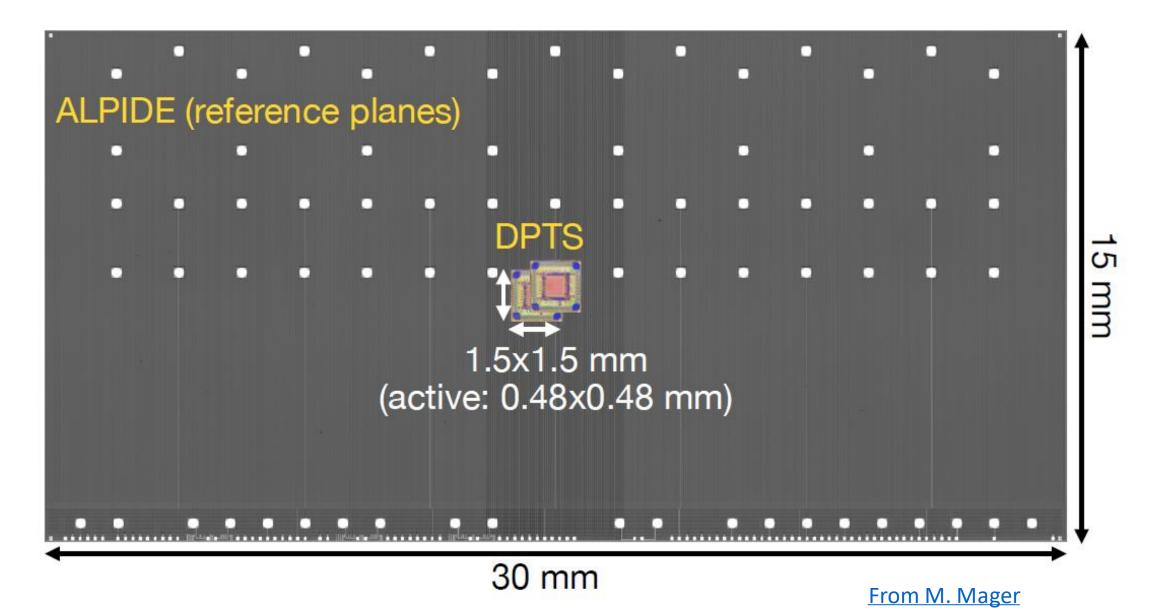

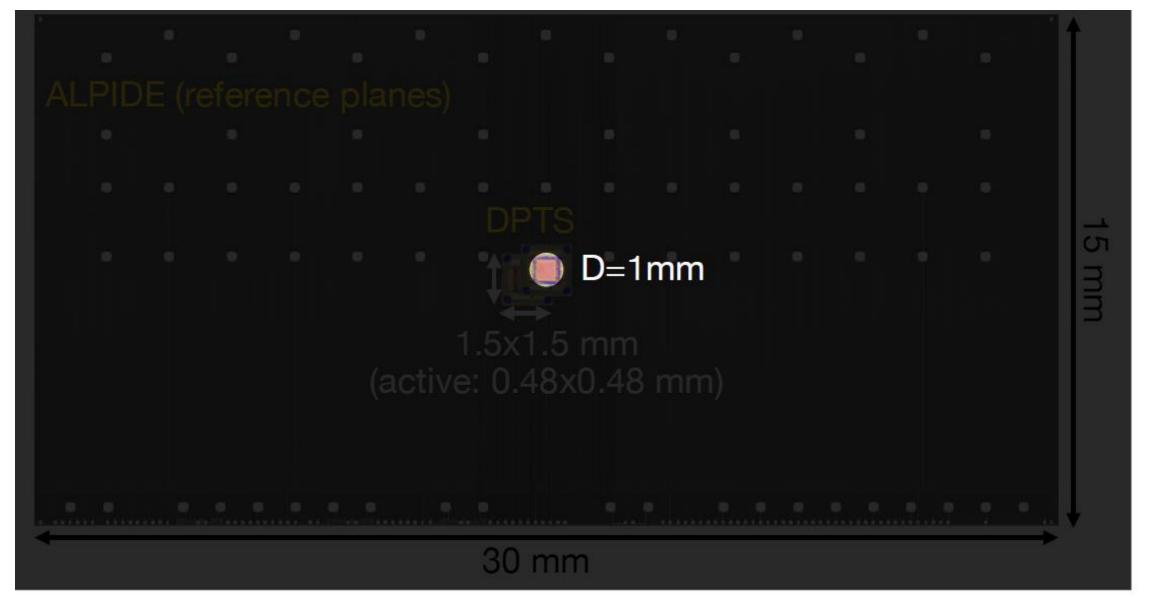

## Digital Pixel Test Structure (DPTS)

- Test structure of the first chips submission in TPSCo (Tower Partners Semiconductor Co) 65 nm CMOS imaging process

- $32 \times 32$  pixels, 15 µm pixel pitch

- 50 µm silicon thickness

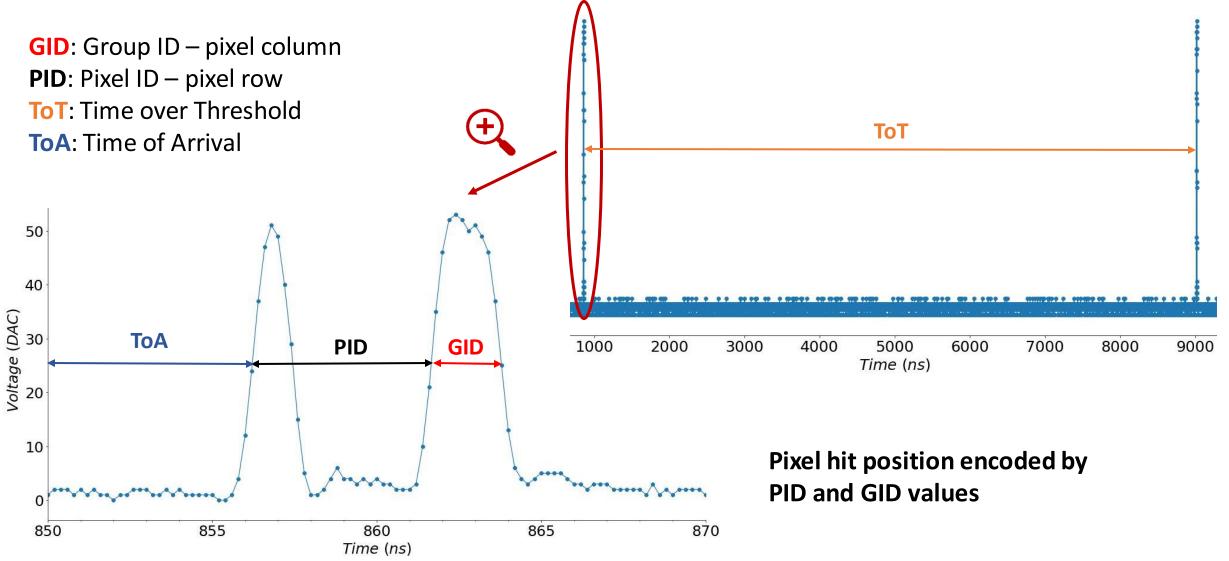

- Asynchronous digital readout with Time over Threshold (ToT) information

- Time-based encoding of the hit position

1.5 mm (active 0.48 mm)

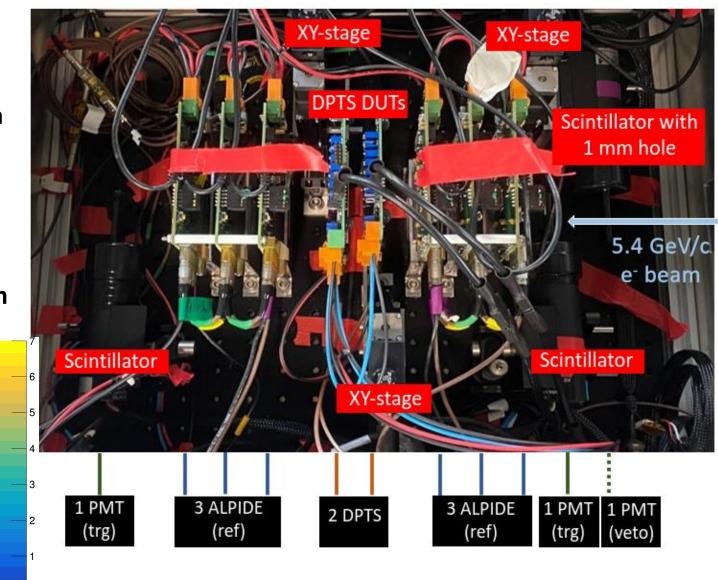

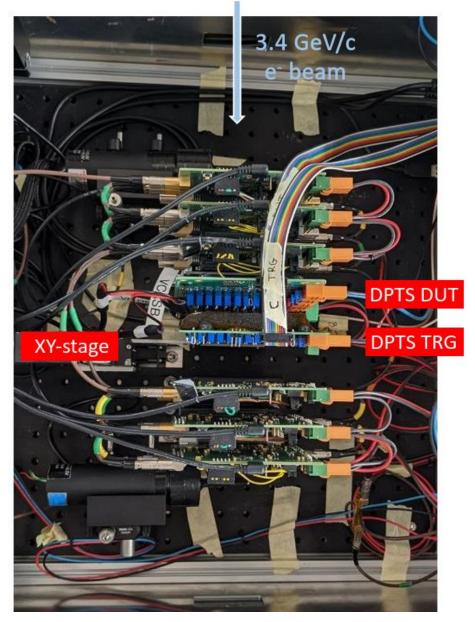

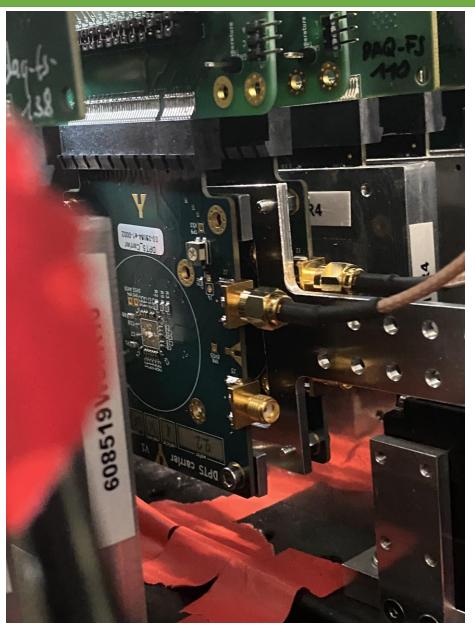

#### Testbeam setup – DESY September 2021

- 2 DPTS as DUTs

- New devices (not irradiated) at standard operation conditions (-1.2 V back bias)

- Scintillator with 1 mm hole (veto) to trigger on a narrower beam spot

- Moving stages to align hole scintillator and DUTs

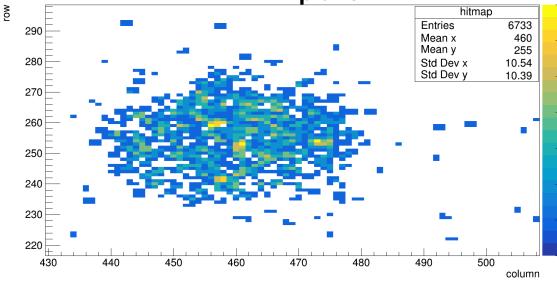

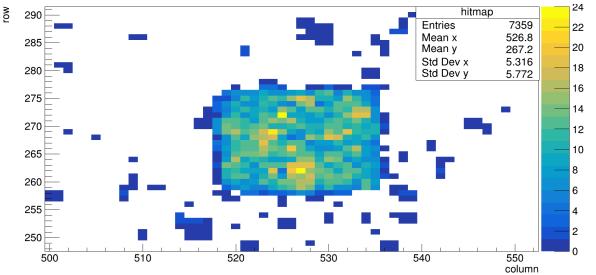

Scintillator hole as seen by the closest upstream ALPIDE plane

#### Testbeam setup – DESY March 2022

ALICE

- DPTS DUT

- > Different levels of irradiations at varying operation parameters

- One DPTS as trigger

- Moving stage to align DPTS trigger

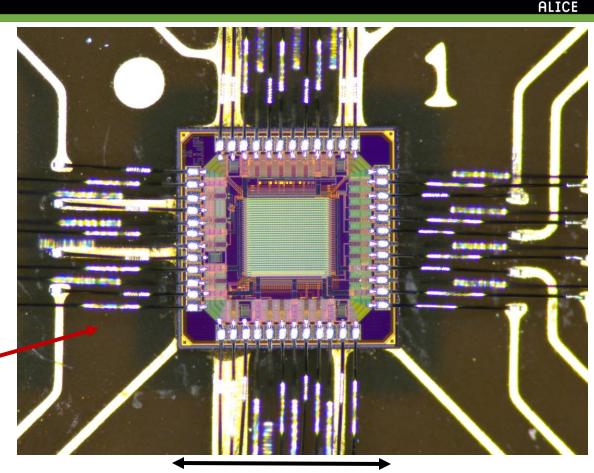

#### DPTS trigger as seen by the closest upstream ALPIDE plane

#### Data acquisition and analysis

- DPTSs digital outputs are read out with a PC oscilloscope (picoscope)

- ALPIDE planes and picoscope are controlled and data acquired by using EUDAQ2

https://github.com/eudaq/eudaq

• Analysis is conducted with Corryvreckan

https://gitlab.cern.ch/corryvreckan/corryvreckan

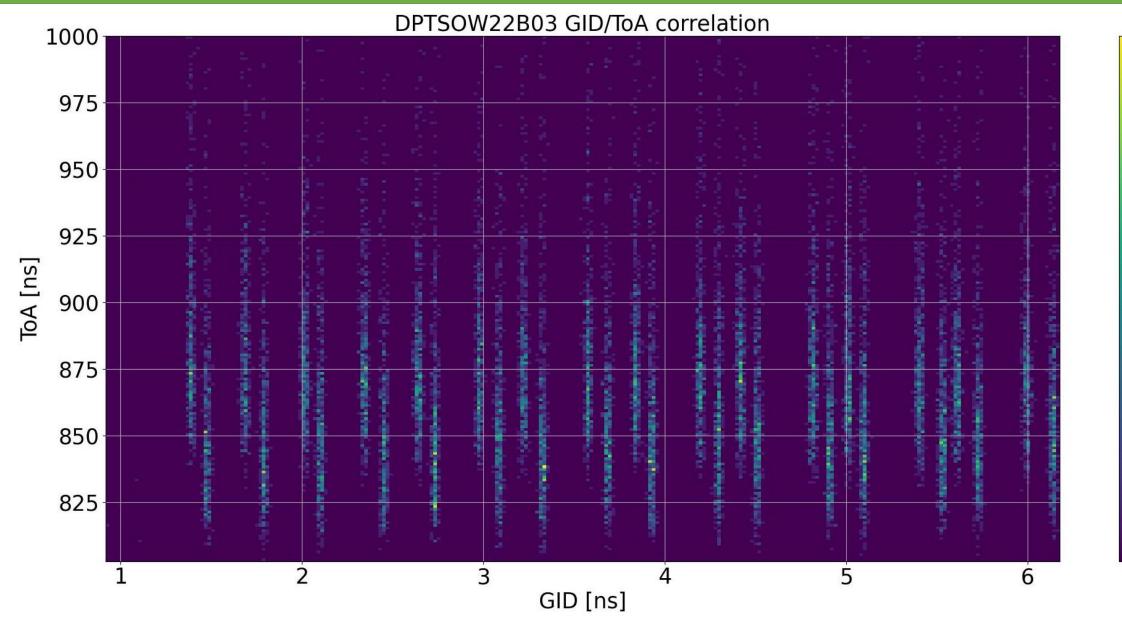

#### **DPTS Readout features**

ALICE

• The hits from all the pixels are digitized and conveyed by the readout into a single digital output

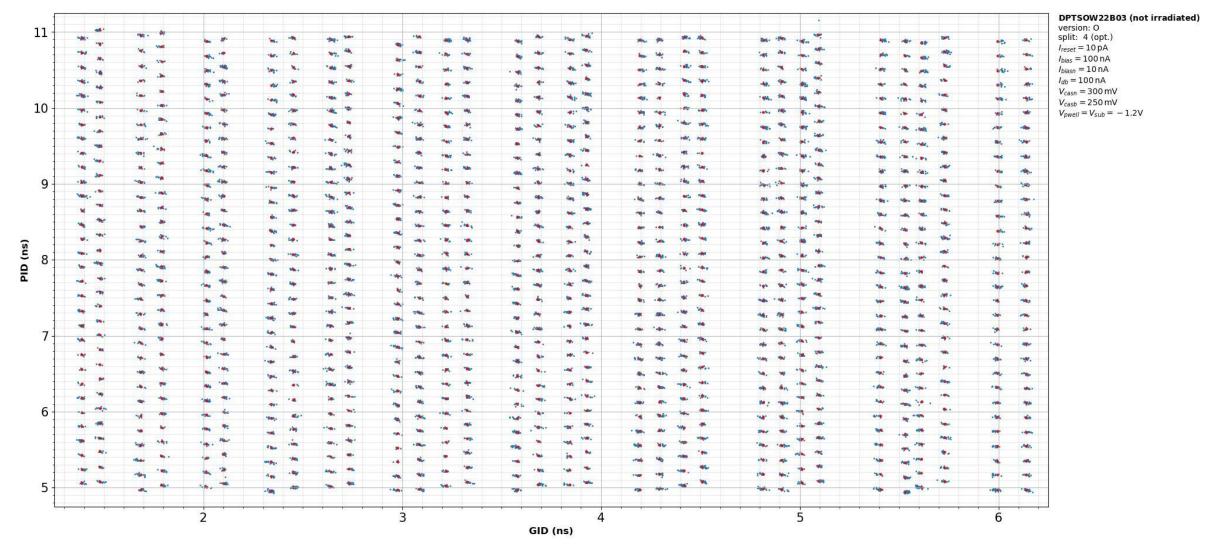

#### Time to position decoding map

- Additional calibration file passed to Corryvreckan to address DPTS pulses decoding

- For each pulse, GID and PID are measured and hit is assigned to a pixel according to nearest neighbor logic

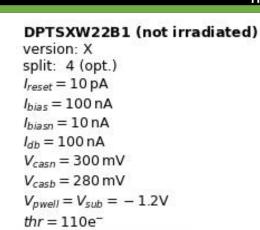

#### Spatial residuals

- DESY September 2021 data: DPTSXW22B1, standard operation conditions

- Track selection:  $\chi^2/n_{dof} < 5$

- Spatial resolution O(4.3 μm)

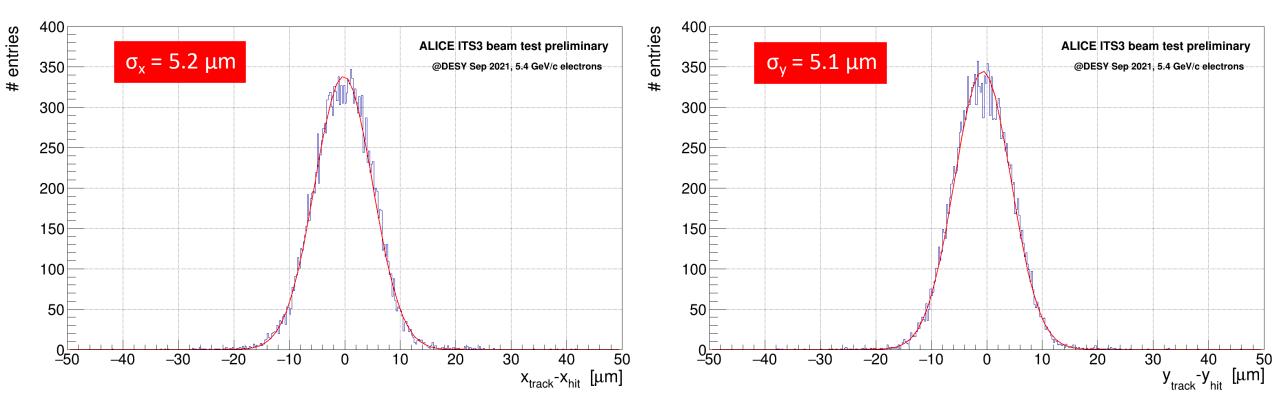

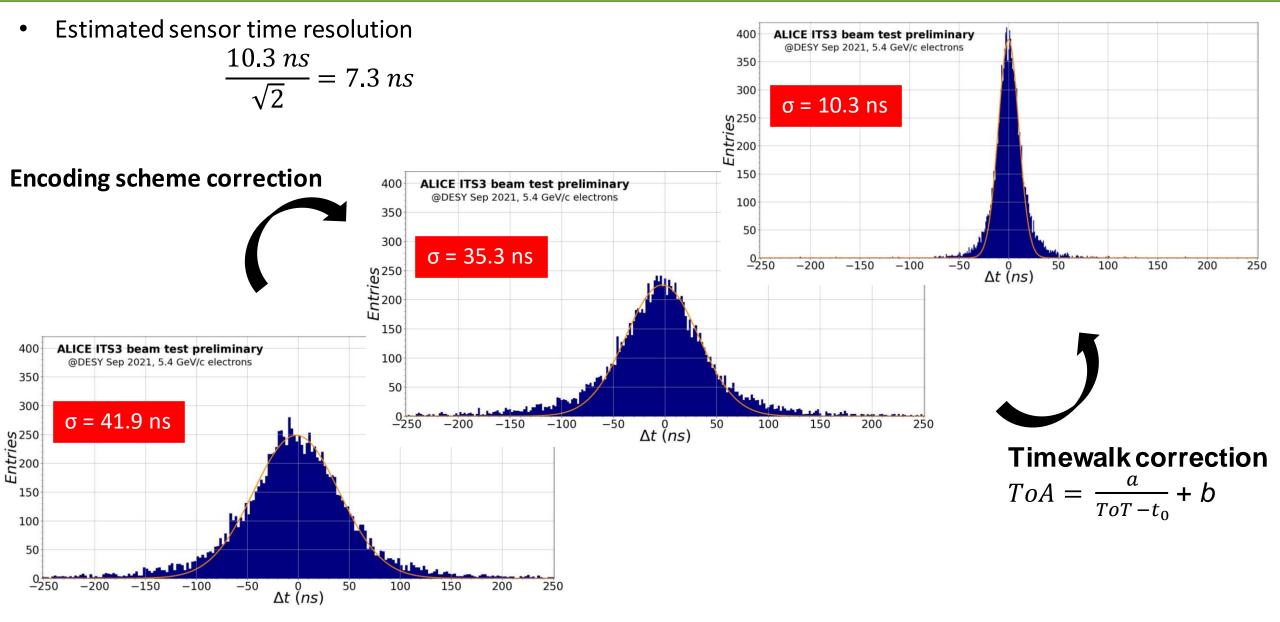

#### Timing resolution - analysis

- DESY September 2021 data

- No timing layer in the ALPIDE telescope

- Only tracks associated to both DUT are considered

- Track selection:  $\chi^2/n_{dof} < 5$

- The timestamp is given by the Time of Arrival (ToA) of the pixel signal with respect to the trigger

- 2 timestamps per track

- Time residuals distribution = ToA DPTS1 ToA DPTS2

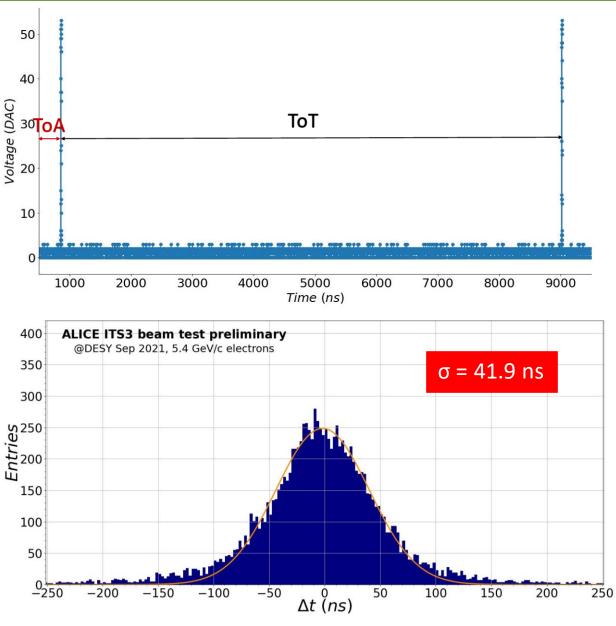

- Corrections to be performed

- Pixel encoding scheme

- Timewalk correction

#### Timing resolution - corrections

Digital Pixel Test Structure characterization with the ALPIDE telescope

ALICE

#### Timing resolution - results

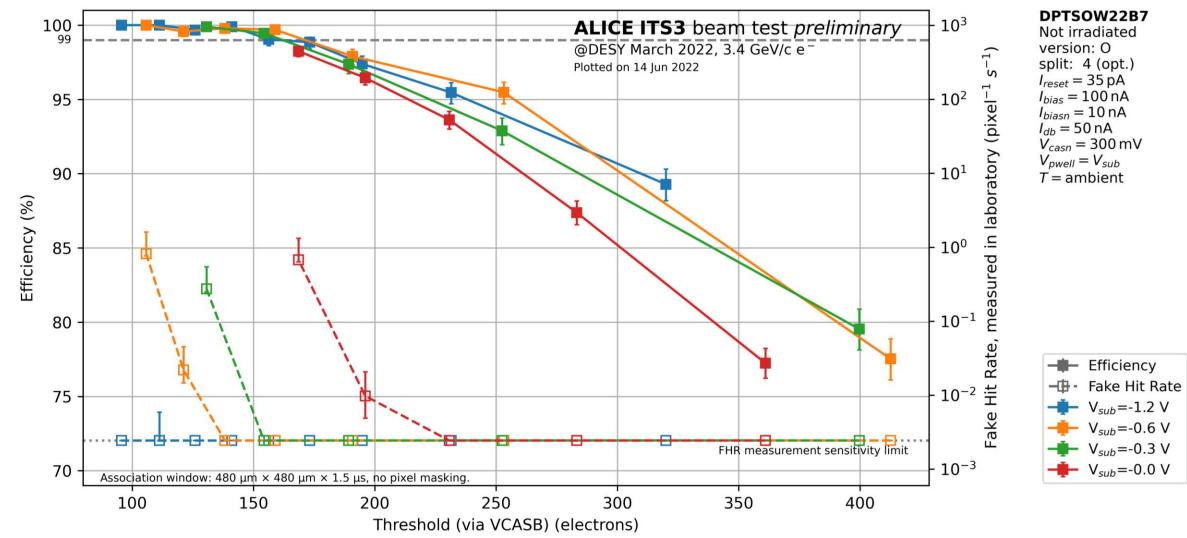

#### **Detection efficiency**

- DESY March 2022 data: DPTSOW22B7, operation condition scan at room temperature

- Efficiency above 99.7% below 150 e<sup>-</sup> threshold at -1.2 V back bias

#### Summary

- DPTS is a MAPS fabricated in 65 nm CMOS imaging sensor technology

- Chip thoroughly tested during several testbeam campaigns

- Non-irradiated device under standard operation conditions:

- > Spatial residuals  $O(5 \mu m)$

- Time residuals O(10 ns)

- Detection efficiency above 99.7%

- Performance figures of first prototype are very promising for the ITS3 requirements

#### Outlook

- Irradiated devices analysis ongoing (NIEL irradiation levels from 10<sup>13</sup> to 10<sup>15</sup> 1 MeV n<sub>eq</sub> cm<sup>-2</sup>)

- In-pixel efficiency studies

- Another testbeam (at CERN PS) data taking has just concluded:

- > Studied chip behavior under controlled temperature

- ➢ Studied new operation conditions (larger back-bias range, up to −3 V)

- Analysis ongoing

#### Outlook

- Irradiated devices analysis ongoing (NIEL irradiation levels from 10<sup>13</sup> to 10<sup>15</sup> 1 MeV n<sub>eq</sub> cm<sup>-2</sup>)

- In-pixel efficiency studies

- Another testbeam (at CERN PS) data taking has just concluded:

- Studied chip behavior under controlled temperature

- ➢ Studied new operation conditions (larger back-bias range, up to −3 V)

- Analysis ongoing

Big thank you to the DESY testbeam support team!

The measurements leading to the shown results have been performed at the Test Beam Facility at DESY Hamburg (Germany), a Member of the Helmholtz Association (HGF)

# Additional slides

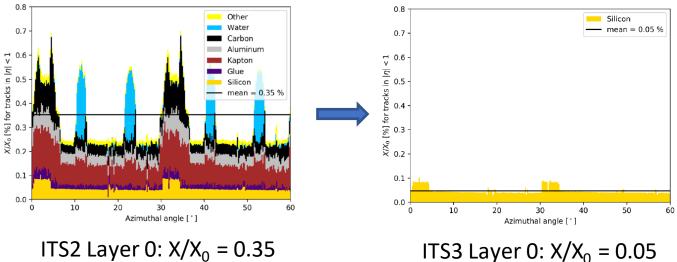

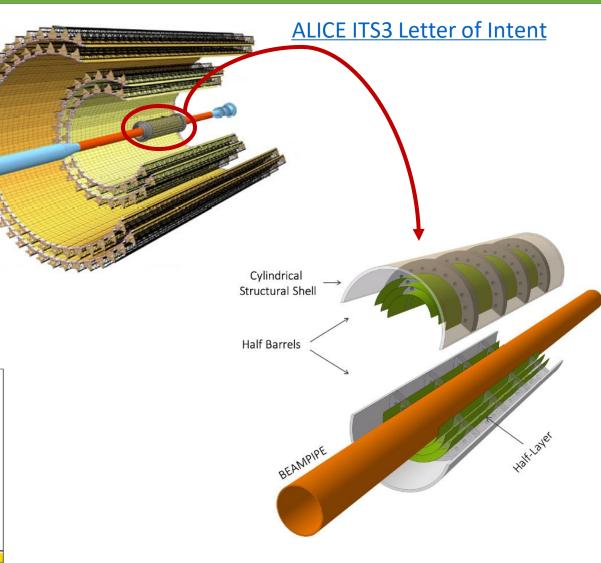

## ALICE Inner Tracking System 3 (ITS3)

- Improve vertexing at high rate and low transverse momentum

- Replace the 3 layers of the ITS Inner Barrel

- Fully cylindrical layers with radii of 18/24/30 mm around the beam pipe

- Design based on wafer-scale bent MAPS thinned down to 20-40 μm

- Target technology: 65 nm CMOS sensors

- "Moderate" radiation hardness requirements

- > NIEL: 10<sup>14</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup>

- ➤ TID: 10 MRad

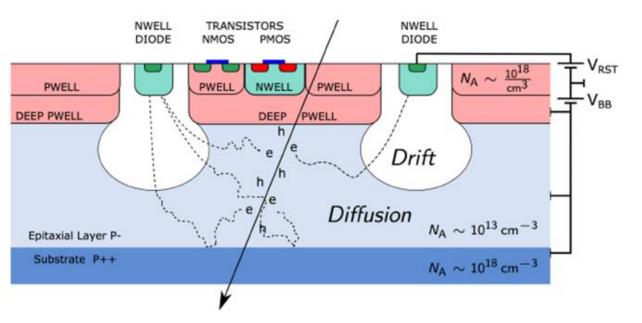

- TowerJazz 180 nm CMOS Standard Imaging Process pixel sensor:

- High-resistivity (> 1 kΩ·cm) p-type epitaxial layer (25 μm) on p-type substrate

- 2 μm diameter n-well electrode, ~ 5 pF input capacitance

- 50 μm overall sensor thickness

- Monolithic design:

- In pixel amplification, discrimination, 3 hit storage registers

- Ultra-low power consumption:

- ➢ 40 nW/pixel

- 20 mW/cm<sup>2</sup>

- High hit rate transmission:

- ➤ ~6 MHz/cm<sup>2</sup> hit rate chip output data transfer

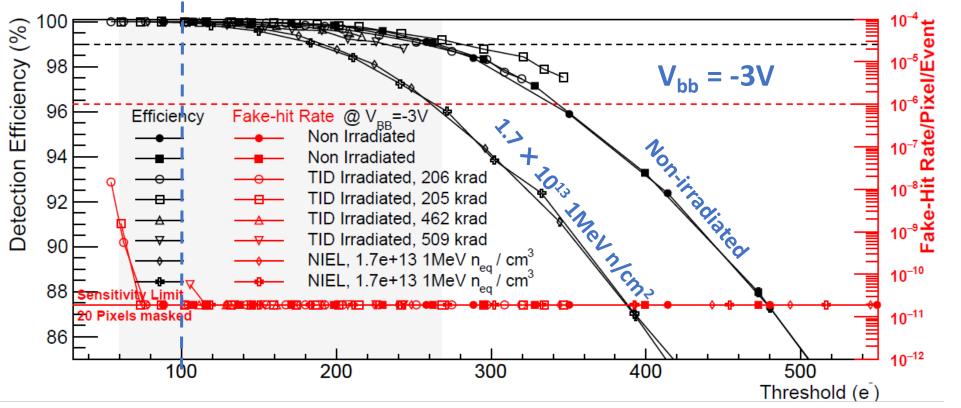

#### ALPIDE performance figures

- Measured with 6 GeV/c pion beam

- At 100 e<sup>-</sup> of operation threshold and  $V_{bb} = -3$  V:

- Detection efficiency above 99.99%

- > Fake hit rate < 2 ×  $10^{-11}$  pixel hits/event

- Irradiated chips performance is comparable with not-irradiated chips

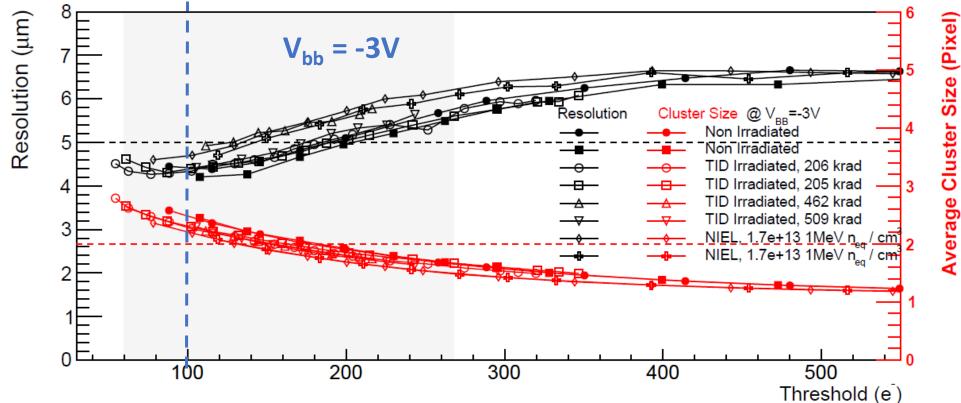

#### ALPIDE performance figures

- Measured with 6 GeV/c pion beam

- At 100 e<sup>-</sup> of operation threshold and  $V_{bb} = -3$  V:

- $\succ$  Spatial resolution below 5  $\mu$ m

- Not irradiated and TID/NIEL chips show similar performance

#### The ALPIDE telescope

- High flexibility and portability

- 6 ALPIDE tracking planes as standard configuration

- ALPIDE DAQ board based on FPGA

- Custom trigger board

- Movable XY stages for DUT(s) and PMT(s)

- Data acquisition integrated into EUDAQ2

#### Trigger on veto scintillator

From M. Mager

#### Trigger on veto scintillator

#### Trigger on veto scintillator

#### From M. Mager

#### Encoding scheme time correction