# **Calorimeter Upgrade Meeting**

Analog Electronics COTS design

22/jun/2010

# Main ideas of COTS

- Commercial Off The Shelf

- Intended to be cheaper than ASIC

- Easy to find

- Commercially tested, no risk of mistakes in chip design

- Much faster and easyer design and test

- Not the same integration level

- Not the same flexibility

- Not the same performance

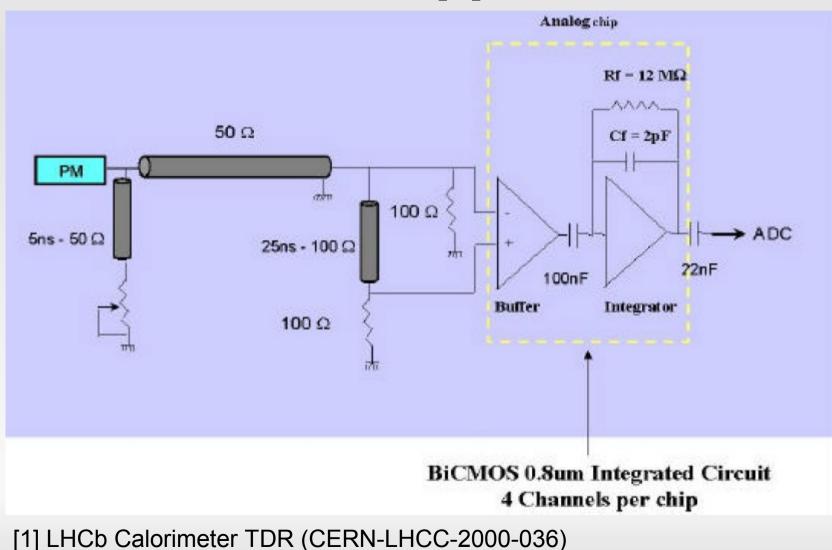

## **Current CALO reminder**

Current CALO scheme [1]

# **Current CALO reminder**

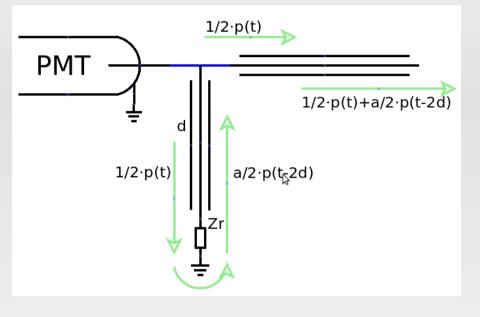

- Clipping with delay lines

- In the PMT Base

# **Current CALO reminder**

### Integration

Delayed Lines Integrator

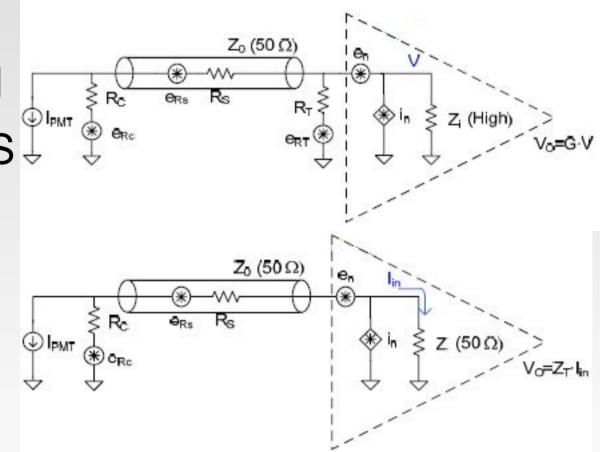

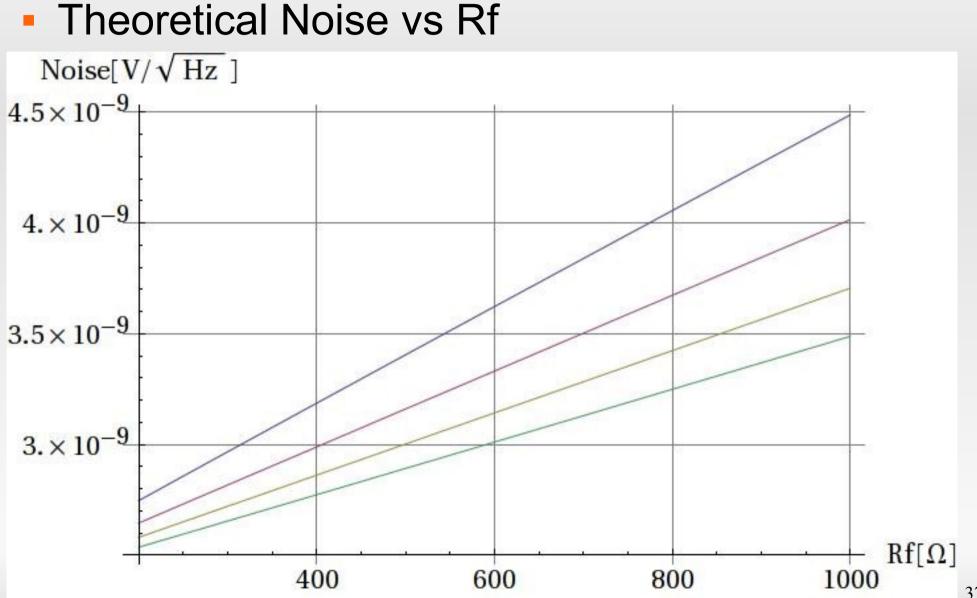

# **Noise Problematic**

- Reducing the gain in the PMTs → less signal and same noise!

- Low noise needed

- Difficult with COTS  $\downarrow$

- Noise in the

PMT base

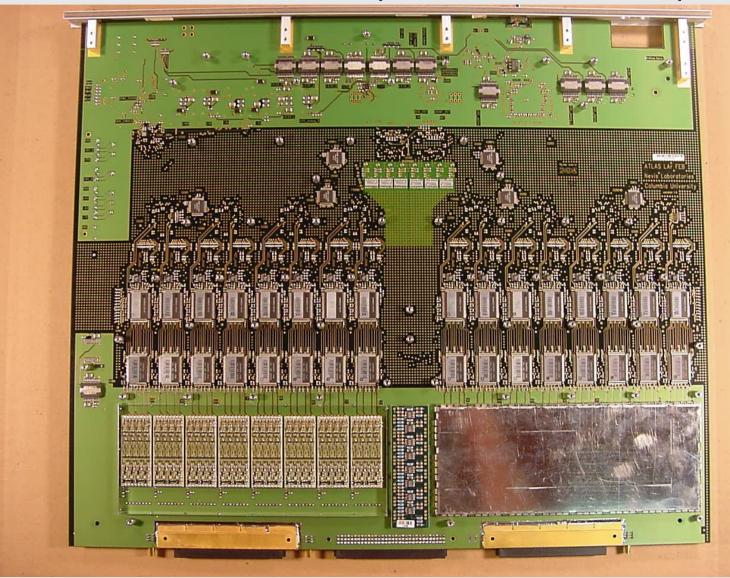

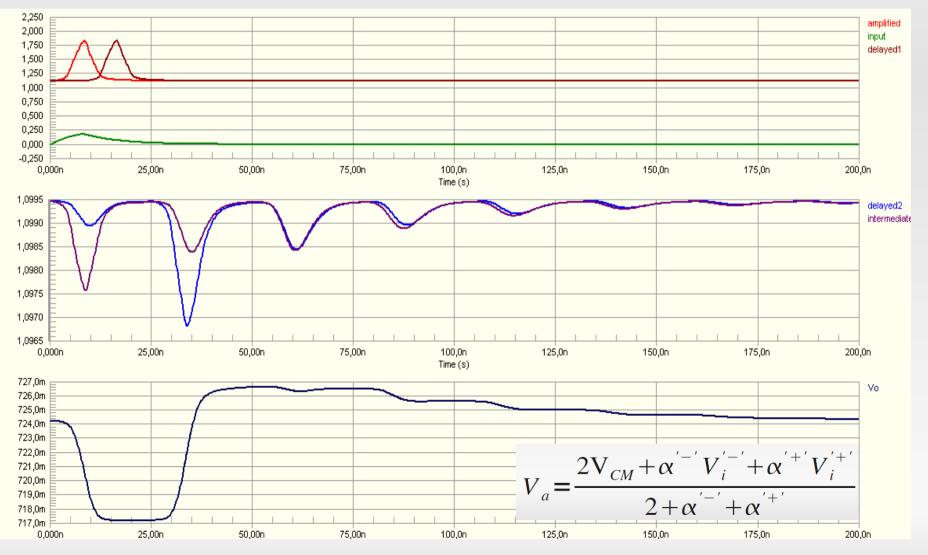

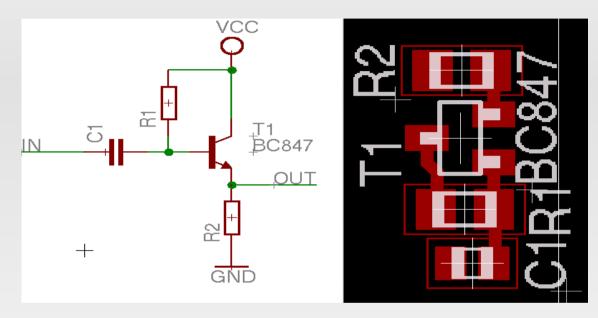

- Super Common Based Amplifier

- ATLAS LAr CALO uses one of those (4 chan)

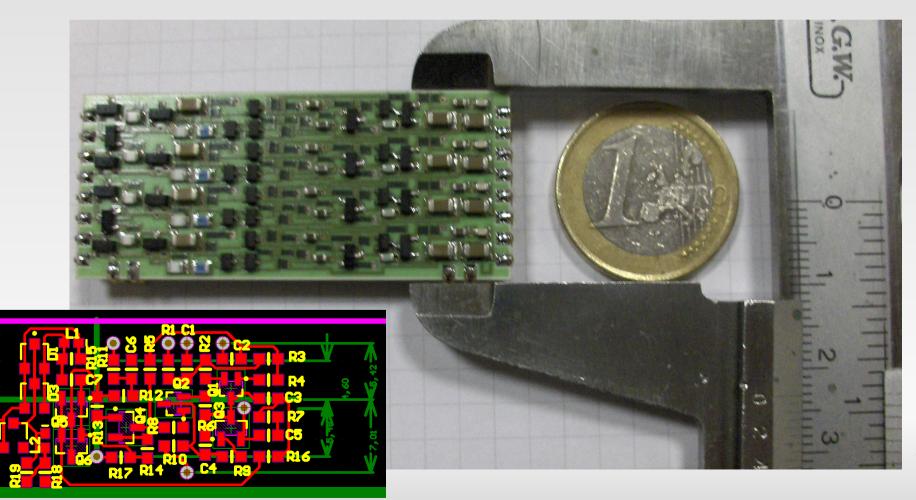

#### Space is not an issue (LAr Calo Board)

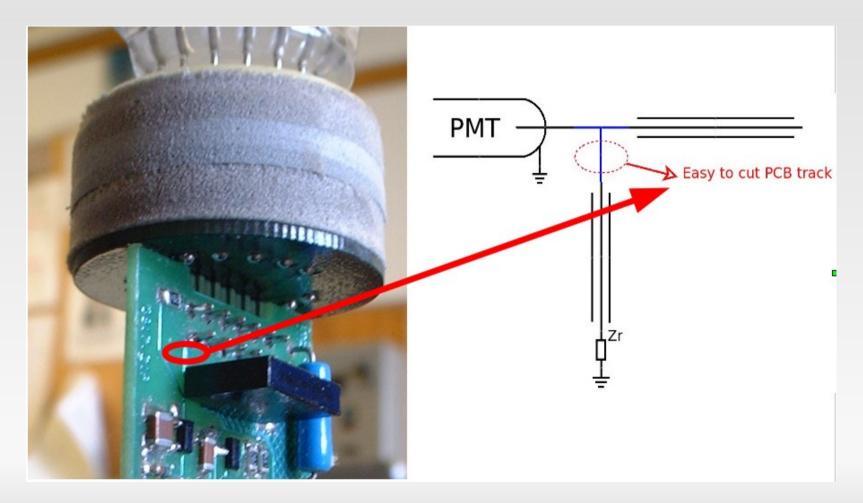

Manipulate the PMT's base to reduce noise

- Manipulate the PMT's base to reduce noise and relax system specifications

- The resistor in the PMT's base has some contribution to noise, we could get rid of it.

- Clipping in the base reduces useful signal, we would remove it.

- With greater signal the signal/noise ratio would increase.

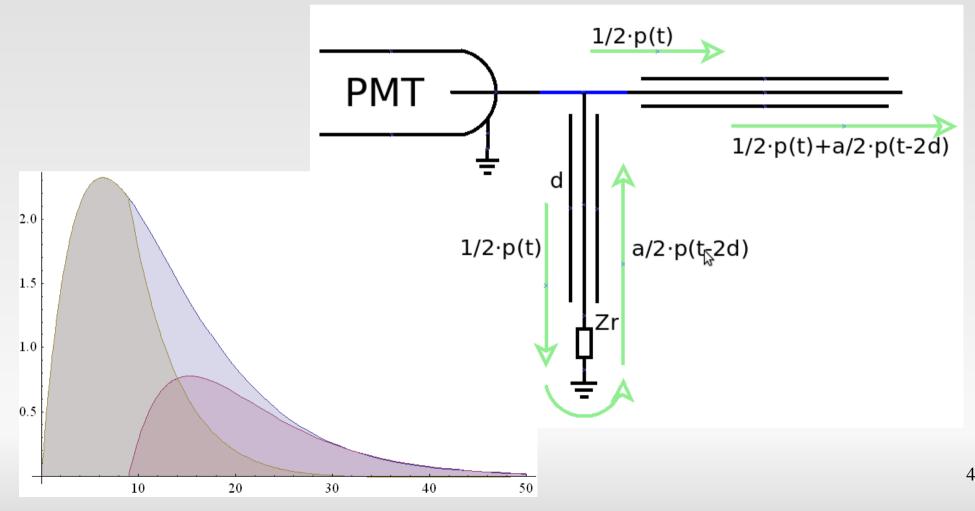

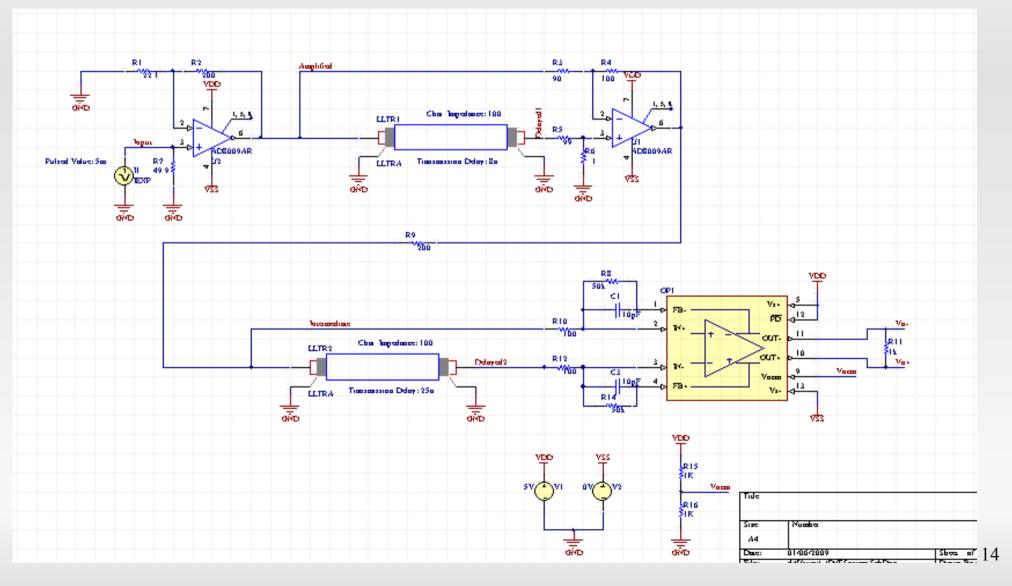

# **Different Clipping Approach**

- Clipping after amplifying

→ Impedance problem...

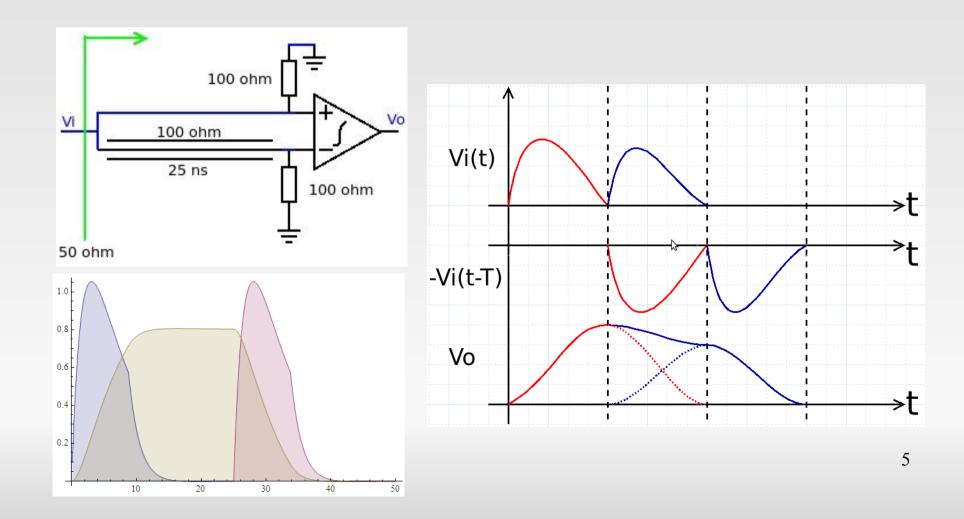

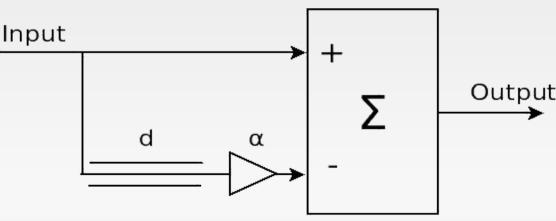

- Equivalent system found, same impulse response but no impedance problems.

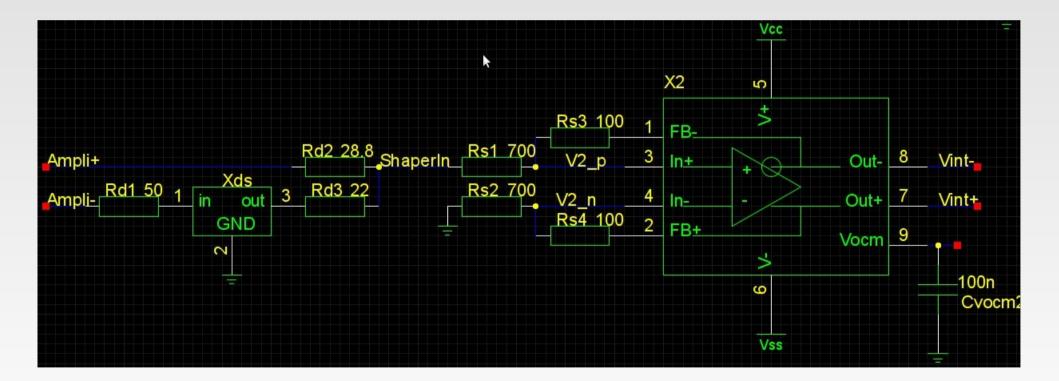

Scheme with Differential operational amplifier

#### Scheme with Differential operational amplifier

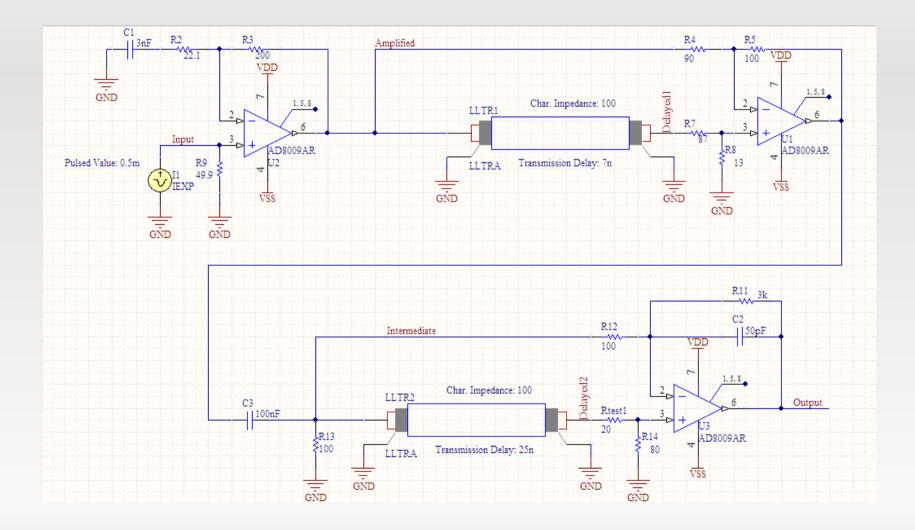

Schematic of the adaptation system

Equations of the system

$$Z_{B} = R_{B} || (r_{d} + R_{L}) (hfe + 1)$$

$$Z_{OUT} = R_{L} || r_{d} + \frac{Z_{0} || R_{B}}{hfe + 1}$$

$$r_{d} = \frac{hie}{hfe + 1}$$

$hie \approx 100$  $hfe \approx 500$  $r_d \approx 0.2$  $R_L \approx 1 \text{K5}$  $R_B \approx 416 \text{K}$

$Z_B \approx 230 \text{K}$   $Z_{OUT} \approx 2$   $Gain \approx 1$   $C \approx some \, nF$ Power Consumption  $\approx 3_{16}^{\text{mW}}$

Different approach to same idea, no loop

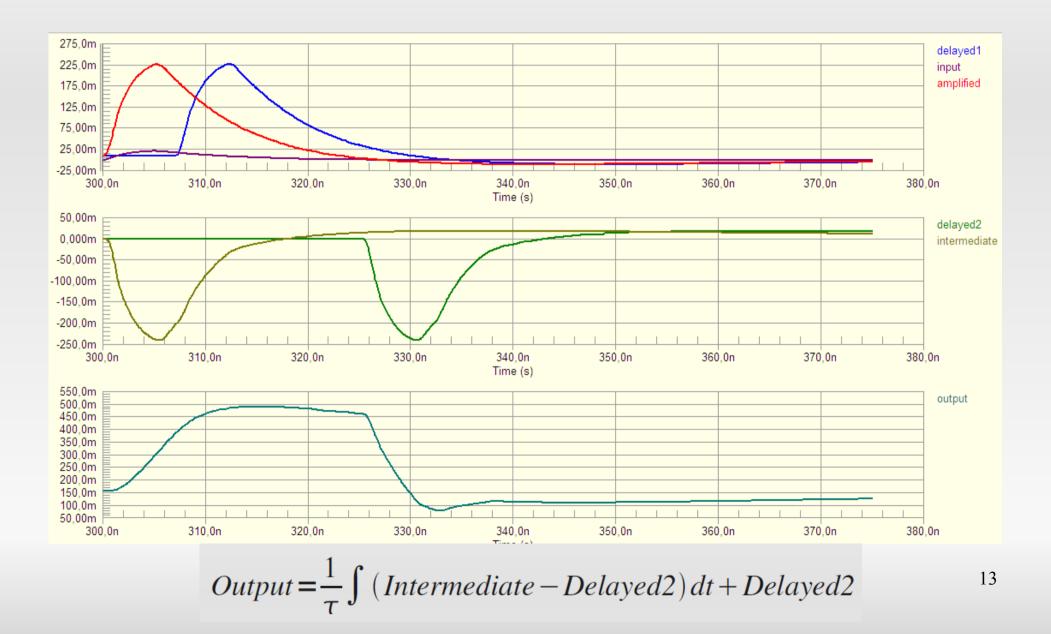

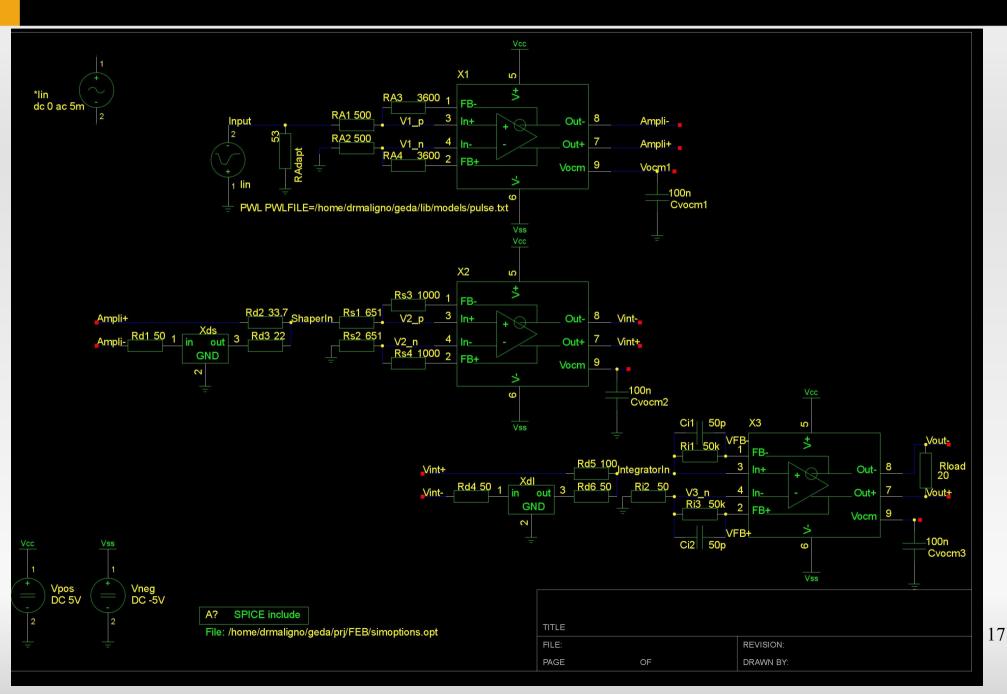

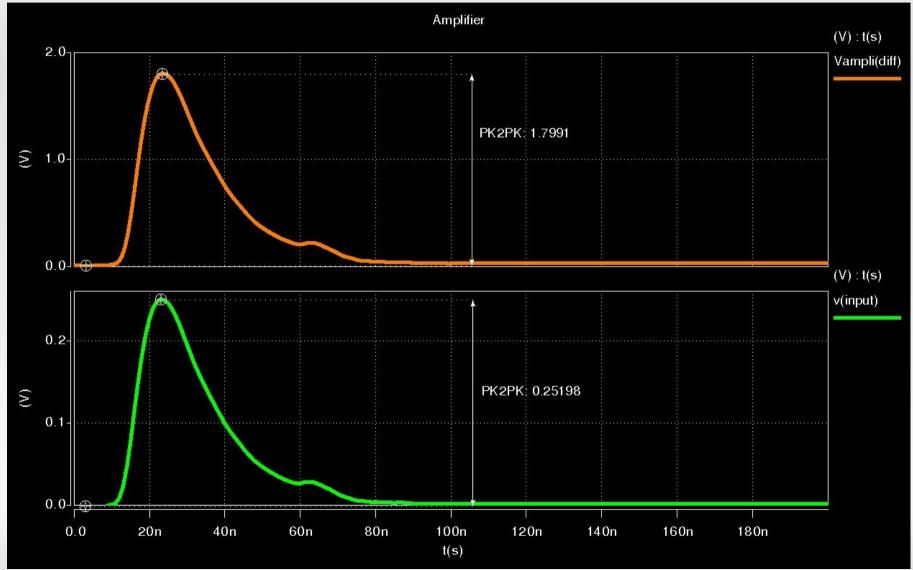

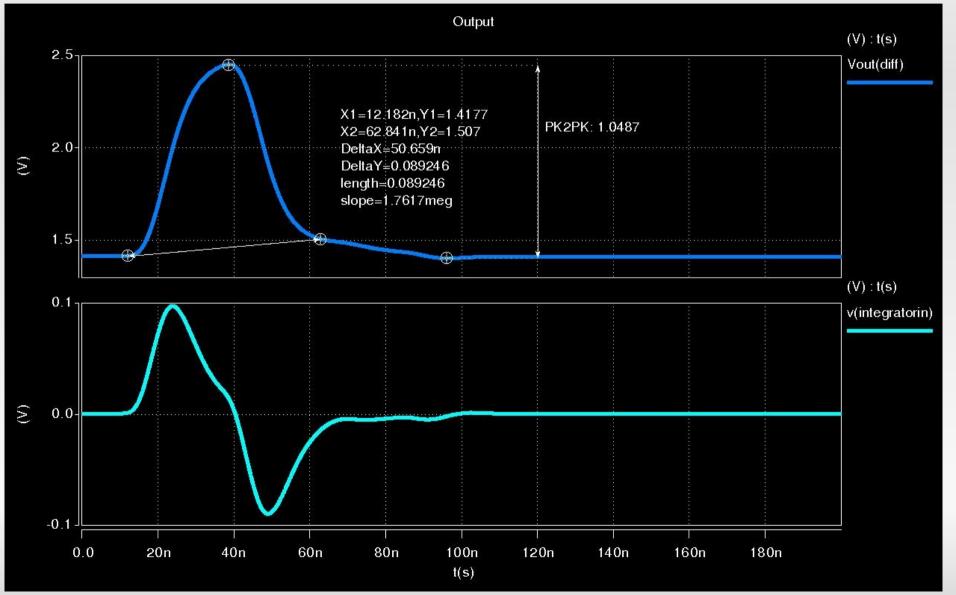

#### Amplifying Stage

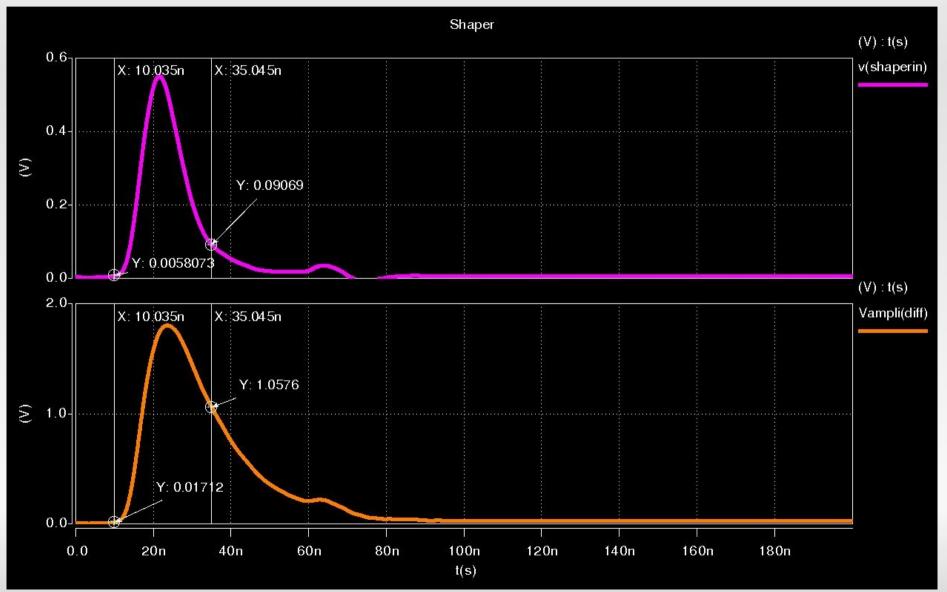

#### Clipping Stage

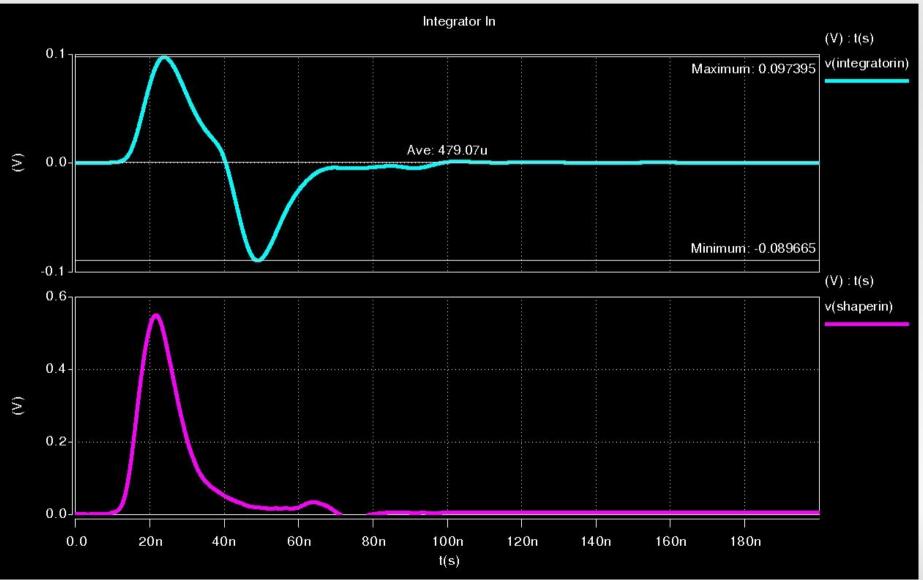

#### Integrator Input

#### Integrator Output

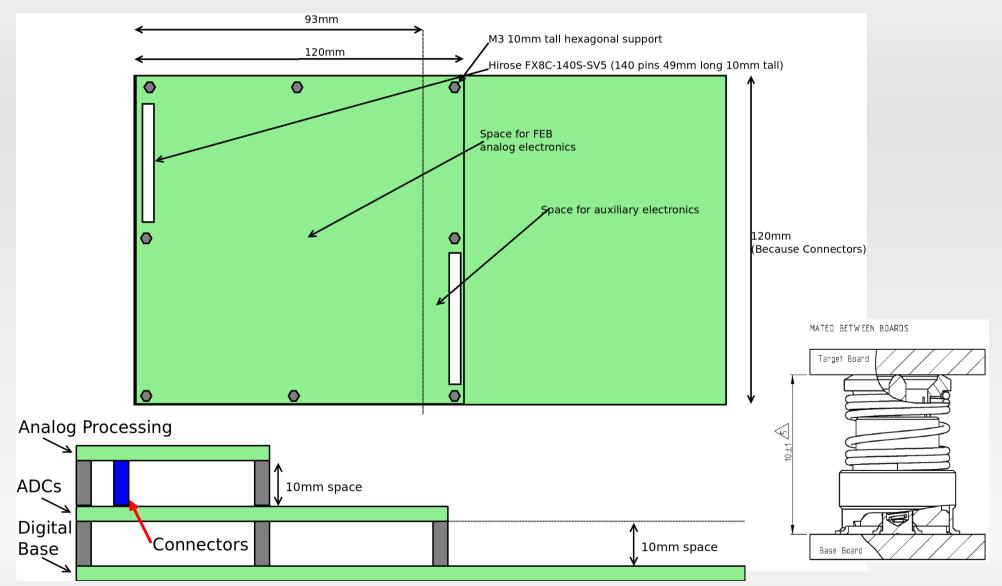

# **ADC Selection**

- In order to make the proper interface between the analogical part and the ADC it is necessary to have it previously selected.

- Our ADC needed 12 bits resolution, at least 40MHz conversion frequency and it was also desirable a small package due to space restrictions.

- The more suitable components for our application where:

- Texas Instruments ADS6122

- 1 ADC/Chip but 5x5mm only, LVDS, DDR!

- Texas Instruments ADS6222

- 2 ADC/Chip, LVDS, DDR!

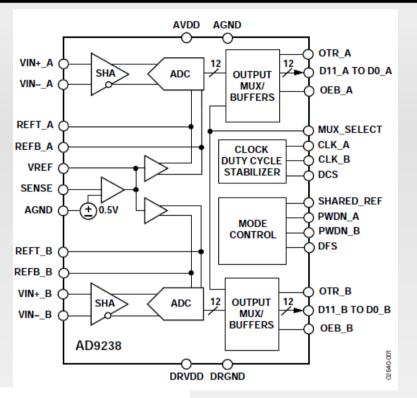

- Analog Devices AD9238

- 2 ADC/Chip, LVTTL.

# **ADC Selection**

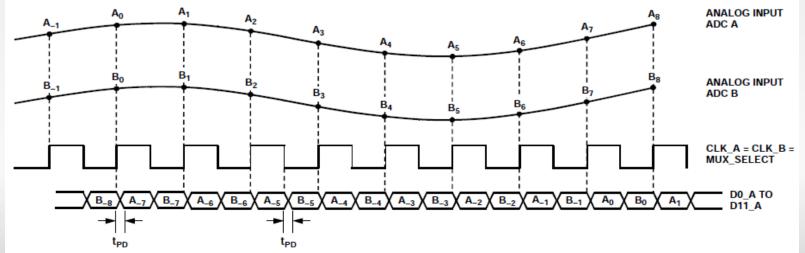

- Analog Devices AD9238

- One sampling clock per channel

- Optional multiplexing

- No RAM configuration

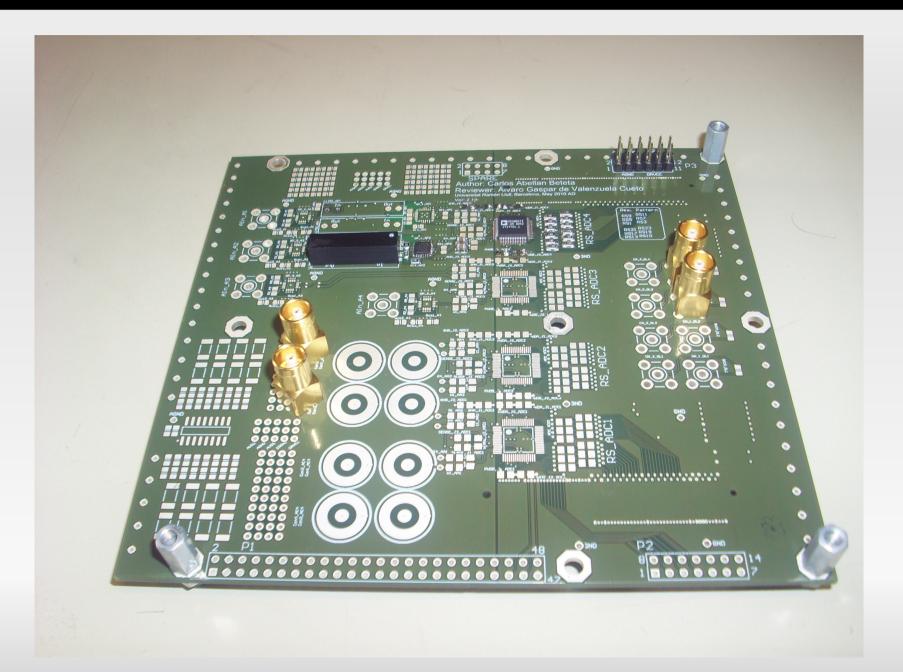

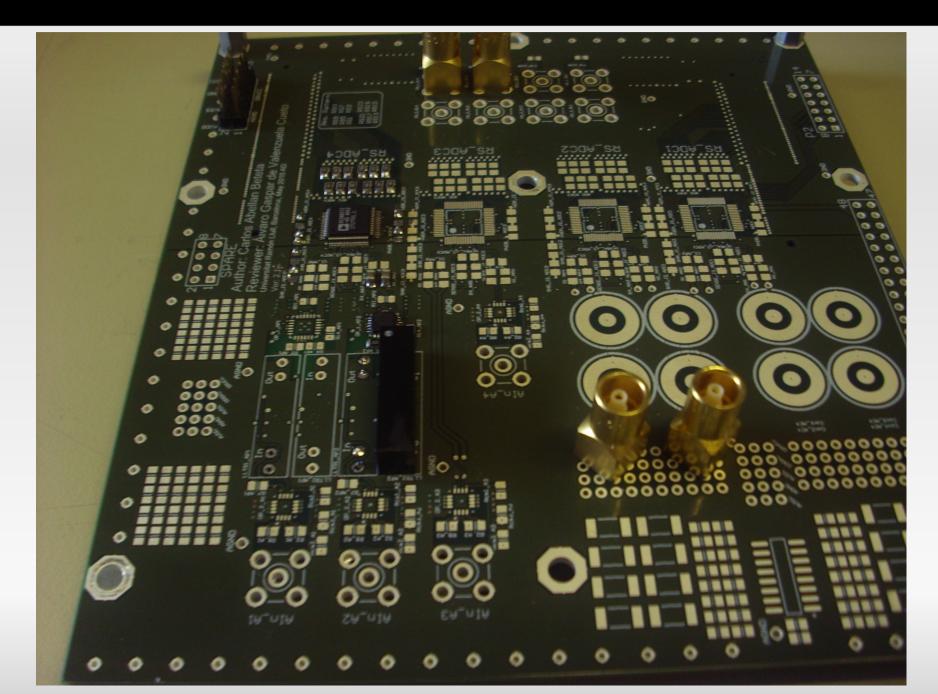

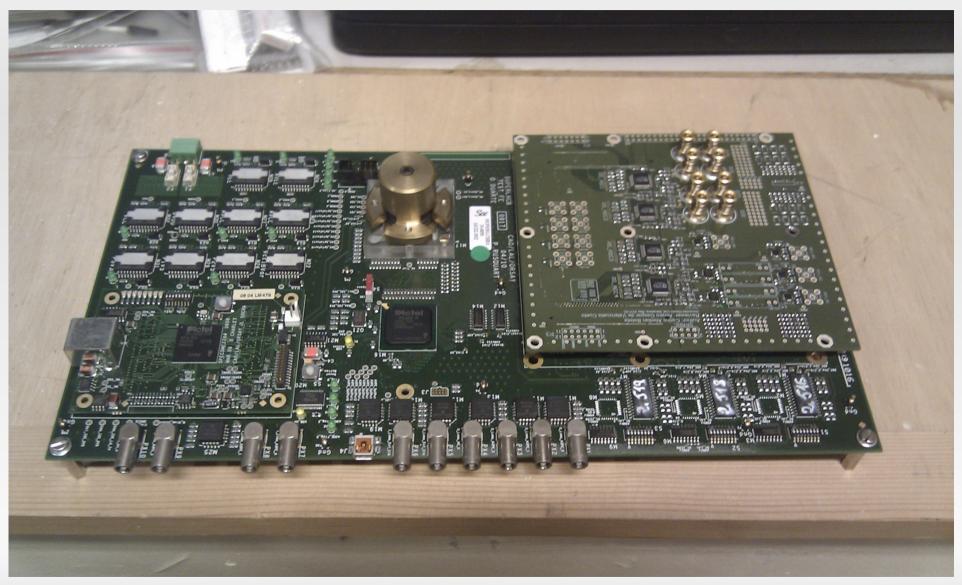

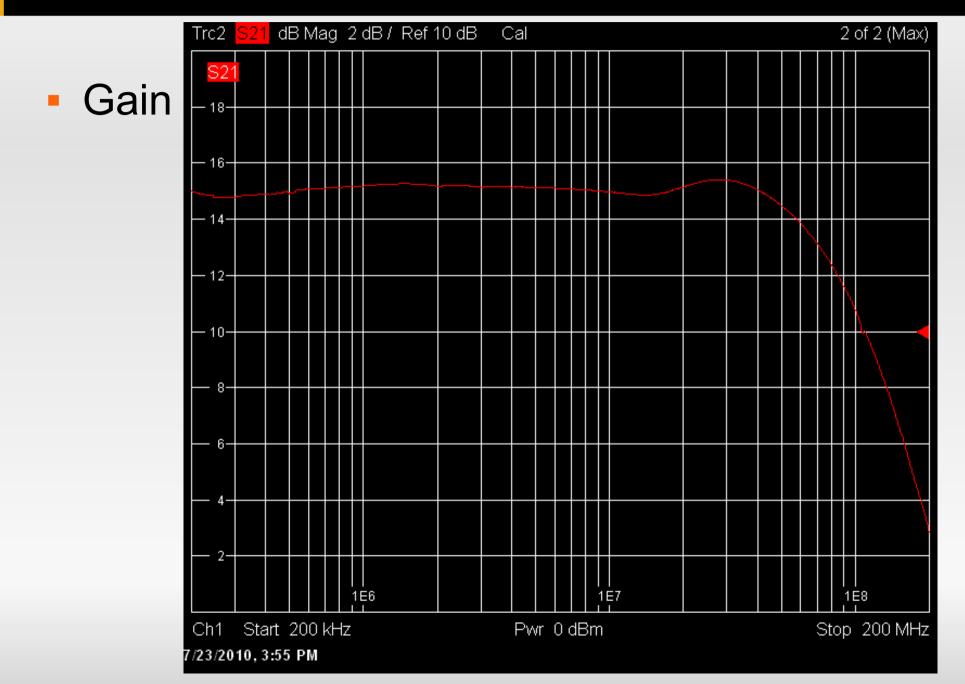

### **Some Measurements**

### **Some Measurements**

# **Further Steps**

- Finish the prototype and measure all the real life effects

- Perform noise measurements and tradeoff with reflection coefficient

- Fine tune shaping method

- Measure ADC response

- Tests with digital part

#### • If more information needed...

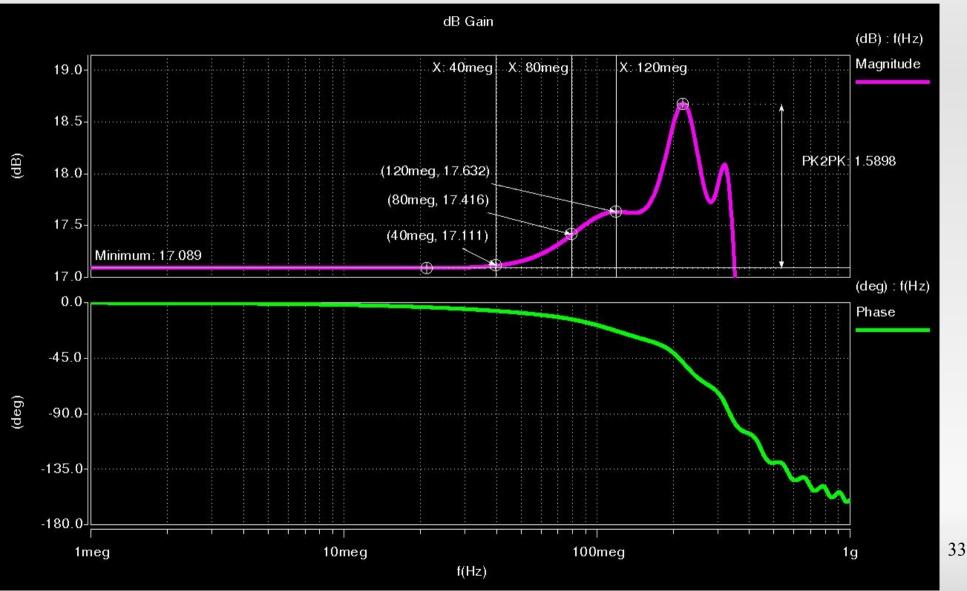

#### Input Stage Gain

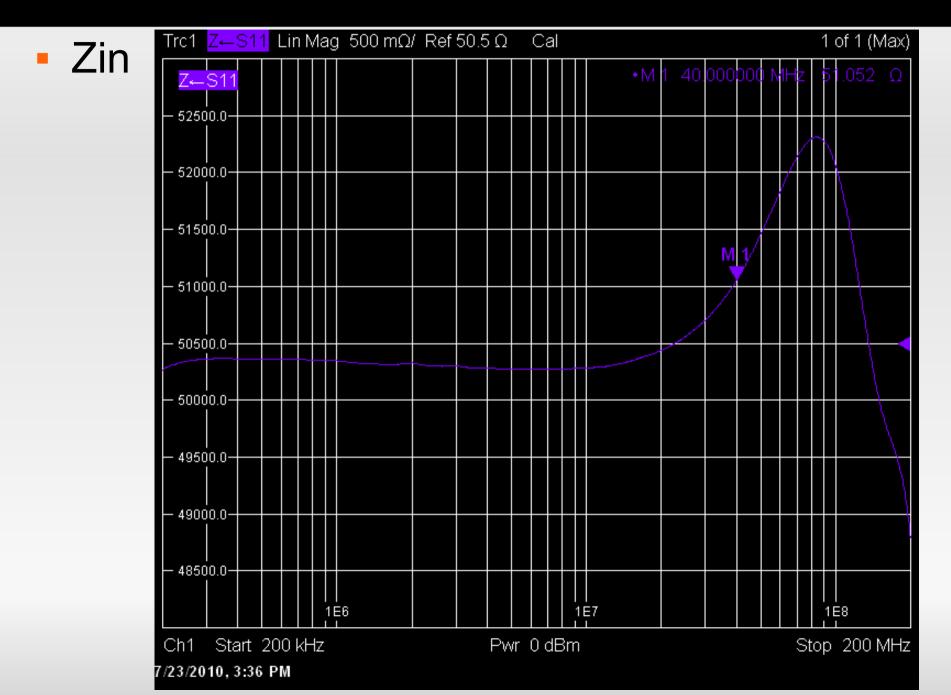

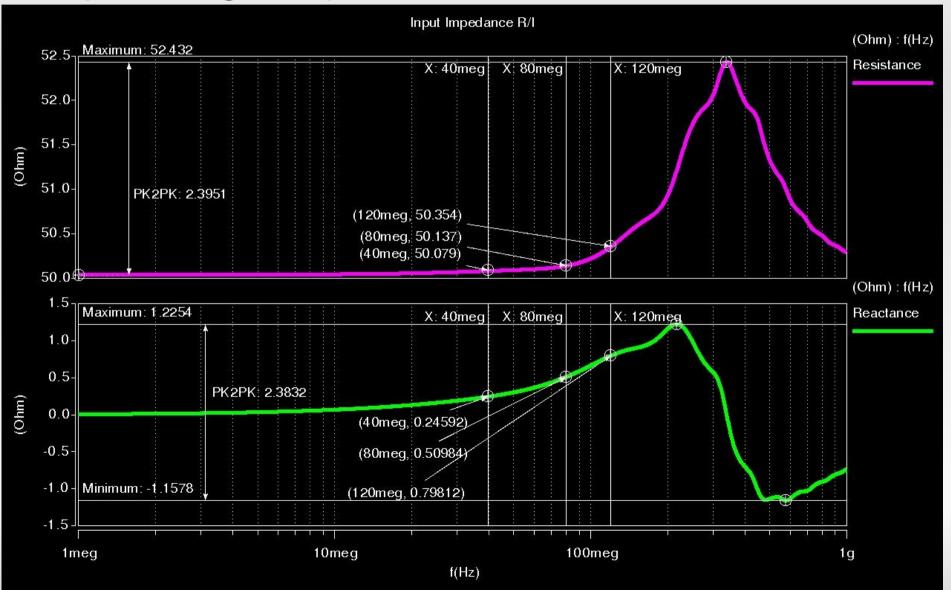

#### Input Stage Impedance

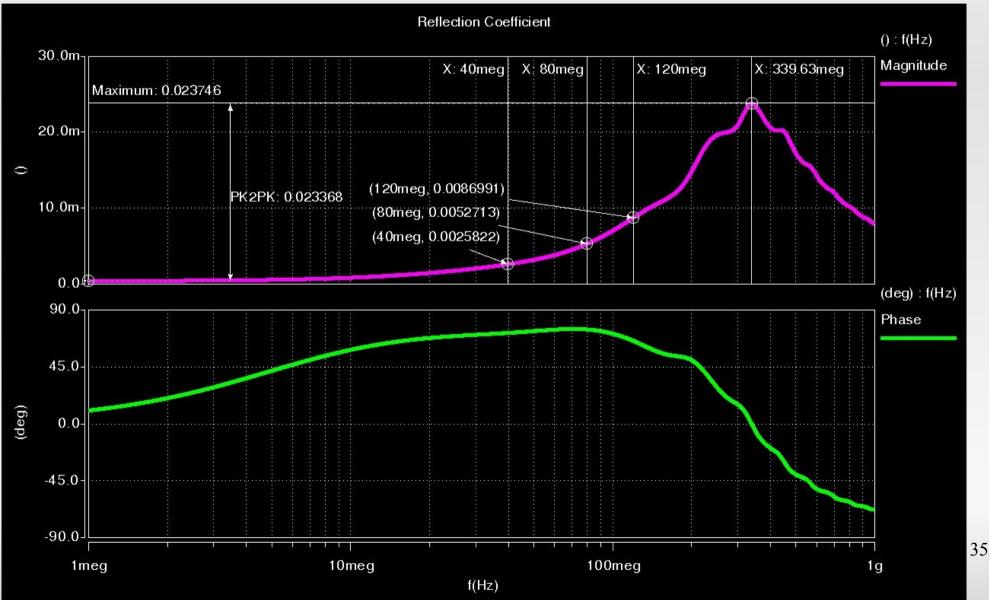

#### Input Stage Reflection Coefficient

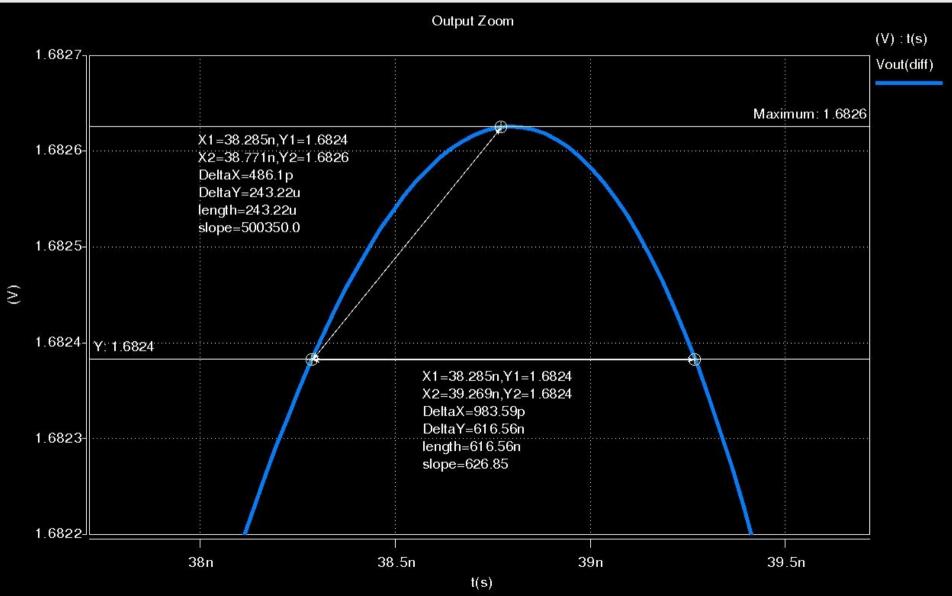

#### Output Zoom

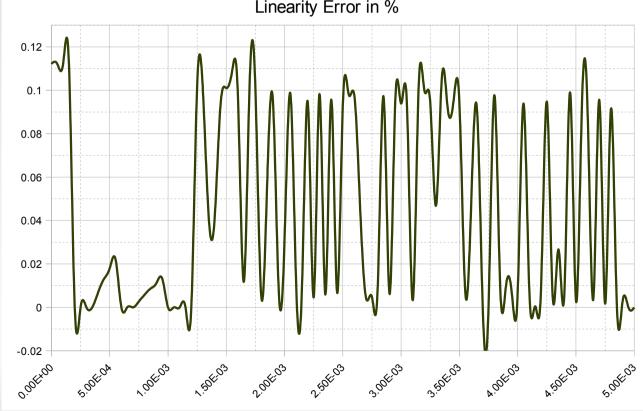

- Linearity

- Definition: Charge/Voltage [C/V]

- Simulated Linearity Error dependin on input pulse amplitude