# SMALL SENSOR DIODES WITH LFOUNDRY 150NM

Patrick Pangaud, Pierre Barrillon, Alexandre Habib, Mei Zhao, Marlon Barbero

pangaud@cppm.in2p3.fr

29 july 2021

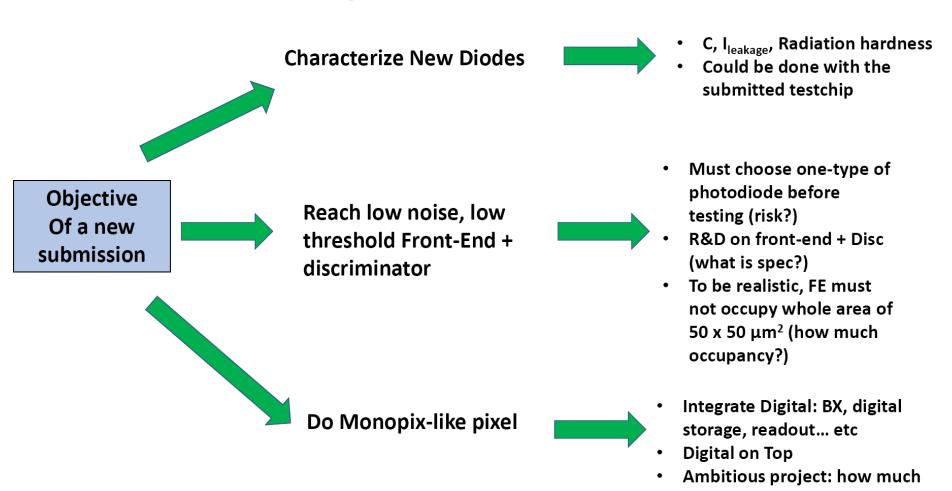

#### Motivations

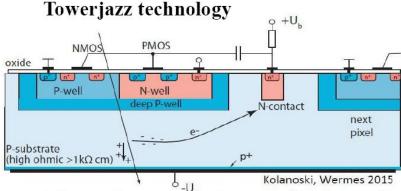

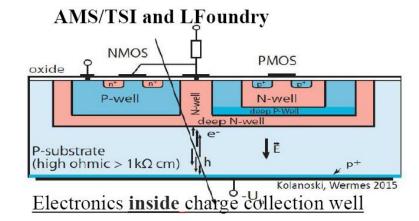

Two design approaches

"Small Collection Diode" design:

Electronics outside charge collection well

PROS: Small sensor capacitance → Low power consumption and noise

CONS: Long drift distances → Less radiation hard

$$ENC_{thermal}^2 \propto \frac{4}{3} \frac{kT}{g_m} \overbrace{\tau}^2$$

"Large Collection Diode" design:

PROS: Short drift distances > Radiation tolerant

**CONS:** Large sensor capacitance → Noise & speed (power) penalties

$$au_{CSA} \propto rac{1}{g_m} rac{\mathbf{C_d}}{C_f}$$

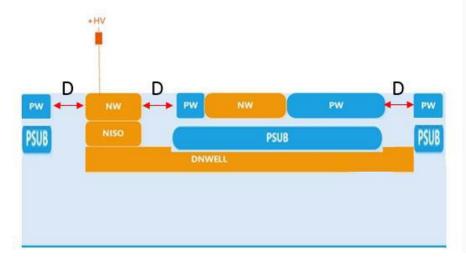

## New Rad-Hard Small pixel approach

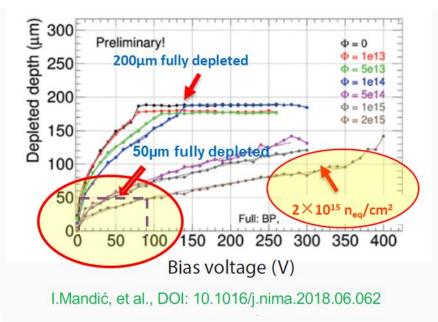

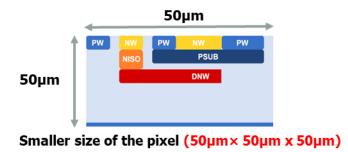

- Let think to reach a pixel size of 50µm x 50µm x 50µm

- 50μ x 50μ square and 50μ depth

- From ~10V (no Irrad) to 90V (2x10<sup>15</sup> neq/cm<sup>2</sup>)

- With Backside Metallization

- Less restrictive guardings

- Uniform drift field

D= distance (very important parameter)

#### How to reach HV=100V?

The total Voltage potential (top to bottom) at 100 V is achieved and the substrate is fully depleted (50µm)

By applying Voltage on TOP and Bottom And the thickness should be 50µm if we want to keep the pixel efficiency

All TCAD simulations come from TCAD profile from foundry and all results were validated by Lfoundry.

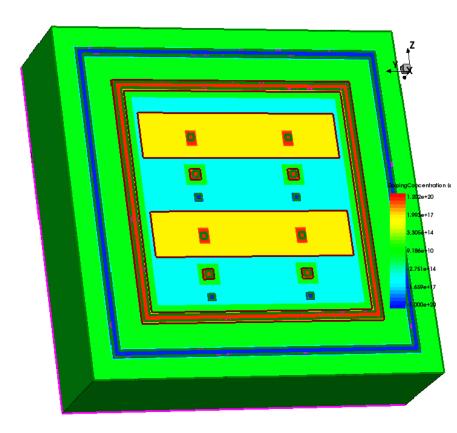

#### **TCAD 3D Simulation**

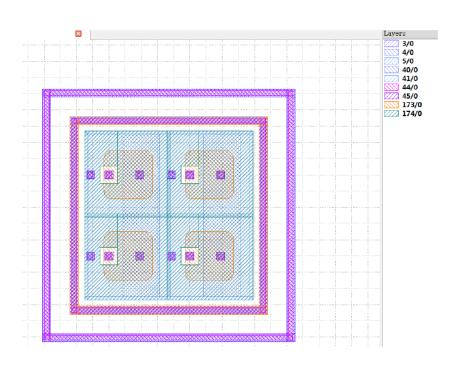

Matrix 2x2

#### **CPPM TCAD 3D Simulation**

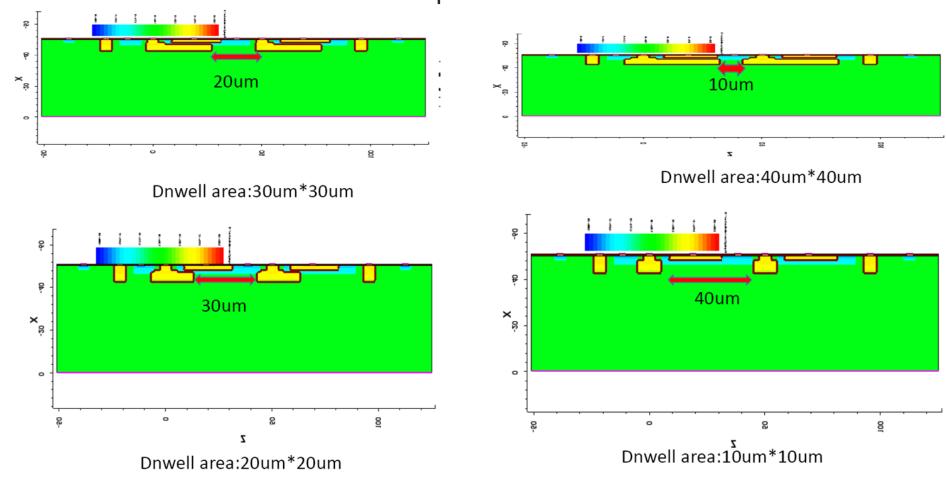

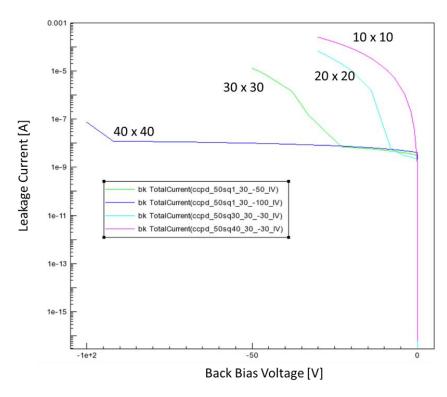

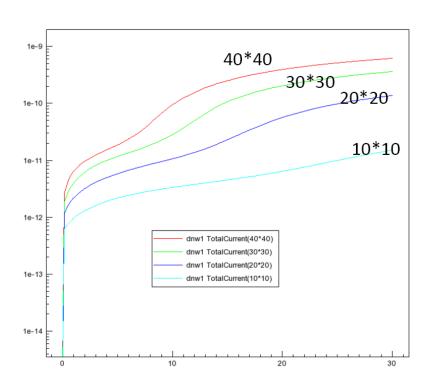

4 structures according the distance between pixels (DNW gap) Bigger is the DNW area, higher is the BV, but higher is the capacitance Trade-off between DNW area and capacitance value

#### TCAD simulations

The study also shows that the pixel corners represent a weak point, since the distance between DNW is at its maximum. This means a higher probability for a punch-through between the PSUB layer and the substrate.

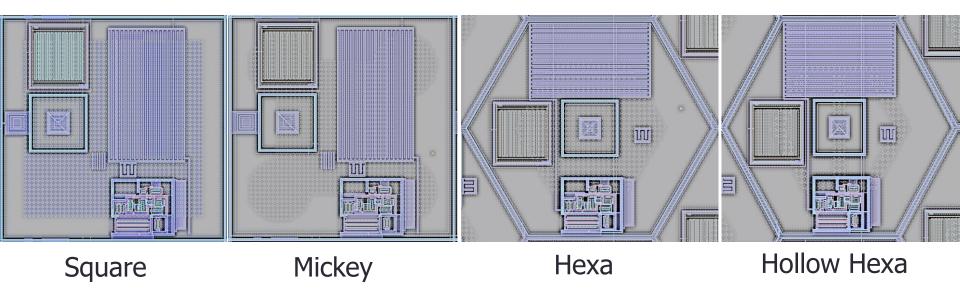

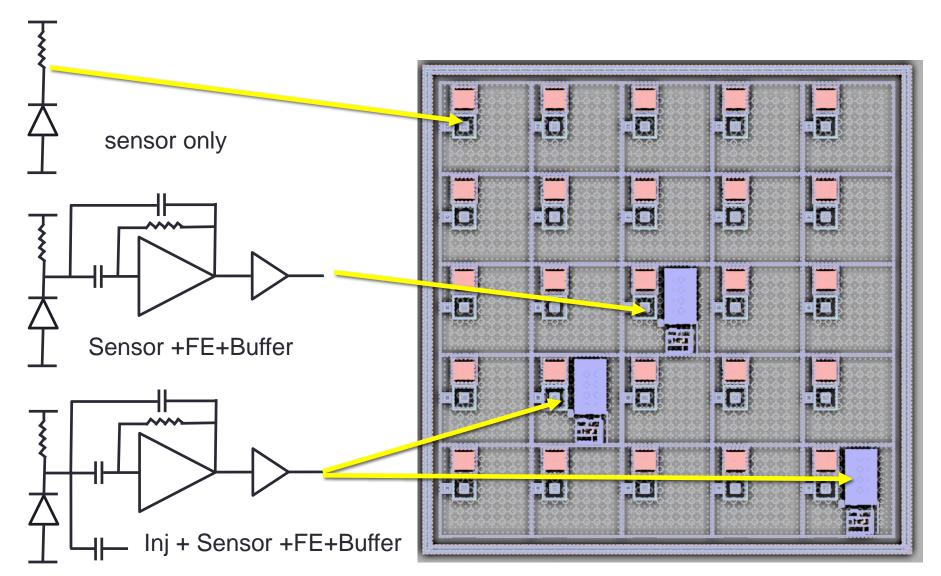

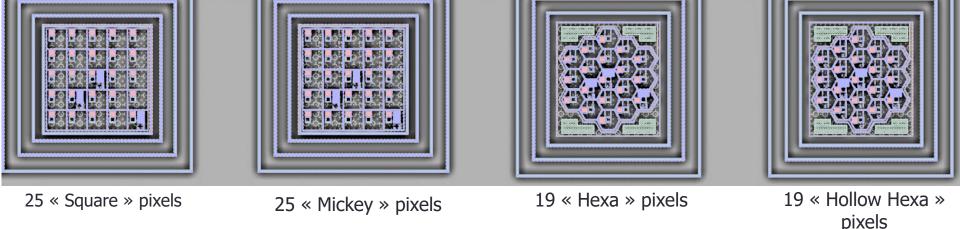

To resolve this problem, four diode structures were proposed:

- Square ( as a reference)

- Mickey ear square ( to minimize the distance)

- Hexagonal (where the maximum distance between DNW is constant)

- Hollow Hexa ( to minimize the Capacitance)

#### Small sensor diodes flavors

Square

Mickey

Hexa

Hollow Hexa

| DNW structure  | Capacitance [fF] | Breakdown voltage [V]<br>(Back Bias) |

|----------------|------------------|--------------------------------------|

| Square 40 x 40 | 126              | -100                                 |

| Mickey 30 x 30 | 107              | -70                                  |

| Hexagone 30    | 77               | -66                                  |

| Hollow Hexa 30 | 55               | -66                                  |

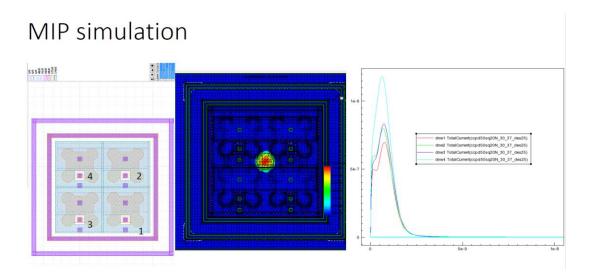

From TCAD simulation

#### TCAD simulations

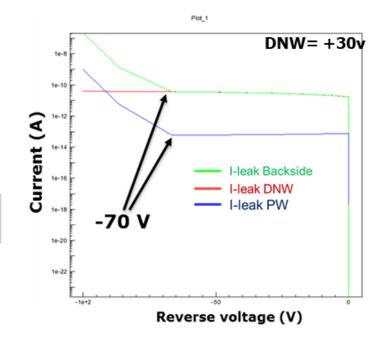

10nA/4px global leakage current for different diode (DNW) sizes, for a top bias @30 V (3kohms substrate)

5nA/4px leakage current for different diode (DNW) sizes, for a bottom bias @0 V (3kohms substrate)

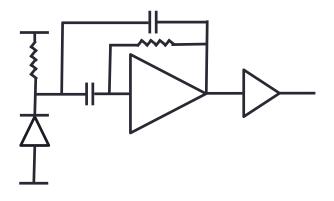

## Small pixels flavors front-end

## Small pixels matrix (25 "square" pixels)

## Small pixels test chip

- This test chip is a part of the LF-MONOPIX2.

- The tape-out was in may 2020.

- Delivering chip: end of 2020 (wafer thickness 700μm, 200μm, 100μm, 75μm)

- Test features to do (with and without radiations)

- E-TCT

- Analog readout of the pixels

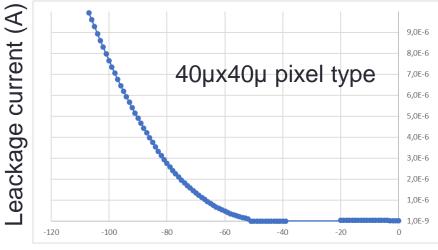

## 1st Sensor Results (700µm)

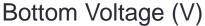

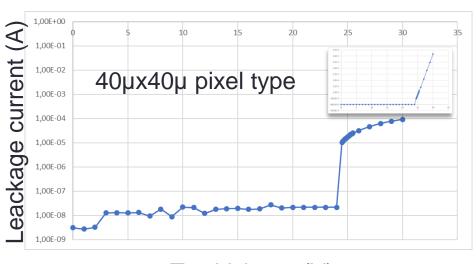

30nA/4px global leakage current for different diode (DNW) sizes, for a top bias @24 V BV at 54V ( 2kohms substrate)

Top Voltage (V)

10nA/4px leakage current for different diode (DNW) sizes, for a bottom bias @0 V BV at 24V ( 2kohms substrate)

The total Voltage potential (top to bottom) at 78 V is achieved

## Summary

- Small sensor DMAPS (fully depleted with uniform drift field) can be designed by using LF 150nm without any process modification

- A 50µm x 50µm pixel size test chip was designed on 2020

- Leakage current, BV voltage, MIP simulation were simulated by using doping profile. All simulations were reviewed by the LFOUNDRY

- The pixel contains analog Front-end, to help the sensor measurement

- The test chip with several pixel flavours is under evaluation. The wafer resistivity is 2kohms with 700μm, 200μm, 100μm, 75μm thickness

- The small sensor <u>proof of concept is done</u>. Need additional test We need contribution for the test, especially on E-TCT test.

- Can we plan to design a small matrix for the RD50-MPW3?

We will be happy to get contribution for the pixel readout design

## **BACKUP**

time, how many resources

### Brainstorming