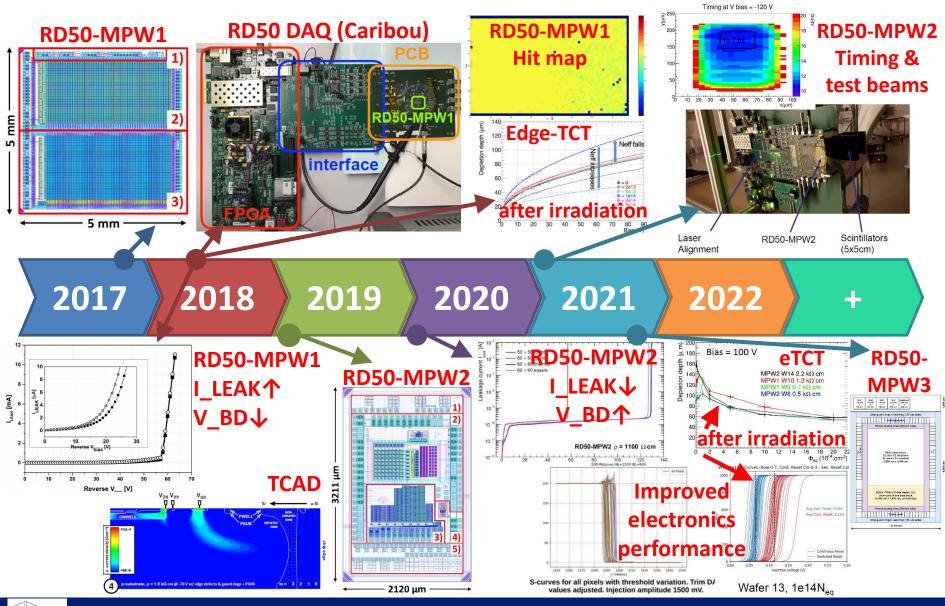

## **CERN-RD50 CMOS timeline**

17-19 November 2021 – Valencia (hybrid)

RD50

E. Vilella (Uni. Liverpool) – RD50 WS

#### **RD50-MPW2**

- Very successful chip, but with limitations

- Reduced number of rows and columns (8 x 8)

- No pixel digital readout to identify particle hits

- Very simple TX readout → some measurements too slow or not possible

## **RD50-MPW3**

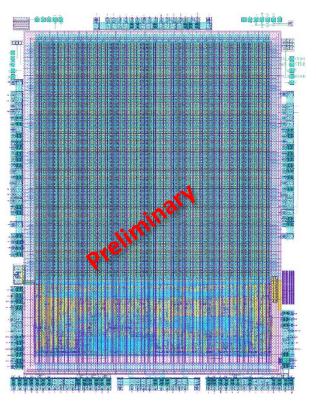

- Larger and more advanced matrix to further study HV-CMOS sensors

- 64 rows x 64 columns

- With in-pixel digital readout (FE-I3 style)

- With optimised peripheral readout for effective pixel configuration and fast data TX

- With all the lessons learned from RD50-MPW1/2

- Chip submission in November 2021 through an MPW shuttle run

- Resistivities: standard, 1.9k and >2k Ω·cm

| TEST<br>750 um<br>x<br>750 um              | TEST<br>750 um<br>x<br>750 um | 750 um 750 um 750 um 600 um x x x x x                                                                                                      |          |                   |        |  |  |  |  | ~1,000 um |

|--------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|--------|--|--|--|--|-----------|

|                                            |                               | 62 u<br>64 r                                                                                                                               | Analogue | matrix<br>mpixels | m wide |  |  |  |  | -6,600 um |

|                                            | (                             | EOCs, FIFOs (32-hits depth), CU,<br>slow control and blas block<br>(3,968 um x 1,496 um, preliminary)<br>Power routing lines (200 um wide) |          |                   |        |  |  |  |  |           |

| Chip guard rings + seal ring (150 um wide) |                               |                                                                                                                                            |          |                   |        |  |  |  |  |           |

| ~5,100 um                                  |                               |                                                                                                                                            |          |                   |        |  |  |  |  |           |

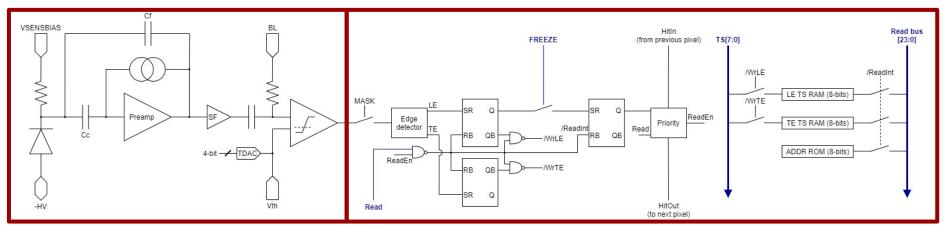

# **RD50-MPW3 – Pixel schematic**

#### Analogue readout

## **Digital readout**

- Analogue readout from RD50-MPW2

- Digital readout, highly improved, from RD50-MPW1

- New in-pixel logic

- To mask noisy pixels (MASK)

- New priority circuit for less-area consuming alternative

- Possibility to pause digitisation of new hits until readout is complete (FREEZE)

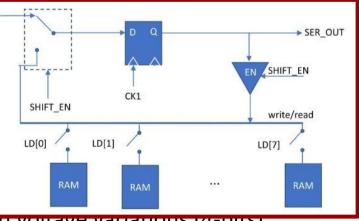

- 8-bit SRAM shift register for serial configuration

- Pixel-trimming to compensate for threshold voltage variations (4-bits)

- Flag to mask noisy pixels (1-bit)

- Signals to enable/disable calibration circuit (1-bit), SF output (1-bit), COMP output (1-bit)

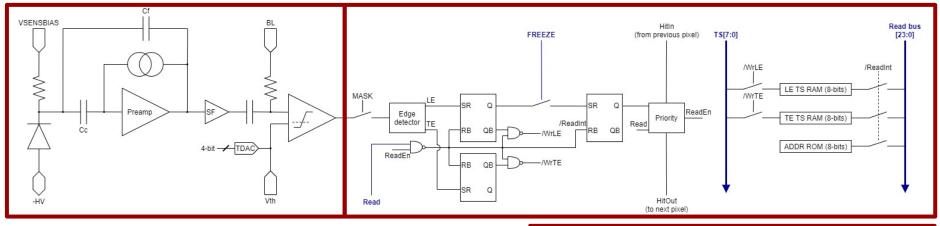

# **RD50-MPW3 – Pixel schematic**

#### Analogue readout

## **Digital readout**

- Analogue readout from RD50-MPW2

- Digital readout, highly improved, from RD50-

- New in-pixel logic

- To mask noisy pixels (MASK)

- New priority circuit for less-area consumi

- Possibility to pause digitisation of new hit

- 8-bit SRAM shift register for serial configu

- Pixel-trimming to compensate for threshold voltage variations (4-bits)

Flag to mask point give la (1, bit)

R. Casanova, 38th RD50 WS

SER\_IN

- Flag to mask noisy pixels (1-bit)

- Signals to enable/disable calibration circuit (1-bit), SF output (1-bit), COMP output (1-bit)

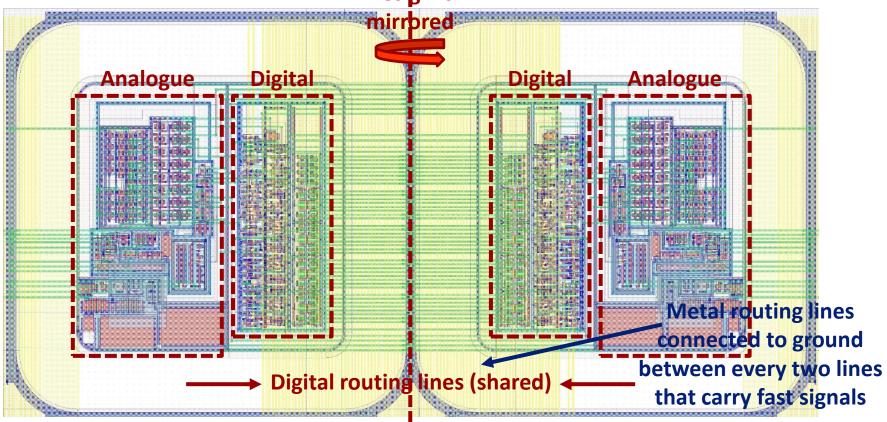

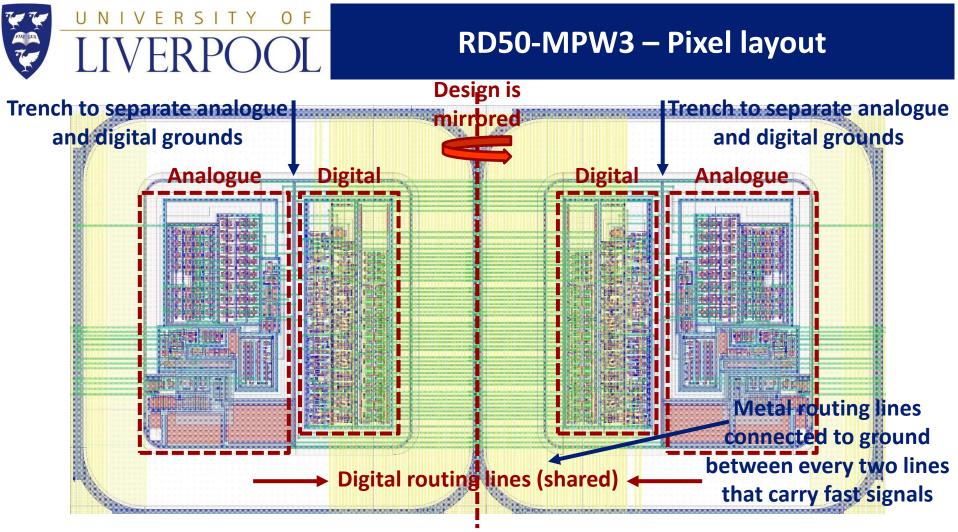

## **RD50-MPW3 – Pixel layout**

Design is

- Double column scheme to alleviate routing congestion and minimise crosstalk

- Pixels within double column share many signals  $\rightarrow \sim x0.5$  less routing lines

- Digital input/outputs (TS IN, TS OUT, ADDR), control signals (Read, Freeze, etc.)

- Pixel size is 62 μm x 62 μm

- Double column scheme to alleviate routing congestion and minimise crosstalk

- Pixels within double column share many signals  $\rightarrow \sim$  x0.5 less routing lines

- Digital input/outputs (TS IN, TS OUT, ADDR), control signals (Read, Freeze, etc.)

- Pixel size is 62 μm x 62 μm

# LIVERSITY OF

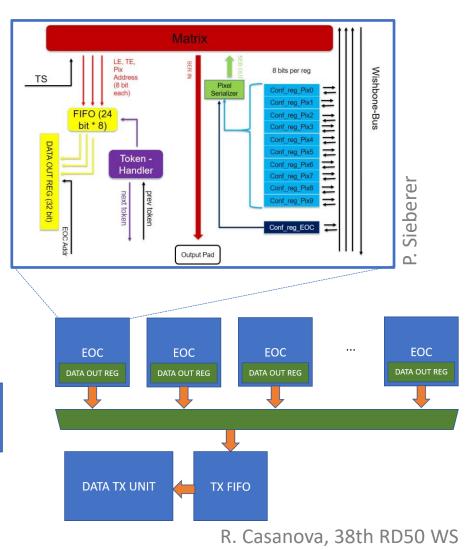

## RD50-MPW3 – EOC + readout + slow control

#### New EOC architecture - Components

- FIFO stores hit data (LE TS, TE TS and ADDR)

- FSM reads double column

- Token mechanism to determine which EOC is read out

### **Readout**

- Pixel is read out immediately after hit (if FIFO is not full)

- CU reads EOCs sequentially

- Data stored temporarily in TX FIFO

- Data TX unit with LVDS port @ 640 Mbps

CONTROL UNIT

#### **Slow control**

Based on I2C protocol for external communication using internal Wishbone bus

## **RD50-MPW3 – Status**

## **Logistics**

- Funding request

- With 11 RD50 institutes

- Submitted to and approved by RD50

- PO

- Sent from CERN to the foundry

- This is always an adventure...

## **Design & submission**

- We have encountered a number of last minute issues

- Design team is working very hard to solve them in due time

- Deadline to submit is Monday 22.11.21 (although the foundry has confirmed they can manage a few days delay)

- RD50 prolongation request May 2018

- M1: Characterization of the diodes and readout electronics of unirradiated and irradiated RD50-MPW1 samples (Q4/2018) → <u>Achieved</u>

- M1.2 (new): Design and submission of RD50-MPW2 (Q1/2019) →

<u>Achieved</u>

- M1.3 (new): Characterization of unirradiated and irradiated RD50-MPW2 samples (Q1/2020 → Q3/2021) → <u>Achieved</u>

- M1.4 (new): Design and submission of RD50-MPW3 (Q4/2021) →

Ongoing

- M2: Design and submission for fabrication of RD50-ENGRUN1 (Q4/2018)

- M3: Characterization of unirradiated and irradiated RD50-ENGRUN1 samples (Q3/2019, Q3/2020)

- M4: Characterization of irradiated backside biased RD50-ENGRUN1 samples for operation beyond 10<sup>16</sup> n<sub>eq</sub>/cm (Q4/2020)

- M5: Studies of stitching process options (Q4/2021)

- M6: Characterization of unirradiated and irradiated stitched samples (Q4/2022)