# 4D particle tracking with monolithic silicon pixel sensors in SiGe BiCMOS

Lorenzo Paolozzi

**EPFL Seminar**

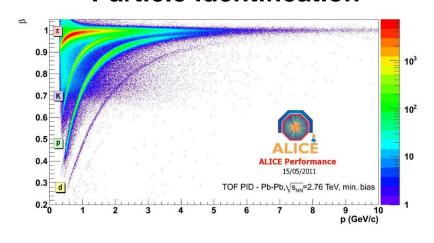

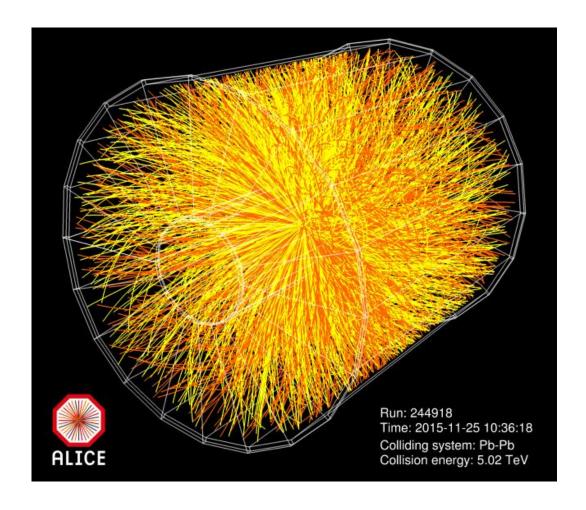

### Precise timing measurement in HEP

#### **Particle identification**

**Pile-up suppression**

#### **Support for fast tracking**

8/11/2021

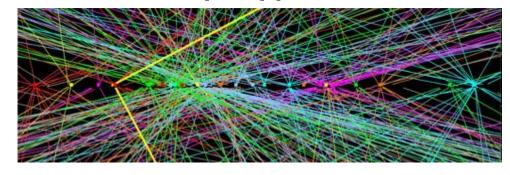

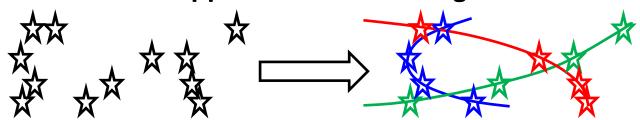

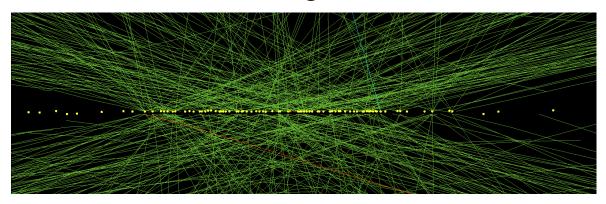

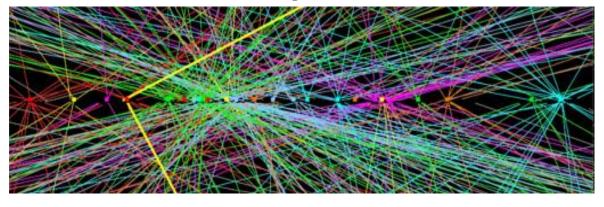

### 4D tracking for pile-up suppression

Hartmut F-W Sadrozinski et al 2018 Rep. Prog. Phys. 81 026101

#### Without timing information

8/11/2021

### 4D tracking for pile-up suppression

Hartmut F-W Sadrozinski et al 2018 Rep. Prog. Phys. 81 026101

#### Without timing information

#### With timing information

### 4D tracking for pile-up suppression

#### **Summary**

- 1. SiGe HBTs for fast, low power timing measurement.

- 2. SiGe BiCMOS technologies.

- 3. R&D at the University of Geneva.

- 4. The FASER pre-shower detector.

- 5. The path toward picosecond time resolution.

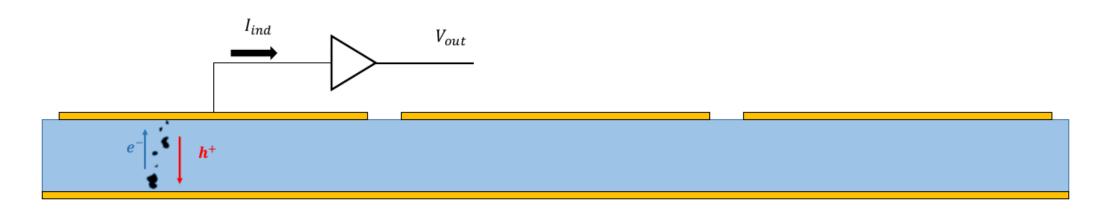

What are the main parameters that determine the time resolution of semiconductor detectors?

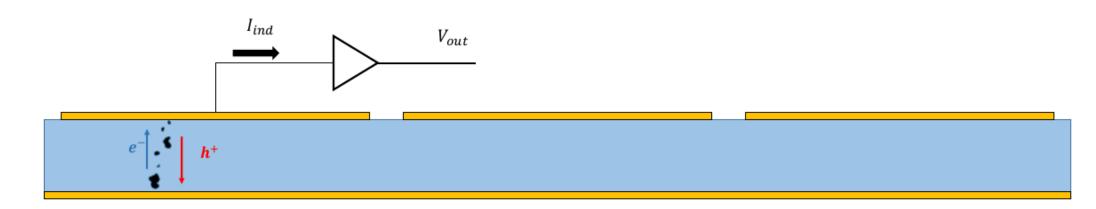

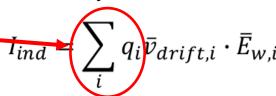

$$I_{ind} = \sum_{i} q_{i} \bar{v}_{drift,i} \cdot \bar{E}_{w,i}$$

What are the main parameters that determine the time resolution of semiconductor detectors?

Geometry and fields

$$I_{ind} = \sum_{i} q_{i} \bar{v}_{drift,i} \cdot \bar{E}_{w,i}$$

What are the main parameters that determine the time resolution of semiconductor detectors?

- Geometry and fields

- Charge collection noise

What are the main parameters that determine the time resolution of semiconductor detectors?

- Geometry and fields

- Charge collection noise

- Electronic noise -

$$I_{ind} = \sum_{i} q_{i} \bar{v}_{drift,i} \cdot \bar{E}_{w,i}$$

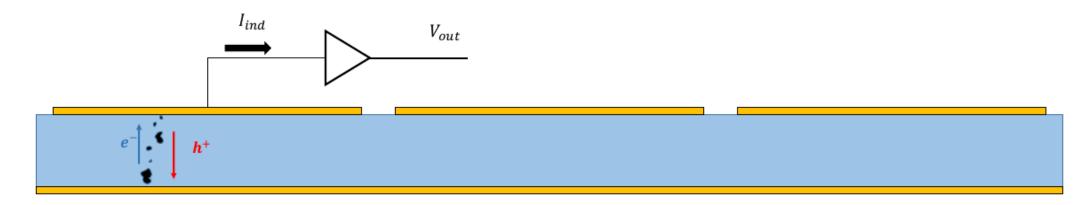

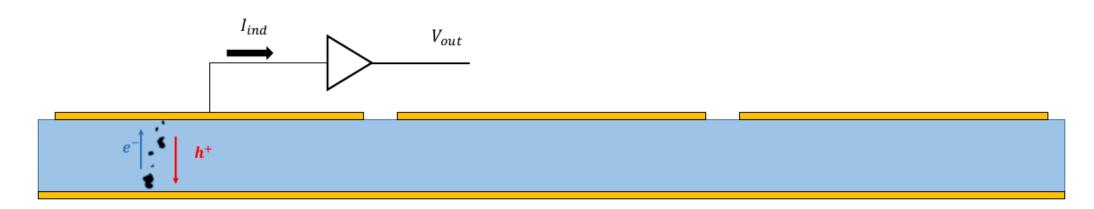

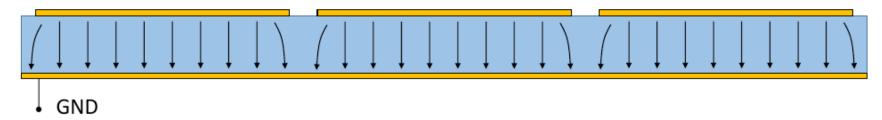

#### 1. Geometry and fields

#### **Sensor optimization for time measurement** means:

Sensor time response **independent** from the particle trajectory

→ "Parallel plate" read out: wide pixels w.r.t. depletion region

$$I_{ind} = \sum_{i} q_{i} \bar{v}_{drift,i} \cdot \bar{E}_{w,i} \cong v_{drift} \frac{1}{D} \sum_{i} q_{i}$$

Scalar, saturated

Scalar, uniform

Uniform weighting field (signal induction)

Desired features:

- Uniform electric field (charge transport)

- Saturated charge **drift velocity** (signal speed)

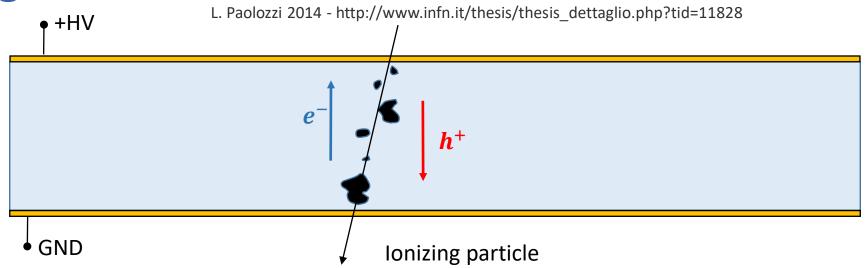

#### 2. Charge-collection noise

is produced by the **non uniformity of the charge deposition** in the sensor:

$$I_{ind} \cong v_{drift} \frac{1}{D} \sum_{i} q_{i}$$

When **large clusters** are absorbed at the electrodes, their contribution is removed from the induced current. The **statistical origin** of this variability of  $I_{ind}$  makes this effect irreducible in PN-junction sensors.

8/11/2021

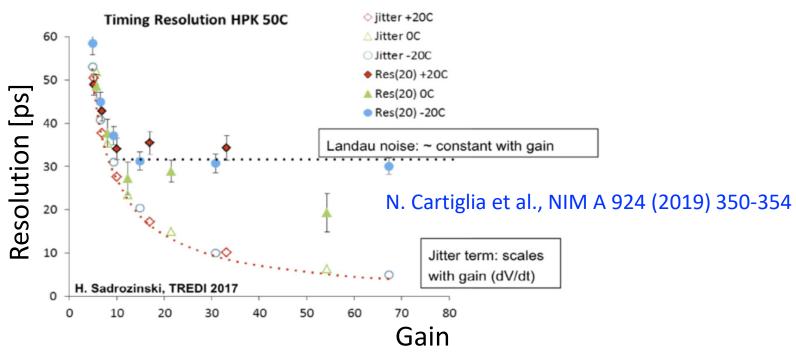

#### 2. Charge-collection noise

Charge collection noise represents an intrinsic limit to the time resolution for a semiconductor PN-junction detector.

~30 ps reached by present LGAD sensors.

Lower contribution from sensors without internal gain

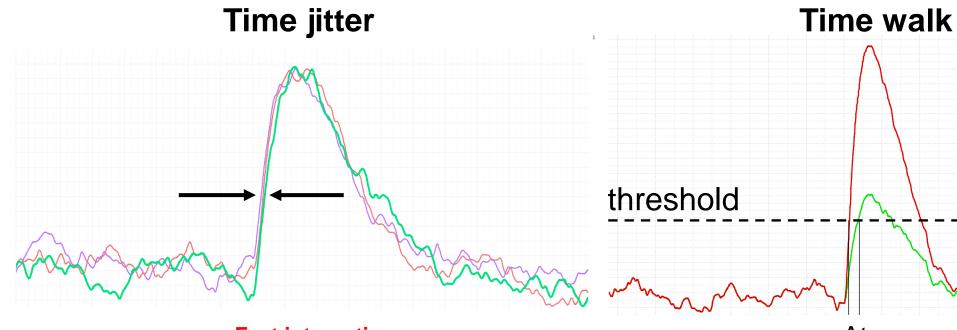

#### 3. Electronic noise

Once the geometry has been fixed, the time resolution depends mostly on the amplifier performance.

#### **Fast integration**

$$\sigma_t = \frac{\sigma_V}{dV/dt} \cong \frac{ENC}{I_{Ind}}$$

#### 3. Electronic noise

Once the geometry has been fixed, the time resolution depends mostly on the amplifier performance.

**Fast integration**

$$\sigma_t = \frac{\sigma_V}{dV/dt} \cong \frac{ENC}{I_{Ind}}$$

$$\sigma_t \propto ENC$$

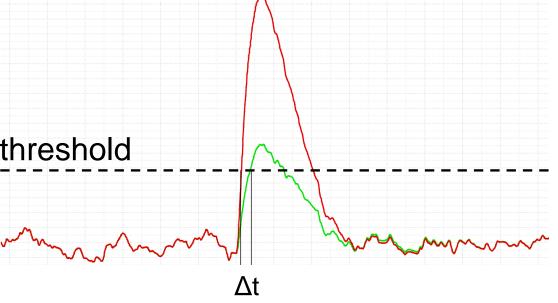

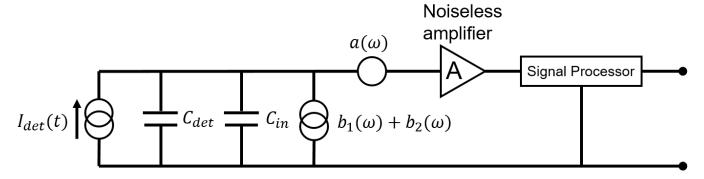

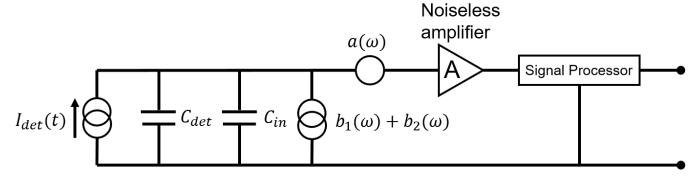

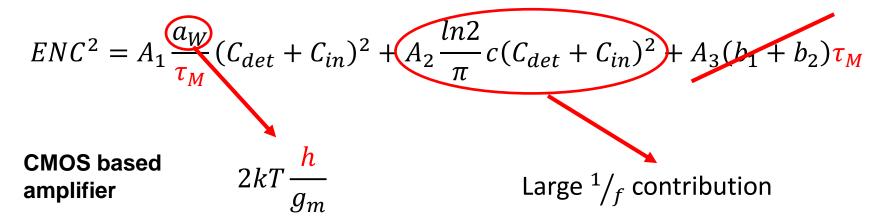

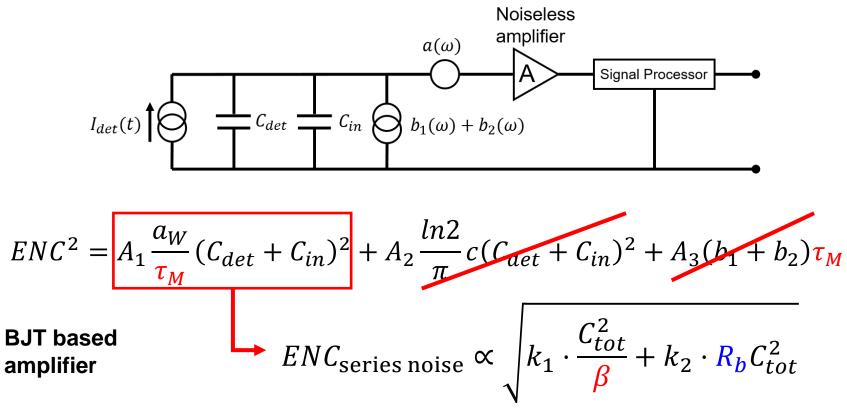

#### Equivalent Noise Charge: device comparison

$$ENC^{2} = A_{1} \frac{a_{W}}{\tau_{M}} (C_{det} + C_{in})^{2} + A_{2} \frac{\ln 2}{\pi} c(C_{det} + C_{in})^{2} + A_{3} (b_{1} + b_{2}) \tau_{M}$$

$$\tau_{M} \sim 1 \text{ ns}$$

How do MOS-FET and BJT compare in terms of noise?

8/11/2021

#### Equivalent Noise Charge: device comparison

#### Equivalent Noise Charge: device comparison

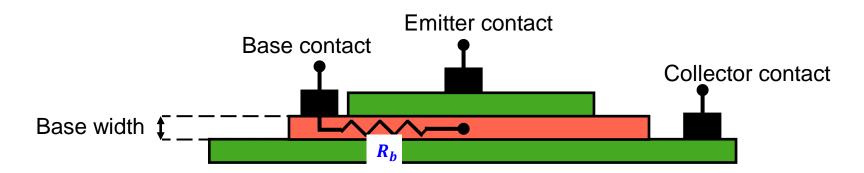

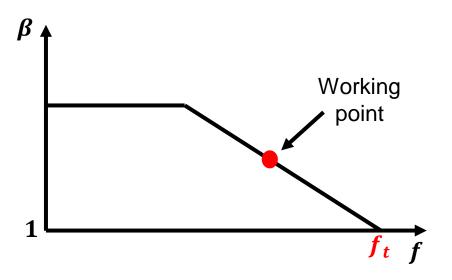

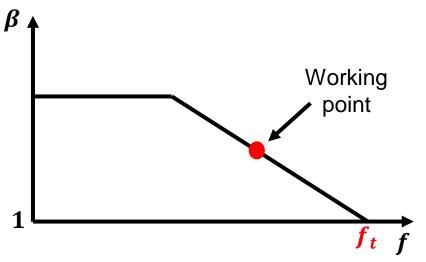

**Goal:** maximize the current gain  $\beta$  at high frequencies while keeping a low base resistance  $R_b$

8/11/2021

### **Equivalent Noise Charge**

For a NPN BJT, the amplifier current gain  $\beta$  can be expressed as:

$$\beta = \frac{i_C}{i_B} = \frac{\tau_p}{\tau_t}$$

$\mathcal{T}p$  = hole recombination time in Base

$\mathcal{I}_t$  = electron transit time (Emitter to Collector)

Large  $\beta \Longrightarrow$  Minimize the electron transit time

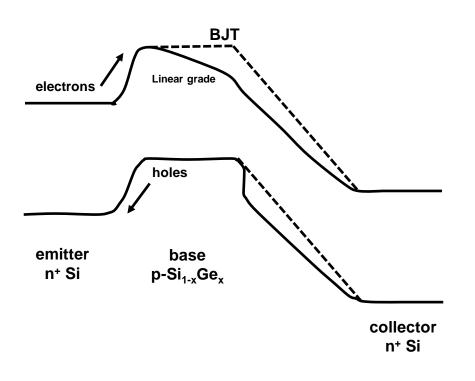

### SiGe HBT technology for low-noise, fast amplifiers

In SiGe Heterojunction Bipolar Transistors (HBT) the **grading** of the bandgap in the Base changes the **charge-transport mechanism** in the Base from **diffusion** to **drift**:

#### **Grading of germanium in the base:**

field-assisted charge transport in the Base, equivalent to introducing an electric field in the Base

- $\Rightarrow$  short e<sup>-</sup> transit time in Base  $\Rightarrow$  very high  $\beta$

- $\Rightarrow$  smaller size  $\Rightarrow$  reduction of  $R_b$  and very high  $f_t$

**Hundreds of GHz**

12

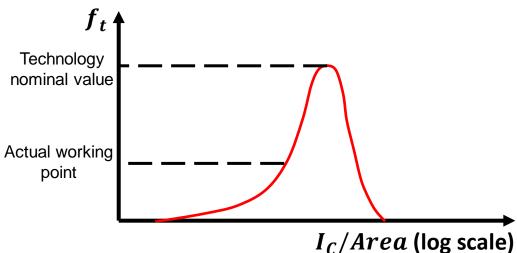

### Current gain and power consumption: $f_t$ is the key

|                        | $f_t = 10 \; GHz$ | $f_t = 100  GHz$ |

|------------------------|-------------------|------------------|

| $eta_{max}$ at 200 MHz | 50                | 500              |

| $eta_{max}$ at 1 GHz   | 10                | 100              |

| $\beta_{max}$ at 5 GHz | 2                 | 20               |

### Current gain and power consumption: $f_t$ is the key

|                          | $f_t = 10 \; GHz$ | $f_t = 100  GHz$ |

|--------------------------|-------------------|------------------|

| $\beta_{max}$ at 200 MHz | 50                | 500              |

| $\beta_{max}$ at 1 GHz   | 10                | 100              |

| $\beta_{max}$ at 5 GHz   | 2                 | 20               |

Trade-off: **ENC**

**Power Consumption**

13

$f_t > 100 \ GHz$  technologies are necessary for fast, low-power amplification.

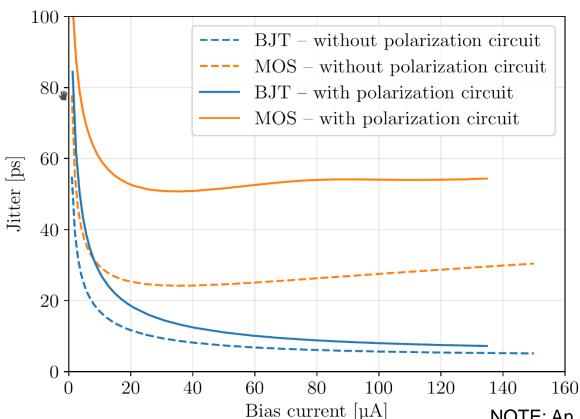

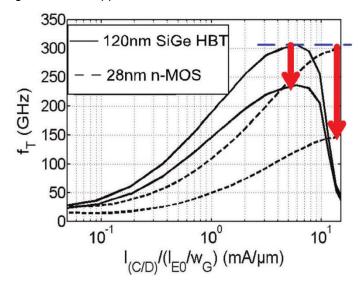

### SiGe HBT vs CMOS (our simulation)

Intrinsic amplifier jitter, an example: Common emitter (source) configuration in a 130nm technology.

NOTE: An extra parasitic capacitance was accounted for the insulation of the HBT from substrate.

#### **Summary**

- 1. SiGe HBTs for fast, low power timing measurement.

- 2. SiGe BiCMOS technologies.

- 3. R&D at the University of Geneva.

- 4. The FASER pre-shower detector.

- 5. The path toward picosecond time resolution.

#### SiGe BiCMOS: A commercial VLSI foundry process

#### **SiGe BiCMOS Markets Served**

Optical fiber networks

**Smartphones**

**IoT Devices**

Microwave Communication

Automotive: LiDAR, Radar and Ethernet

HDD preamplifiers, line drivers, Ultra-high speed DAC/ADCS

16

https://towerjazz.com/technology/rf-and-hpa/sige-bicmos-platform/

#### Some applications

- Automotive radars

- (27/77 GHz)

- Satellite

- communications

- Point-to-point radio (V-

- band, E-band)

- Defense

- Security

- LAN RF transceivers (60 Instrumentation GHz)

A fast-growing technology: f<sub>max</sub> = 700 GHz transistor recently developed (DOT7 project, IHP microelectronics)

#### SiGe BiCMOS: A commercial VLSI foundry process

### Some foundries offering SiGe BiCMOS:

- IHP Microelectronics (→ Research Inst.)

- Towerjazz

- Globafoundries

- TSMC

- STm

- AMS

- ...

Implemented as an adder module to an existing CMOS technologies.

Typical increase for same tech. node in cost: ~10-15 %

8/11/2021

#### Some characteristics of SiGe

Integrated in CMOS platforms SiGe-HBT AND Si-CMOS

Vertical transport device

Not as dependent on lithography as CMOS

Cryogenic compatible

Silicon-based device operating at < 1 K</li>

Inherently rad. hard

Good radiation tolerance with standard processing

High output current drive

Tolerance to parasitics

L. Paolozzi - EPFL Seminar 8/11/2021

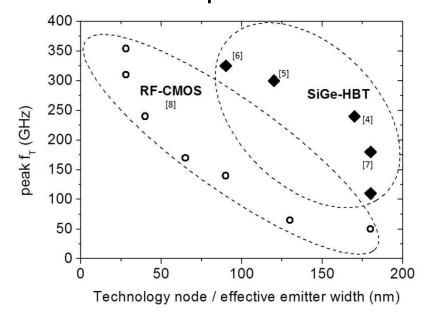

#### A comparison with CMOS technologies

#### Intrinsic performance

A. Mai and M. Kaynak, SiGe-BiCMOS based technology platforms for mm-wave and radar applications. DOI: 10.1109/MIKON.2016.7492062

#### Robustness to parasitics

M. Schröter, U. Pfeiffer and R. Jain, Silicon-Germanium Heterojunction Bipolar Transistors for mm-Wave Systems: Technology, Modeling and Circuit Applications.

19

### SiGe HBT scaling

| Figure of merit                | SiGe HBT |          | CMOS    |          |

|--------------------------------|----------|----------|---------|----------|

|                                | Base     | Scaling  | Base    | Scaling  |

| f <sub>T</sub>                 | Good     | Improves | Good    | Improves |

| f <sub>MAX</sub>               | Good     | Improves | Good    | Improves |

| NF <sub>MIN</sub>              | Good     | Improves | Good    | Improves |

| 1/f noise                      | Good     | Neutral  | Neutral | Worsens  |

| g <sub>M</sub> /g <sub>O</sub> | Good     | Improves | Poor    | Worsens  |

| g <sub>M</sub>                 | Good     | Improves | Poor    | Improves |

| mismatch                       | Good     | Neutral  | Poor    | Worsens  |

| linearity                      | Good     | Neutral  | Good    | Worsens  |

| voltage headroom               | Neutral  | Neutral  | Poor    | Worsens  |

| breakdown voltage              | Good     | Neutral  | Poor    | Worsens  |

From: J.D. Cressler, IEEE transactions on nuclear science, vol. 60, n. 3 (2013)

L. Paolozzi - EPFL Seminar

8/11/2021 20

#### SG13G2 technology from IHP Microelectronics

Exploit the properties of state-of-the-art SiGe Bi-CMOS transistors to produce an ultra-fast, low-noise, low-power consumption amplifier

#### Leading-edge technology: IHP SG13G2

130 nm process featuring SiGe HBT with

- Transistor transition frequency:  $f_t = 0.3 THz$

- DC Current gain:  $\beta = 900$

- Delay gate: 1.8 ps

21

#### **Summary**

- 1. SiGe HBTs for fast, low power timing measurement.

- 2. SiGe BiCMOS technologies.

- 3. R&D at the University of Geneva.

- 4. The FASER pre-shower detector.

- 5. The path toward picosecond time resolution.

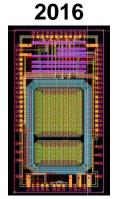

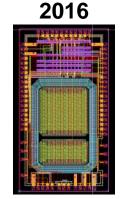

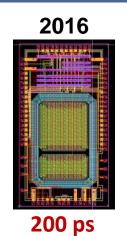

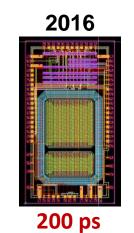

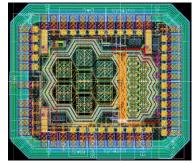

#### 2016

- $1000 \times 500 \,\mu m$  pixel.

- Discriminator output.

- 200 ps time resolution.

For the a TOF PET Project

23

**200** ps

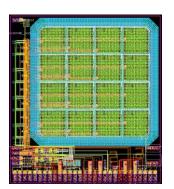

Monolithic silicon pixel sensors in SiGe BiCMOS technology

Roma Tor Vergata

For the a

TOF PET

Project

23

200 ps

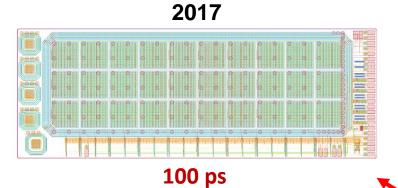

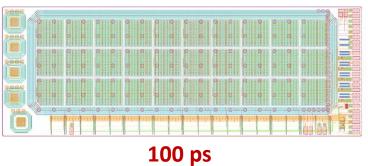

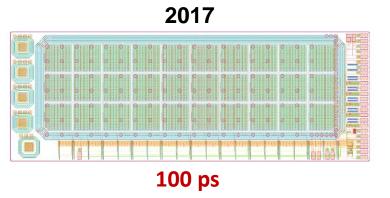

Monolithic silicon pixel sensors in SiGe BiCMOS technology

- $500 \times 500 \mu m$  pixels

- 100 ps TDC + I/O logic

- 100 ps time resolution.

Roma Tor Vergata

#### 2017

2019

23

200 ps

Monolithic silicon pixel sensors in SiGe BiCMOS technology

- $500 \times 500 \,\mu\text{m}$  pixels

- TDC + I/O logic

- 100 ps time resolution.

- Minor bug fixes on TDC.

## 2017 100 ps

2019

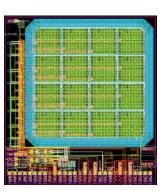

Monolithic silicon pixel sensors in SiGe **BiCMOS** technology

2018

**50** ps

- 65µm side, hexagonal pixels

- Discriminator output

- 50 ps time resolution

For HEP timing sensor R&D

23

2019

Monolithic silicon pixel sensors in SiGe BiCMOS technology

2018

**50** ps

2019

**New results**

2021

For HEP timing sensor R&D

23

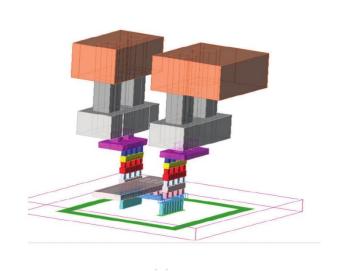

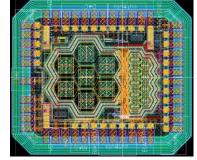

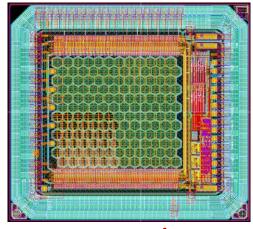

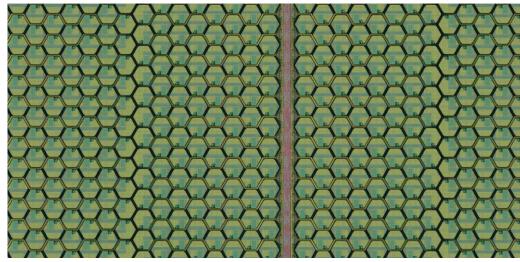

# The "ATTRACT" prototype

MPW submission in 2019 funded by H2020 ATTRACT MonPicoAD project

Prototype chip with 5 different pixel matrices for R&D investigation

#### 1. Active pixel:

- Front End in pixel

- HBT preamp + driver (in pixel) + CMOS discriminator (outisde pixel)

- 2. TT-PET version:

- HBT preamp + CMOS discriminator

- 3. Limiting amplifier:

- HBT preamp + HBT limiting amplifier

- 4. Double Threshold:

- HBT preamp + two CMOS discriminators

- 5. Analogue Channels:

- HBT preamp + two HBT Emitter Followers to  $500\Omega$  Resistance on pad.

8/11/2021

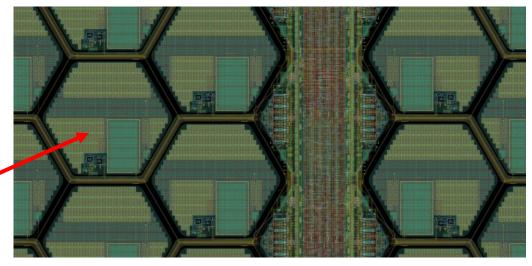

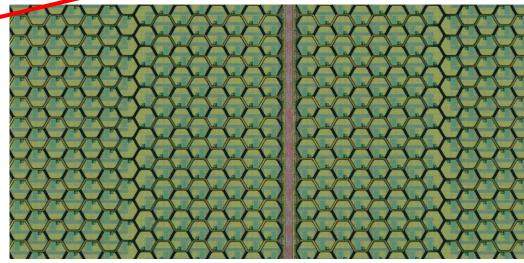

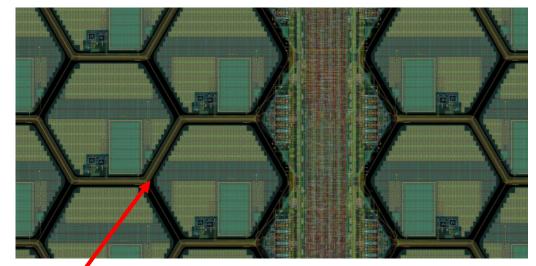

# The "ATTRACT" prototype

25

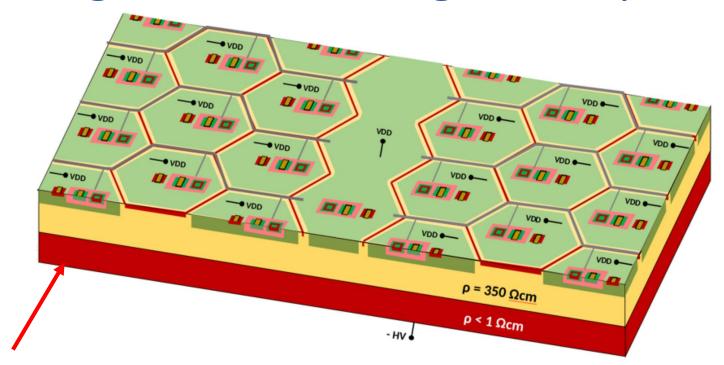

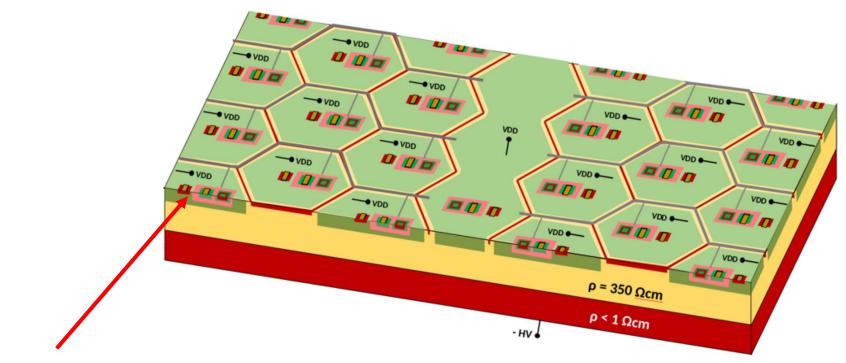

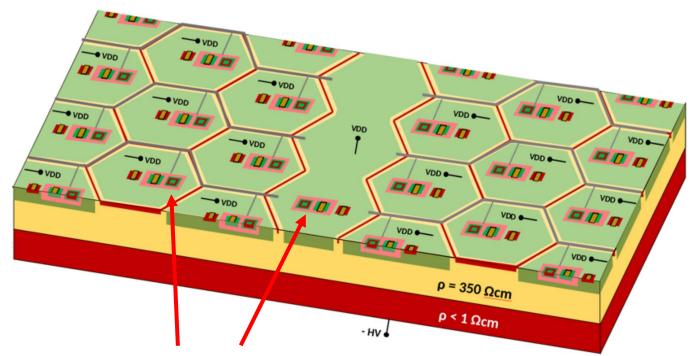

Hexagonal pixel, 65 micron side PSTOP Separate electronics well

B doped, 20 Ωcm

B doped, 50 Ωcm

- Negative HV applied to substrate from backside and from top.

- All pixels and electronic nwells at positive low voltage.

- Typical HV: -140 V corresponds to a depletion layer of 26 μm.

Typical signal charge for a MIP: ~1600 electrons.

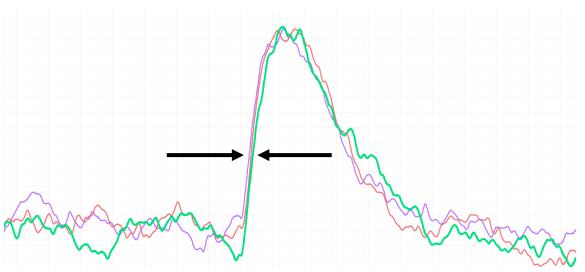

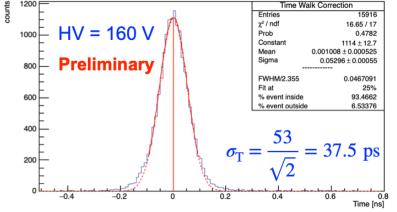

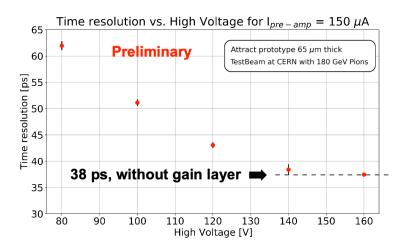

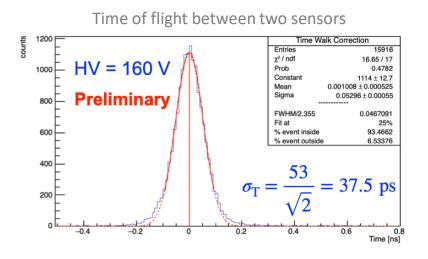

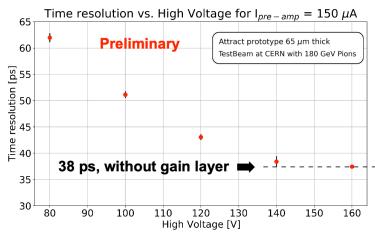

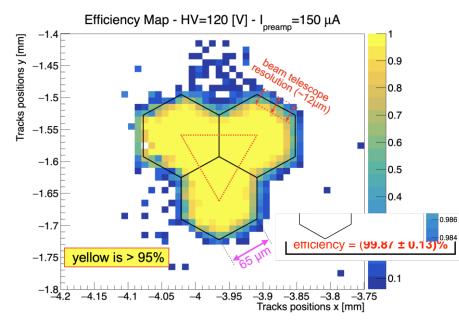

### Small pixel ATTRACT prototype – test beam results

- Tested at CERN SPS testbeam in Q2 2021

- Timing plateau at ~38 ps and detection efficiency >99%

### Time of flight between two sensors $\chi^2$ / ndf

### No avalanche gain

### Small pixel ATTRACT prototype – test beam results

- Tested at CERN SPS testbeam in Q2 2021

- Timing plateau at ~38 ps and detection efficiency >99%

No avalanche gain

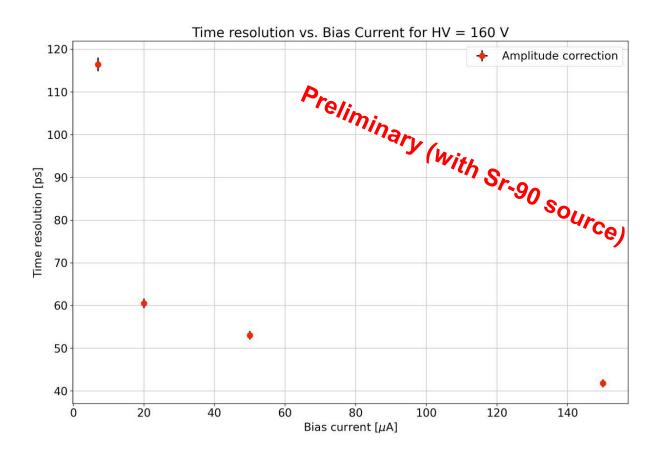

# Small pixel ATTRACT prototype – power consumption

8/11/2021 27

### **Summary**

- 1. SiGe HBTs for fast, low power timing measurement.

- 2. SiGe BiCMOS technologies.

- 3. R&D at the University of Geneva.

- 4. The FASER pre-shower detector.

- 5. The path toward picosecond time resolution.

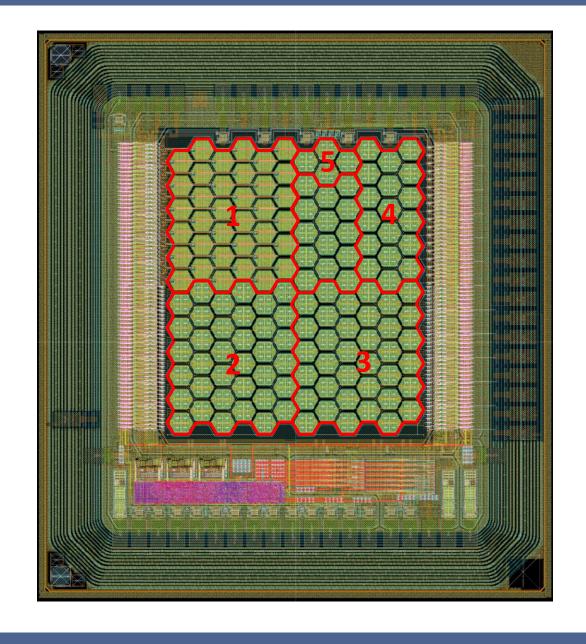

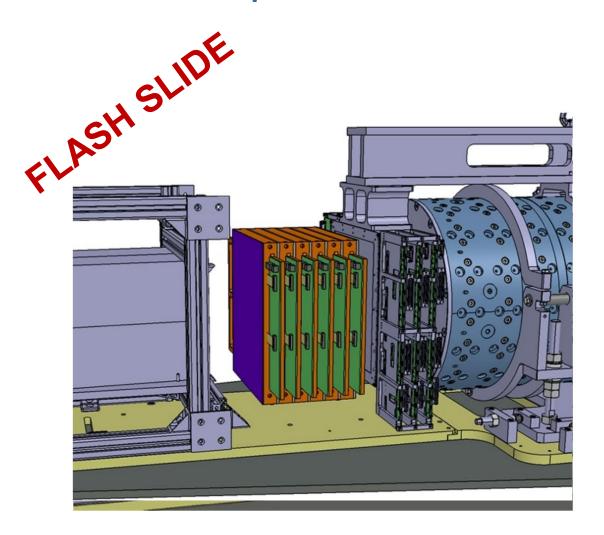

### The FASER pre-shower

L. Paolozzi - EPFL Seminar

- Enable di-photon channel in FASER.

- Distinguish two ultra-collimated EM showers.

- Time resolution target: ~100 ps.

- Very large pixel dynamic range: 0.5 fC 64 fC.

- Large area prototype submission: July 2021.

- Full-reticle ASIC submission: March 2022.

8/11/2021 29

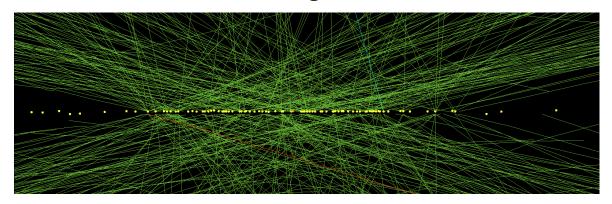

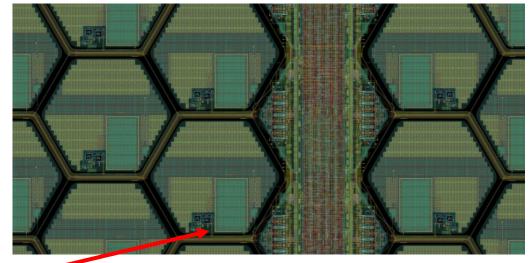

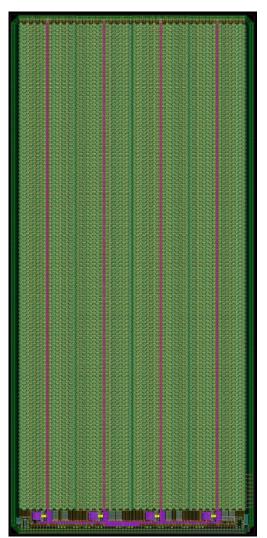

### Monolithic design for 4D tracking: FASER pre-shower

- <1 Ωcm, heavily P-doped substrate.

- Negative High Voltage applied to the substrate.

8/11/2021

## Monolithic design for 4D tracking: FASER pre-shower

- Electronics inside the guard-ring, isolated from substrate using deep n-well.

- Triple well design: polysilicon, nmos and HBTs in an isolated pwell, pmos directly in the pixel nwell.

- Pixel and electronic deep n-wells are kept at positive low voltage.

L. Paolozzi - EPFL Seminar 8/11/2021

## Monolithic design for 4D tracking: FASER pre-shower

- Analogue electronics in pixel, digital electronics in a separate deep-nwell to improve noise robustness.

>95% fill factor.

- Target time resolution: ~100ps.

- Very large pixel dynamic range: 0.5 fC 64 fC.

- Polysilicon capacitance to nwell is too high to realize a proper biasing: pmos bias is necessary.

- Pixel bias at Vcc to avoid body effect on pmos.

- Polysilicon capacitance to nwell is too high to realize a proper biasing: pmos bias is necessary.

- Pixel bias at Vcc to avoid body effect on pmos.

- Capacitive coupling using a matrix of large area pmos distributed in the pixel.

- Polysilicon capacitance to nwell is too high to realize a proper biasing: pmos bias is necessary.

- Pixel bias at Vcc to avoid body effect on pmos.

- Capacitive coupling using a matrix of large area pmos distributed in the pixel.

- Nmos are preferred in sensitive nodes, to avoid unnecessary parasitic capacitance towards the input.

- Polysilicon capacitance to nwell is too high to realize a proper biasing: pmos bias is necessary.

- Pixel bias at Vcc to avoid body effect on pmos.

- Capacitive coupling using a matrix of large area pmos distributed in the pixel.

- Nmos are preferred in sensitive nodes, to avoid unnecessary parasitic capacitance towards the input.

- Signal routing after amplification stage requires shielded bus to avoid cross-talk to pixels.

- Digital electronics in separate well.

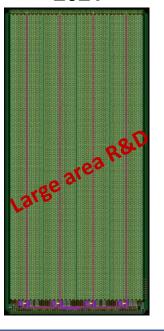

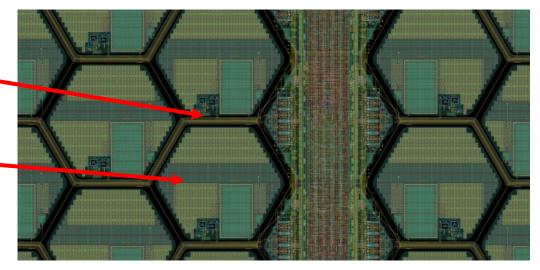

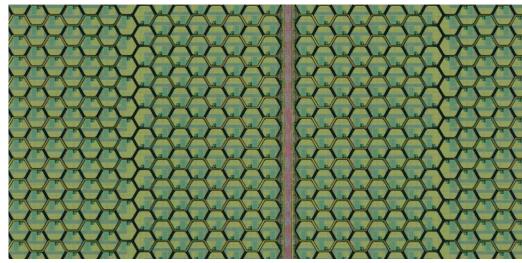

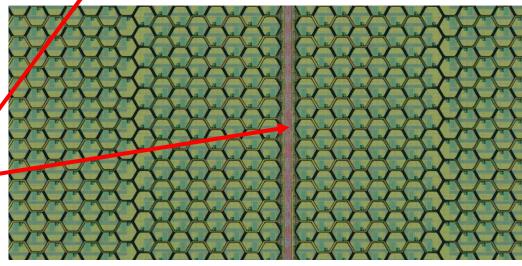

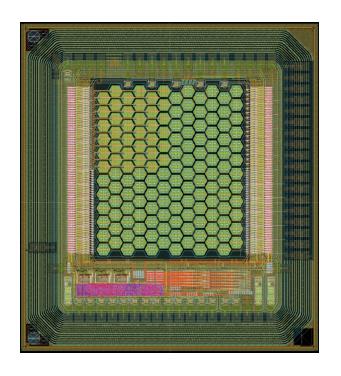

### Pre-production ASIC

- Large area, fully functional prototype  $(7.5 \times 15 \text{ mm}^2)$ .

- Two alternative test layouts with 3 columns.

- Submitted July 2021.

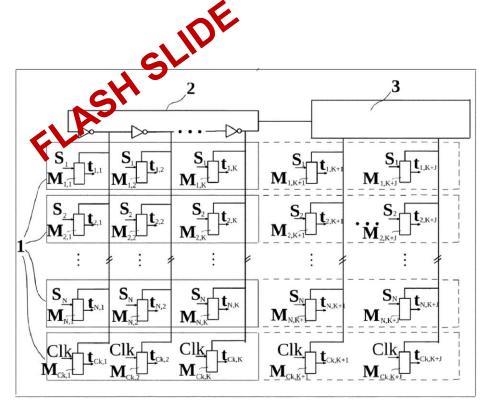

### A self calibrating, low-power TDC

- 16 channels, each made by three sets of latches (1) connected to the same ring oscillator (2) to measure TOA and TOT of the signal.

- 1 calibration channel is used to measure the period of the ring oscillator on an event-by-event basis (UniGe patent).

- Linear Feedback Shift Registers (3) are used to extend the dynamic range of the measurements / also to store and trasnfer data.

- The large load on the Ring Oscillator may reduce its speed: a chain of buffers is connected to maintain a high oscillation frequency.

- The Ring Oscillator is always running, to increase its stability, while the buffers can be activated on demand, to reduce the power consumption.

https://worldwide.espacenet.com/patent/search?q=pn%3DEP3591477A1

## **Summary**

- 1. SiGe HBTs for fast, low power timing measurement.

- 2. SiGe BiCMOS technologies.

- 3. R&D at the University of Geneva.

- 4. The FASER pre-shower detector.

- 5. The path toward picosecond time resolution.

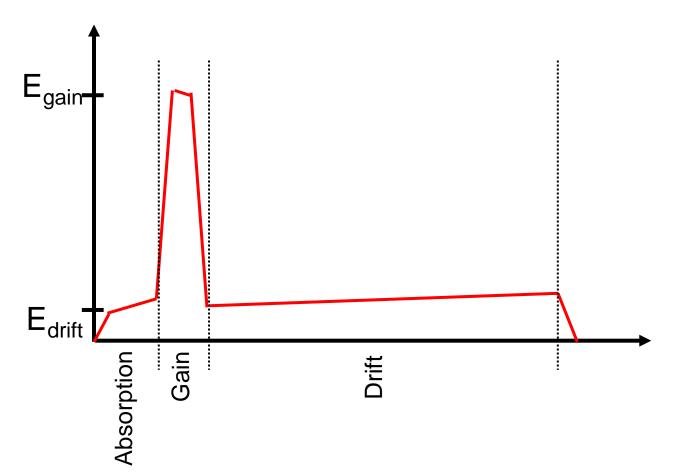

### PicoAD: The PicoSecond Avalanche detector

Multi-Junction, pixelated avalanche detector. **EU Patent EP18207008.6** n-type pixels High resistivity, p-doped layer n-region gain layer p-region gain layer Very low resistivity p-doped substrate

### PicoAD: The PicoSecond Avalanche detector

• Multi-Junction, pixelated avalanche detector.

L. Paolozzi - EPFL Seminar

**EU Patent EP18207008.6**

8/11/2021

### PicoAD: The PicoSecond Avalanche detector

Multi-Junction, pixelated avalanche detector.

#### EU Patent EP18207008.6

- The introduction of fully-depleted multi-pn junctions allows to engineer the electric field.

- New device with unique timing and reliability performance.

- Gain with 100% fill-factor.

- Geant4 + Cadence simulations estimate ~2ps time resolution contribution from the sensor.

- Requires low-noise, ultra fast electronics to be fully exploited.

UNIVERSITÉ DE GENÈVE

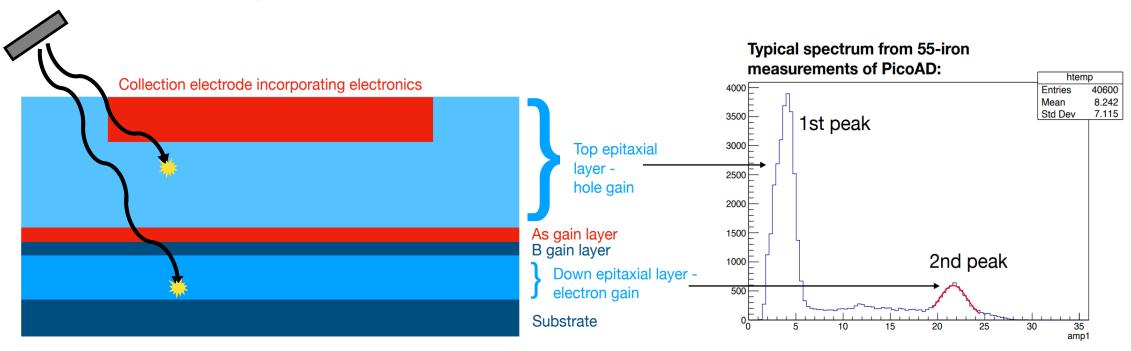

### First PicoAD prototypes

- Integrated in a special wafer for the ATTRACT prototype.

- Process design in collaboration with IHP.

- First prototype tested in lab and at SPS beam line.

### **CAVEAT:**

Not ideal manufacturing process, it was not possible to saturate the charge drift velocity.

8/11/2021

### PicoAD: First prototype test with Fe-55 source

39

**Fe-55** X-ray source: point-like charge deposition inside the sensor

Gain = 2nd peak / 1st peak before hole gain

### PicoAD: First prototype test with Fe-55 source

40

### Measurements of sensor gain using 55-iron source in climate chamber:

#### Measured sensor gain depends on temperature:

Higher gain for lower temperatures due to change in impact ionisation coefficient α:

$$G \propto e^{\alpha(E,T)\cdot d}$$

with  $\alpha(E,T) \propto e^{-(a+b\cdot T)/E}$

$G$  = Gain, d=distance, E=electric field

#### Significant gain of > 20

Note: challenging to determine due to convolution of sensor and frontend effects at lower temperatures

-> Proof of novel picoAD concept

Preliminary results from beam test are promising

UNIVERSITÉ DE GENÈVE

L. Paolozzi - EPFL Seminar 8/11/2021

### **MONOLITH Project: Targets**

### 5-year ERC Advanced project at University of Geneva. PI: Giuseppe Iacobucci.

- Develop the PicoAD technology for ionizing radiation.

- Develop picosecond electronics for large area chips (Front-End, TDC, Logic).

- Assess radiation hardness of the PicoAD.

- Integrate the sensor in a Full Reticle detector for HEP experiments.

# **MONOLITH Project: Milestones**

Starting date. July 2020:

Optimized front-end and wafers for picosecond timing. December 2020:

Low-power, picosecond TDC. December 2021:

December 2022: Small prototype integration.

June 2024: Full-reticle chip.

### CONCLUSIONS

- SiGe BiCMOS proved the feasibility of a monolithic integration of silicon pixel sensors for ionizing radiation for large area detectors with state-of-the-art space-time resolution.

- Previous prototypes showed 38 ps time resolution without avalanche gain.

- A full-reticle chip will be produced for the new FASER pre-shower, targeting 100 ps time resolution.

- The development of a 4D detector with picosecond time resolution is in progress with the MONOLITH project. State-of-the-art space and time resolution are possible in a single device.

## Publications and patents

#### **Articles:**

• First TT-PET prototype:

Proof-of-concept amplifier:

• Small-area pixels power consumption: arXiv:2005.14161 - Accepted for publication on JINST

• Hexagonal small-area pixels: JINST 14 (2019) P11008, https://doi.org/10.1088/1748-0221/14/11/P11008

• TT-PET demonstrator chip testbeam: JINST 14 (2019) P02009, <a href="https://doi.org/10.1088/1748-0221/14/02/P02009">https://doi.org/10.1088/1748-0221/14/02/P02009</a>

• TT-PET demonstrator chip design: JINST 14 (2019) P07013, <a href="https://doi.org/10.1088/1748-0221/14/07/P07013">https://doi.org/10.1088/1748-0221/14/07/P07013</a>

JINST 13 (2017) P02015, https://doi.org/10.1088/1748-0221/13/04/P04015

JINST 11 (2016) P03011, https://doi.org/10.1088/1748-0221/11/03/P03011

• TT-PET engineering: <u>arxiv:1812.00788</u>

• TT-PET simulation & performance: <u>arxiv:1811.12381</u>

#### **Patents:**

• PLL-less TDC & synchronization System: EU Patent EP18181123.3

• Picosecond Avalanche Detector: EU Patent EP18207008.6

L. Paolozzi - EPFL Seminar 8/11/2021 Extra

# Extra Material

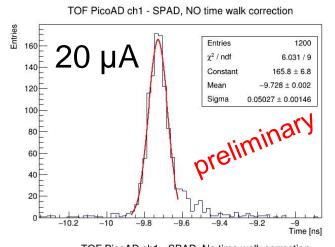

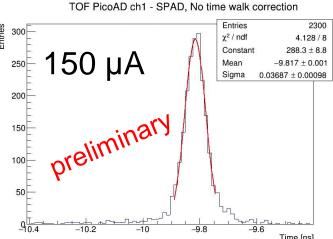

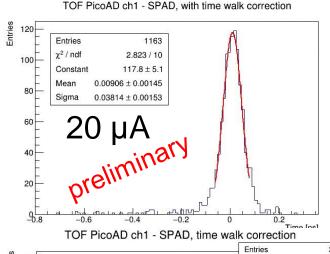

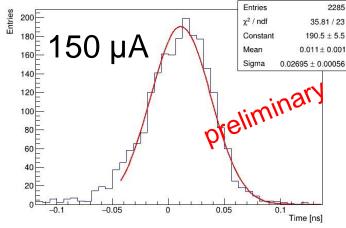

### PicoAD: Preliminary results from beam test

### No time walk correction

### With time walk correction

- A time resolution of 50ps is achieved at very low power consumption and without time walk correction.

- Integrates state-of-the-art time and space resolution in a single device.

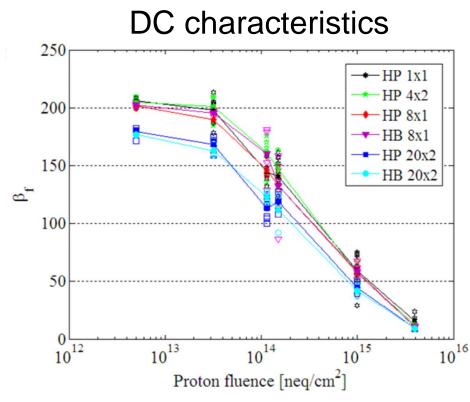

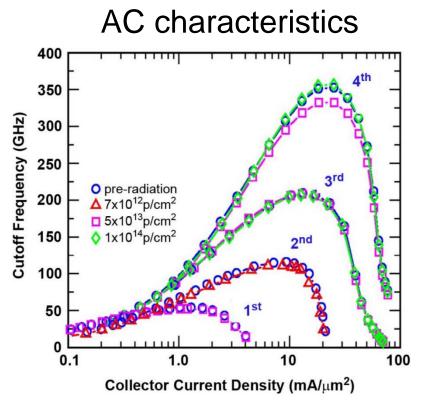

### Radiation hardness of standard commercial HBTs

S. Díez et al, IEEE Nuclear Science Symposuim & Medical Imaging Conference, Knoxville, TN, 2010, pp. 587-593, doi: 10.1109/NSSMIC.2010.5873828.

From: J.D. Cressler, IEEE transactions on nuclear science, vol. 60, n. 3 (2013)

No studies available on AC characteristics and noise above 10<sup>14</sup> p/cm<sup>2</sup>

L. Paolozzi - EPFL Seminar Extra 1