## **CROME**

# Hardware/Software Co-Simulation of a Zynq SoC inside the CROME Measurement and Processing Unit

Jonas BODINGBAUER, Katharina CEESAY-SEITZ, Hamza BOUKABACHE

23/11/2021 - System-on-Chip Interest Group Meeting - CERN

https://crome.web.cern.ch

Daniel Perrin, Gael Ducos, Markus Widorski, Michel Pangallo, Sarath Kundumattathil Mohanan, Doris Forkel-Wirth, Stefan Roesler

# **Agenda**

Hardware/Software Co-Simulation of a Zynq SoC inside the CROME Measurement and Processing Unit

- What is CROME?

- HW/SW Co-Simulation

- Short Demo

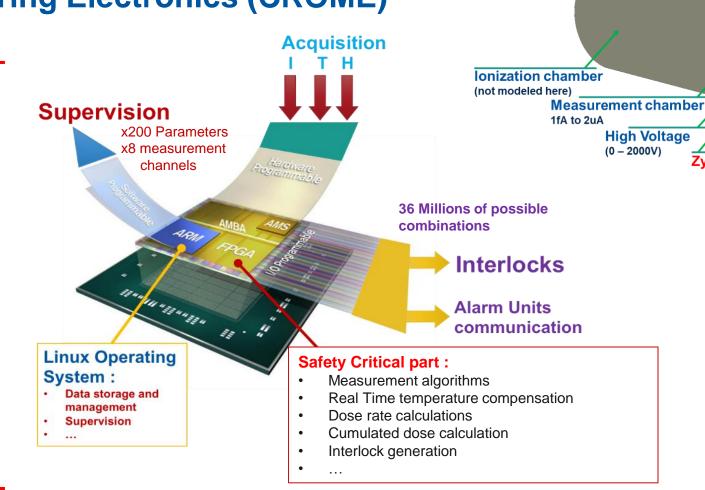

## **CERN Radiation Monitoring Electronics (CROME)**

New in-house developed and produced radiation monitoring system for CERN Radiation Protection

- Real-time monitoring of the ambient dose equivalent rate over **9 decades** (from nSv/h to Sv/h)

- Alarm and interlock functionality with a probability of failure down to 10e-7 (Link)

- Edge computing (an SoC FPGA based system)

- Long-term, permanent reliable data logging

- Unified solution for RP and environmental monitoring

HW-/SW Co-Simulation - Jonas Bodingbauer

Detector (Ionization chamber in this picture) CMPU - Electronics Core Monitoring & Processing Unit)

TOWARDS A NOVEL MODULAR ARCHITECTURE FOR CERN RADIATION MONITORING Radiat Prot Dosimetry. 2017 Apr; 173(1-3): 240–244.

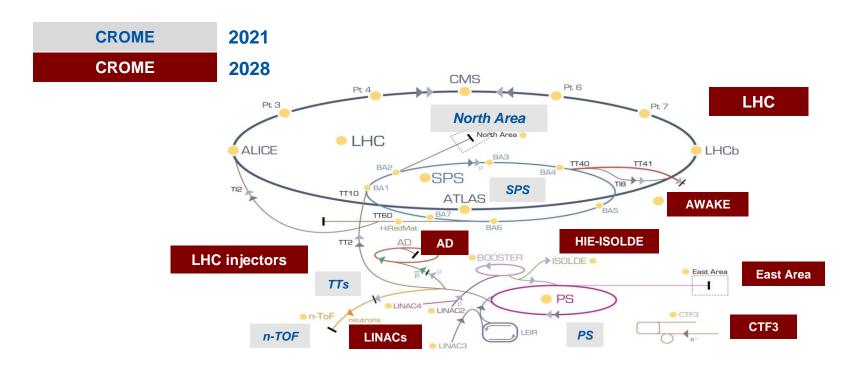

### Radiation & Environmental Monitoring System at CERN

Currently we have replaced:

153 radiation monitors, 78 alarm units, 107 Power Supplies

(532 pieces of equipment)

Self production capabilities

## **CERN Radiation Monitoring Electronics (CROME)**

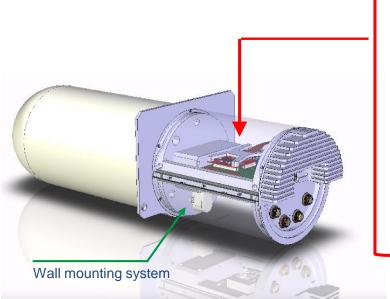

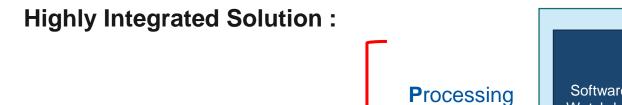

**Highly Integrated Solution:**

Fault Resilient Design for 28nm ZYNQ SoC based Radiation Protection Monitoring System Fulfilling Safety Integrity Level 2

<u>First System-on-Chip Workshop</u> – CERN – June 12, 2019

SoM cooling

Zyng 7000 based SoM

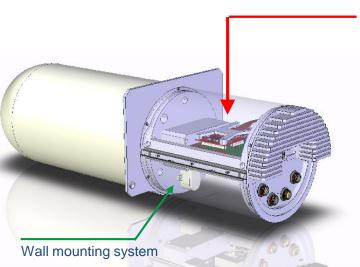

### **CERN Radiation Monitoring Electronics (CROME)**

**S**ystem

**ARM**

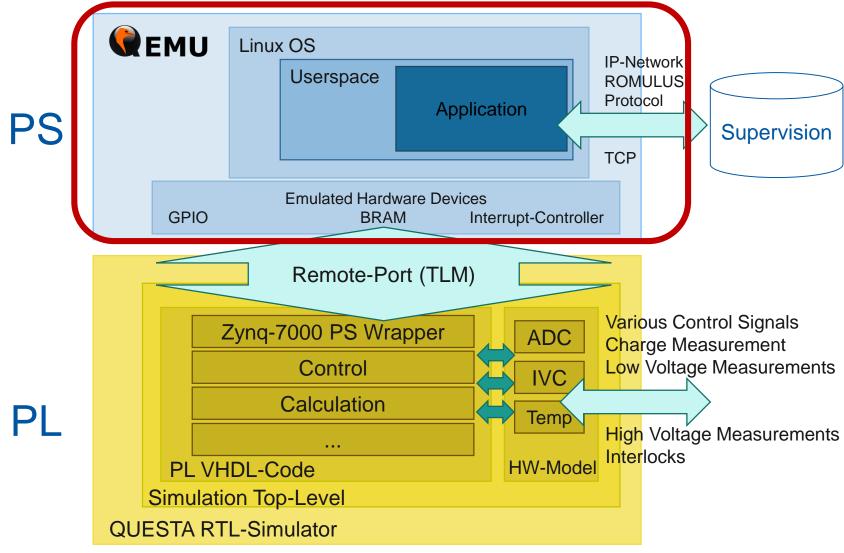

## Hardware-/Software Co-Simulation

#### What?

Simulation of software and hardware at the same time

### Why?

- System level verification

- Simplifies development because of visibility of signals

- Much faster than simulation of CPU in RTL → feasible

- Virtual Prototyping. Hardware does not need to be available yet (not applicable for us)

#### How?

23/11/2021

- Two simulators connected together to allow for simulation of entire system, so: one for Software and one for Hardware

- QEMU simulating Linux and Questa for RTL

- "A generic and open source machine emulator and virtualizer"

- "provides a virtual model of an entire machine (CPU, memory and emulated devices) to run a guest OS"

- Translates Guest instructions dynamically to Host instructions

HW-/SW Co-Simulation - Jonas Bodingbauer

#### Our case

- Emulates the two ARM Cores and (implemented) peripherals on a desktop PC

- Runs Linux and embedded application

CERN Radiation Monitoring Electronics and its Integration Into both, CERN and ESS Supervisory Systems

System-on-Chip Interest Group Meeting – CERN – April 29th 2020

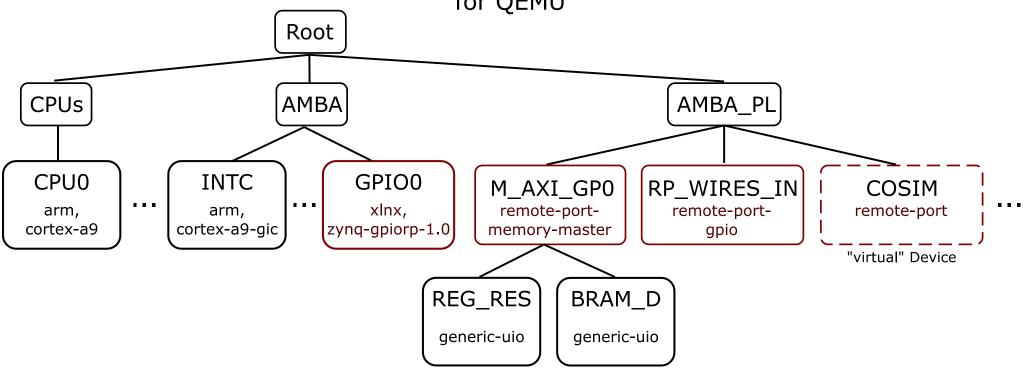

# HW - Device Tree for QEMU

### Register XGPIOPS\_DIRM\_OFFSET Details

This register controls whether the IO pin is acting as an input or an output. Since the input logic is always enabled, this effectively enables/disables the output driver.

Each bit of the bank is independently controlled.

This register controls bank0, which corresponds to MIO[31:0].

| Field Name  | Bits | Туре | Reset Value | Description                                                                                                                     |

|-------------|------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| DIRECTION_0 | 31:0 | rw   | 0x0         | Direction mode                                                                                                                  |

|             |      |      |             | 0: input                                                                                                                        |

|             |      |      |             | 1: output                                                                                                                       |

|             |      |      |             | Each bit configures the corresponding pin within the 32-bit bank                                                                |

|             |      |      |             | NOTE: bits[8:7] of bank0 cannot be used as inputs.                                                                              |

|             |      |      |             | The DIRM bits can be set to 0, but reading DATA_RO does not reflect the input value. See the GPIO chapter for more information. |

Xilinx Zynq-7000 SoC Technical Reference Manual Page 1338

# **EMU GPIO Device**

**CROME System**

```

static uint64_t gpio_dir_prew(RegisterInfo *reg, uint64_t val)

ZynqGPIOState *s = ZYNQ GPIO(reg->opaque);

uint32_t data = (uint32_t) val;

uint32_t data_old = *(uint32_t *)reg->data;

int bank = gpio_get_bank(reg->access->addr);

int width = bank==1 ? 22 : 32;

uint32_t mask = data ^ data_old; //all bits where something changed

gpio_update_pins(s, bank, ∅, width, mask,

(s->regs[R GPIO DATA X(bank)]),(s->regs[R GPIO OEN X(bank)]),

data,data_old);

return val;

```

Applications Linux Device Drivers

**Emulated** Devices

**QEMU**

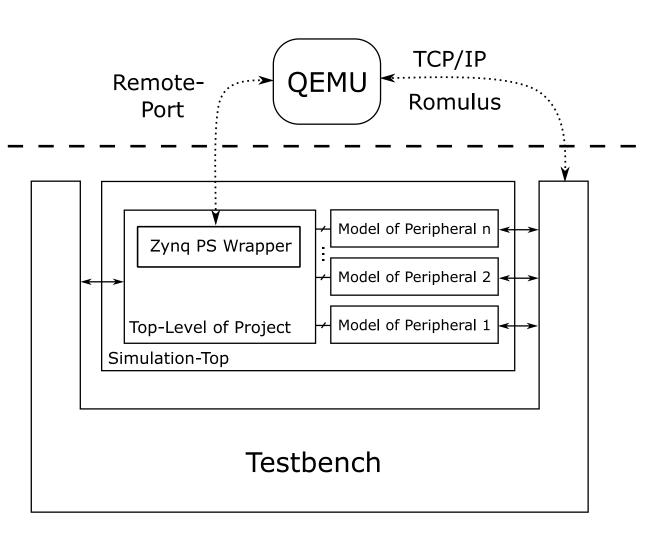

# Overview of communication, simplified

Software issues pin change

Device-driver writes to some memory location

RTL simulator receives packet and translates it to pin-changes

QEMU device gets triggered, translates and sends packet

Simulator propagates changes to design

# libsystemctlm-soc / remote-port

- Communication between two simulators

- RTL: SystemC library for sending and receiving remote-port packets

- QEMU: C counterpart, "Virtual QEMU device"

- TLM semantics

- SystemC bridges, which translate packets from tlm to pin changes

- AXI, ACE, CHI, CXS, PCI

- GPIO

23/11/2021

- Provides time synchronisation between simulators

- Uses unix-socket or tcp

## **RTL-Simulation**

- Run simulation on Top-Level

- Exchange the Zynq component

- Implement Models of Peripherals

- Our Case: ADCs, Temp Sensor, Measurement electronics

- Current Objective: writing a system-level testbench using UVM

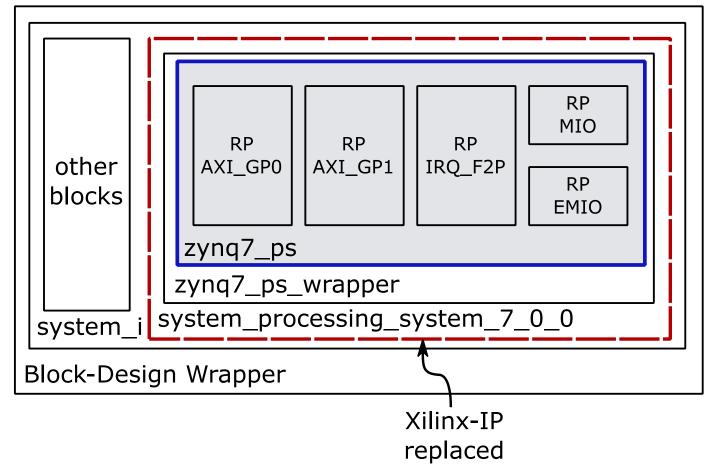

### **RTL-Simulation**

- Replacing instance system\_proccessing\_system7\_0\_0 with custom instance

- Exposes AXI busses GPIO and other connections to VHDL

- Translates messages from remote-port to RTL pin changes and vice versa

- Needs Mixed Language Simulator (SystemC, VHDL and/or Verilog)

- Developed with Questa

REMUS

Supervision

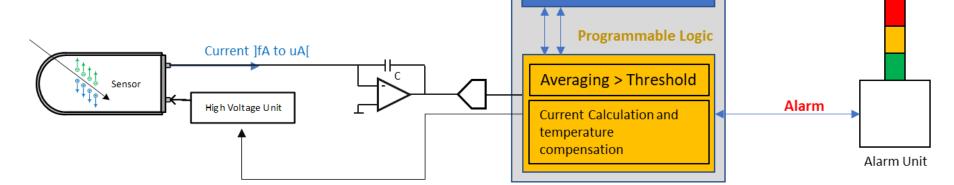

# **Demo Setup**

- When average input current is **above** a threshold an **alarm** is triggered

- This alarm results in a pin change in hardware

- Also sent to software

- Configured so it only averages one value → instant changes

Zynq SoC

**Processing System**

**User Application**

Linux

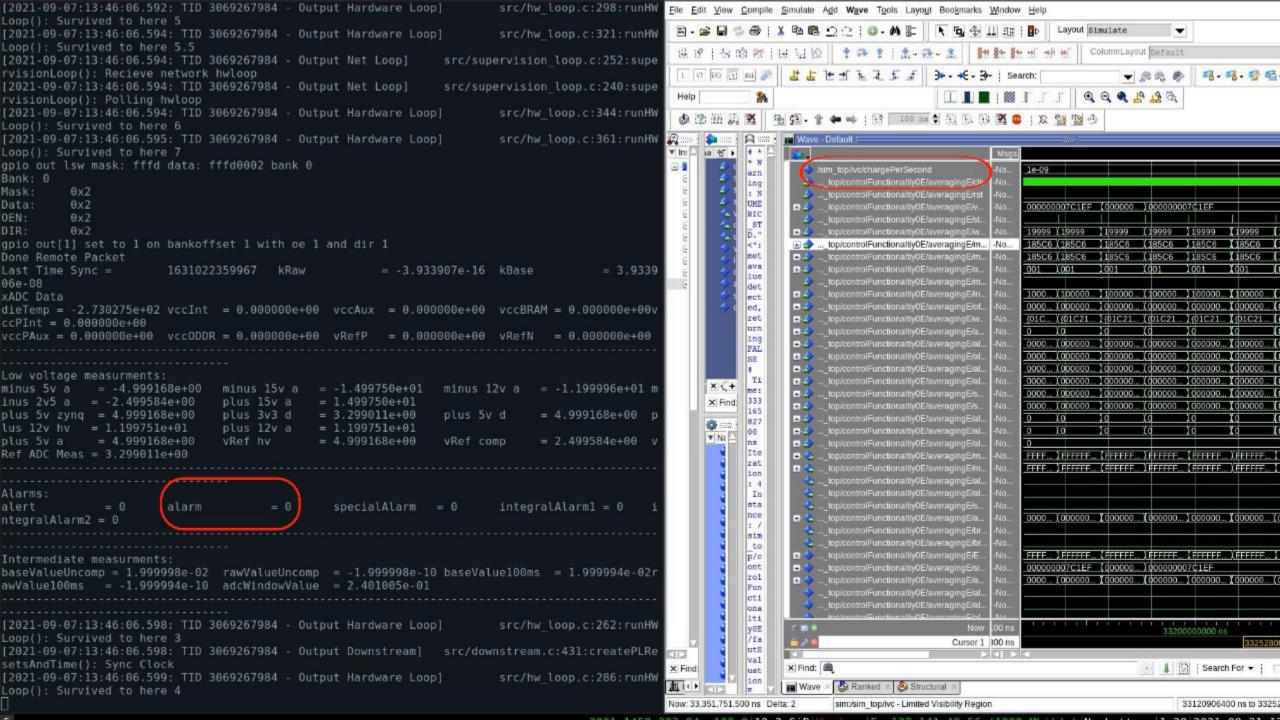

### Results

Introduction

- Working Co-Simulation for the ZYNQ and furthermore the **CMPU**

- Currently used for debugging of additional features

- Simulation speed is only ~30 times slower than realtime **@1MHz** for our design

## Outlook

- Could likely be adjusted to other projects

- If SystemC Model exists, RTL part could be replaced to further increase simulation speed

- Other open source tools like Verilator could be interesting to further speed up simulation

**HW/SW Co-Simulation**

## **Open Source Projects Used**

- Xilinx Qemu https://github.com/Xilinx/qemu

- Xilinx libsystemctlm-soc <a href="https://github.com/Xilinx/libsystemctlm-soc">https://github.com/Xilinx/libsystemctlm-soc</a>

- Xilinx qemu-devicetrees <a href="https://github.com/Xilinx/qemu-devicetrees">https://github.com/Xilinx/qemu-devicetrees</a>

- Rick Wertenbroek, CoSimulation https://blog.reds.ch/?p=1180

23/11/2021

Custom plastic chamber with

graphite coating

### **CERN Radiation Monitoring Electronics (CROME)**

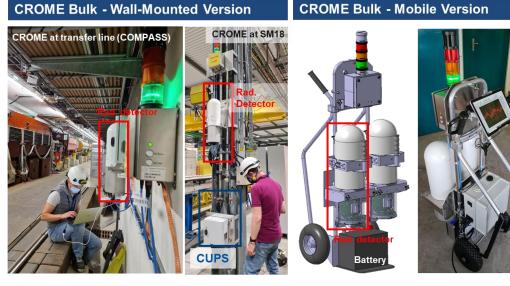

### Two configurations:

### CROME Rack Version – High radiation Areas

### CROME Bulk Version – Low radiation Areas