## The Saltro chip design for TPC pad readout

#### **Talk outline**

The historical perspective.

The SAltro demonstrator.

Projections and ideas for the future.

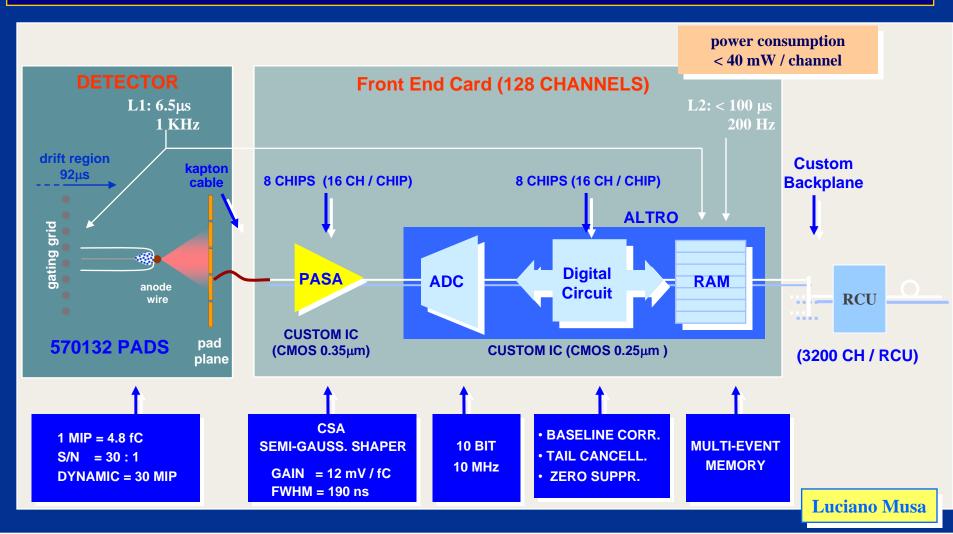

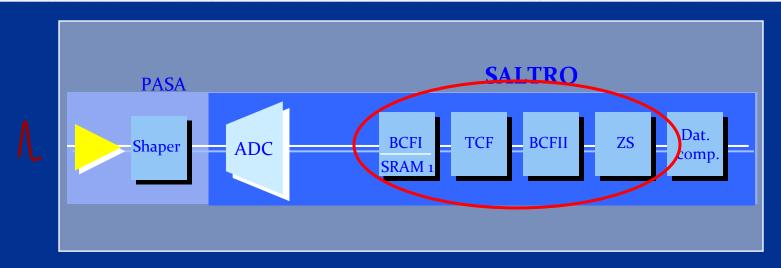

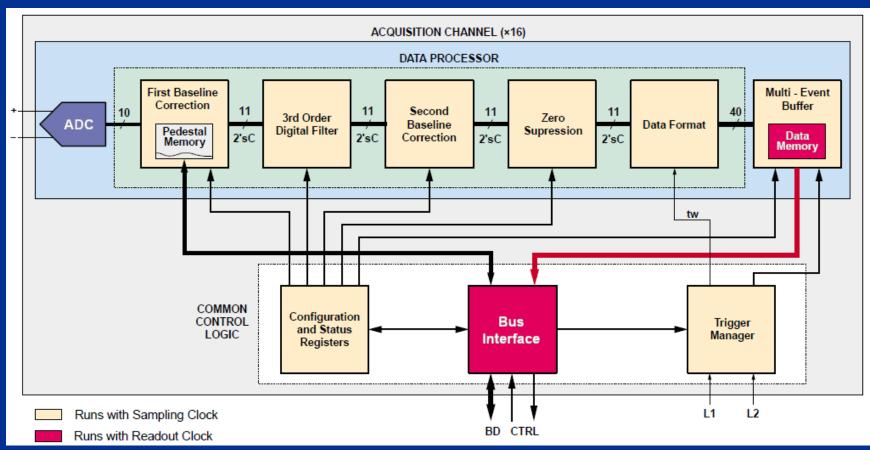

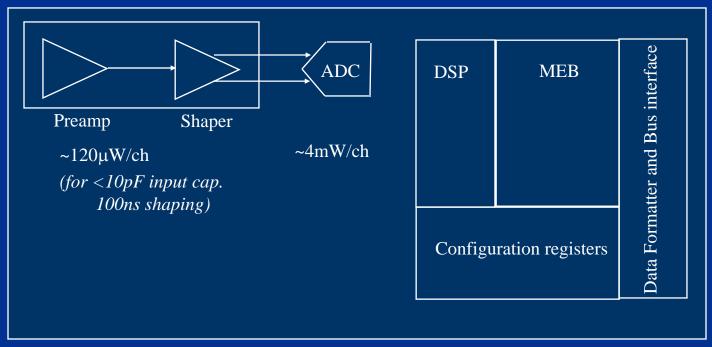

#### S-Altro architecture

#### Based on the existing PASA + Altro electronics designed for the Alice TPC

#### **SAltro Demonstrator**

#### Goal:

To demonstrate integration per channel of an analog frontend, an ADC and digital signal processing in a single chip.

Data processing of 100us of data sampled at 10MHz.

Prepare ideas for TPC readout in the ILC & CLIC

#### **SAltro Demonstrator Architecture**

- 16 Channels.

- **Sampling rate 10, 20, 40MHz.**

- ADC: 10 bits per sample.

- Level 1 commences sampling of a data-stream.

- 1008 (max) samples per data-stream.

- DSP for zero suppression.

- 40 bit word data packets containing timestamp and length.

- Possibility to by-pass DSP to have raw data.

- MEB (1024\*40 RAM).

- Max. storage of 4 non-zero suppressed data-streams.

or

- Max. storage of 8 zero suppressed data-streams and/or with reduced data-stream length.

- Level 2 must arrive before next Level1 in order to keep the data.

- <80 MHz readout on 40 bit CMOS bus.

Technology: IBM 130nm CMOS 8RFDM

## Saltro demonstrator Preamplifier/Shaper

- Single-ended input, differential output

- Dual polarity

- 4 Gain options: 12, 15, 19 & 27mV/fC

- 4 Shaping times: 30, 60, 90 & 120ns.

- Linearity <1% to 150 fC</li>

- Shutdown mode (for power pulsing via a duty cycle clock)

- Preamplifier enable (bypass shaper)

$I_{det}$   $C_f$   $C_{pz}$   $R_{pe}$   $R_{$

Size: 1100um X 210um Power: 8.4mW/channel Supply: 1.5V

Massimiliano De Gaspari

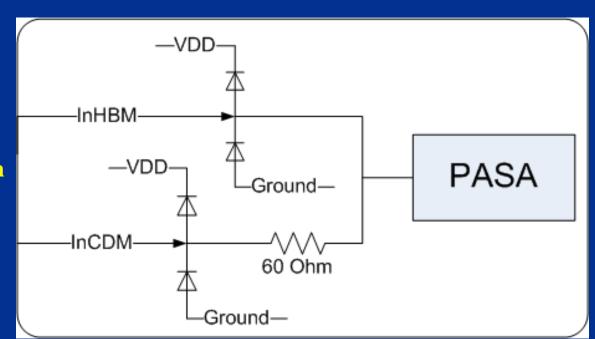

## **Front-end: ESD protections**

Each front-end has two input pads in parallel (only one bonded):

- Simple double diode protection scheme (Human Body Model)

- Structure with series resistor for enhanced protection (Charged Device Model)

The series resistor adds noise to the input signal.

Noise: 300e<sup>-</sup> @ 10pF detector capacitance

**Expected noise increase (simulated): 20-30%**

Massimiliano De Gaspari

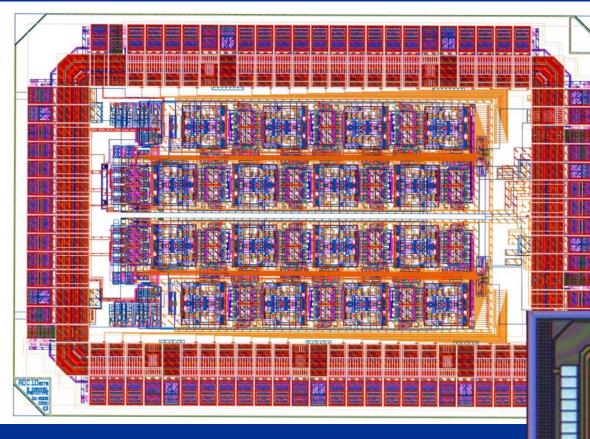

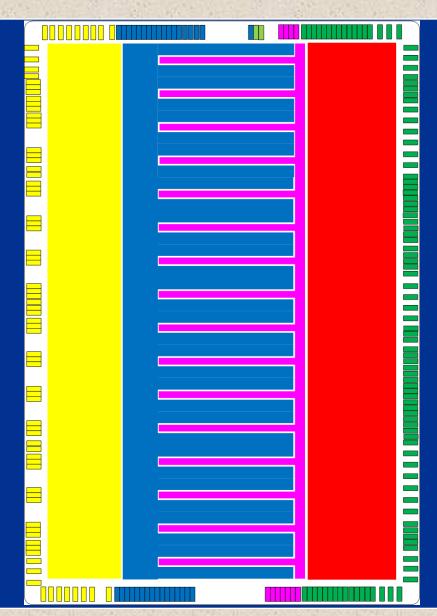

# Pipelined ADC: 2-Channel Prototype Layout

Single ADC area Prototype area

1.57 X 0.45 = 0.7 mm<sup>2</sup> 2.35 X 1.6 = 3.76 mm<sup>2</sup>

A 10-bit 40MS/s Pipelined ADC in a 0.13µm CMOS Process – TWEPP 2009

ENOB =  $\sim$ 9 FOM = 1.56pJ

**Hugo França-Santos**

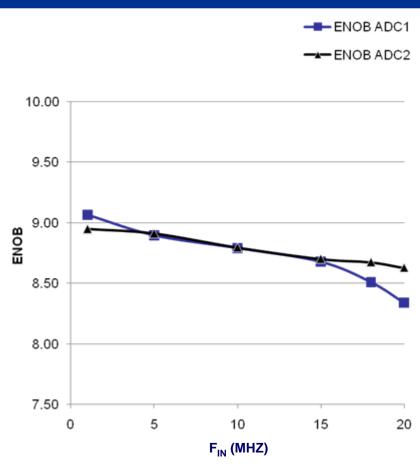

## ADC TEST: Dynamic Characterization at 40MS/s

| Dynamic Performance at 40                    | ENOB            |        |        |      |

|----------------------------------------------|-----------------|--------|--------|------|

| PARAMETER                                    | INPUT FREQUENCY | ADC1   | ADC2   | UNIT |

|                                              | 1.0071MHz       | 9.07   | 8.95   | Bits |

|                                              | 4.9988MHz       | 8.90   | 8.91   |      |

| Effective Number of Bits (ENOB)              | 9.9915MHz       | 8.79   | 8.80   |      |

| Effective Number of Bits (ENOB)              | 14.9841MHz      | 8.68   | 8.70   |      |

|                                              | 17.9993MHz      | 8.51   | 8.67   |      |

|                                              | 19.9890MHz      | 8.34   | 8.63   |      |

|                                              | 1.0071MHz       | 56.33  | 55.63  | dB   |

|                                              | 4.9988MHz       | 55.32  | 55.41  |      |

| Signal to noise and distortion ratio (SINAD) | 9.9915MHz       | 54.68  | 54.71  |      |

| Signal to holse and distortion ratio (SiNAD) | 14.9841MHz      | 54.00  | 54.14  |      |

|                                              | 17.9993MHz      | 52.98  | 53.97  |      |

|                                              | 19.9890MHz      | 51.96  | 53.70  |      |

|                                              | 1.0071MHz       | -75.03 | -74.08 | dB   |

|                                              | 4.9988MHz       | -71.12 | -69.94 |      |

| Spurious free dynamic range (SFDR)           | 9.9915MHz       | -64.78 | -68.74 |      |

| Spanous nee dynamic range (SFBN)             | 14.9841MHz      | -61.13 | -72.25 |      |

|                                              | 17.9993MHz      | -58.89 | -66.34 |      |

|                                              | 19.9890MHz      | -56.89 | -68.06 |      |

|                                              | 1.0071MHz       | -69.66 | -70.73 | dB   |

|                                              | 4.9988MHz       | -63.12 | -66.90 |      |

| Total Harmonic Distortion (THD)              | 9.9915MHz       | -64.44 | -65.65 |      |

| . Star Harmonic Bistordon (HIB)              | 14.9841MHz      | -67.57 | -69.26 |      |

|                                              | 17.9993MHz      | -62.01 | -64.66 |      |

|                                              | 19.9890MHz      | -60.87 | -65.69 |      |

Power Consumption: 34 mW

**Hugo França-Santos**

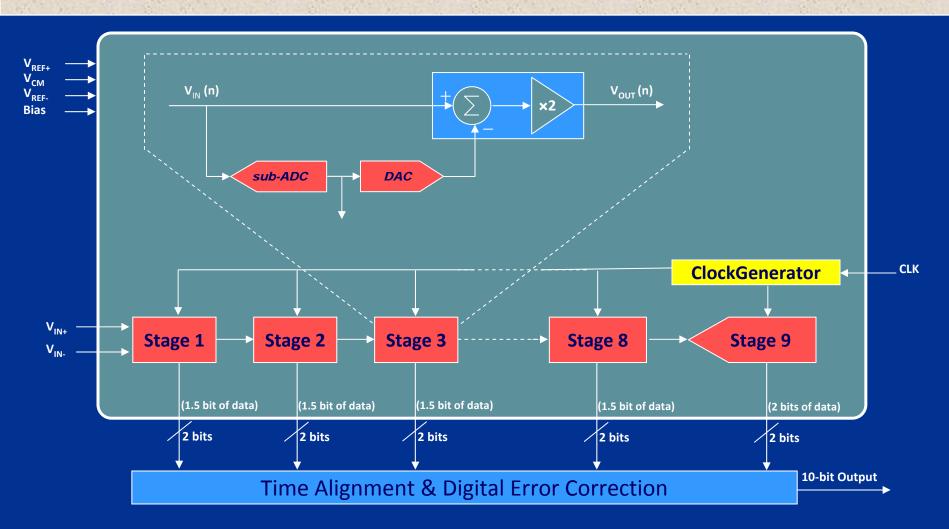

## Pipeline ADC

10bit, 40MHz, 1.5V supply, 34mW power, 0.7mm<sup>2</sup> area

Power pulsing possible through bias pin.

Massimiliano De Gaspari

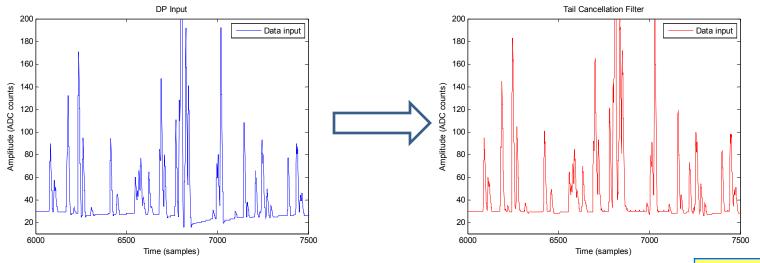

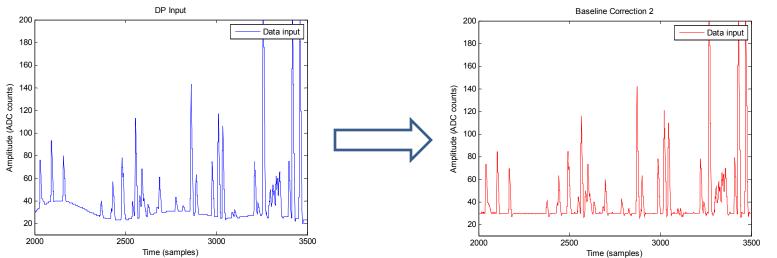

## **DP** functions

| Baseline correction 1 | Removes systematic offsets that may have been introduced due to clock noise pickup etc.  The SRAM is used for storage of baseline constants which can then be used a look-up table and subtracted from the signal. |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tail cancellation     | Compensates the distortion of the signal shape due to very long ion tails.                                                                                                                                         |

| Baseline correction 2 | Reduces low frequency baseline movements based on a moving average filter.                                                                                                                                         |

| Zero suppression      | Removes samples that fall below a programmable threshold.                                                                                                                                                          |

Eduardo Garcia

## **DP** simulation results

> TCF example test: rest of the filters are disabled.

> BC2 example test: rest of the filters are disabled.

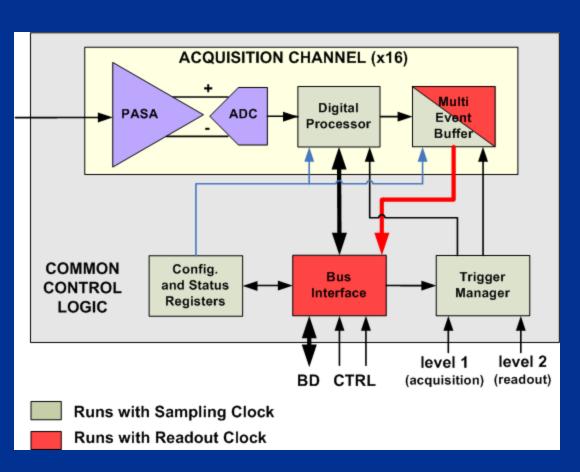

## S-ALTRO DP plus Altro control and interface

L1: Starts the data acquisition.

L2: Validates data from previous L1.

BD: 40 bit bidirectional bus; 20 bits address + 20 bit data. 80 Mbps readout.

**CTRL**: 6 bits including

Global Reset, Sampling and Readout clocks.

Eduardo Garcia

## DSP, memories and data-formatter

#### **Conditions:**

Static Analysis Toggle probability: 0.3

VDD = 1.5V Temperature: 25 C

Sclk = 50MHz Voltage variation: 10%

Rdoclk = 90Mhz Signoff verification

#### **Encounter Statistical Power Analysis:**

Average power (considered in rail analysis): 118.62 mW

P. Aspell

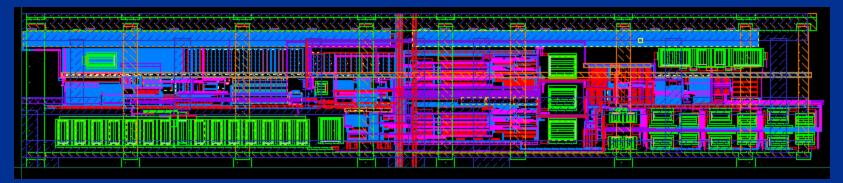

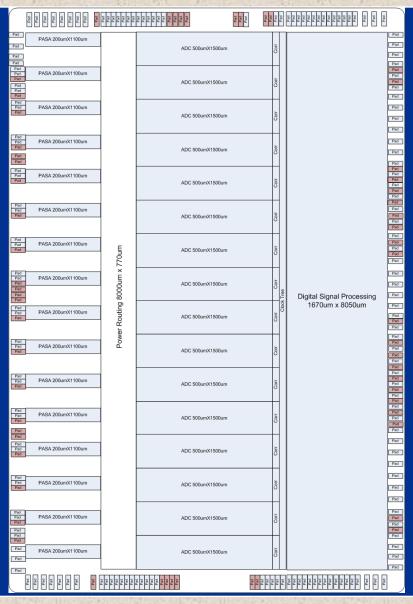

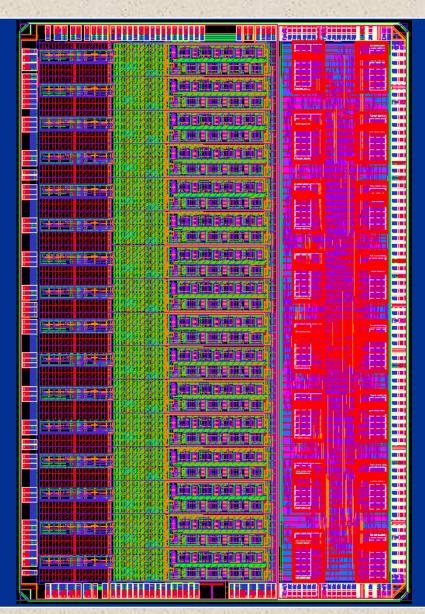

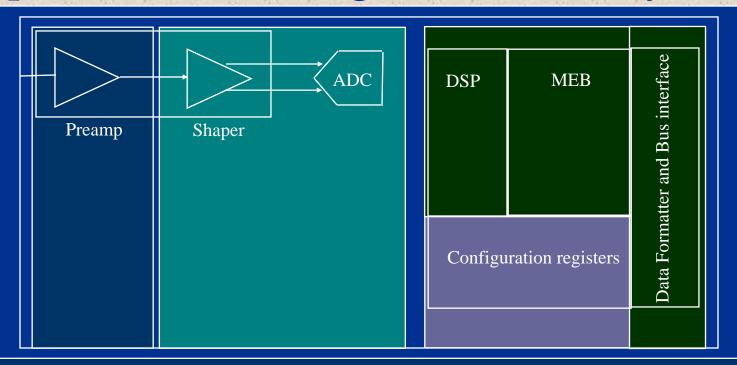

## **S-ALTRO** Demonstrator Floorplan

16-channels:

PASA 210um X 1100um

ADC 500um X 1500um

Digital Signal Processing

1670um X 8050um

The wide power routing ensures low IR power supply drop (10mV for the ADC)

PASA ~8mW/ch, ADC 32mW/ch @40MHz Digital functions ~114mW Total power ~ 750mW

### **Power domains**

**Power domains:**

PASA analog

ADC analog

ADC digital

Digital core

Digital Pads

Power supply decoupling capacitors:

600pF/channel PASA

600pF/channel ADC analog

40pF/channel ADC reference voltages

80pF/channel ADC digital

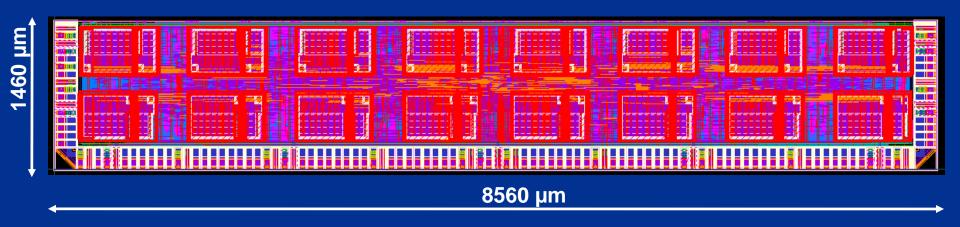

## Layout

Size: 5750um x 8560um (49.22mm<sup>2</sup>)

MPW organised by CERN.

Chip submitted in August 2010

Expected back at the end of 2010.

The pad placement has been optimised for packaging within a TQFP 176 pin package.

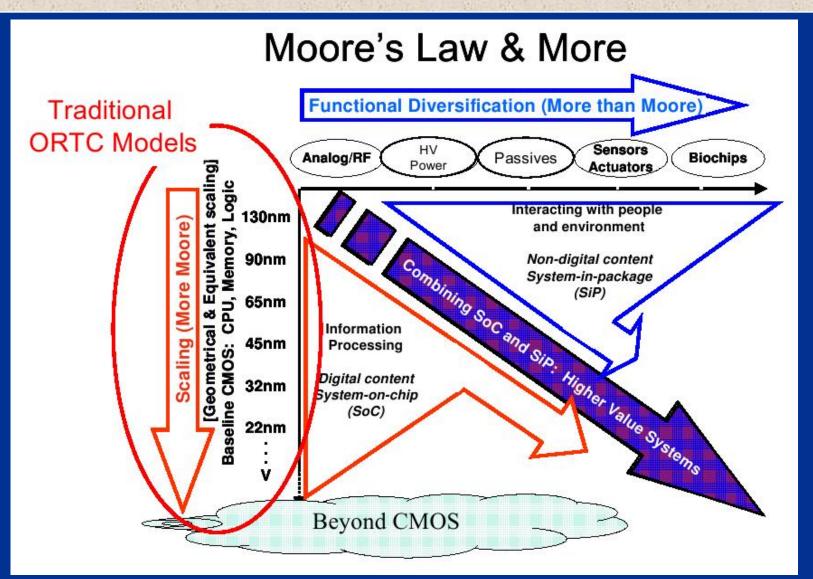

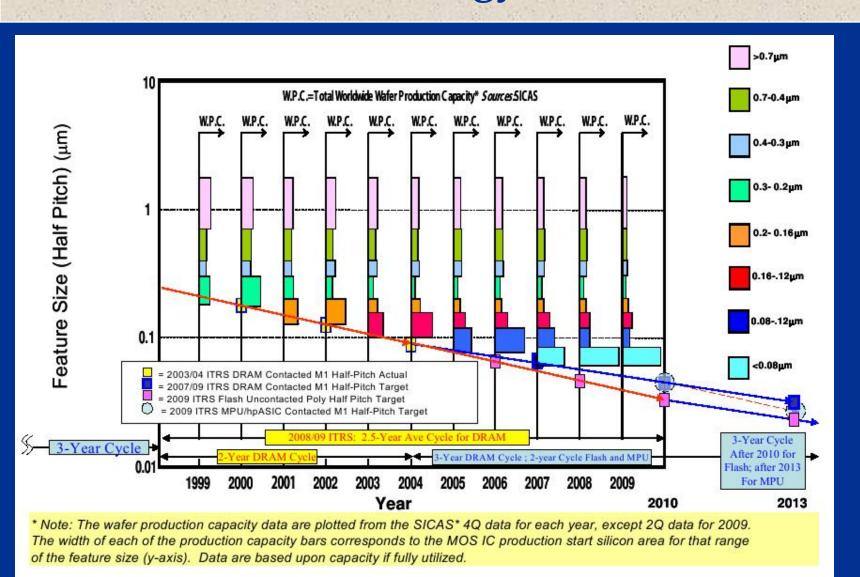

## The Future & Technology Trends

Source: ITRS roadmap 2009

# **Technology Trends**

Source: ITRS roadmap 2009

## **Technology: CERN microelectronics group**

- In addition to our current use of 0.25μm, 0.13μm and 90nm CMOS technologies CERN are now investigating 65nm CMOS technology.

- 12" wafers

- <10 Metal layers

- Vdd = 0.9V to 1.2V

- 840k gates/mm<sup>2</sup>

- Regular MPWs.

- LP process uses thicker gate oxide to GP to reduce leakage.

| Standard Offering |                            | 65GP      | 65LP      | 65LPG    |          |

|-------------------|----------------------------|-----------|-----------|----------|----------|

|                   |                            |           |           | G        | LP       |

| Vt                | Low                        | <b>()</b> | <b>(</b>  |          | 0        |

|                   | Medium Low                 |           | <u> </u>  |          |          |

|                   | Standard                   | <b>a</b>  | <b>@</b>  | <b>@</b> | <b>@</b> |

|                   | High                       | 9         | <b>②</b>  | <u> </u> | <u> </u> |

| Ю                 | 1.8V                       | <b>3</b>  |           |          |          |

|                   | 1.8V (2.5V Under-drive)    | <u> </u>  | <b>a</b>  | •        |          |

|                   | 2.5V                       | <u> </u>  | <b>②</b>  | •        |          |

|                   | 3.3V (2.5V Over-drive)     | <b>a</b>  | <b>()</b> | •        |          |

|                   | 3.3V                       | <u> </u>  | <u> </u>  |          |          |

| SRAM              | Ultra High Density (0.499) | <u> </u>  |           |          |          |

|                   | High Density (0.525)       | <u> </u>  | <b>a</b>  |          | <b>②</b> |

|                   | High Current (0.62)        | <b>a</b>  | <u> </u>  | <b>O</b> | <u> </u> |

|                   | Dual Port (0.97)           | <u> </u>  | <u> </u>  | <u> </u> | 0        |

|                   | Dual Port (1.158)          | <u> </u>  |           |          | <b>@</b> |

|                   |                            |           |           |          |          |

- CERN are now evaluating several 65nm design kits.

- Test structure submission planned for early 2011. To be followed by radiation studies.

- Standard cell libraries are available. They will probably need modification to be compatible with our needs.

# **Digital**

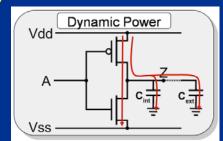

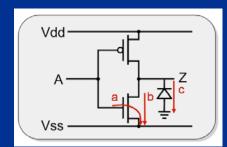

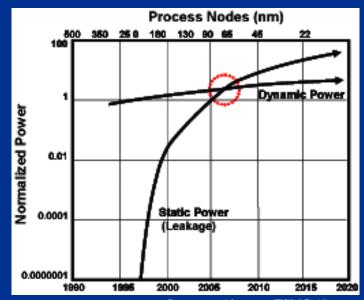

Scaling reduces source/drain capacitances and reduces power supply levels.

- Dynamic power goes down.

- $P_{dyn} = (C.Vdd^2 + Q_{short\_circuit} Vdd) f$  . activity

- However static power increases even in CMOS:

- Leakage currents increase including gate leakage current.

- Multiple power domains possible (vdd= 0.9V to 1.2V) depending on operating frequency required.

- » Very high speed : Lowest Vt and max Vdd

- » Moderate and Low Speed: higher Vt and reduced Vdd.

- The digital power consumption will take a larger % of total chip power in future designs compared to previous chips.

Source: Altera on TSMC 65nm

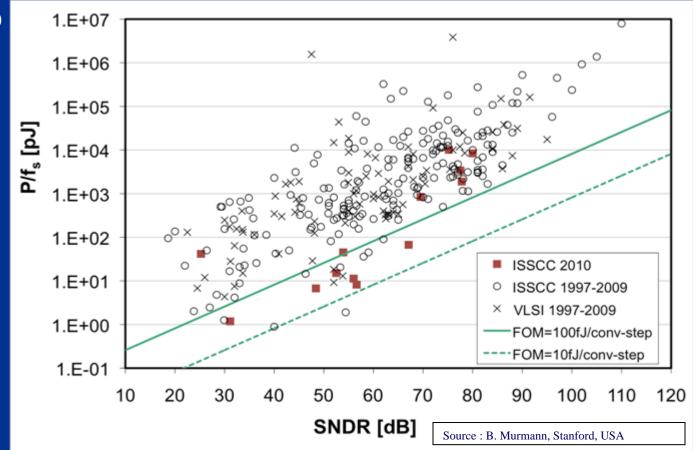

### **ADC** Trends

- FOM  $\sim$  P / (2<sup>ENOB</sup>. 2BW)

- 1pJ is high

- (~40mW @ ENOB 9, 40MS/s)

- 100fJ is good

- (~4mW @ ENOB 9, 40MS/s)

- 50fJ excellent

- (~2mW @ ENOB 9, 40MS/s)

#### State of the art:

A 30fJ/conversion 8b 0 to 10MS/s Asynchronous SAR ADC in 90nm CMOS. P. Harp et. al. IMEC ISSCC 2010 [They measured 69uW at 10MS/s,]

A 550uW 10b 40MS/s SAR ADC with Multistep Addition-only Digital Error Correction, Sang-Hyun Cho et al. CICC 2010 (FOM = 42fJ/conversion) designed in 0.13um CMOS

P. Aspell CERN

## Front-ends

- Front-end power can be very finely tuned but requires detailed knowledge of the sensor characteristics.

- » Total input capacitance (sensor + coupling to neighbours + board) is required to optimise the input transistor current.

- » Charge collection properties are required to make the correct choice of shaping time. If the shaping time is too small ballistic deficit will degrade S/N.

- Input transistor current scales with detector capacitance and charge collection time. Approx.  $10\mu\text{A/pF}$  for 25ns shaping and ~  $2.5\mu\text{A/pF}$  for 100ns shaping.

| Rough estimate of front-end power budgets |                   |                  |  |  |

|-------------------------------------------|-------------------|------------------|--|--|

| Electrode capacitance                     | for 100ns shaping | for 25ns shaping |  |  |

| 1pF                                       | 12μW ??           | 48μW             |  |  |

| 10pF                                      | 120μW             | 480μW            |  |  |

| 20pF                                      | 240μW             | 1.6mW            |  |  |

| 50pF                                      | 800μW             | 3.2mW            |  |  |

## Estimate for future power (static)

64 channels = Analog power ~ 263mW + Digital power ~ a few hundred mW. Approx. 400-500mW / chip.

128 channels = Analog power 526mW + Digital power ~ some hundreds mW. Approx. ~800-900mW / chip.

Should be possible to get < 7mW/ch for everything on a 128 ch chip.

Power management & pulsing may then be applied to reduce power further.

# Power management: Power domains for reducing power further during "down" time (dynamic).

Preamp > Reduce current via bias control, important to maintain a low impedance on the electrode.

Shaper > Reduce current to approx. zero via bias control. Vdd could be maintained.

ADC > Stop clock and reduce current to approx. zero via bias control. Vdd could be maintained.

Configuration reg.s > Reduce Vdd to minimum voltage necessary to hold data. Current consumption limited to leakage currents.

Digital logic > Switched off by reducing Vdd to 0V.

Duty cycle of UP/DOWN time determined by a clock.

## **Summary**

- The SAltro architecture is derived from the Altro architecture currently used for TPC readout in ALICE.

- The SAltro demonstrator chip has been designed and submitted.

- » Comprises 16 channels of Front-end + ADC + DSP on the same chip.

- » Chip return back from foundry for beginning of 2011.

- » Many things can be studied using the SAltro demonstrator:

- GEM properties: capacitance, charge collection time, optimal shaping, channel to channel coupling etc.

- Internal power pulsing on front-end and ADC via clock and bias control.

- The power consumption of the present 16 channel chip is about the same absolute value as future chips with more channels. This makes the demonstrator useful for groups studying external power pulsing.

- The future looks favourably on the SAltro architecture.

- » The industrial trend is with us continually looking for ways to reduce power.

- » The ADC remains the critical element w.r.t. power, however state of the art ADCs are becoming more and more power efficient.

- » Front-end power optimisation requires detailed knowledge of the sensor characteristics.

- » Power management within a chip is now common place in modern industrial chips and could be a useful tool for power pulsing.