## DAQ for AMBER Experiment

Igor Konorov on behalf of DAQ group

Institute for Hadronic Structure and Fundamental Symmetries (E18)

TUM Department of Physics

Technical University of Munich

AMBER Technical Board, 19-th April 2022

# PRM Setup

| Detectors     | #Planes | #Channels | FEE               | #FEs | #L0 MUX | Channel<br>Noise, Hz | Data rate<br>Total / L0 MUX<br>GB/s | Data rate<br>after TPC<br>TRG GB/s |

|---------------|---------|-----------|-------------------|------|---------|----------------------|-------------------------------------|------------------------------------|

| BMS 1-6       | 6       | 512       | iFTDC             | 16   | 2       | 10                   | 0.07 / 0.04                         | 0.002                              |

| HODO          | 5       | 528       | iFTDC             | 18   | 2       | 200                  | 0.2 / 0.1                           | 0.005                              |

| SciFi Tracker | 16      | 3072/1536 | Special iFTDC     | 16   | 2       | 10 000               | 0.4 / 0.2                           | 0.01                               |

| SciFi         | 44      | 3148      | iFTDC             | 99   | 12      | 100                  | 2.0 / 0.2                           | 0.04                               |

| Pixel Silicon | 12      | 113 M     | ALPIDE+FMUX       | 36   | 4       | 0                    | 0.32 / 0.08                         | 0.01                               |

| GEM           | 24      | 36864     | VMM/TIGER         | ?    | 6-12    | 1000                 | 1.0 / 0.16                          | 0.03                               |

| MWPC          | 15      | 11520     | iFTDC             | 180  | 15      | 100                  | 1.5 / 0.1                           | 0.04                               |

| ECAL          | 1       | 256       | Upgraded<br>MSADC | 16   | 2       | ?                    | ?                                   | ?                                  |

| TPC           | 4       | 192       | SIS3316           | 12   | 1       | -                    | 0.18 / 0.18                         | 0.18                               |

| TOTAL         |         |           |                   |      | 46-52   |                      | 5.2                                 | 0.32                               |

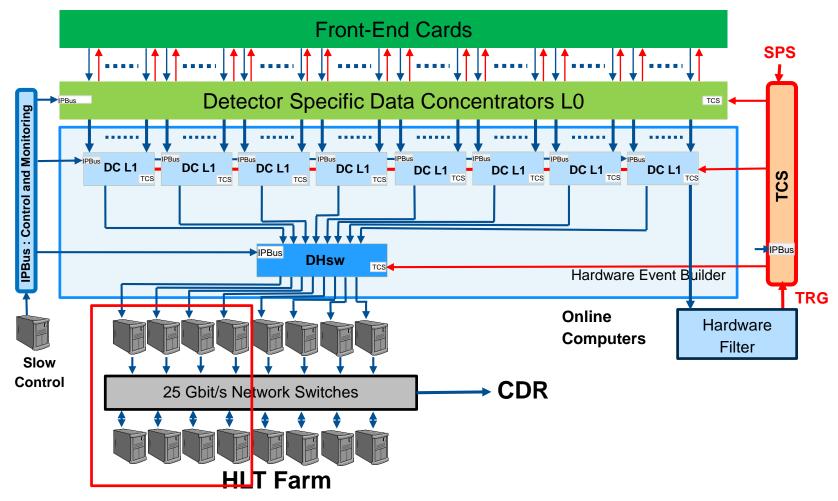

### COMPASS++/AMBER DAQ Architecture

### DAQ FPGA Cards for PRM Run

Expected data rate: 6 GB/s within spill or maximum 2 GB/s sustained.

#### Needed and available DAQ FPGA Cards:

- 8 x L1 MUX

- 1 x TS Builder

- 4 x Spill Buffer PCle cards

- Migration to ATCA

- 2x + 6x ATCA shelfs available

- 4 x ATCA carrier cards to be produced

#### Development of new MUX card for DAQ

- V6 FPGA are old, although still can be purchased

- K7 Ultrascale based on XCKU3P FPGA

- 16 x 12 Gbps ports, 16GB DDR4 Memory

- Few modules will be developed and produced for upgrade of DAQ MUX

=> 8 kEuro

=> N x 380 Euro

### DAQ FPGA Cards for PRM Run

#### DAQ Computing:

- 4 x PCAMRE

- 1 x AMBER type + 4 AMBER type servers

=> 10 kEuro

- Alternative 2 x CMPASS type available, more COMPASS type can be taken from COMPASS DAQ later

- 1 x disk storage + 1 being ordered + 3 disk storages are needed

=> 5+15 kEuro

■ 3 x HLT notes available + few more (?) to be purchased

=> N x 2.5 kEuro

# PRM Setup

| Detectors     | #Planes | #Channels | FEE               | #FEs | #L0 MUX | Channel<br>Noise, Hz | Data rate<br>Total / L0 MUX<br>GB/s | Data rate<br>after TPC<br>TRG GB/s |

|---------------|---------|-----------|-------------------|------|---------|----------------------|-------------------------------------|------------------------------------|

| BMS 1-6       | 6       | 512       | iFTDC             | 16   | 2       | 10                   | 0.07 / 0.04                         | 0.002                              |

| HODO          | 5       | 528       | iFTDC             | 18   | 2       | 200                  | 0.2 / 0.1                           | 0.005                              |

| SciFi Tracker | 16      | 3072/1536 | Special iFTDC     | 16   | 2       | 10 000               | 0.4 / 0.2                           | 0.01                               |

| SciFi         | 44      | 3148      | iFTDC             | 99   | 12      | 100                  | 2.0 / 0.2                           | 0.04                               |

| Pixel Silicon | 12      | 113 M     | ALPIDE+FMUX       | 36   | 4       | 0                    | 0.32 / 0.08                         | 0.01                               |

| GEM           | 24      | 36864     | VMM/TIGER         | ?    | 6-12    | 1000                 | 1.0 / 0.16                          | 0.03                               |

| MWPC          | 15      | 11520     | iFTDC             | 180  | 15      | 100                  | 1.5 / 0.1                           | 0.04                               |

| ECAL          | 1       | 256       | Upgraded<br>MSADC | 16   | 2       | ?                    | ?                                   | ?                                  |

| TPC           | 4       | 192       | SIS3316           | 12   | 1       | -                    | 0.18 / 0.18                         | 0.18                               |

| TOTAL         |         |           |                   |      | 46-52   |                      | 5.2                                 | 0.32                               |

### Components Availability for MUX and iFTDCs

- L0 MUX: 46-52 Cards needed, V6 version, components availability

- PCB production and assembly => 500 Euro x 50 = 25 kEuro

- V6 FPGA => 380 Euro x 50 = 20 kEuro, 2 weeks delivery

- Other components => 300 Euro x 50 = 15-20 kEuro

- Flash XCF128XFT64C, last order 07.2022, not available, consider to program FPGAs remotely at power up

- Jitter cleaner Si5338, no delivery time, to be investigated

- TCS clock recovery ADN2814, available

- DC/DC converters => some available, some delivery 35 weeks

- ☐ iFTDC : 320 cards needed

- PCB production and assembly => 150 Euro x 320 = 48 kEruo

- Artix XC7A50T FPGA => 100 Euro x 320 = 32 kEuro , delivery date 4.01.2024 (Digikey), 60 weeks (Mouser, AVNET)

- Other components => 150 Euro x 320 = 48 kEuro

- Flash S25FL256, available

- DC/DC, 35 weeks delivery time

## Module's Production Strategy

- Many components have long delivery time

- High volatility of IC market affects delivery time and price

- Proposed strategy :

- Define priority for module production: number of modules to be produced and amount of money available. I would suggest to start with L0 MUX.

- Order most critical components like FPGAs, DCDC converters

- Order all others components and schedule PCB production and assembly

## Summary of DAQ Investments

#### Computing

- Optional 4 x PCAMRE 10 kEuro

- 4 x Disk storage 20 kEuro

- HLT nodes N x 2.5 kEuro

- DAQ Hardware

- 4 x ATCA carrier cards

8 k Euro

- ☐ Detector cards

- 50 x L0 MUX

- PCB and assembly 25 kEuro

- V6 FPGA 20 kEuro

- Other components 20 kEuro

- 320 x IFTDC cards

- PCB and assembly 48 kEuro

- ARTIC FPGA 32 kEuro

- Other components 48 kEuro

# Thank you