#### PHENIX FVTX detector for AMBER

Kun Liu Los Alamos National Laboratory April 19, 2022

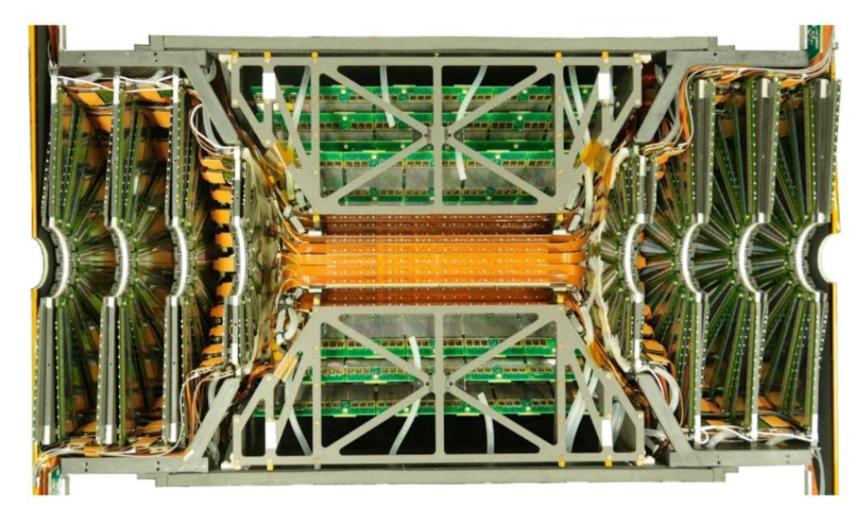

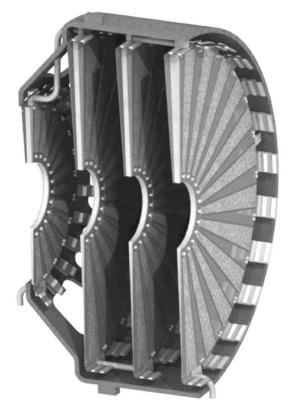

#### **FVTX** detector

- Silicon-strip vertex tracker designed and built by LANL for PHENIX

- Sensors, front-end ASICs, mechanical/cooling structure, PS available to take (for free)

- Detector was very lightly used

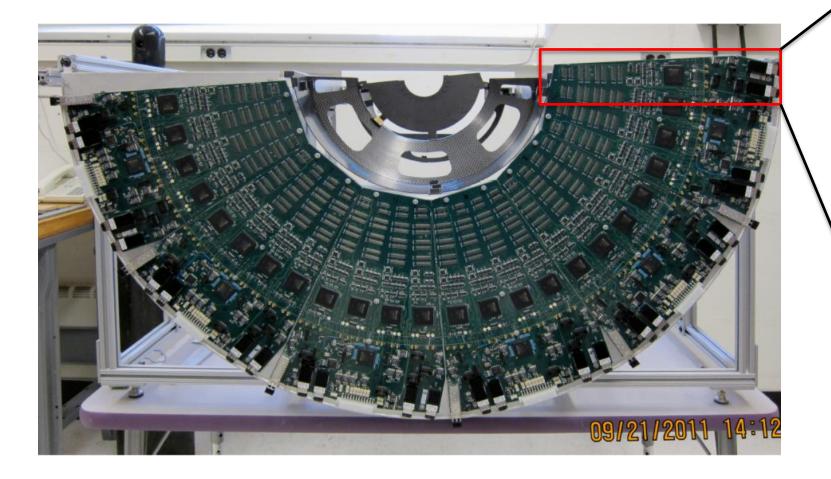

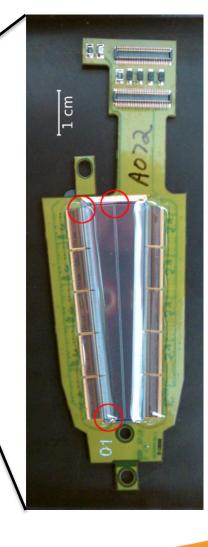

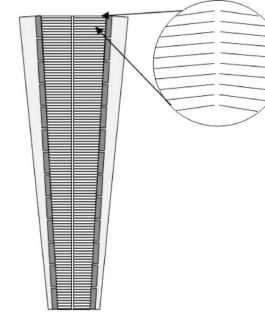

Silicon-strip sensors

# Sensor specs

| Silicon sensor thickness (µm)     | 320   |

|-----------------------------------|-------|

| Strip pitch (µm)                  | 75    |

| Number of strips per column       | 1664  |

| Inner radius of silicon (mm)      | 44    |

| Outer radius of silicon (mm)      | 168.8 |

| Strip length at inner radius (mm) | 3.4   |

| Strip length at outer radius (mm) | 11.5  |

| Pulse timing (ns)                 | 30    |

| Number of wedges per disk         | 48    |

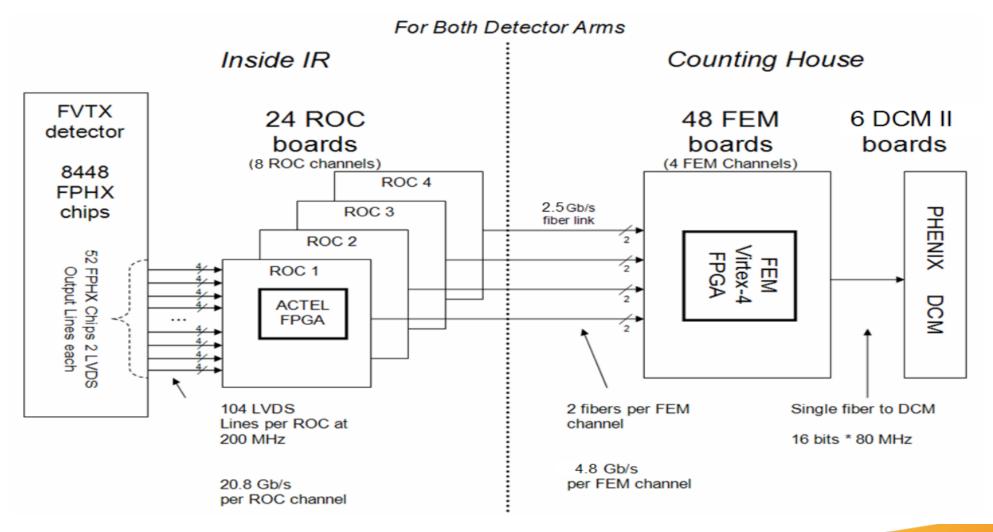

#### Readout chain

## Front-end ASIC (FPHX)

- Wire bonds to HDI for chip I/O, power, and ground 2.7 mm Bond pads to strips

- Directly bonded to the detector

- Programmable bias, threshold, rising/fall time, etc.

- Trigger-less data push structure, continuous 20bit (7-bit address, 7-bit time stamp, 3-bit ADC) data stream via LVDS output

- Process up to 4 hits within 4 clocks

### Readout Card (ROC)

- Receive data via LVDS from multiple FPHX

- Core function implemented on Radiation-hard FPGAs

- Combine and sync the data streams

- Send data to FEM in the counting house via optical fibers

- Handle slow control and calibration

### Front End Module (FEM)

- Receive data from ROCs over optical fiber

- Associate incoming data with beam clock counter and buffer the last 64 beam clocks

- Receive L1 trigger and send the data-of-interest to DAQ

- Distribute and receive slow control data

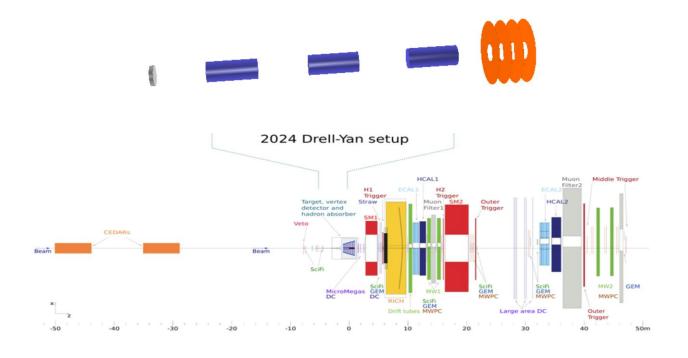

#### Adapting FVTX for AMBER's 2025 DY run

- Use 4 large disks and place them immediately after the last target

- Reuse the sensors, disk structure, cooling system, PS from FVTX

- Fabricate new ROCs based on the same board design, but change the FPGA firmware to directly interface with AMBER's DAQ data collector

# **Funding**

- DOE early career

- □\$2.5M (\$0.5M/year for 5 years)

- □Cover the full detector

- LANL LDRD

- □\$1M (\$0.33M/year for 3 years)

- □Cover ¼ of the detector a prototype

- □Will seek future funding to instrument the remaining detector

Expect the announcement in late June or early July

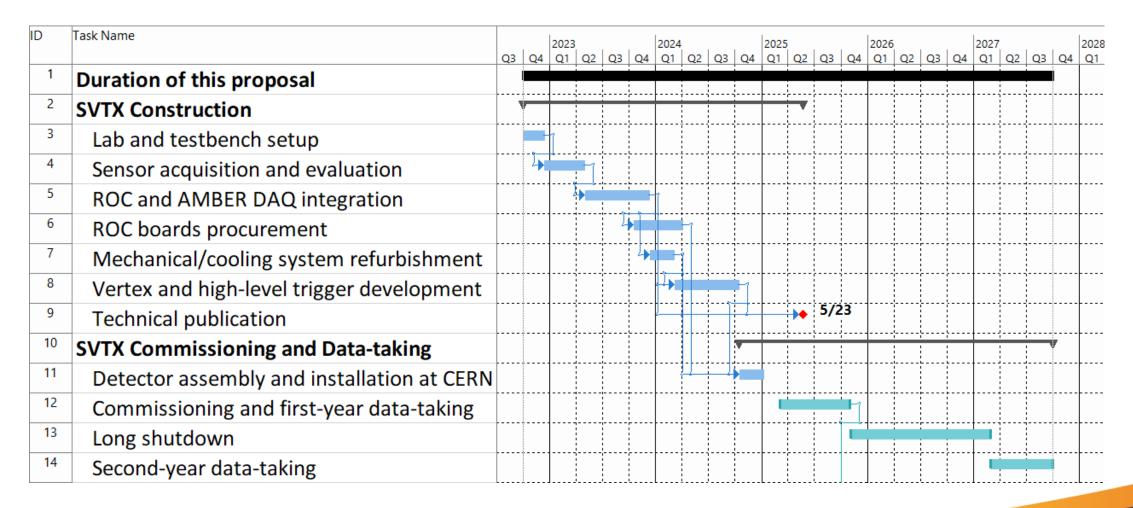

#### **Tentative schedule**