EP-DT Detector Technologies

# Silicon Detector R&D in DT

## **EP-DT Group Meeting**

09/12/2021

Florian Dachs (EP-DT-DD) Katharina Dort (EP-DT-TP) Anja Himmerlich (EP-DT-SSD)

### Katharina Dort [DT-TP]

# https://

gitlab.cern.ch/

corryvreckan/

# Pixel detector R&D in DT-TP

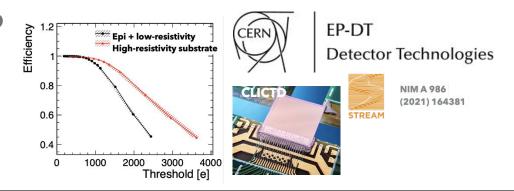

- Pixel detector R&D for future collider detectors, emphasis on Higgs factories

- High precision, low mass

- Pursued within EP R&D programme and various collaborative frameworks (AIDAinnova, CLICdp) and strong connection to EP-ESE + DESY + UniGE

- Simulation-based sensor optimisation and experimental verification with technology demonstrators

- Team members: Justus Braach, Eric Buschmann, Dominik Dannheim, Katharina Dort, Peter Švihra

Built + maintain high-rate telescope at SPS

Software tools for the (HEP) community

**EP-DT**

CERN

- Corryvreckan test-beam reconstruction and analysis

- Allpix Squared Monte Carlo simulation framework for end-to-end simulation of silicon sensors

https:// gitlab.cern.ch/ allpix-squared/ allpix-squared

EP R&D

**Detector Technologies**

AIDA

2021 JINST 16 P03008

# Pixel detector R&D in DT-TP

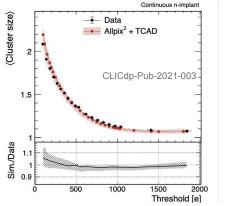

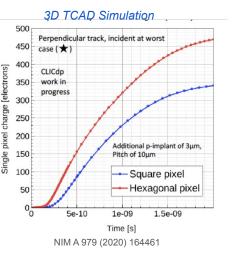

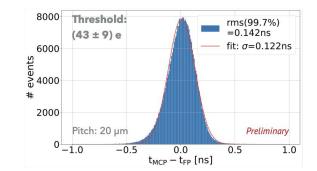

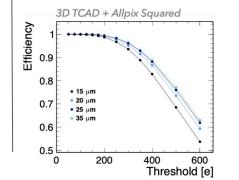

**Sensor Optimisation**

- Combined electrostatic

3D TCAD + transient MC simulation for

- Precise sensor modelling

- High simulation rates

NIM A 964 (2020) 163784

- Design optimisation for fast sensor timing

- Hexagonal pixel layout for improved performance

Monolithic CMOS sensor with sub-nanosecond timing

Modified 180 nm CMOS imaging process

*Pixel pitch: 8.66 μm - 20 μm*

• Time resolution < 150 ps

Katharina Dort [DT-TP]

EP-DT Detector Technologies

Hexagonal pixel layout

CERN

# Pixel detector R&D in DT-TP

Advances materials for monolithic sensors

- Larger active sensor volume

- Improved detector performance: efficiency, spatial + time resolution https://agenda.linearcollider.org/event/9211/contributions/49443/

## Monolithic sensors in 65nm CMOS

- Process optimisation using simulations

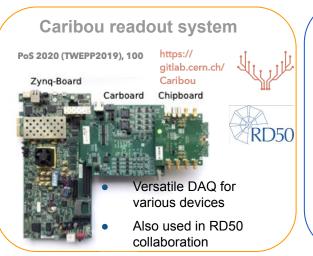

- Characterisation of digital test-chip (DPTS) with Caribou DAQ

- Detailed test-beam studies spring next year

- Timing performance + comparison to simulation

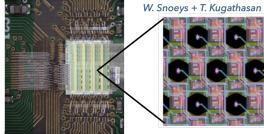

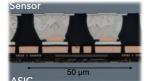

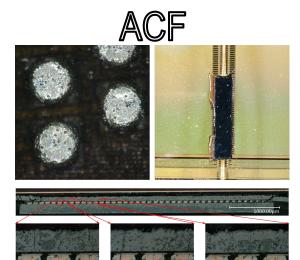

### Novel fine-pitch hybridisation

- Development + characterisation of small-pitch (25 μm) bump-bonding process

CERN-THESIS-2020-338

- Proof-of-principle for alternative in-house bonding technique using Anisotropic Conductive Film (ACF)

- Also used for module integration (see part from Florian) Conductive ACF ball

### CLICpix2 hybrid assembly (IZM)

https://agenda.linearcoll ider.org/event/9211/con

tributions/49469/attach

ments/37464/58685/IL

CX MVicente ACF.pdf

Flip-chip bonder at UniGE

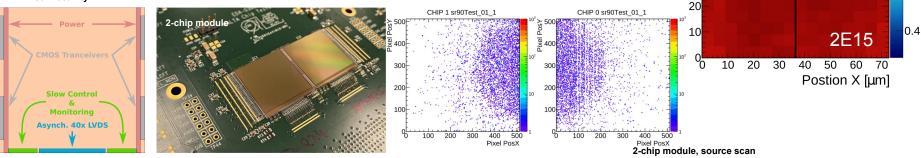

## CMOS pixel detector R&D and module development (CERN)

Florian Dachs\*, Abhishek Sharma, Julian Weick, Peter Svihra, Mateus Vicente, Milou van Rijnbach, Dominik Dannheim, Petra Riedler

EP-DT & WP 1.3 & EP-ADE in close collaboration with the QARTIab and Bondlab at the DSF, working closely CERN services and with institutes (e.g. Univ. of Geneva)

- Studies performed on the monolithic CMOS pixel chip "MALTA" designed for high radiation hardness and produced in the 180 nm TowerJazz process

- 2x2 cm<sup>2</sup> overall size, 36.4 µm symmetric pixel pitch

- fast detection and readout compatible with 40MHz event rate

- redundant CMOS transceivers for chip-to-chip data and allows direct chip-to-chip powering

- Focus on the study of various interconnection techniques and chip-to-chip transmission of power and data to build large scale, low-mass modules

- **Optimize base wafer material**, chips produced on different epi wafers as well as on high res CZ wafers

- Performance tests and qualification on chip and module level

### MALTA connectivity

**EP-DT**

Efficiency: 95.1±0.2 % @ 240 e MALTA, Cz silicon, NGAP, 2E15 1MeV n\_/cm<sup>2</sup>, SUB @ -55V, sector 2

ATLAS

Digita

[mm]

60

50

40

30

Position Y

Collection

electrode

MALTA pixel cell

**Detector Technologies**

EP

R&D

Efficiency [%/100]

0.8

0.6

## CMOS pixel detector R&D and module development

**Detector Technologies**

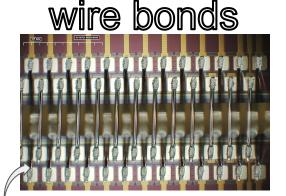

Study interconnection techniques and establish assembly procedures

Al wedge wire bonding as baseline to study chip performance

**Functioning 2-chip** and 4-chip modules assembled and currently undergoing testing

- ACF connections studies on chip interconnection with a Silicon bridge

- multiple glues tested

- multiple mech. supports developed

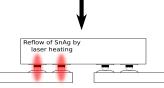

# laser reflow

**EP-DT**

Laser reflow technique where Sn tipped Cu studs are bonded to Ni/Au plated pads

ENIG plating done by DT **Micro-Pattern Technologies** lab (Rui de Oliveira)

Technique shows high quality bonds on broken assemblies

## CMOS pixel detector R&D and module development (

EP-DT Detector Technologies

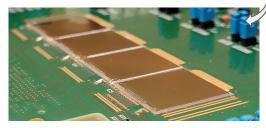

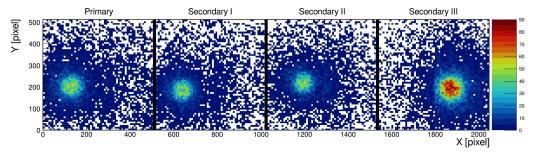

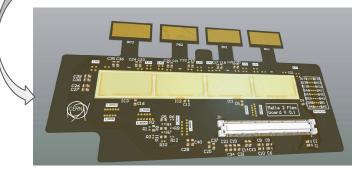

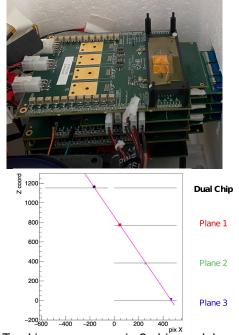

Study chip-to-chip power and data transfer - performance tests on 2-chip and 4-chip modules

Source scan on continuously read out **4-chip module** (total size 8x2 cm<sup>2</sup>) **Readout full module via one chip only:**

Studies on current 4-chip board enable development towards light-weight flex-based 4-chip module

- Chip-2-flex mounting

- Designed for direct pad-to-pad bonding with various interconnection techniques!

- Design completed

### 2-chip board in cosmic telescope:

- Tracking across gap in 2-chip modules and efficiency studies ongoing!

- Planning for test-beam measurements in 2022

## **Radiation Hard Silicon Detectors**

EP-DT Detector Technologies

## Work performed by the EP-DT Solid State Detectors (SSD) team

Frameworks:

SSD: 1.5 Staff, 2 Fellows, 3 PhD students & visiting scientists + collaborators SSD labs in bldgs. 28 and 186

## RD50 – Radiation hard semiconductor devices for very high luminosity colliders

- $\Rightarrow$  66 Institutes with 420 members, collaboration formed in 2001

- ⇒ CERN SSD acting as host lab, providing co-spokesperson, the budget holder and admin support (Veronique Wedlake)

- ⇒ CERN SSD scientific contributions in 4 main areas

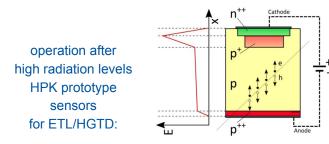

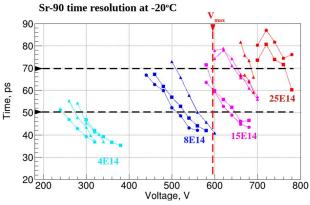

Timing detectors for harsh radiation environments

in particular: LGAD – Low Gain Avalanche Diodes

Defect formation in defect engineered semiconductors

in particular: acceptor removal

Modelling of radiation damage on microscopic and device level

in particular: NIEL – Non Ionizing Energy Loss

Characterization tools for irradiated silicon devices

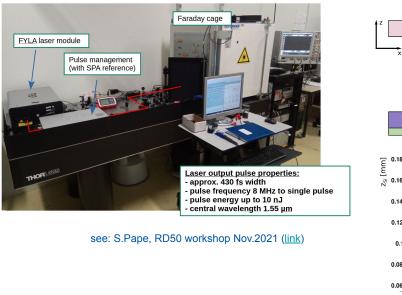

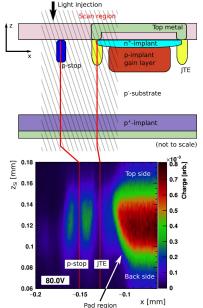

in particular: TPA-TCT - Two Photon Absorption - Transient Current Technique

## **Radiation Hard Silicon Detectors**

EP-DT Detector Technologies

### Example on Sensor Development:

### LGAD – Low Gain Avalanche Diodes

### Example on Characterization tools:

TPA-TCT: Two Photon Absorption – Transient Current Technique

⇒ Laser induced charge generation in silicon devices used to

evaluate detector properties (3D resolution: 1.5 um x 1.5 um x 15 um)

⇒ Hardware financed by a CERN Technology Transfer grant

see: E.Curras, EP-RD seminar 06.12.21 (link)

## Radiation Hard Silicon Detectors

**EP-DT Detector Technologies**

BO

#### Radiation induced degradation of the LGAD gain: **Acceptor Removal Effect** $\Rightarrow$ Deactivation of Boron as shallow dopant neutron irradiated W7 samples (<sup>90</sup>Sr setup) et al. 2015 JINST 10 P07006 80000 • W7-C9 70000 e Most typical radiation induced reaction: ▲ W7-I6 • W7-110 60000 charge 50000 Conduction Band Conduction Band E $Si_i + B_s \rightarrow B_i$ 40000 30000 p++ **Radiation Damage** 20000 B acceptor 2.1015 cm-2 1000 $B_i + O_i \rightarrow B_i O_i$ Moll, PoS(Vertex 2019) 027 Ev Ev Valence Band alence Band 1000 1500 bias voltage [V]

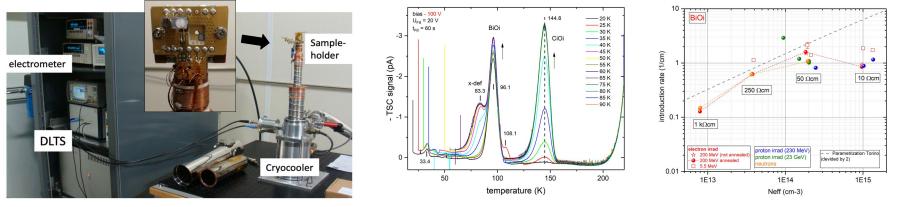

Defect spectroscopy: Deep-level-transient spectroscopy (DLTS) & Thermally stimulated current technique (TSC)

RD50 workshop 202

6

đ

A. Himmerlich