## ULTRA-LOW NOISE SPADS IN 350 NM CMOS TECHNOLOGY FOR CHERENKOV RADIATION DETECTION IN PARTICLE AND ASTROPHYSICS

S. Grosse, <u>S. Dreiner</u>, J. Hauser, D. Weiler, M. Ligges, P. vom Stein, S. Weyers

Fraunhofer Institute for Microelectronic Circuits and Systems (IMS), Duisburg, Germany

# 11th International Workshop on Ring Imaging Cherenkov Detectors (RICH2022)

12.–16. Sept. 2022

University of Edinburgh

# OUTLINE

- Introduction

- Pros and Cons: SiPMs for RICH detectors

- CSPAD Technology at Fraunhofer IMS

- 3D Integration (Back-SPADs)

- Summary

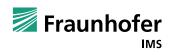

#### Introduction Fraunhofer IMS

- Fraunhofer Institute for Microelectronic Circuits and Systems

- Located in Duisburg, NRW, Germany

- Founded 1984

- > 250 employees

- Infrastructure:

- In-house 0.35 µm CMOS cleanroom with spezialized processes

- Microsystem Lab for post-processing

- Test and assembly capabilities

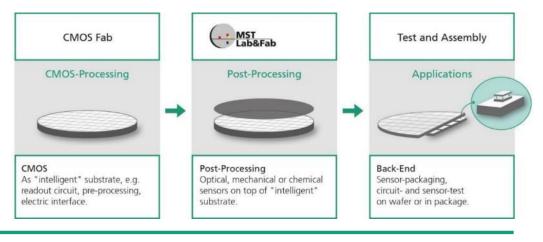

#### Introduction SPAD Operating Principle

- Single-Photon-Avalanche-Diode (SPAD) is an avalanche photo diode which is operated with a voltage higher than the breakdown voltage (= Geiger-Mode)

- Single photons can be detected

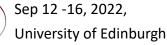

- -> Photon Detection efficiency (PDE) = Avalanche Probability (AP) \* Quantum Efficiency (QE)

- Fast operation with good time resolution (~100ps FWHM)

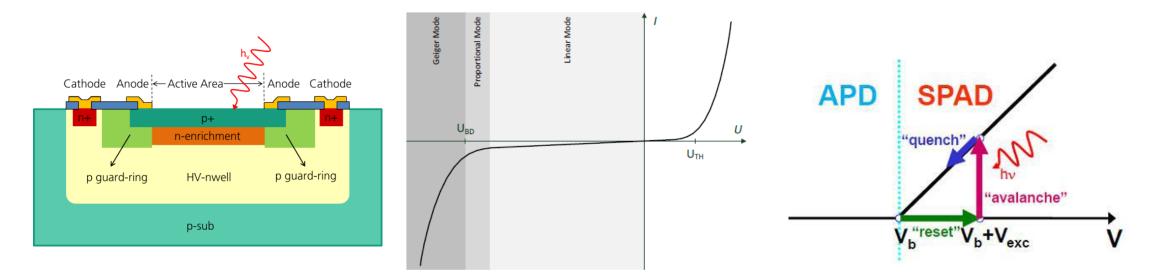

#### Introduction Passive Quenching

- simple quenching with resistor, used in SiPM (array of conncected passive quenched SPADs)

- high dead time during Reset due to recharge of diode capacitance with the resistance  $R_B$

#### **SIPMs for RICH detectors**

#### PROS:

- high photodetection efficiency (PDE)

- operation in the magnetic field

- Iow supply voltage

- fast response

- flexible granularity

- compact

#### CONS:

- high dark count rate {~100kHz / mm<sup>2</sup> at RT)

- Radiation damage

- Cooling

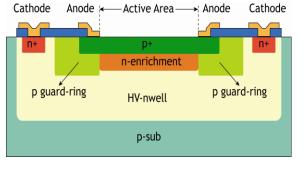

### **CSPAD (CMOS integrated SPAD)**

#### Technology

- Avalanche Photodiode (APD) operated in Geiger mode

- Smart frontside illuminated pixels integrated into standard 0.35µm CMOS process (dual gate oxide, 4 metal layers)

#### **Unique Selling Points**

- Lowest Dark-Count-Rate

- High uniformity

- Picosecond time resolution

- High sensitivity in blue and UV

#### Applications

LIDAR, Raman spectroscopy, low light imaging, FLIM

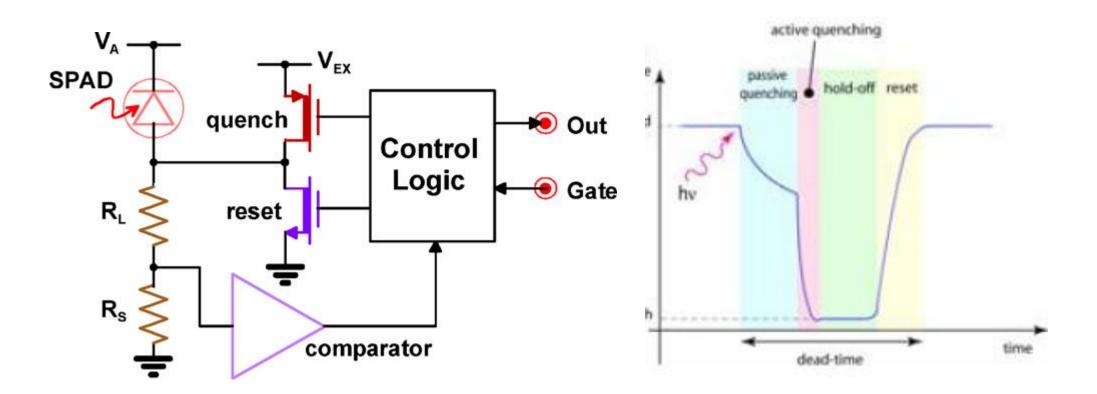

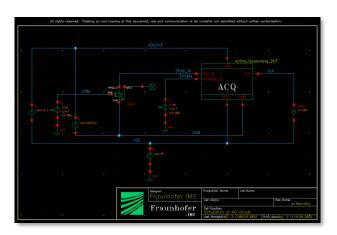

#### CSPAD Active Quenching

F. Zappa et al., Sensors and Actuators A: Physical Volume 153, Issue 2, 3 August 2009, Pages 197-204

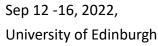

## CSPAD Sources for dark counts

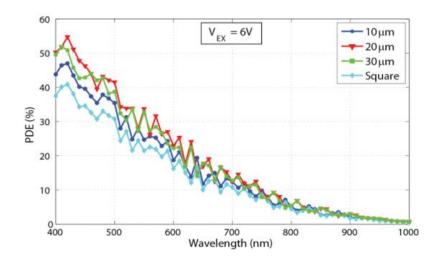

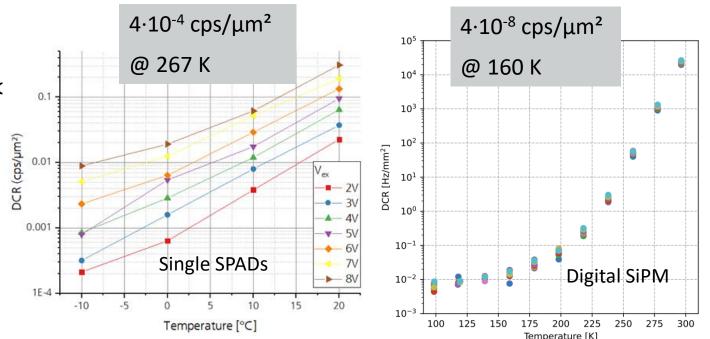

#### CSPAD Dark Count Rate

World's lowest Dark Count Rate (DCR) for CMOS integrated SPADs:

- Band2Band tunneling was reduced in order to lower the DCR at low temperatures (2. Generation)

- Down to 0.04 cps/mm<sup>2</sup> by cooling to 160 K or 400 cps/mm<sup>2</sup> at 267 K

- "Hot SPADs" could be deactivated

- DCR at higher temperature is limited by diffusion current from the non-depleted area, fully depleted BSI or an n-buried layer can reduce this current

Fischer, P., SPAD Array Chips with Integrated Readout with High Fill Factor and Low Dark Count Rate at Low Temperatures, 15th Pisa Meeting on Advanced Detectors (May 2022)

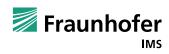

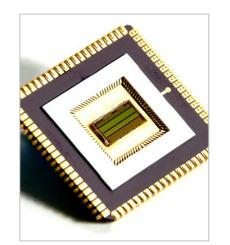

#### **CSPAD Development** Linear sensor for spectroscopy applications

#### **Specifications**

- Pixel pitch: 20 μm (along sensor)

- SPAD area: 14 μm × 76 μm

- Pixel count: 2 × 128

- Fill factor: 60 %

- Measurement period: 2.95 μs

- Typ. Gating width: 12.5 ns

- Crosstalk: 13 %

+ several line sensors for LIDAR applications

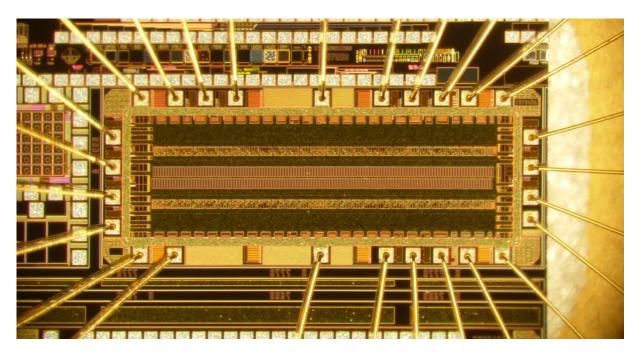

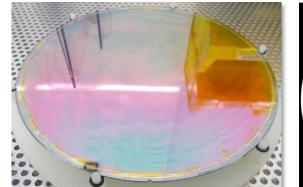

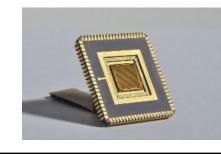

#### **CSPAD Development Analog Silicon Photo Multiplier**

Photograph of SiPM designed and fabricated at IMS

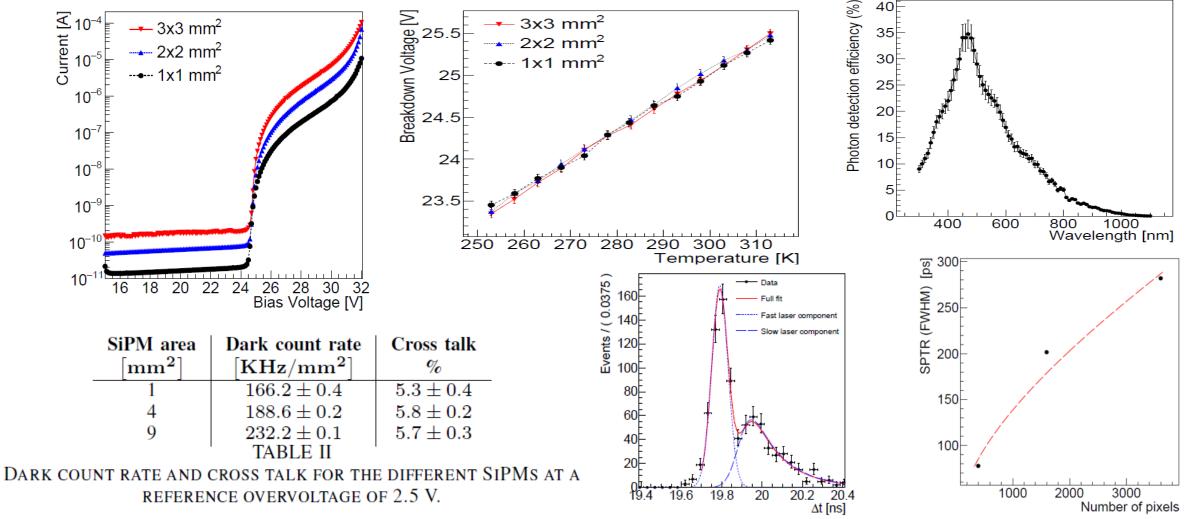

#### SiPM specifications

- Pixel pitch: 50 μm

- Array size: 1 mm × 1 mm

- Fill factor: 68 %

- Dead time: 80 ns

- Breakdown voltage: 26 V

- CMOS integration enables

- Amplifiers

- $\Rightarrow$  increase output signal amplitude

- Impedance converters ⇒ increase timing resolution

- deactivation of hot pixels

- in-pixel memory

#### External CSPAD Use Analog Silicon Photo Multiplier

X. Liang et al., "Silicon photomultipliers with area up to 9 mm<sup>2</sup> in a 0.35 nm CMOS process", IEEE J. ELEC. DEV. SOC. 2019

#### **External CSPAD Use**

Ursprung

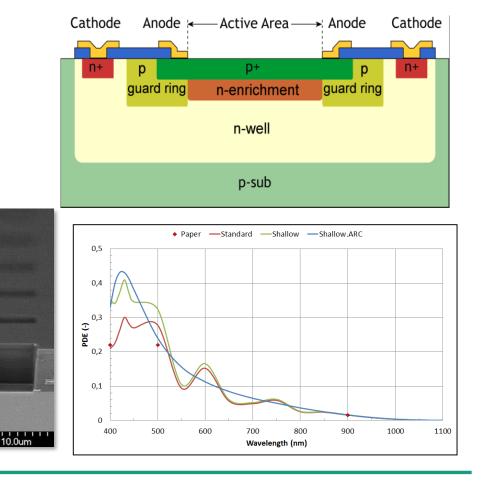

## **Additional Developments Analog Silicon Photo Multiplier**

Development DOSE( Deep Optical Stack Etching) + ARC (Anti Reflective Coating)

Variante 2

For PET SPADs shallow p+ doping (PDE Improvement)

10

Variante 1

Air UVNIT

iO.-

10

S-4700 7.0kV 8.1mm x3.00k YAGBSE

**Entrance windows**

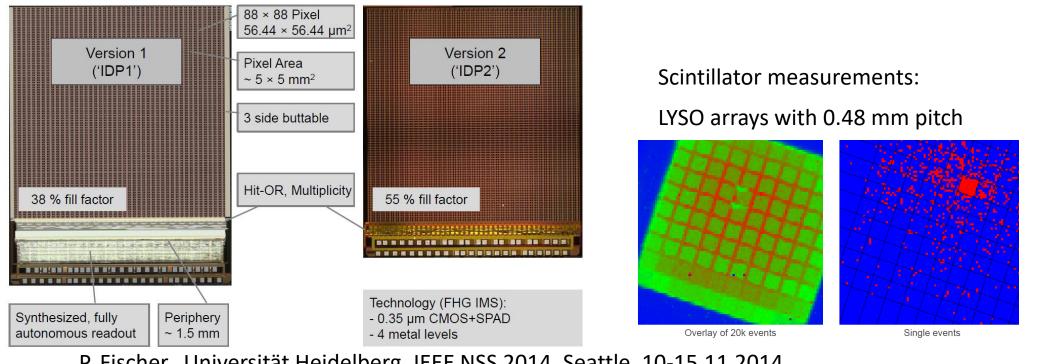

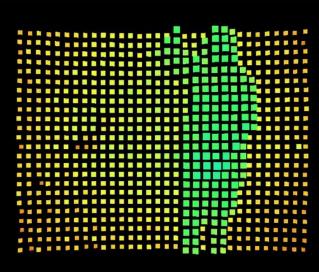

#### **External CSPAD Use Digital Silicon Photo Multiplier**

88\*88 SPAD array with full 2D readout (dSiPM)

Goal is to use full 2D image information to study scintillators, do imaging (fluoresence, night vision, astronomy), do physics (Compton scattering ..)

P. Fischer, Universität Heidelberg, IEEE NSS 2014, Seattle, 10-15.11.2014

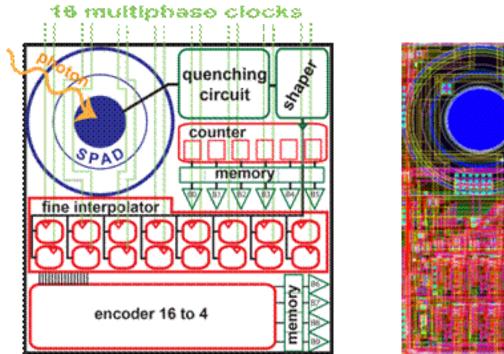

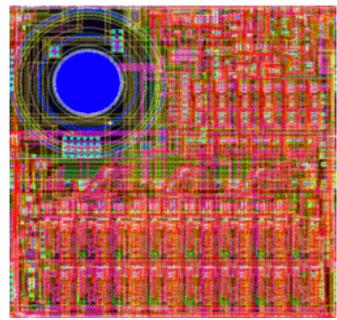

## **3D Integration (Back-SPADs) Motivation: MiSPiA smart-pixel for direct TOF**

- Block diagram (left) and Layout (right) of the SPAD based smart pixel, showing the main components

- The pitch is 150µm; the SPAD has 30µm diameter (Pixel fill factor 3.14%)

University of Edinburgh

MiSPIA (everyphotoncounts.com)

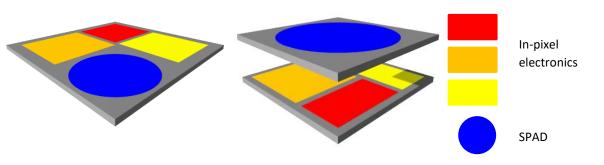

## **3D Integration (Back-SPADs)**

## **Concept: Wafer-To-Wafer Bonding**

- Optical Sensor with maximum fill-factor, optimized substrate-doping, ...

- Huge read-out circuitry needed, dense logic  $\rightarrow$  2-wafer-solution (also foundry CMOS or Sensor wafer possible)

- Straight, symmetric wiring necessary between pixel and read-out  $\rightarrow$  wafer-stacking

- Fine pitch interconnect between wafers required  $\rightarrow$  "µVias" with ALD

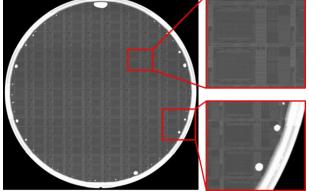

#### **3D Integration (Back-SPADs) Integration technology**

- Direct 8" wafer bonding

- Layout and process optimization for planarity

- Multi-stage chemical mechanical planarization (CMP)

- Alignment analysis (accuracy < 1 μm)</p>

- Bonding interface analysis by scanning acoustic microscopy (SAM)

- Combination of technology nodes

- High performance electronics with ultra-low noise SPADs

- Read-out close to sensor area

Wafer stack

SAM image

## 3D Integration (Back-SPADs) ALD for μVias

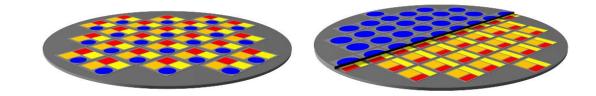

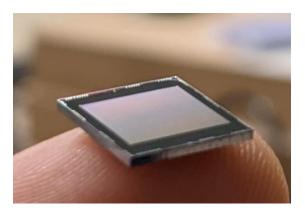

## 3D Integration (Back-SPADs) CSPAD LIDAR Sensors

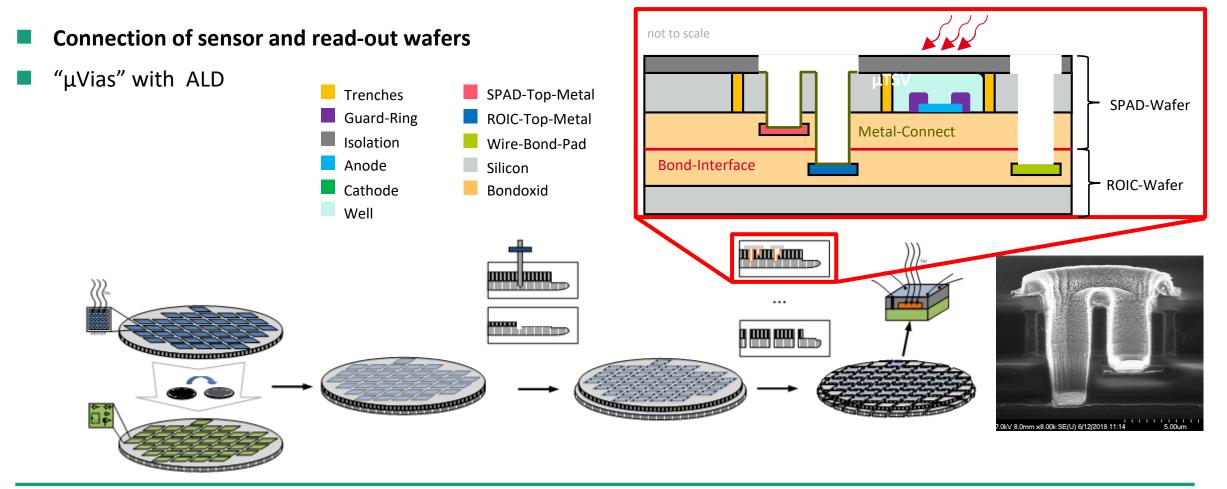

#### Connection of sensor and read-out wafers

- Wafer-2-wafer solution for backside-illuminated LIDAR-Sensors

- Several LIDAR demonstrators designed and fabricated

- W2W interconnect "μVia" with ALD

- Array with  $\geq$  10k pixels (x4 SPADs; x2 Vias) in fab

- Photon timing and counting mode

- Variable coincidence settings (Each pixels with 4 SPADs)

- In-pixel time-to-digital converters (TDC) and built-in TDC monitoring

- Adaptive background light suppression (Reduced sunlight noise)

- Flexible Resolution (Region of Interest)

**CSPAD**

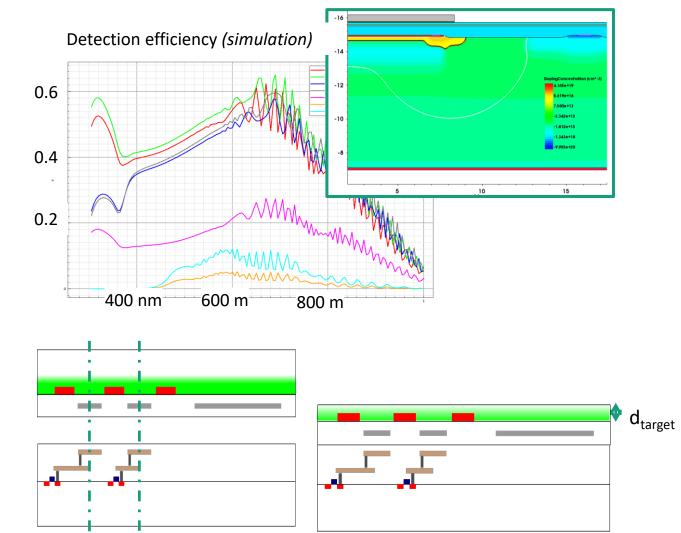

## 3D Integration (Back-SPADs) EPI and Doping Profile

Change from SOI -> EPI Wafers (reduced DCR)

- Optimized doping profile and silicon thickness for (high avalanche efficiency, fully depleted, PDE> 40% for 300-800 nm)

- Anti reflective coating (now optimized for 905nm LIDAR applications, but other wavelengths possible)

Challenges:

- Etch-Stop -> doping selective etching necessary -> HNA

- CMP-planarization

- Backside passivation for fully depleted diodes

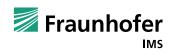

# **3D Integration (Back-SPADs)**

## Low Temperature PureB deposition

- Deposition of a few nm thick boron film

- similar to boron delta doping

- very good passivation

- no degradation due to EUV, DUV, UV radiation

- Full depletion of the film is possible

- CMOS Backend compatible

- P+ doping above BOX of the SOI wafer is not necessary

- Passivation for EPI wafer (Back SPADS) could be solved

Robust UV/VUV/EUV PureB Photodiode Detector Technology With High CMOS Compatibility

Lis K. Nanver, Member, IEEE, Lin Qi, Vahid Mohammadi, K. R. M. Mok, Wiebe B. de Boer, Negin Golshani, Amir Sammak, Thomas L. M. Scholtes, Alexander Gottwald, Udo Kroth, and Frank Scholze

#### **Circuit Design**

- Long term experience in circuit design for image sensors (>10 years SPADs)

- Advanced simulation tools for performance improvement

- High performance quenching circuits

- High precision timing electronics (TDC)

- Goal 20 ps timing resolution

- Cadence tool set up

#### Summary

- Introduction to the in CMOS integrated SPAD technology CSPAD

- Presenting the DCR results and limits

- Next step for digital SiPMs -> 3D Integration with in-pixel (Micro Cell) electronics

- **3**D Integration developments at Fraunhofer IMS

- Dr. Stefan Dreiner

- Core Competence Technology

- Semiconductor Sensor Devices

- Tel. +49 203-3783-2993

- stefan.dreiner@ims.fraunhofer.de

Follow us: **Original** More information about 3D-Sensing at https://www.ims.fraunhofer.de/en/

Meet our experts at:

»Vision 2022« Oct. 04.-06., Hall 10- booth 10E76

# Thank you for your attention