## Qualification of DIRICH readout chain

P. Subramani<sup>1</sup>, J. Förtsch<sup>1</sup>, J. Michel<sup>3</sup>, C. Pauly<sup>1</sup>, D. Pfeifer<sup>1</sup>, M. Traxler<sup>2</sup>, K.-H. Kampert<sup>1</sup> for the CBM RICH- and TRB collaboration contact: subramani@uni-wuppertal.de

<sup>1</sup>Bergische Universität Wuppertal, Germany, <sup>2</sup>GSI Helmholtzzentrum für Schwerionenforschung, Germany, <sup>3</sup>Goethe Universität Frankfurt, Germany

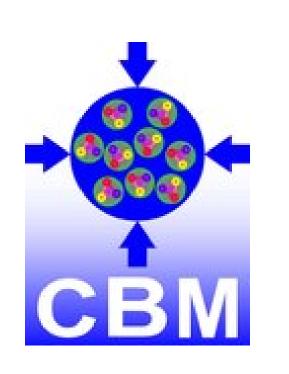

## **DIRICH readout chain**

- Low power modular FPGA based readout chain.

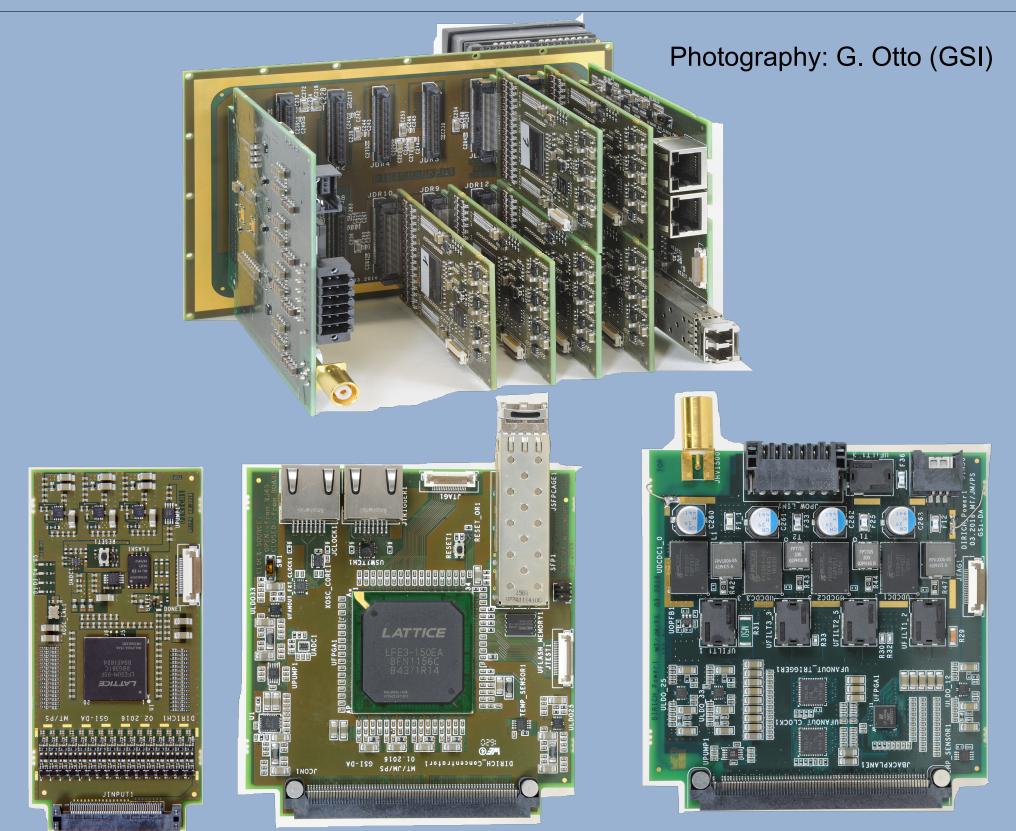

- Six 64ch HAMAMATSU H12700 MAPMTs and readout electronics connected by backplane which provides light and gas tight seal.

### **DIRICH front-end module (FEB) :**

- Reads out half MAPMT (32 + 1 channels). • Each channel features own inverter amplifier, FPGA based discriminator and TDC (Lattice

- ECP5).

- Leading and trailing edge measurements  $\rightarrow$ Time over Threshold.

- Leading edge timing precision ~ 20 ps RMS.

## Measurement set-up

**Power module**

**Combiner module :**

Combines data from 12 DIRICH-FEBs to 2.4 Gbit link to common readout interface. Distributes clock input to individual FEBs.

#### **Power module :**

• Distributes high voltage for PMTs (~ -1000V). • Distributes low voltages to read out modules via onboard DCDC convertors  $(32V \rightarrow \{1.1, 1.2, 2.5, 3.3V\}).$

- board (TRB3)). • 2 light sources : Picosecond

- pulse Laser (Ring), Pulsed LED (homogeneous).

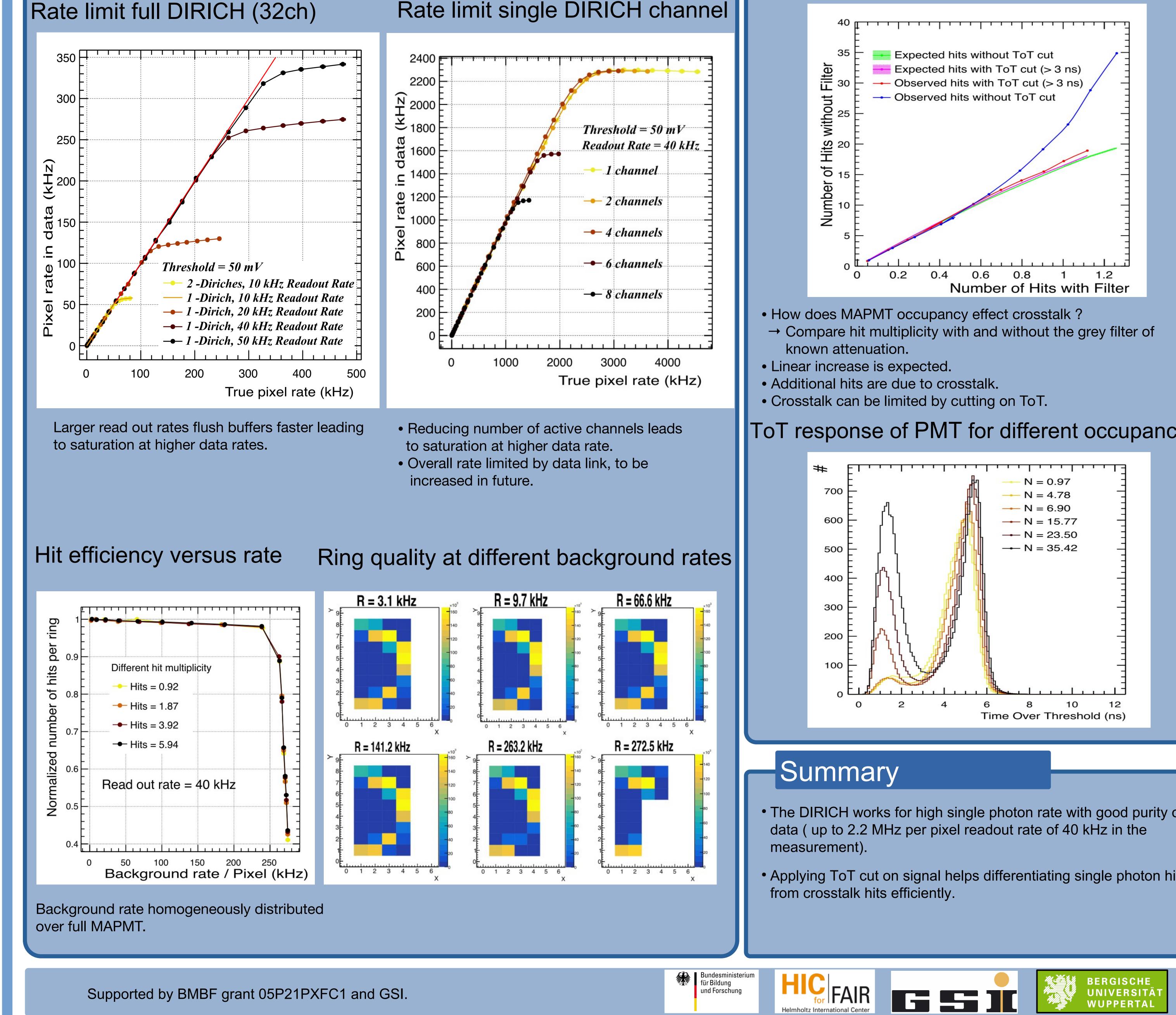

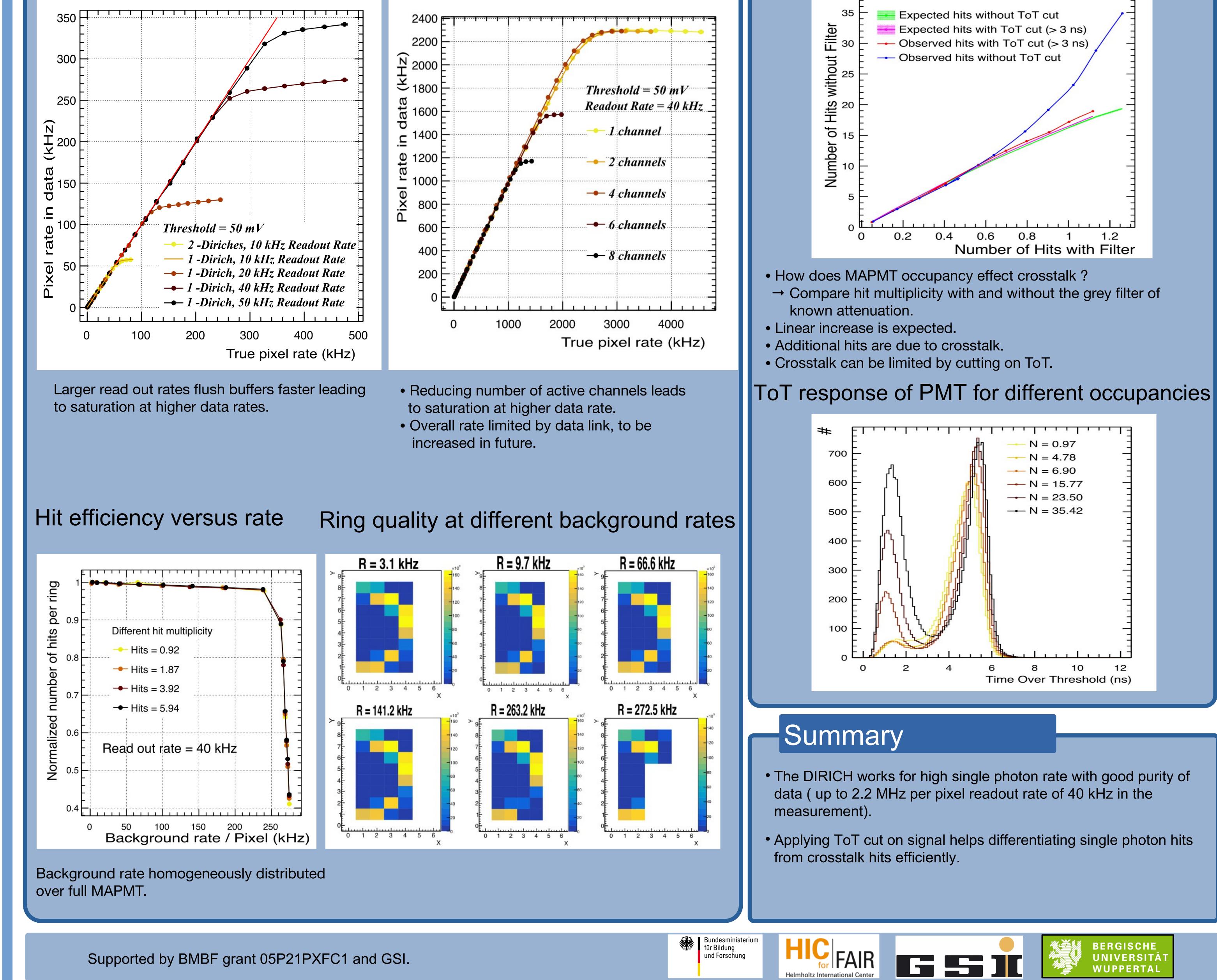

# Rate capability measurement

Combiner

DIRICH

Rate limit single DIRICH channel

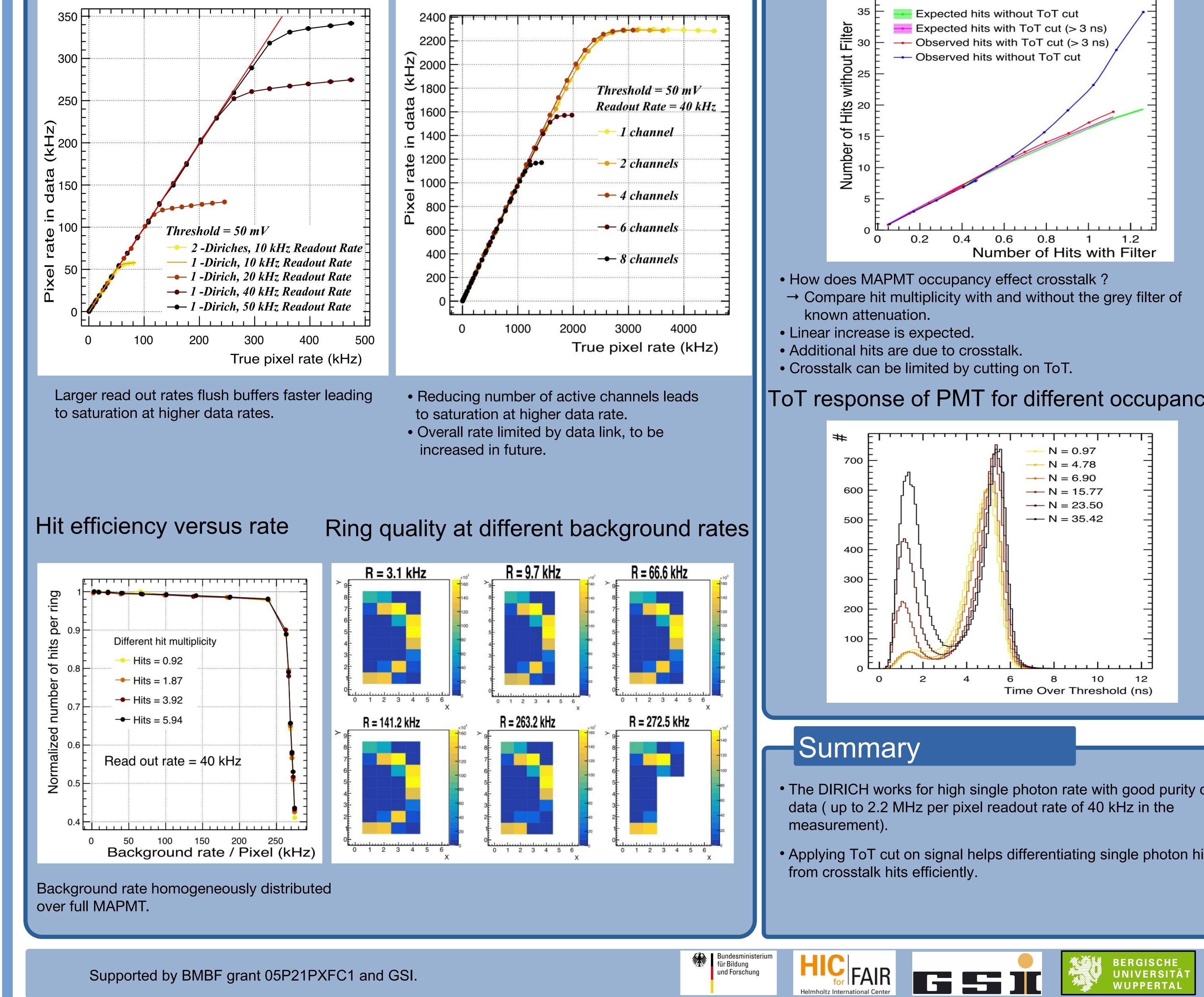

## Crosstalk suppression using ToT