Poster 226:-<u>G. Chiarello<sup>1,2\*</sup></u>, A. Corvaglia<sup>2</sup>, F. Cuna<sup>2,4</sup>,B.D'Anzi<sup>3,5</sup>, N. De Filippis<sup>3,6</sup>, W. Elmetenawee<sup>3</sup>, E. Gorini<sup>2,4</sup>, F. Grancagnolo<sup>2</sup>, M. Greco<sup>2,4</sup>, A. Miccoli<sup>2</sup>, M. Panareo<sup>2,4</sup>, M. Primavera<sup>2</sup>, G. F. Tassielli<sup>3,5</sup>, A. Ventura<sup>2,4.</sup>

ACAT2022 – 21st International Workshop on Advanced Computing and Analysis Techniques in Physics Research (23 – 28 Oct 2022), Bari, Italy

#### Abstract

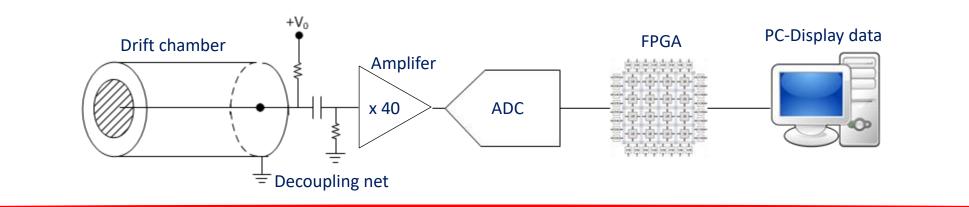

Ultra-low mass and high granularity Drift Chambers fulfill the requirements for tracking systems of modern High Energy Physics experiments at the future high luminosity facilities (FCC-ee or CEPC). We present how, in Helium based gas mixtures, by measuring the arrival times of each individual ionization cluster and by using proper statistical tools, it is possible to perform a bias free estimate of the impact parameter and precise particle identification. Typically, in a helium-based drift chamber, consecutive ionization clusters are separated in time by a few ns, at small impact parameters up to a few tens of ns, at large impact parameters. For an efficient application of the cluster timing technique, consisting in isolating pulses due to different ionization cluster, it is, therefore, necessary to have read-out interfaces capable of processing high speed signals. We present a full front-end chain, able to treat the low amplitude sense wire signals (a  $\sim$ few mV), converted from analog to digital with the use of high bandwidth ( $\sim$ 1 GHz) FADCs and an electronic board including an FPGA for a real-time processing of the signals.

## **Cluster counting/timing operation**

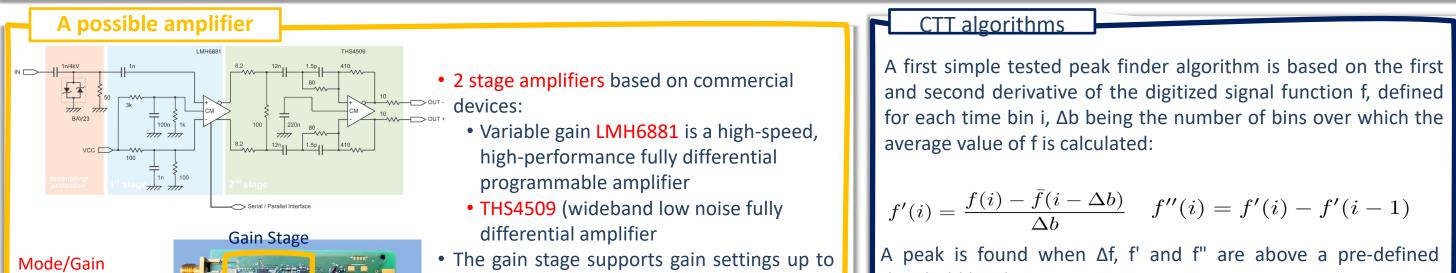

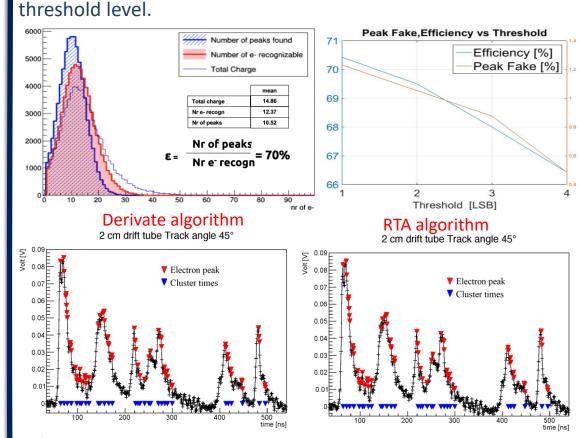

The Cluster Timing Technique (CTT), which consists in measuring the arrival times on the sense wires of each individual ionization electron, overcomes a substantial bias in the impact parameter estimate (normally in drift chambers, only the time of the first cluster is used to estimate the track impact parameter) and offers the possibility of greatly improving the particle identification capabilities (Cluster Counting Technique, CCT). This technique uses statistical tools to reduce the biased estimate, by exploiting the information of all clusters detected with a peak finding algorithm. An on-line algorithm (in VHDL/Verilog languages) identifies, in the digitized signals after a pre-amplification, in real time, the peaks due to the single ionization electrons, records their times and amplitudes and sends the data stored to an external device when a specific trigger signals occurs.

programming. with dip switches it is possible to select the gain of the first stage.

about 50 dB with small accurate 0.25dB gain steps, although the VGA can also be parallel programmed.

• Bandwidth about 1GHz

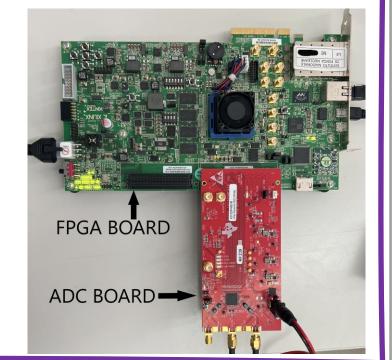

# **FPGA and ADC**

A fast read-out CTT algorithm has been developed with success as VHDL code implemented on a Virtex 6 FPGA (maximum input/output clock switching frequency of 710 MHz). The hardware setup includes also a 12-bit monolithic pipeline sampling ADC at conversion rates up to 2.0 GSPS. To improve the performance of the algorithms used (and try others with better performance) it was decided to focus on more performing hardware. The new hardware, for this reason, uses an FPGA with better performances (in terms of time and power) and allows us to reduce the processing time and to manage multichannel ADCs:

### • KIT EVAL ULTRASCALE FPGA KCU105

- UltraScale<sup>™</sup> XCKU040-2FFVA1156E

- Transceiver 20 GTH

- 2 moduli SFP+ da 10Gbps

### ADC ADC32RF45

- 14-Bit, Dual-Channel, 3.0-GSPS ADC

- Noise Floor: –155 dBFS/Hz

- RF Input Supports Up to 4.0 GHz

- Aperture Jitter: 90 fS

- Channel Isolation: 95 dB at  $f_{IN}$  = 1.8 GHz

A further algorithm that is being implemented on FPGAs is the Running Template Algorithm (RTA). It is based on a bin-by-bin difference of the waveform with a normalized search template.

### Summary

The derivate algorithm has been implemented and tested on FPGAs, while the RTA algorithm is in the testing phase with PC simulations and testbench. From these tests, it results that there is a peak detection efficiency of 72%, with 1.2% fake peak rate, for the derivative algorithm, while 70% for the RTA algorithm, with 1% of fake peak rate.

<sup>1</sup>Istituto Nazionale di Fisica Nucleare, Pisa, Italy <sup>2</sup>Istituto Nazionale di Fisica Nucleare, Lecce, Italy <sup>3</sup>Istituto Nazionale di Fisica Nucleare, Bari, Italy

<sup>4</sup>Università del Salento, Italy <sup>5</sup>Università degli Studi di Bari »Aldo Moro», Italy <sup>6</sup>Politecnico di Bari, Italy

for information and details contact: gianluigi.chiarello@infn.it