# Timing reference correction for the CMS improved Resistive Plate Chambers (iRPC)

Jianing Song\*, Zhen-an Liu, Jingzhou zhao, Qingfeng Hou, Weizhuo Diao, Wenxuan Gong On behalf of the CMS Muon Group

23rd Virtual IEEE Real Time Conference (RT2022) 1 Aug 2022

- Introduction

- iRPC timing reference issue

- Timing reference correction

- Test results

- Summary

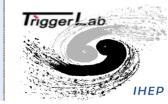

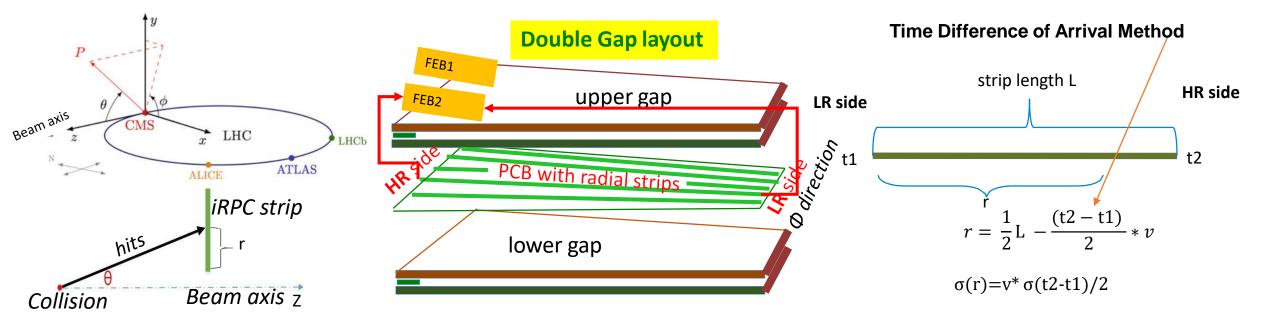

### **iRPC** introduction

Extend the RPC coverage up to  $|\eta| = 2.4$  to increase redundancy in high eta region in stations 3 and 4 *RE 3.1 and RE 4.1 Improved RPC*  • Main motivations/goals:

- Increase rate capability (2 kHz/cm<sup>2</sup>).

- Better time resolution for background rejection 25 ns -> 1.5 ns.

- Better spatial resolution for tracking in r direction 40 cm-> 2 cm.

- Improved contribution of RPCs to muon triggering in the forward region.

- Electronics:

- Two ends readout.

- New frontend electronics.

-ay Cage (Copper).

• New backend electronics.

**Total of 72 iRPC chambers**

<sup>1</sup> chamber  $\approx$  1.6 x 1.2 m<sup>2</sup> trapezoidal shape 20° in  $\phi$   $\implies$  18 chambers/disk

### Principle of iRPC position measurement

• Two-end readout iRPC used in CMS Phase II upgrade

• Electronics

**Dimensions**: 165 cm x (63-114) cm

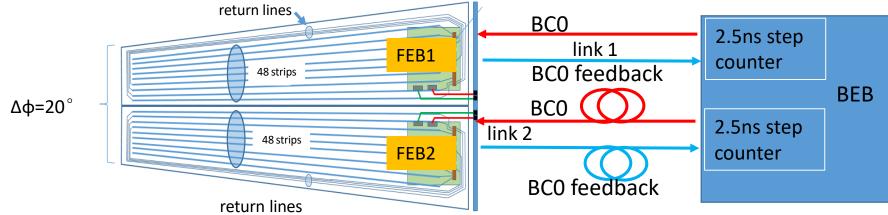

- Each iRPC chamber is equipped with 2 Frontend Electronics Boards (FEBs), connected to the backend electronics board (BEB) via 2 GBT links.

- The GBTx is a radiation tolerant chip that can be used to implement multipurpose high speed (3.2-4.48 Gbps user bandwidth) bidirectional optical links for high-energy physics experiments.

- iRPC spatial resolution (θ direction)

- Hit position: r is calculated by the time difference of signals from two ends.

- Much improved hit localization along the strip can be achieved.  $\sim 2 \text{ cm}$  from cosmic test result.

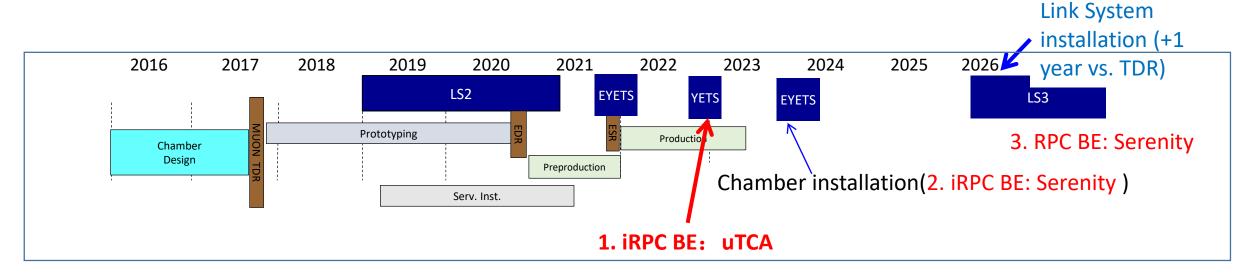

- iRPC backend

- 2 Steps Installation Roadmap: uTCA+ATCA

- 2022-2023: iRPC BE uTCA (current work for demonstrator)

- 2024: iRPC BE ATCA-Serenity (final system)

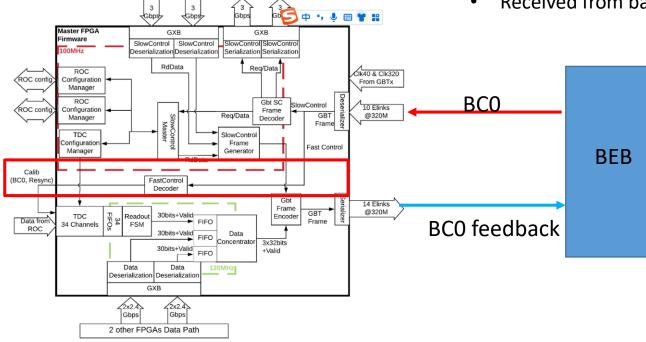

Focus on the central FPGA

### FEB signal timing

• FEB TDC timing principle

2 other FPGAs Control Path

- Fast control signal (BCO, Resync, etc.)

- BCO—the first bunch among **3564** bunch crossing as time reference for FEB.

- 3564 : circumference (26659 m )/bunch distance(7.48 m)

- Received from backend on all FEBs within a fixed latency.

| Slow Control Request Frame              |        |       | ne Header (Fa |            |         |                      | w Control Request Inform | Slow Cont               | Slow Control Payload               |           |         |  |  |

|-----------------------------------------|--------|-------|---------------|------------|---------|----------------------|--------------------------|-------------------------|------------------------------------|-----------|---------|--|--|

| Fied Name                               | Resync | BC0   | ResetSCPath   |            | FPGASel | FSVD                 | WrRe                     | q BurstAdditionnalWords |                                    |           | WrData1 |  |  |

| Field length                            | 1      | 1     | 1             | 10         | 3       | 7                    | 1                        | 8                       |                                    | 6 16      | 16      |  |  |

| GBT Frame Group                         |        |       | G4            |            |         | -                    |                          | G3                      | G                                  | 2 G1      | GO      |  |  |

| Slow Control Payload Frame              |        | Fran  | ne Header (Fa | ast contro | l)      | Slow Control Payload |                          |                         |                                    |           |         |  |  |

| Fied Name                               |        |       |               | MiscCtrl   | FPGASel |                      |                          | WrData(N)               | WrData(N+1) WrData(N+2) WrData(N+3 |           |         |  |  |

| Field length                            | 1      | 1 1 1 |               | 10         | 10 3    |                      |                          | 16                      | 16 16                              |           | 16      |  |  |

| GBT Frame Group                         |        |       | G4            |            |         |                      |                          | G3                      | G                                  | 2 G1      | GO      |  |  |

| w Control Request Fr                    | ame    | •     |               |            | 1       | Fr                   | ar                       | ne Header (             | Fas                                | st contro | D       |  |  |

| -                                       |        |       |               | _          | -       |                      |                          | _                       |                                    |           |         |  |  |

| Fied Name                               |        |       | Res           | sync       | BC      | -0                   | ResetSCPath              |                         | WiscCtrl                           | FPGASe    |         |  |  |

| Field length                            |        |       | 100 C         | 1          | 1       | 1 1                  |                          |                         | 10 3                               |           |         |  |  |

| Field length                            |        |       |               |            | 1       | -                    | -                        | T                       |                                    | 10        | 5       |  |  |

| Field length<br>GBT Frame Group         |        | +     |               |            | 1       |                      | -                        | <br>G4                  |                                    | 10        | 5       |  |  |

|                                         |        |       |               | ·          | ±       |                      |                          |                         |                                    | 10        | 5       |  |  |

| GBT Frame Group                         |        |       |               | · · · · ·  | 1<br>   |                      |                          | G4                      |                                    |           |         |  |  |

| GBT Frame Group<br>w Control Payload Fr | ame    | 2     |               |            |         | Fr                   | ar                       | G4<br>ne Header (       | Fas                                | st contro | )       |  |  |

| GBT Frame Group                         | ame    | •     |               |            | sync    | Fr                   | ar                       | G4                      | Fas                                | st contro | )       |  |  |

| GBT Frame Group<br>w Control Payload Fr | ame    | •     |               | Res        |         | Fr                   | ar                       | G4<br>ne Header (       | Fas                                | st contro | )       |  |  |

### System timing from backend

- Functionalities/tasks of iRPC Backend

- Slow Control (powering up FEB, TDC configuration, Petiroc configuration...)

- Monitoring

- Fast Control (BC0 distribution ...)

- Trigger primitive (Clusterzation)

- Readout (DAQ)

- Difficulties

- How to develop and verify BEB functions in lab without test facility like detector, FEB, or GBTx chip ?

- What is the clock requirement of FEE and how to realize?

- How to synchronize different links in the backend ?

• Timing reference distribution and correction of distribution difference .

Trigger Lab

IHEP

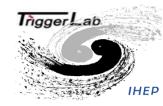

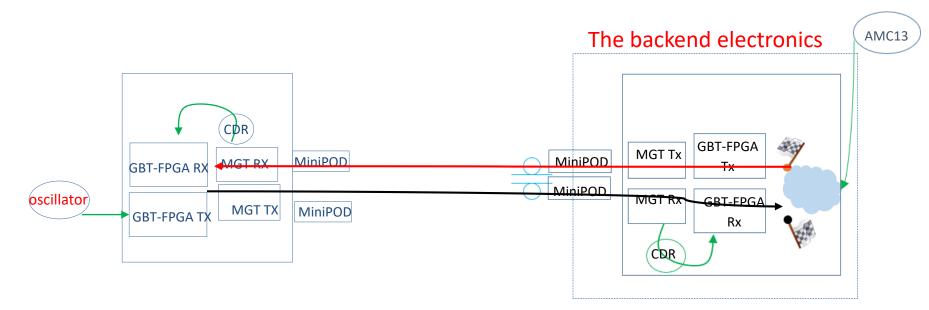

### Timing reference distribution

- Problem

- The Bunch Cross 0 (BC0) signal from AMC13 as a timing reference is distributed to each FEB located in different RPC stations by BEB.

- AMC13: This module is designed to provide TTC, DAQ and TTS services to modules in a MicroTCA crate for CMS.

- Arrival times of BC0 between links are different.

- Latency = T\_GBT FPGA + T\_length + T\_GBTx , T\_GBT FPGA and T\_GBTx are the same for all FEBs.

- Different fiber lengths lead to different latencies and this need to be measured and corrected.

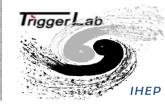

### Correction of distribution difference

- Solution

- Latency measurement need to be done.

- latency must be fixed values and measured accurately.

- A 12-bit counter of the 2.5 ns step is developed in BEB and used to measure the loopback time of different links. through a self-defined handshake mechanism.

- The downlink and uplink are estimated to have same time consuming and the difference is caused by different fiber length.

- Taking the faster link as the reference we apply a correction value to the slower link according to the loopback time via slow control.

- Correction value (1.25 ns step) = (Latency\_big Latency\_small)/2 .

- TDC data on each FEB will minus its specific correction value to minimize the latency difference between paths.

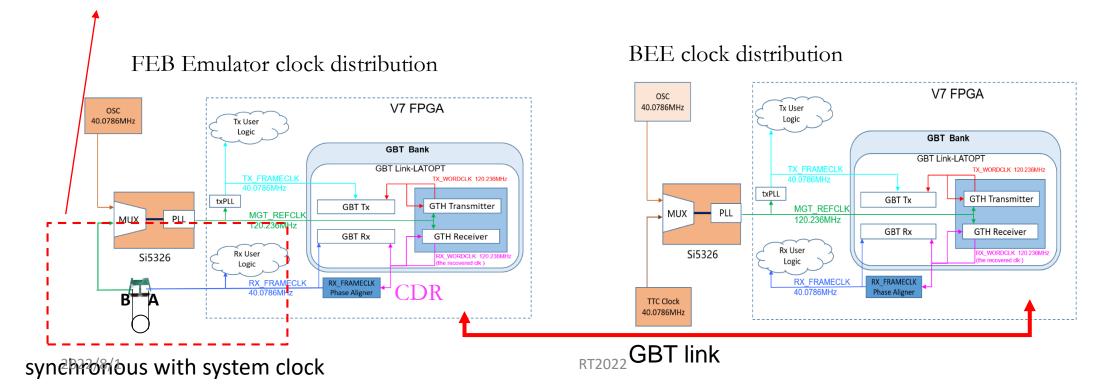

### Implementation in FEB emulator

- Before we have the real FEB electronics, we did the test using GBT-FPGA based emulator.

- FEB emulator Rx CDR clock is synchronous with BEB system clock.

- Managed to use Rx CDR clock as GBT-FPGA Tx clock.

- Through RJ-45 daughter board.

### System clock generation in FEB emulator

Trigger Lab

11

IHEP

- The backend -- 40.0786MHz system clock from AMC13 .

- FEB emulator –40.0786MHz OSC after power up.

- Rx CDR clock is generated and aligned on FEB emulator.

- Then Rx CDR clock is fanned out through RJ45 A and connected to RJ45 B .

- Clock from RJ45 B replaces OSC as FEB emulator system clock after MUX.

### **Correction** implementation

Latency measurement

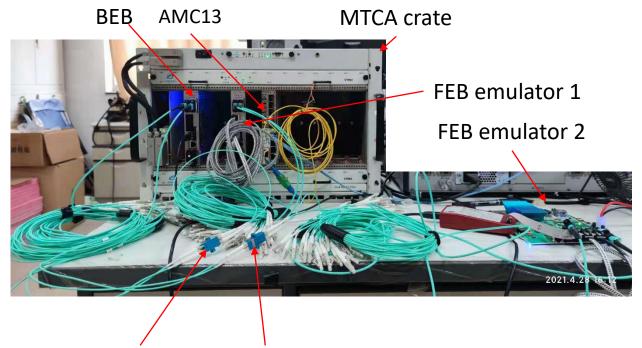

- Test System setup in Beijing lab

- System clock source: AMC13

- Backend : 1 BEB

- Frontend :2 FEB emulators(represent the 2 FEBs on 1 iRPC chamber)

GBT link 1 GBT link 2

### test result

#### • Latency measurement Test result

| Waveform - hw_ila_4                                                                                                 |                |                |         |             |             |                    |             |                      |             |             |             |             |             |             |             |             | ?.          | _ |

|---------------------------------------------------------------------------------------------------------------------|----------------|----------------|---------|-------------|-------------|--------------------|-------------|----------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|---|

| Q   +   −   ϑ   ▶   ≫   ■   ฿   @   Q   X   •f                                                                      | K → ±          | ±r +F Fe       | •     • |             |             |                    |             |                      |             |             |             |             | ٦           |             |             |             |             |   |

| LA Status: Idle                                                                                                     |                | 533            |         |             |             |                    |             |                      |             |             |             |             |             |             |             |             |             |   |

| Name                                                                                                                | Value          |                |         | 532         | 533         | 534                | 535         | 536                  | 537         | 538         | 53)         | 540         | 541         | 542         | 543         | 544         | 545         |   |

| & gbtExmplDsgn_inst/latency_measure_1/BEE_latmeasure_end                                                            | 0              |                |         |             |             |                    |             |                      |             |             |             |             |             |             |             |             |             |   |

| gbtExmplDsgn_inst/latency_measure_1/clk40_counter[12:0]                                                             | 21             |                | 19      | 20          | 21          | <u> </u>           |             |                      |             |             |             | 22          |             |             |             |             |             |   |

| gbtExmplDsgn_inst/latency_measure_1/clk_out_400MHz_counter[12:0                                                     |                |                | 199     | 209         | 219         | _ <u></u>          |             |                      | \           |             |             | 225         |             |             |             |             |             |   |

| gbtExmplDsgn_inst/latency_measure_1/datacheck_receive[111:0]                                                        | fa0babeac1dacd |                |         | a45c1a45c1a | fa0babeac1d | <u>a45c3a45c3a</u> | 445c4a45c4a | 45c5a45c5a           | 45c6a45c6a  | a45c7a45c7a | a 5c8a45c8a | 445c9a45c9a | a45caa45caa | a45cba45cba | a45cca45cca | a45cda45cda | 445cea45cea |   |

| ■ gbtExmpIDsgn_inst/latency_measure_1/datagen_reply[79:0] ■ gbtExmpIDsgn_inst/latency_measure_2/clk40_counter[12:0] | 21             | 0901009        | c1b     | c1b08c1b08c | c1b09c1b09c | c1b0ac1b0ac        | ed0babeac1d | c1b0cc1b0cc          | c1b0dc1b0dc | c1b0ec1b0ec | c b0fc1b0fc | c1b10c1b10c |             |             | c1b13c1b13c |             | c1b15c1b15c |   |

| gotExmplDsgn_inst/latency_measure_2/clk_out_400MHz_counter[12:0]                                                    |                |                | 19      | 20          | 21          |                    |             |                      |             |             |             | 22          |             |             |             |             |             |   |

| gbtExmplDsgn_inst/latency_measure_2/datacheck_receive[111:0]                                                        | fa0babeac1dacd | lcffffbeefcafe | 693     | 6935f6935f6 | fa0babeac1d | 69301693016        | 69302693026 | 69303693036          | 69304693046 | 69305693056 | 693-6553006 | 69307693076 | 69308693086 | 69309693096 | 693ca693ca6 | 693cb693cb6 | 69300693006 |   |

| 💘 gbtExmplDsgn_inst/latency_measure_2/datagen_reply[79:0]                                                           | c1b09c1b09c1b0 | 09c1b09        | c1b     | c1b08c1b08c | c1b09c1b09c | c1b0ac1b0ac        | ed0babeac1d | c1b0cc1b0cc          | c1b0dc1b0dc | c1b0.cibUec | c1b0fc1b0fc | c1b10c1b10c | c1b11c1b11c | c1b12c1b12c | c1b13c1b13c | c1b14c1b14c | c1b15c1b15c |   |

|                                                                                                                     | 1              |                |         |             |             |                    |             |                      |             |             |             |             |             |             |             |             |             | 1 |

| Measurement time ste                                                                                                | ep             | 25ns           | B       | X clo       | ck          |                    |             | 2.5 ns               | coa         | rse ti      | me          |             |             |             |             |             |             |   |

|                                                                                                                     |                |                |         |             |             |                    |             |                      |             |             |             |             |             |             |             |             |             |   |

| BEB to FEB emulator1                                                                                                | cnt            | 22*25 = 550 ns |         |             |             |                    |             | 216 * 2.5 = 540.0 ns |             |             |             |             |             | ۸ _ C       | F nc        |             |             |   |

| BEB to FEB emulator2                                                                                                | cnt            | 22*25 = 550 ns |         |             |             |                    |             | 215 * 2.5 = 537.5 ns |             |             |             |             |             | Δ = 2       | .5 115      |             |             |   |

A deterministic latency between BEB and FEB emulator was achieved and measured, indicating that the test system works normally.

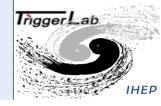

### BEB to one FEB joint test

- Joint test system setup

- One backend board receives 1 link from FEB.

- The backend performs slow control (FEB powering up, configuration, etc.) and fast control (BCO distribution, etc.) for the FEBs.

- Test results

- When the FEB receives a BCO, it will sent the BCO timestamp to backend. The result shows that the backend sends BCO to FEB every 3564BX constantly, indicating the system works normally.

- The sigma of BCO timestamp from FEB is 23.32 ps proves that the distribution of BCO is successful.

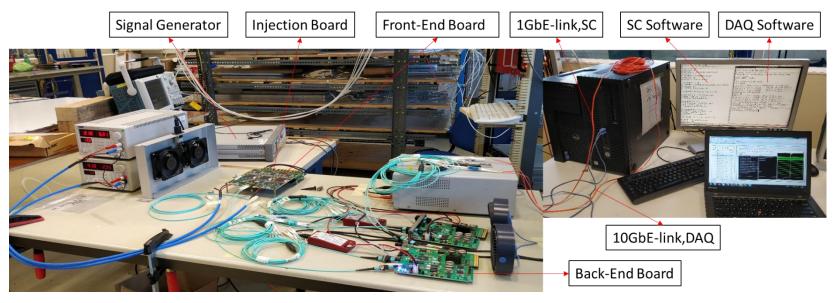

### BEB to two FEB joint test

- Joint test system setup

- One backend board receives 2 links from FEBs.

- The length of fibers are different to simulate real cases.

### BEB to two FEB test method

- Detail

- The BC0 distribution to one FEB has been proved successful.

- This method was used to measure the latency between two links, which will affect the backend trigger function rather than iRPC position resolution.

- Eg. If muons hit the middle of the chamber, FEB1 and FEB2 will give same position(~2 cm) but different timing because of different latency.

- The backend records the start of BCO distribution and the end of BCO feedback via a 12-bit counter of the 2.5 ns step.

- Half of the time difference(1.25 ns step) between two links will be used to correct the slower link via slow control.

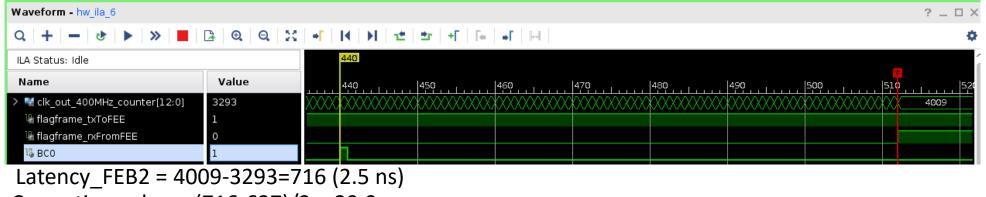

### BEB to two FEB quick test result

• Latency measurement test result

| Waveform - hw_ila_6              |       |                 |              |                  |     |     |     |     |                     | ? _  | □× |

|----------------------------------|-------|-----------------|--------------|------------------|-----|-----|-----|-----|---------------------|------|----|

| Q   +   −   ϑ   ▶   ≫   ■        | 🔁 🔍 Q | 20   <b>-</b> F | I €   M   12 | :   ±r   +Γ   Te |     |     |     |     |                     |      | •  |

| ILA Status: Idle                 |       | 4               | 48           |                  |     |     |     |     |                     |      |    |

| Name                             | Value |                 | 450          | 460              | 470 | 480 | 490 | 500 | 510                 | 520  | 53 |

| > 💐 clk_out_400MHz_counter[12:0] | 1407  | XXXXX           | XXXXXXXXX    |                  |     |     |     |     | 00 <mark></mark> 00 | 2044 |    |

| <u> </u>                         | 1     |                 | 1447         |                  |     |     |     |     |                     |      |    |

|                                  | 0     |                 |              |                  |     |     |     |     |                     |      |    |

| 15 BCO                           | 1     |                 |              |                  |     |     |     |     |                     |      |    |

#### Latency\_FEB1 = 2044-1407=637 (2.5 ns)

Correction value = (716-637)/2 = 39.0

A deterministic latency between BEB and FEB was achieved and measured, this latency difference can be used to correct the FEB TDC timestamp.

Next step

- The latency measurement requirement (2.5 ns/1.25 ns/smaller?) and effect need to be studied further.

- The implementation of latency measurement can be improved based on requirement.

- iRPC timing reference issue including FEB signal timing and backend system timing has been researched and verified.

- Timing reference distribution and correction has been studied in both emulator and FEB.

- The test results show that the sigma of BCO distribution is 23.32 ps which will be used for iRPC position calculating. The latency between two links was measured and waiting to be corrected and verified in the next step.

## Thanks!

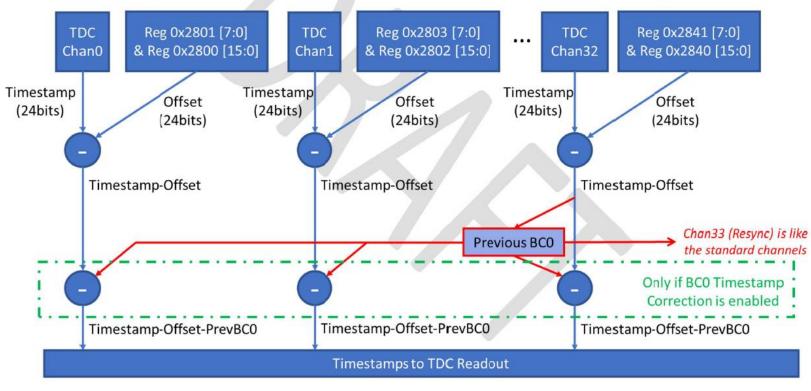

### FEB TDC timestamp correction module

TDC timestamp correction module (Channel offset SlowControl slave base address -> 0x2800)

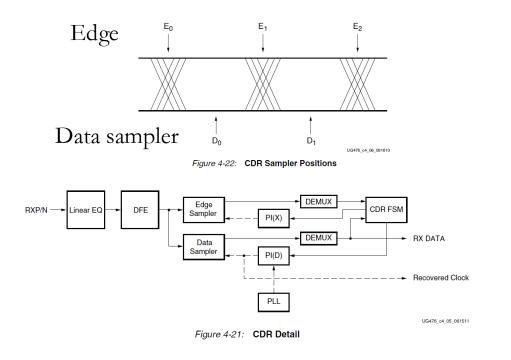

### Rx CDR clock introduction

- Stream of Serial Data 10010 All Subsequent Data Transmitted First Alignment Block Finds Aligned to Correct Comma or Header Byte Boundary RXUSRCLK2 A minimum of 32 RXUSRCLK2 cycles are required between two RXSLIDE **BXSLIDE** pulses Slide results on RXDATA **RXSlide** after several cycles of latency through the PCS path Intermediate Data 00000000 RXDATA 000000000000100111 00000000000010011 0100111110 TXDATA 0000000001001111100 UG476 c4 53 06201

- The CDR state machine uses the data from both the edge and data samplers to determine the phase of the incoming data stream and to control the phase interpolators (PIs)

The data is shifted right by one bit for every RXSLIDE pulse issued. The GBT receiver searches for the Header in the incoming data and checks it. Link is established after GBT Rx receiving 24 successive Headers(0110/0101). Then use Header flag to align the Rx CDR clock.

### Phase 2 RPC Upgrade Project Overview